并行数据转换为串行数据,总线输出

微机原理及应用综合练习二

微机原理综合练习二第一章微型计算机系统概述一、单项选择题1. 计算机中的CPU指的是()A.控制器B.运算器和控制器C.运算器、控制器和主存D.运算器2. 计算机的发展阶段的划分通常是按计算机所采用的()A.内存容量B.电子器件C.程序设计语言D.操作系统3. CPU中的运算器的主要功能是()A.负责读取并分析指令B.算术运算和逻辑运算C.指挥和控制计算机的运行D.存放运算结果4. 计算机系统总线中,可用于传送读、写信号的是()A.地址总线B.数据总线C.控制总线D.以上都不对二、填空题1. 在微机的三组总线中,总线是双向的。

2. 计算机软件系统分为和。

第二章80X86微处理器一、单项选择题1. 8088CPU的外部数据总线的位数为()A.4 B.8C.16 D.322. 在8086CPU中,不属于总线接口部件的是()A.20位的地址加法器B.指令队列C.段地址寄存器D.通用寄存器3. 在8088系统中,只需1片8286就可以构成数据总线收发器,而8086系统中构成数据总线收发器的8286芯片的数量为()A.1B.2C.3 D.44. 8086的指令队列的长度是()A.4个字节B.5个字节C.6个字节D.8个字节5. CPU内部的中断允许标志位IF的作用是()A.禁止CPU响应可屏蔽中断B.禁止中断源向CPU发中断请求C.禁止CPU响应DMA操作D.禁止CPU响应非屏蔽中断6. 8086CPU中,一个最基本的总线周期中的时钟周期(T状态)数目为()A.1 B.4C.2 D.67. 8086的执行部件EU中通用寄存器包括()A.AX,BX,SP,BPB.AX,BX,CX,DXC.AL,BL,CL,DLD.SP,BP,SI,DI8. 在8086的存储器写总线周期中,微处理器给出的控制信号(最小模式下)WR,RD,M/IO分别是()A.1,0,1B.0,1,0C.0,1,1D.1,0,09. 在8086的总线周期中,ALE信号的有效位置是()A.T1 B.T2C.T3 D.T410. 8086 CPU响应DMA传送请求的信号是()A.READY B.HLDAC.RDD.INTA11. 在8086的存储器写总线周期中,微处理器给出的控制信号(最小模式下)WR,RD,M/IO分别是()A.1,0,1B.0,1,0C.0,1,1D.1,0,012. 当8086CPU从总线上撤消地址,而使总线的低16位置成高阻态时,其最高4位用来输出总线周期的()A.数据信息B.控制信息C.状态信息D.地址信息13. 在8086的小模式系统中,M/IO、RD和WR当前信号为1、0、1,表示现在进行的是()A.I/O读B.I/O写C.存储器写D.存储器读14. 8086CPU中指令队列采用的访问原则是()A.先进先出B.先进后出C.后进先出D.自由出入15. 在8086系统中,内存采取分段结构,段与段之间是()A.分开的B.连续的C.没有限制,都可以D.重叠的16. 在8086系统中,CPU被启动后,IP及四个段寄存器的初始状态是()A.全部清0 B.全部置成FFFFHC.IP=FFFFH,四个段寄存器清0 D.CS=FFFFH,其它寄存器清017. 在8086系统中,一条指令的存放地址一般由段地址寄存器CS和指令指针寄存器IP来决定。

UART总线

UART (Universal Asynchronous Receiver/Transmitter)通用异步收发器UART是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠票也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。

现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

1.UART协议的工作特点1.1数据采样UART协议是实现设备之间低速数据通信的标准协议。

因发送时不需同时发送时钟,故此协议为异步。

UART链接典型为38400,9600波特。

如下图1,UART字符格式为1个起始位,5~8个数据位,1个地址位或奇偶位(可选),1个停止位。

由于接收器、发送器异步工作,无需联接接收和发送时钟。

接收器采取对输入数据流高度采样方式,通常采样为16,并根据采样值确定位值。

按惯例,使用16个采样值的中间三个值。

1.2 UART帧区分UART一参数MAX-IDL,用来设置空闲字符的多少。

一旦一字符在线上被接收,UART 控制器开始计数接收到的空闲字符。

若下一数据字符接收前,一MAX-IDL多个空闲字符被接收,则产生空闲时间,缓冲区被关闭。

顺次对CPU32+核心发出一中断请求,要求从缓冲区接收数据。

SPI、I2C、UART三种串行总线的原理、区别及应用

简朴描述:SPI 和I2C这两种通信方式都是短距离旳,芯片和芯片之间或者其他元器件如传感器和芯片之间旳通信。

SPI和IIC是板上通信,IIC有时也会做板间通信,但是距离甚短,但是超过一米,例如某些触摸屏,手机液晶屏那些很薄膜排线诸多用IIC,I2C能用于替代原则旳并行总线,能连接旳多种集成电路和功能模块。

I2C是多主控总线,因此任何一种设备都能像主控器同样工作,并控制总线。

总线上每一种设备均有一种独一无二旳地址,根据设备它们自己旳能力,它们可以作为发射器或接受器工作。

多路微控制器能在同一种I2C总线上共存这两种线属于低速传播;ﻫ而UART是应用于两个设备之间旳通信,如用单片机做好旳设备和计算机旳通信。

这样旳通信可以做长距离旳。

UART和,UART就是我们指旳串口,速度比上面三者快,最高达100K左右,用与计算机与设备或者计算机和计算之间通信,但有效范畴不会很长,约10米左右,UART长处是支持面广,程序设计构造很简朴,随着USB旳发展,UART也逐渐走向下坡;SmBus有点类似于USB设备跟计算机那样旳短距离通信。

ﻫ简朴旳狭义旳说SPI和I2C是做在电路板上旳。

而UART和SMBUS是在机器外面连接两个机器旳。

具体描述:1、UART(TX,RX)就是两线,一根发送一根接受,可以全双工通信,线数也比较少。

数据是异步传播旳,对双方旳时序规定比较严格,通信速度也不是不久。

在多机通信上面用旳最多。

2、SPI(CLK,I/O,O,CS)接口和上面UART相比,多了一条同步时钟线,上面UART旳缺陷也就是它旳长处了,对通信双方旳时序规定不严格不同设备之间可以很容易结合,并且通信速度非常快。

一般用在产品内部元件之间旳高速数据通信上面,如大容量存储器等。

3、I2C(SCL,SDA)接口也是两线接口,它是两根线之间通过复杂旳逻辑关系传播数据旳,通信速度不高,程序写起来也比较复杂。

一般单片机系统里重要用来和24C02等小容易存储器连接。

serdes原理

serdes原理SerDes原理解析什么是SerDesSerDes是一种串行器/解串器(Serializer/Deserializer)的简写,它是一种用于将并行数据转换为串行数据(或者将串行数据转换为并行数据)的集成电路(IC)技术。

在数字通信领域,SerDes常用于高速数据传输和通信接口。

串行数据和并行数据在开始解释SerDes原理之前,我们需要了解串行数据和并行数据的概念。

•串行数据是指将数据位按照顺序一个接一个地发送,每个数据位之间通过时钟信号来区分。

•并行数据是指将多个数据位同时发送,每个数据位占用一个信号线。

SerDes的原理SerDes的主要功能是将并行数据转换为串行数据(Serializer)或将串行数据转换为并行数据(Deserializer)。

它由两部分组成:串行器和解串器。

串行器(Serializer)串行器将并行数据转换为串行数据,实现了数据的串行化。

它的输入为多个并行数据位,输出为一个串行数据流。

串行器的工作流程如下:1.并行输入数据位通过数据处理电路进行编码和加工,以适应传输和接收的要求。

2.经过编码和加工的数据经过串行器内部的串行输出电路,逐位地传输到输出信号线上。

3.在串行器内部,每个数据位之间通过时钟信号来同步。

串行器常用于数据传输的发送端,如计算机内部总线、高速网络通信和存储器接口等领域。

解串器(Deserializer)解串器将串行数据转换为并行数据,实现了数据的解串行化。

它的输入为一个串行数据流,输出为多个并行数据位。

解串器的工作流程如下:1.串行输入数据流通过输入接收电路,逐位地接收到解串器内部。

2.在解串器内部,输入数据流中的每个数据位经过时钟信号的同步和解码处理。

3.解码后的数据经过解串器的并行输出电路,并行地输出到多个数据线上。

解串器常用于数据传输的接收端,如计算机内部总线、高速网络通信和存储器接口等领域。

SerDes的应用SerDes技术在现代通信领域有着广泛的应用,主要体现在以下几个方面:1.高速网络通信:SerDes能够在高速网络中实现可靠的数据传输和接收,提升网络带宽和通信速度。

计算机三级(PC技术)笔试149

[模拟] 计算机三级(PC技术)笔试149一、选择题(每题1分,共60分) 在下列各题的[A]、[B]、[C]、[D] 四个选项中,只有一个选项是正确的。

第1题:在数据传送过程中,数据由串行变为并行,或并行变为串行,这种转换是通过接口电路中的______实现的。

A.数据寄存器B.移位寄存器C.锁寄存器D.地址寄存器参考答案:B第2题:下列关于批处理操作系统的描述,错误的是( )。

A.它属于单用户操作系统B.它属于多用户操作系统C.它的两大特点是多道运行和成批处理D.它可以脱机操作参考答案:A第3题:RAID是一种提高键盘存储速度、容量和可靠性的技术。

下面有关RAID的叙述中,错误的是______。

A.RAID的中文名称是磁盘冗余阵列B.条块技术可以提高磁盘存储器的传输性能C.为了提高可靠性,RAID中采用了镜像冗余技术和校验冗余技术D.RAID只能用SCSI磁盘驱动器来实现参考答案:D第4题:假设某汇编语言源程序的代码段的段名是CSEG,启动地址为START,下面可用来预置CS寄存器的语句是( )。

A.ASSUME CS:CSEGB.END STARTC.MOV CS,CSEGD.MOV AX,CSEG和MOV CS,AX参考答案:B第5题:网卡的功能是将PC机或服务器连接到网络上,下面关于以太网网卡的叙述中,不正确的是( )。

A.百兆速率的以太网网卡采用BNC细同轴电缆接口B.以太网网卡采用CSMA/CD介质访问控制方法C.每块网卡都有一个全球惟一的网络地址(网卡的物理地址)D.目前使用最多的以太网网卡是10/100M自适应网卡参考答案:A网卡(Network Interface Card,NIC)作为局域网中最基本的部件之一,又可以称之为网络卡或网络接口卡。

网卡的工作原理,就是整理计算机上发往网络上的数据,并将数据分解为适当大小的数据包之后向网络发送。

第6题:下面关于PC机键盘的叙述中,不正确的是( )。

总线是什么?常见总线类型

总线是什么?常见总线类型

摘要: 谈总线之前,首先应该明白总线是什幺?度娘的完整定义是:总线是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束,按照计算机所传输的信息种类。

其实,小编觉得,总线就是是一种内部结构,它是cpu、内存、...

谈总线之前,首先应该明白总线是什幺?度娘的完整定义是:总线是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束,按照计算机所传输的信息种类。

其实,小编觉得,总线就是是一种内部结构,它是cpu、内存、输入、输出设备传递信息的公用通道。

工程师为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线。

另外就是采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备间实现互连。

总线分类:

1、总线按功能和规范可分为五大类型:数据总线、地址总线、控制总线、扩展总线及局部总线。

数据总线、地址总线和控制总线也统称为系统总线,即通常意义上所说的总线。

常见的数据总线为ISA、EISA、VESA、PCI 等。

地址总线:是专门用来传送地址的,由于地址只能从CPU 传向外部存储器或I/O 端口,所以地址总线总是单向三态的,这与数据总线不同,地址总线的位数决定了CPU 可直接寻址的内存空间大小。

SPI、I2C、UART三种串行总线的区别

c中没有引用————char &c =b ;上面的式子在c里面是错误的,提示错误:error: expected ‘;’, ‘,’ or ‘)’ before ‘&’ tokenc中没有引用,c++中才有,如果你用的是gcc编译器,将会出错,如果改为g++,就可以了;如果不想改,那么就只能用指针来传要改变的参数了SPI、I2C、UART三种串行总线的区别SPI:高速同步串行口。

3~4线接口,收发独立、可同步进行UART:通用异步串行口。

按照标准波特率完成双向通讯,速度慢SPI:一种串行传输方式,三线制,网上可找到其通信协议和用法的3根线实现数据双向传输串行外围接口Serial peripheral interfaceUART:通用异步收发器UART是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠票也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。

现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

I2C:能用于替代标准的并行总线,能连接的各种集成电路和功能模块。

I2C是多主控总线,所以任何一个设备都能像主控器一样工作,并控制总线。

SPI和UART的区别

SPI:高速同步串行口。

3~4线接口,收发独立、可同步进行UART:通用异步串行口。

按照标准波特率完成双向通讯,速度慢I2C:一种串行传输方式,三线制,网上可找到其通信协议和用法的3根线实现数据双向传输串行外围接口 Serial peripheral interfaceUART:通用异步收发器UART是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠票也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART 是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。

现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

I2C:能用于替代标准的并行总线,能连接的各种集成电路和功能模块。

I2C是多主控总线,所以任何一个设备都能像主控器一样工作,并控制总线。

总线上每一个设备都有一个独一无二的地址,根据设备它们自己的能力,它们可以作为发射器或接收器工作。

多路微控制器能在同一个I2C总线上共存。

更详细的区别:第一个区别当然是名字:SPI(Serial Peripheral Interface:串行外设接口);I2C(INTER IC BUS:意为IC之间总线)UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)第二,区别在电气信号线上:SPI总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。

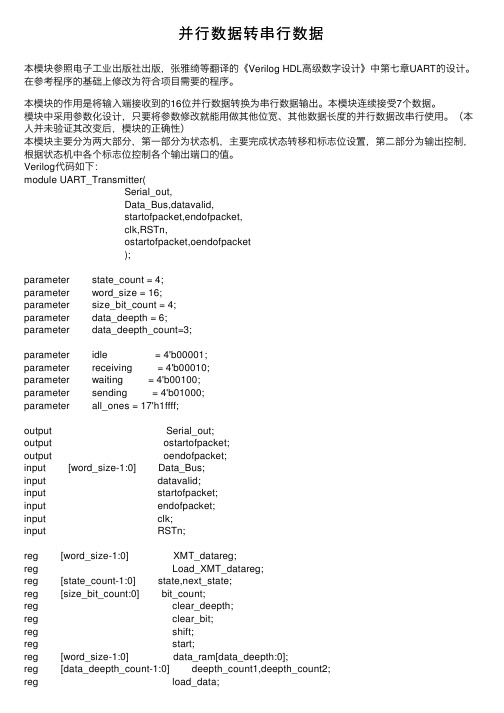

并行数据转串行数据

并⾏数据转串⾏数据本模块参照电⼦⼯业出版社出版,张雅绮等翻译的《Verilog HDL⾼级数字设计》中第七章UART的设计。

在参考程序的基础上修改为符合项⽬需要的程序。

本模块的作⽤是将输⼊端接收到的16位并⾏数据转换为串⾏数据输出。

本模块连续接受7个数据。

模块中采⽤参数化设计,只要将参数修改就能⽤做其他位宽、其他数据长度的并⾏数据改串⾏使⽤。

(本⼈并未验证其改变后,模块的正确性)本模块主要分为两⼤部分,第⼀部分为状态机,主要完成状态转移和标志位设置,第⼆部分为输出控制,根据状态机中各个标志位控制各个输出端⼝的值。

Verilog代码如下:module UART_Transmitter(Serial_out,Data_Bus,datavalid,startofpacket,endofpacket,clk,RSTn,ostartofpacket,oendofpacket);parameter state_count = 4;parameter word_size = 16;parameter size_bit_count = 4;parameter data_deepth = 6;parameter data_deepth_count=3;parameter idle = 4'b00001;parameter receiving = 4'b00010;parameter waiting = 4'b00100;parameter sending = 4'b01000;parameter all_ones = 17'h1ffff;output Serial_out;output ostartofpacket;output oendofpacket;input [word_size-1:0] Data_Bus;input datavalid;input startofpacket;input endofpacket;input clk;input RSTn;reg [word_size-1:0] XMT_datareg;reg Load_XMT_datareg;reg [state_count-1:0] state,next_state;reg [size_bit_count:0] bit_count;reg clear_deepth;reg clear_bit;reg shift;reg start;reg [word_size-1:0] data_ram[data_deepth:0];reg [data_deepth_count-1:0] deepth_count1,deepth_count2;reg load_data;reg ending;reg ostartofpacket;reg oendofpacket;assign Serial_out = XMT_datareg[0];always @ (state or startofpacket or endofpacket or deepth_count1 or deepth_count2 or datavalid or bit_count )begin:Output_and_next_stateLoad_XMT_datareg = 0;load_data = 0;clear_deepth = 0;clear_bit = 0;shift = 0;start = 0;ending = 0;next_state = state;case(state)idle:if(startofpacket == 1)beginload_data = 1;next_state = receiving;endreceiving:beginif(datavalid == 1)load_data = 1;if(endofpacket == 1)beginnext_state = waiting;endendwaiting:beginstart = 1;Load_XMT_datareg = 1;next_state = sending;endsending:if(bit_count != word_size-1)shift = 1;elsebeginif(deepth_count2!=deepth_count1)beginclear_bit =1;Load_XMT_datareg =1;endelsebeginclear_bit =1;clear_deepth = 1;ending = 1;next_state = idle;endenddefault:next_state = idle;endcaseendalways @ (posedge clk or negedge RSTn)begin:State_Transitionsif(RSTn == 0)state <= idle;elsestate <= next_state;endalways @ (posedge clk or negedge RSTn)begin:Register_Transfersif(RSTn == 0)beginXMT_datareg <= all_ones;bit_count <= 0;deepth_count1 <= 0;deepth_count2 <= 0;endelsebeginif(load_data ==1)begindata_ram[deepth_count1] <= Data_Bus;deepth_count1 <= deepth_count1 + 1;endelse if(clear_deepth == 1)deepth_count1 <= 0;if(start == 1)ostartofpacket <= 1;elseostartofpacket <= 0;if(Load_XMT_datareg == 1)beginXMT_datareg <= data_ram[deepth_count2];deepth_count2 <= deepth_count2 + 1;endelse if(clear_deepth == 1)deepth_count2 <= 0;if(clear_bit == 1)bit_count <= 0;else if(shift == 1)bit_count <= bit_count + 1;if(ending == 1)oendofpacket <= 1;elseoendofpacket <= 0;if(shift == 1)XMT_datareg <= {1'b1,XMT_datareg[word_size-1:1]};endendendmodule注:state_count :状态机中状态个数word_size数据宽度size_bit_count:⽤于位宽计数,与数据宽度相关,例如:16位宽度则要4位计数,32位宽度则要5位计数data_deepth:数据长度-1,本模块数据长度为7,data_deepth_count:⽤于数据长度计数,作⽤类似于size_bit_count。

嵌入式系统原理及应用复习知识点总结

第一章1、嵌入式系统的应用范围:军事国防、消费电子、信息家电、网络通信、工业控制。

2、嵌入式系统定义:嵌入式系统是以应用为中心,以计算机技术为基础,软件与硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

(嵌入式的三要素:嵌入型、专用性与计算机系统)。

3、嵌入式系统的特点:1)专用性强;2)实时约束;3)RTOS;4)高可靠性;5)低功耗;6)专用的开发工具和开发环境;7)系统精简;4、嵌入式系统的组成:(1)处理器:MCU、MPU、DSP、SOC;(2)外围接口及设备:存储器、通信接口、I/O接口、输入输出设备、电源等;(3)嵌入式操作系统:windows CE、UCLinux、Vxworks、UC/OS;(4)应用软件:Bootloader5、嵌入式系统的硬件:嵌入式微处理器(MCU、MPU、DSP、SOC),外围电路,外部设备;嵌入式系统的软件:无操作系统(NOSES),小型操作系统软件(SOSES),大型操作系统软件(LOSES)注:ARM处理器三大部件:ALU、控制器、寄存器。

6、嵌入式处理器特点:(1)实时多任务;(2)结构可扩展;(3)很强的存储区保护功能;(4)低功耗;7、DSP处理器两种工作方式:(1)经过单片机的DSP可单独构成处理器;(2)作为协处理器,具有单片机功能和数字处理功能;第二章1、IP核分类:软核、固核、硬核;2、ARM处理器系列:(1)ARM7系列(三级流水,thumb指令集,ARM7TDMI);(2)ARM9系列(DSP处理能力,ARM920T)(3)ARM/OE(增强DSP)(4)SecurCone 系列(提供解密安全方案);(5)StrongARM系列(Zntle产权);(6)XScale系列(Intel产权);(7)Cortex系列(A:性能密集型;R:要求实时性;M:要求低成本)3、ARM系列的变量后缀:(1)T:thumb指令集;(2)D:JTAG调试器;(3)快速乘法器;(4)E:增强DSP指令;(5)J:Jave加速器4、ARM{X}{Y}{Z}{T}{D}{M}{I}{E}{J}{F}{S} :x—系列号,y—内部存储管理和保护单元,Z—含有高速缓存。

UART简介

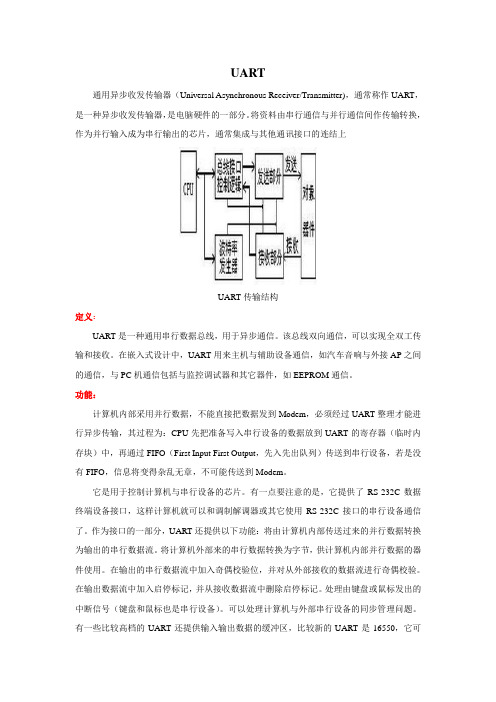

UART通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),通常称作UART,是一种异步收发传输器,是电脑硬件的一部分。

将资料由串行通信与并行通信间作传输转换,作为并行输入成为串行输出的芯片,通常集成与其他通讯接口的连结上UART传输结构定义:UART是一种通用串行数据总线,用于异步通信。

该总线双向通信,可以实现全双工传输和接收。

在嵌入式设计中,UART用来主机与辅助设备通信,如汽车音响与外接AP之间的通信,与PC机通信包括与监控调试器和其它器件,如EEPROM通信。

功能:计算机内部采用并行数据,不能直接把数据发到Modem,必须经过UART整理才能进行异步传输,其过程为:CPU先把准备写入串行设备的数据放到UART的寄存器(临时内存块)中,再通过FIFO(First Input First Output,先入先出队列)传送到串行设备,若是没有FIFO,信息将变得杂乱无章,不可能传送到Modem。

它是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠标也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。

如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

单片机知识点

试题1 参考答案一、填空题(25分,每空1分)1. A T89S51单片机为8 位单片机3. A T89S51的异步通信口为全双工(单工/半双工/全双工)4. A T89S51有 2 级中断, 5 个中断源5. A T89S51内部数据存储器的地址范围是00H~7FH ,位地址空间的字节地址范围是20H~2FH ,对应的位地址范围是00H~7FH ,外部数据存储器的最大可扩展容量是64K 。

6. A T89S51单片机指令系统的寻址方式有__寄存器寻址__、____直接寻址____、___寄存器间接寻址_____、_立即寻址____、基址寄存器加变址寄存器寻址。

10. 若A中的内容为67H,那么,P标志位为 1 。

11. 74LS138是具有3个输入的译码器芯片,其输出作为片选信号时,最多可以选中8 片芯片。

3.串行口方式3发送的第9位数据要事先写入(SCON )寄存器的( TB8)位。

4.串行口的方式0的波特率为( f OSC/12 )。

6.在内部RAM中可位寻址区中,位地址为40H的位,该位所在字节的字节地址为(28H)。

7.如果(A)=58H,(R1)= 49H,(49H)= 79H,执行指令XCH A, @R1后;结果(A)=( 49 H ) ,(49H)=( 58H )。

8.利用81C55可以扩展(3)个并行口,(256)个RAM单元。

9.当单片机复位时PSW=(00 )H,SP=(07H),P0~P3口均为(高)电平。

10.若A中的内容为88H,那么,P标志位为(0 )。

11.当A T89S51执行MOVC A,@A+ DPTR指令时,伴随着(PSEN* )控制信号有效。

12.A T89S51访问片外存储器时,利用(ALE)信号锁存来自(P0口)发出的低8位地址信号。

13.已知fosc=12MHz,T0作为定时器使用时,其定时时间间隔为(1us )。

14.若A T89S51外扩8KB 程序存储器的首地址若为1000H,则末地址为(2FFF)H。

SPI、I2C、UART、USB串行总线协议的区别

SPI、I2C、UART、USB串行总线协议的区别SPI、I2C、UART三种串行总线协议的区别第一个区别当然是名字:SPI(Serial Peripheral Interface:串行外设接口);I2C(INTER IC BUS)UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)第二,区别在电气信号线上:SPI总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。

SPI总线可以实现多个SPI设备互相连接。

提供SPI串行时钟的SPI设备为SPI主机或主设备(Master),其他设备为SPI从机或从设备(Slave)。

主从设备间可以实现全双工通信,当有多个从设备时,还可以增加一条从设备选择线。

如果用通用IO口模拟SPI总线,必须要有一个输出口(SDO),一个输入口(SDI),另一个口则视实现的设备类型而定,如果要实现主从设备,则需输入输出口,若只实现主设备,则需输出口即可,若只实现从设备,则只需输入口即可。

I2C总线是双向、两线(SCL、SDA)、串行、多主控(multi-master)接口标准,具有总线仲裁机制,非常适合在器件之间进行近距离、非经常性的数据通信。

在它的协议体系中,传输数据时都会带上目的设备的设备地址,因此可以实现设备组网。

如果用通用IO口模拟I2C总线,并实现双向传输,则需一个输入输出口(SDA),另外还需一个输出口(SCL)。

(注:I2C资料了解得比较少,这里的描述可能很不完备)UART总线是异步串口,因此一般比前两种同步串口的结构要复杂很多,一般由波特率产生器(产生的波特率等于传输波特率的16倍)、UART接收器、UART发送器组成,硬件上由两根线,一根用于发送,一根用于接收。

显然,如果用通用IO口模拟UART总线,则需一个输入口,一个输出口。

第三,从第二点明显可以看出,SPI和UART可以实现全双工,但I2C不行;第四,看看牛人们的意见吧!wudanyu:I2C线更少,我觉得比UART、SPI更为强大,但是技术上也更加麻烦些,因为I2C需要有双向IO的支持,而且使用上拉电阻,我觉得抗干扰能力较弱,一般用于同一板卡上芯片之间的通信,较少用于远距离通信。

电子类基础课试题B

河南省2021年普通高等学校对口招收中等职业学校毕业生测验电子类根底课试题卷考生注意:所有答案都要写在答题卡上,写在试题卷上无效一、选择题〔电子技术根底1-30;电工根底31-55。

每题2分,共110分。

每题中只有一个选项是正确的,请将正确选项涂在答题卡上〕1.半导体二极管,此中区的引出线称二极管的负极。

A.N B.P C.Si D.Ge 2.稳压二极管的正常工作状态是A.导通状态B.截止状态C.反向击穿状态D.任意状态3.假设使三极督工作在截止区,必需满足的外部条件是A.发射结正偏,集电结反偏B.发射结正偏,集电结正偏C.发射结反偏,集电结反偏D.发射结反偏,集电结正偏4.在共发射极底子放大电路中,基极电阻R b的作用是A.放大电流B.调节基极偏置电流C.把放大的电流转换成电压D.防止输入信号被短路5.放大器的电压放大倍数A V =﹣70,此中负号代表A.放人倍数小于0 B.同相放大C.反向放大D.衰减6.抱负集成运放的开环电压放大倍数是A.常数B.小于零C.等于零D.无穷大7.通用型集成运放的输入级采用差动放大电路,这是因为它的A.输入电阻低B.输出电阻高C.共模按捺比大D.电压放大倍数小8.OCL电路采用的直流电源是A.正电源B.负电源C.不确定D.正负双电源第1 页〔共9 页〕第 2 页〔共 9 页〕9.影响放大电路静态工作点的因素中 的影响最大。

A .放大倍数B .电流C .电压D .温度10.反响信号的极性和原假设的基极信号极性相反为A .正反响B .负反响C .电流反响D .电压反响11.要提高放大器的输出电阻,可以采用A .电压负反响B .电流负反响C .交流反响D .直流反响12.在稳压管稳压电路中,表达正确的选项是A .稳压管并联B .稳压管串联C .输出电压可以调节D .属于串联型稳压电路13.集成三端稳压器CW7815的输出电压为A .5 VB .9 VC .12 VD .15 V14.串联型稳压电源中调整管处于A .放大状态B .开关状态C .饱和状态D .截止状态15.交越掉真属于非线性掉真之一,此中 也属于非线性掉真A .饱和掉真,频率掉真B .截止掉真,频率掉真C .饱和掉真,截止掉真D .饱和掉真,截止掉真,频率掉真16.自激振荡的起振条件是A .u u F A <1B .u u F A =1C .u u F A >1D .1 u u F A 17.十进制数27对应的二进制数为A .10010B .10011C .11010D .1101118.非门的逻辑功能是A .有0出1,有1出1B .有1出1,有1出0C .有0出1,有1出0D .有1出1,有1出019.逻辑函数的化简方法有 两种。

serdes总线通信原理

serdes总线通信原理

SERDES(Serializer/Deserializer)是一种用于高速数据传输的通信技术,常用于计算机系统内部的芯片和模块之间的通信。

它将并行数据转换为串行数据,然后通过串行线路进行传输,接收端再将串行数据转换回并行数据。

SERDES总线通信原理包括以下步骤:

1. 并行数据输入:并行数据从发送端输入到SERDES芯片。

2. 数据编码:SERDES芯片将并行数据进行编码,通常采用高效的编码技术,如8B/10B或者64B/66B编码。

3. 串行数据转换:编码后的数据转换为串行数据,通过串行线路进行传输。

4. 传输:串行数据通过传输线路传输到接收端。

5. 串行数据转换:接收端的SERDES芯片将串行数据转换为并行数据。

6. 数据解码:接收端的SERDES芯片对串行数据进行解码,将其恢复为原始的并行数据。

7. 并行数据输出:解码后的并行数据输出到接收端的设备或模块。

SERDES总线通信原理的优点包括:

1. 传输速率高:SERDES技术可以实现高速数据传输,可以满足对带宽要求较高的应用。

2. 传输距离长:通过串行传输可以减少信号衰减和时钟抖动,使得

数据传输距离可以更远。

3. 线路复杂度低:相比于并行传输,串行传输只需要较少的线路和连接器,可以减少系统复杂度和成本。

4. 抗干扰能力强:SERDES技术可以采用差分信号传输,可以有效抑制电磁干扰和噪声影响。

SERDES总线通信原理通过将并行数据转换为串行数据进行传输,可以实现高速、长距离、低复杂度、抗干扰的数据传输。

I2C总线工作原理

I2C总线工作原理I2C总线工作原理 (1)1 I2C总线特点 (1)2 I2C总线协议 (2)2.1 起始和停止条件 (2)2.2 数据传输格式 (3)2.3 应答ACK信号的传送 (3)2.4仲裁和时钟同步 (4)2.5 7位的地址格式 (4)3 串/并、并/串转换 (5)3.1并串转换原理 (5)3.2串并转换原理 (5)4 HE寄存器总线工作原理 (5)5 E2PROM原理 (6)6 V erilog 硬件设计语言 (7)7 集成电路设计流程 (8)1 I2C总线特点I2C双向串行总线将主机或者从机的并行数据转换为串行数据,并通过SDA 线传输。

SCL则是串行时钟线,I2C总线通过SDA和SCL两条串行总线实现设备器件间的通信。

与其它串行总线相比,I2C总线具有一下几方面的特点:(1).只有两条总线线路:一条串行数据线(SDA);一条串行时钟线(SCL)。

(2).每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机、从机关系软件设定的地址;主机可以作为主机发送器或者主机接收器。

(3).它是一个真正的多主机系统,如果两个或者更多主机同时初始化数据传输可以通过冲突检测和仲裁防止数据被破坏。

(4).串行的8位双向数据传输位速率在标准模式下可以达到100kbit/s,快速模式下可以达到400kbit/s,高速模式下可以达到3.4Mbit/s。

(5).I2C总线支持任何IC生产过程(NMOS、CMOS、双极性)。

并且通过SDA、SCL两条串行线与连接到总线上的器件间传递信息。

每个器件都有一个唯一的是地址识别,而且都可以作为一个接收器或者发送器(由器件的功能决定)。

I2C 总线的相关术语定义如下表所示:I2C总线术语的定义表1SDA 和SCL 都是双向线路,都通过一个电流源或上拉电阻连接到正的电源电压。

当总线空闲时,这两条线路都是高电平。

连接到总线的器件输出级必须是漏极开路或集电极开路才能执行线与的功能。

计算机三级(PC技术)65_真题-无答案

计算机三级(PC技术)65(总分100,考试时间90分钟)选择题(每题1分,共60分)1. 在Windows 98操作系统典型安装时,用于存储鼠标的光标动画文件的文件夹是A. SystemB. CursorsC. ConfigD. Command2. 鼠标是一种输入设备,当用户移动鼠标时,向计算机中输入的信息是( )。

A. 鼠标移动的距离B. 鼠标移动的速度C. 鼠标到达位置处的X和Y坐标D. 鼠标在X和Y方向的位移量3. Windows98采用了集成的可管理的32位网络体系结构,满足了网络应用和通信的需要。

在下列有关Windows98网络与通信功能的叙述中,错误的是【】。

A. 两台PC机可以通过并口或串口直接用电缆连接,进行数据通信B. 安装了Windows98的多台PC机可以互联成网,组成对等网络C. 安装Windows98的PC机可以作为Microsoft网络的客户机D. 拨号网络适配器是指PC机中安装的网卡4. 数码相机是扫描仪之外的另一种重要的图像输入设备。

下面有关数码相机的叙述中,正确的是A. 拍摄图像的质量完全由CCD像素的多少决定B. 数码相机成像过程中要进行A/D转换C. 一台100万像素的数码相机可拍摄分辨率为1280×1024的图像D. 在分辨率相同的情况下,图像文件大小相同5. 关于主板ROM BIOS在计算机系统中的作用,下列说法不正确的是( )。

A. 能过主板BIOS可以完成对系统硬件基本参数的配置B. 操作系统能够运行,主板BIOS也起到了很重要的作用C. 可以通过主板BIOS的供的接口访问系统硬件,如硬盘、串口等D. 主板BIOS应用在旧式PC系统,在现代计算机系统中它已经没有任何作用了6. 下面是关于8259A可编程中断控制器的叙述,其中错误的是:A. 8259A具有将中断源按优先级排队的功能B. 8259A具有辨认中断源的功能C. 8259A具有向CPU提供中断向量的功能D. 一片8259A具有4根中断请求线7. 为了管理各种各样的设备,并使一些设备在不同的工作模式下能够正常工作,Windows 98支持多种类型的设备驱动程序。

并行数据转换为串行数据,总线输出

#(100*`clk_cycle) $stop;

end

always@(posedge ack)

begin

data<=data+1;

address<=address+1;

end

writing writing(.reset(reset),.clk(clk),.address(address),

end

bit0: begin

finish_F=1;

link_write<=0;

end

default:sh8out_state<=Idle2;

endcase

end

endtask

endmodule

测试模块

`timescale 1ns/1ns

`define clk_cycle 50

module writing_tb;

reg finish_F;//???????????

reg ack;

parameter[2:0] Idle1=3'b000,

addr_write=3'b001,

data_write=3'b010,

stop_ack=3'b011;

parameter[3:0] Idle2=4'b0000,

bit0=4'b0001,

end

addr_write: if(finish_F==0) //?????

begin shift8_out;end//???????

else

begin

sh8out_state<=Idle2;