CMOS抗辐射加固集成电路单粒子效应仿真研究进展

0.18μm CMOS器件SEL仿真和设计

0.18μm CMOS器件SEL仿真和设计李燕妃;吴建伟;谢儒彬;洪根深【摘要】宇宙空间存在大量高能粒子,这些粒子会导致空间系统中的CMOS集成电路发生单粒子闩锁.基于0.18 μm CMOS工艺,利用TCAD器件模拟仿真软件,开展CMOS反相器的单粒子闩锁效应研究.结合单粒子闩锁效应的触发机制,分析粒子入射位置、工作电压、工作温度、有源区距阱接触距离、NMOS和PMOS间距等因素对SEL敏感性的影响,并通过工艺加固得出最优的设计结构.重离子试验表明,采用3.2 μm外延工艺,可提高SRAM电路抗SEL能力,当L1、L2分别为0.86 μm 和0.28μrn时,其单粒子闩锁阈值高达99.75 MeV· cm2/mg.【期刊名称】《电子与封装》【年(卷),期】2017(017)002【总页数】5页(P43-47)【关键词】单粒子闩锁;TCAD;加固;重离子试验;外延工艺【作者】李燕妃;吴建伟;谢儒彬;洪根深【作者单位】中国电子科技集团公司第58研究所,江苏无锡214072;中国电子科技集团公司第58研究所,江苏无锡214072;中国电子科技集团公司第58研究所,江苏无锡214072;中国电子科技集团公司第58研究所,江苏无锡214072【正文语种】中文【中图分类】TN406在CMOS集成电路中,相邻的N型区和P型区之间存在两个寄生双极晶体管构成的PNPN可控硅结构(SCR,Silicon controlled rectifier),在空间辐射环境下,该结构被触发导通,在电源与地之间形成低阻抗大电流通路,导致电路无法正常工作甚至烧毁。

这种现象称为单粒子闩锁(SEL,Single Event Latch-up)[1~3]。

重离子导致的单粒子闩锁现象最早在1979年被发现[4],随后的研究表明,空间环境中的质子和中子也会导致单粒子闩锁[5~9]。

近年来越来越多的CMOS电路应用于航空航天领域。

纳米级CMOS集成电路的发展状况及辐射效应

纳米级CMOS集成电路的发展状况及辐射效应刘忠立【期刊名称】《太赫兹科学与电子信息学报》【年(卷),期】2016(014)006【摘要】介绍互补金属氧化物半导体(CMOS)集成电路的发展历程及纳米级CMOS集成电路的关键技术,在此基础上研究了纳米级CMOS集成电路的辐射效应及辐射加固现状.研究结果表明,纳米级FDSOICMOS集成电路无需特殊的加固措施,却比相同技术代的体硅CMOS集成电路有好得多的辐射加固能力,特别适用于空间应用环境.%The development of Complementary Metal Oxide Semiconductor(CMOS) integrated circuit and the key technologies of nanometer scale CMOS integrated circuit are introduced. Based on this, the radiation effects and the current status of radiation hardening for nano scale CMOS integrated circuit are studied. The research shows that the nano scale FDSOICMOS integrated circuit bears a better radiation hardening ability than the same technology generation of bulk silicon CMOS integrated circuit, and it is especially suitable for the application of space technology.【总页数】8页(P953-960)【作者】刘忠立【作者单位】中国科学院微电子研究所,北京 100029;中国科学院半导体研究所,北京 100083【正文语种】中文【中图分类】TN78【相关文献】1.抗辐射模拟CMOS集成电路研究与设计 [J], 赵源;徐立新;赵琦;金星2.体硅CMOS集成电路抗辐射加固设计技术 [J], 米丹;左玲玲3.亚微米CMOS集成电路抗总剂量辐射版图设计 [J], 李若飞;蒋明曦4.纳米级CMOS集成电路的单粒子效应及其加固技术 [J], 赵元富;王亮;岳素格;孙永姝;王丹;刘琳;刘家齐;王汉宁5.CMOS集成电路的抗辐射设计 [J], 张小平;雷天民;杨松;陈仁生因版权原因,仅展示原文概要,查看原文内容请购买。

CMOS APS光电器件单粒子效应脉冲激光模拟实验研究

CMOS APS光电器件单粒子效应脉冲激光模拟实验研究安恒;杨生胜;苗育君;薛玉雄;曹洲;张晨光【期刊名称】《真空与低温》【年(卷),期】2017(023)004【摘要】CMOS APS光电器件因低功耗、小体积的特点已成为遥感卫星成像的重要发展方向.随着半导体技术的不断进步,其单粒子效应已经成为一个影响可靠性的重要因素.针对CMOS APS光电器件,利用实验室脉冲激光模拟单粒子效应设备模拟了重离子在APS光电器件中引起的辐射损伤,分析了CMOS APS光电器件内部不同功能单元对单粒子效应的敏感性,获得了单粒子效应敏感参数.结果表明,CMOS APS光电器件在空间辐射环境中会诱发单粒子翻转和单粒子锁定.研究结果为进一步分析CMOS APS光电器件的抗辐射加固设计提供了理论支持.【总页数】3页(P223-225)【作者】安恒;杨生胜;苗育君;薛玉雄;曹洲;张晨光【作者单位】兰州空间技术物理研究所真空技术与物理重点实验室,兰州 730000;兰州空间技术物理研究所真空技术与物理重点实验室,兰州 730000;兰州空间技术物理研究所真空技术与物理重点实验室,兰州 730000;兰州空间技术物理研究所真空技术与物理重点实验室,兰州 730000;兰州空间技术物理研究所真空技术与物理重点实验室,兰州 730000;兰州空间技术物理研究所真空技术与物理重点实验室,兰州 730000【正文语种】中文【中图分类】V416.5;TN248【相关文献】1.CMOS SRAM器件单粒子锁定敏感区的脉冲激光定位试验研究 [J], 余永涛;封国强;陈睿;蔡明辉;上官士鹏;韩建伟2.商用FPGA器件的单粒子效应模拟实验研究 [J], 张宇宁;张小林;杨根庆;李华旺3.CMOS器件的单粒子效应及其加固 [J], 宋钦岐4.脉冲激光诱发130 nm体硅CMOS器件的单粒子闩锁效应 [J], 李赛;陈睿;韩建伟;上官士鹏;马英起5.CMOS器件单粒子效应电路级建模与仿真 [J], 丁李利;王坦;张凤祁;杨国庆;陈伟因版权原因,仅展示原文概要,查看原文内容请购买。

cmos存储单元电路抗单粒子翻转加固设计研究

cmos存储单元电路抗单粒子翻转加固设计研究CMOS(Complementary Metal-Oxide-Semiconductor)存储单元电路是现代数字电路和计算机系统中常用的一种存储器,其具有非常高的可靠性和稳定性。

然而,在大型集成电路当中,由于放射性粒子的存在,CMOS存储单元电路的单粒子翻转问题成为制约其可靠性的一个重要因素,尤其是在高海拔、太空航行等极端条件下,更容易受到放射性影响。

因此,在CMOS存储单元电路的设计中,抗单粒子翻转加固成为一个热点问题。

本文旨在研究CMOS存储单元电路的抗单粒子翻转加固设计,提出一些有效的方法和措施,从而提高其可靠性和稳定性。

一、单粒子翻转的原因和机制在CMOS存储单元电路中,单粒子翻转通常是由放射性粒子的撞击所引起。

这些粒子通常不会引起电路的明显损坏,但却可以导致单粒子翻转,使电路的状态改变。

这种现象被称为单粒子效应(Single-Event Effect,SEE)。

粒子撞击后会在电路中留下能感应电荷的电离空穴和自由电子,电离空穴和自由电子交互后就可以形成一对电子空穴对,两者之间存在电场,因此可以在电场的作用下迁移,直到撞击到电路的导体结构,从而改变电路的状态。

常见的单粒子翻转现象包括单粒子失效(SEU)、单粒子翻转(SET)和单粒子中断(SEB)等。

二、抗单粒子翻转加固设计方法为了抵御单粒子翻转现象对CMOS存储单元电路的影响,可以采取以下的抗单粒子翻转加固设计方法:1. 采用抗放射性材料一些抗放射性的材料可以在电路中使用,例如氧化铌(Nb2O5)、聚酰亚胺(PI)等。

这些材料具有高的抗放射性和抗温度变化特性,可以在电路中起到抵御放射性粒子的效果。

2. 采用补偿电路技术补偿电路技术是减少单粒子翻转的有效方法之一。

通过采用主动补偿和被动补偿等方法,可以减少电路中发生单粒子翻转的可能性,提高电路的可靠性和稳定性。

3. 采用多重冗余技术通过采用多重冗余技术,可以提高电路的容错性能,减少单粒子翻转对电路的影响。

CMOS存储单元电路抗单粒子翻转加固设计研究

CMOS存储单元电路抗单粒子翻转加固设计研究空间环境中存在着数量庞大的辐射粒子,这些粒子轰击到空间应用的集成电路系统上时,会使电路发生单粒子翻转、单粒子闩锁、单粒子烧毁等诸多辐射效应。

这些单粒子辐射效应将导致系统偏离正常功能,甚至整个芯片系统的失效。

作为储存大量数据的载体和电子系统不可缺少的一部分,存储电路在辐射环境中的单粒子翻转错误已成为危害芯片系统稳定性的重要因素,欧空局就曾经报道过单粒子翻转软错误所引发的卫星坠落事件,可见对存储电路进行抗单粒子翻转加固设计研究是十分必要的。

设计加固(Radiation Hardened by Design,RHBD)因其可以兼容现有标准商用CMOS工艺、节约制造芯片所需的成本,在抗辐射加固领域得到了设计人员的广泛应用。

本文采用RHBD方法对存储电路中的SRAM存储单元,锁存器和D触发器进行了加固设计研究,内容主要包括以下几个方面:(1)SRAM存储单元抗单粒子多节点翻转加固设计研究。

作为占据芯片面积较大的内部存储模块,静态随机存取存储器在辐射环境中的抗单粒子翻转性能直接关系到整个电路系统的可靠性。

本文首先基于设计冗余加固技术在电路级提出了一种抗辐射加固12管SRAM 存储单元结构;之后,根据该电路的构造特点,针对特定的存储节点,在版图级进行了进一步的加固设计。

结果表明,在电路级加固和版图级加固的联合作用下,辐射粒子无论以垂直入射,还是角度入射的形式轰击本文所提出的SRAM存储单元,它都能够完全抵抗由电荷收集及电荷共享所引起的单粒子多节点翻转。

(2)锁存器抗单粒子翻转加固设计研究。

作为时序电路的最小存储单元,锁存器电路在辐射环境下的抗单粒子翻转性能将直接关系到系统处理数据的正确性。

本文利用设计冗余加固技术,通过合理的结构设计,提出了一种低功耗抗单粒子翻转加固锁存器电路结构,并且通过对内部部分电路在高电平时钟周期和低电平时钟周期的复用设计,实现了在数据传输阶段滤除输入单粒子瞬态脉冲以及在保持阶段避免输出节点因内部节点发生单粒子翻转效应而进入高阻状态的设计目的。

CMOS集成电路电荷共享单粒子翻转分析及加固

CMOS集成电路电荷共享单粒子翻转分析及加固我国航天科技近年来取得了飞速的发展,对航天器中所采用的先进集成电路辐射加固技术的研究也迫在眉睫。

随着抗辐射集成电路迈入纳米尺度,集成电路芯片上的晶体管数量越来越多、时钟频率越来越高、工作电压和节点电容的减小,软错误成为航天器中集成电路失效的主要原因,电荷共享对单粒子翻转的研究提出了新挑战。

在纳米技术中,器件的尺寸和间距的减少使得单一的重离子轨迹能够同时覆盖多个器件,从而导致多个器件同时收集电荷。

电荷共享效应导致的多节点电荷收集现象,使得纳米集成电路面临着更为复杂的电路响应以及更为严峻的可靠性问题。

因此,如何在纳米集成电路下对电荷共享的影响机理以及试验表征进行研究,已成为目前集成电路辐照效应研究领域的重点问题。

另一方面,更严重的电荷共享会导致单一节点的加固方法失效,从而抑制电荷共享效应已成为一个重要的措施,以避免集成电路软错误。

如何提出有效的加固技术来缓解电荷共享的影响也成为一个热点问题。

此外,版图布局结构、外界粒子、掺杂工艺、电源电压、体偏置等因素会也随着实际应用环境的变化而变化,这将极大地影响集成电路的电荷共享和可靠性。

因此,深入研究电荷共享对纳米集成电路软错误的影响情况,有助于解决集成电路辐照领域面临的重要研究问题,对于纳米抗辐照加固集成电路设计也具有重要指导意义。

本文针对纳米互补金属氧化物半导体(CMOS)工艺,对电荷共享效应的理论、测量以及加固技术进行了深入讨论,主要研究成果如下:提出了一种利用交叉互锁存储单元(DICE)来测量电荷共享影响范围的测试结构,这种测试结构充分利用了DICE锁存器的工作原理以及敏感节点对同时收集电荷的特性,利用3D计算机辅助工艺设计(TCAD)模拟证实了这种测试结构的合理性。

并且通过设计纳米工艺下的测试芯片,在重离子辐照条件下进行试验测量,试验和模拟结果具有较好的一致性,充分证实了这种方法的有效性。

基于电荷共享范围的测量结果,深入分析了电荷共享对触发器单元单粒子翻转的影响。

单粒子仿真方法研究

单粒子仿真方法研究李若飞;胡长清【摘要】在宇航级器件的设计过程中,主要考虑单粒子效应和总剂量效应.随着工艺尺寸的不断缩小,总剂量效应变得越来越不明显,而单粒子效应变得越来越显著.对于CMOS电路,单粒子效应主要包括单粒子锁定和单粒子翻转,防止单粒子锁定的方法非常成熟,单粒子翻转效应的研究是现今抗辐照研究的主流.评估单粒子效应的方法主要是实验方式,实验评估单粒子效应虽然准确,但是机时少,费用高,实验周期长,给项目研制过程造成很大障碍,因此非常有必要开展单粒子仿真技术研究.提出一种以Hspice电路网表为基础的单粒子效应评估方法,此方法采用脉冲电流模拟单粒子产生的效果,通过此方法可以有效模拟单粒子现象,并找到电路的设计敏感点,有效指导设计.%In the design process of aerospace-grade devices, the main consideration is SEE and TID.As the process dimension is decreased continuously, total dose effect is getting more unobvious, but single event effect becomes more serious. For CMOS circuit, single event effect (SEE) includes Single Event Latchup(SEL) and Single Event Upset(SEU). The method of avoiding SEL is mature, so SEU is the key point in anti-radiation study. Now, the experiments are mainly used for SEU evaluation, which are accurate but have less machine time and more cost, so it is necessary to carry out single event effect simulation technology. The evaluation method for single event effect, based on Hspicenetlist, employing the effect generated by pulse current simulating SEE, is proposed in this paper, which is effective and can guide design.【期刊名称】《微处理机》【年(卷),期】2017(038)003【总页数】5页(P8-12)【关键词】抗辐照;单粒子翻转;单粒子闭锁;比较器;仿真;冲击能量;单粒子效应【作者】李若飞;胡长清【作者单位】中国电子科技集团公司第四十七研究所,沈阳 110032;中国电子科技集团公司第四十七研究所,沈阳 110032【正文语种】中文【中图分类】TN495运行在宇宙空间中的各类人造卫星、空间探测器等航天器的微电子器件都会受到来自空间的宇宙射线以及频谱范围较宽的电磁辐射影响,并产生不同程度的损伤。

纳米级CMOS集成电路的单粒子效应及其加固技术

应和加固技术方面的研究成果,包括首次提出的单粒子时域测试和分析方法、单粒子多节点翻转加固方法和单粒子瞬

态加固方法等.

关键词: 集成电路;纳米级;单粒子效应;抗辐射加固

中图分类号: TN43 文献标识码: A 文章编号: 03722112(2018)10251108

电子学报 URL:http://www.ejournal.org.cn

收稿日期:20161219;修回日期:20170909;责任编辑:梅志强 基金项目:国家自然科学基金(No.61674015,No.11690045)

2512

电 子 学 报

2018年

对芯片成本、性能 的 追 求,不 断 地 推 动 着 集 成 电 路 技术的进步,在同一 芯 片 上 集 成 的 电 路 密 度 不 断 提 高, 电路性能不 断 改 善,这 一 发 展 几 乎 始 终 遵 循 “摩 尔 定 律”的规律[2].当前,先进集成电路几乎全部采用 100nm 以下工艺实现,部分高端集成电路已采用 16nm或 14nm 工艺实现,集成电路技术已经全面进入纳米时代.然而, 随着集成电 路 特 征 尺 寸 缩 小 至 纳 米 尺 度,很 多 器 件 物 理问题和新 的 辐 射 效 应 问 题 随 之 出 现.相 比 于 超 深 亚 微米工艺,纳米级 工 艺 在 器 件 材 料、结 构、尺 寸、工 作 电 压上都发生 了 明 显 的 变 化,其 中 一 些 变 化 将 严 重 影 响 纳米级器件 和 集 成 电 路 的 抗 辐 射 性 能,给 纳 米 级 集 成 电路的 抗 辐 射 加 固 带 来 了 许 多 新 挑 战.主 要 的 问 题 包括:

DOI:10.3969/j.issn.03722112.2018.10.027

一种抗单粒子效应的加固技术研究

一种抗单粒子效应的加固技术研究近年来,单粒子效应越来越成为半导体器件可靠性的重要问题。

单粒子效应主要是指电路器件受到单个粒子的影响而出现的瞬间失效或性能下降现象。

这种效应往往会导致芯片的不可靠性和寿命缩短,极大地影响芯片的应用效果。

因此,抗单粒子效应成为近年来半导体器件可靠性研究的热点问题。

目前,抗单粒子效应的加固技术主要包括提高芯片工艺、优化器件结构和增强电路设计等方面。

本文将分别就这几个方向展开探讨,并提出一些具体的解决方案。

一、提高芯片工艺芯片工艺是影响器件可靠性的重要因素,芯片工艺的精度和稳定性直接关系到器件的可靠性。

在抗单粒子效应的研究中,通过优化芯片工艺来降低器件对单粒子的敏感度被认为是一种有效的方式。

首先,提高成品芯片的掺杂剂浓度可以增加器件的电子束容忍量,以提高芯片的抗单粒子效应能力。

在通量密度高的环境下,掺杂芯片的核激发截面将会增加,从而提高器件的单粒子抗性能。

其次,对于SRAM 类器件,双极性静电保护器件的引入可有效减少器件的抗单粒子效应。

通过控制较小的电流和电压,可将芯片设定为两个不同的状态,从而实现器件的抗单粒子功能。

此外,采用栅极极薄化技术也是提高芯片抗单粒子能力的一种有效手段。

通过将栅极厚度减薄,可将器件对单粒子的敏感度降至最小,并且通过锁定栅电压,可以使SRAM 类器件增加抗剧烈电场和射线影响的能力。

二、优化器件结构优化器件结构是实现抗单粒子效应的另一种有效途径,通过处理硅晶体的晶体结构和引入高介电常数的氧化物等方法,可提高器件的抗单粒子能力。

首先,氧化层厚度必须得到控制以降低外部辐射所带来的影响。

优化氧化层可以增强MOSFET 结构的抗剧烈电场和射线能力。

此外,在硅片的表面形成均匀的氧层也是十分重要的,因为深学层之间的差异会导致器件的电荷堆积增加,引起器件的单粒子敏感性增加。

其次,采用具有极小反向电容的技术和氮化硅层技术也可以增加芯片的抗单粒子能力。

通过将金属引线间距等放大,可以使器件的单电子抗性增强,从而提高器件的抗单粒子能力。

CMOS集成电路总剂量效应加固技术研究现状

CMOS集成电路总剂量效应加固技术研究现状

梁泽宇;庞洪超;李兴隆;骆志平

【期刊名称】《核科学与技术》

【年(卷),期】2024(12)2

【摘要】在核设施运行、乏燃料后处理、可控核聚变、航天卫星与太空探索、核军工、γ辐照站等存在强辐射的场景下,高能粒子、射线会与器件中的半导体材料相互作用产生辐射效应,对信号的完整性和精度产生较大影响。

本文首先介绍了总剂量效应(TID)的作用机制,及其在MOS器件中的主要影响:总剂量效应会导致MOS管阈值电压漂移、跨导下降、载流子迁移率降低和电流额外泄漏等问题。

其次,按照时间顺序依次阐述了近代以来总剂量效应在半导体器件特别是是CMOS器件中的具体影响,尤其对浅槽隔离氧化物(Shallow Trench Isolation, STI)受到总剂量效应的影响做了着重描述。

最后,分析了在电路级中的总剂量效应,以及目前流行的几种抗辐射加固技术。

【总页数】11页(P118-128)

【作者】梁泽宇;庞洪超;李兴隆;骆志平

【作者单位】中国原子能科学研究院核安全与环境工程技术研究所

【正文语种】中文

【中图分类】TN3

【相关文献】

1.CMOS电路总剂量效应最劣偏置甄别

2.现代工艺集成电路的总剂量效应及加固技术

3.浅谈集成电路的总剂量效应及SOI工艺加固技术的应用

4.总剂量效应对CMOS读出电路影响及设计加固方法研究

5.星敏感器用4T像素CMOS图像传感器总剂量效应研究

因版权原因,仅展示原文概要,查看原文内容请购买。

碳基cmos辐照损伤机理及耐辐照加固方法研究

碳基cmos辐照损伤机理及耐辐照加固方法研究

随着集成电路技术的不断发展,半导体器件的辐射环境越来越严峻,辐照能量也日趋

复杂。

因此,对于半导体器件的辐照损伤机理和耐辐照加固方法的研究成为了当前的热点

问题。

本文主要介绍了碳基CMOS器件的辐照损伤机理及其耐辐照加固方法的研究。

碳基CMOS器件是一种新型的半导体器件,由于其较高的性能、低功耗、高可靠性以及抗辐射等特点,而成为一种被广泛关注的器件。

然而,由于碳基CMOS器件的结构和材料的特殊性质,也存在着许多与传统CMOS器件不同的辐照损伤机理和加固方法。

碳基CMOS器件的辐照损伤机理主要有以下几点:一是由于碳基材料的结构与硅基材料不同,碳基CMOS器件在受到辐照后,结构会发生改变,从而导致电学性能下降。

二是由于碳基材料的漂移效应较小,当碳基CMOS器件受到辐照后,漏电流和阈值电压等特性指标的变化也较小。

三是由于碳基材料的晶体结构比较紧密,因此碳基CMOS器件的抗单粒子效应能力较高。

为了解决碳基CMOS器件的辐照损伤问题,目前研究人员主要采用以下耐辐照加固方法:一是采用工艺优化方法,如局部氟离子注入、渗硼等方法,以提高器件的耐辐照能力。

二

是采用结构优化方法,如引入硅材料加固结构等。

三是采用器件级别加固方法,如采用多

个独立的电路单元相互作用的叠片技术等。

纳米CMOS电路在单粒子效应下可靠性分析

纳米CMOS电路在单粒子效应下可靠性分析作者:赵智超吴铁峰来源:《电脑知识与技术》2016年第21期摘要:随着电子元器件的尺寸在不断的发生变化,使得电容和电压不断的降低,纳米CMOS电路对单粒子效应(SEE)的敏感性更高,并且由于单粒子的串扰和多结点翻转现象明显增加,使得工作的可靠性受到一定的影响。

为了更好的保证纳米CMOS电路在SEE下的可靠性,从多方面来对其进行分析和研究,最后通过研究发现,影响纳米CMOS电路在SEE下的可靠性的焦点可能是:抗单粒子瞬态的加固研究、CMOS电路的抗辐射加固设计研究、仿真及加固研究等。

关键词:纳米CMOS电路;单粒子效应;可靠性中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)21-0261-02随着科学技术的不断发展,各种电子元器件和技术也在进行着不断的改进。

航天和航空领域逐渐的使用微处理器和混频器等电子元器件,其需要受到环境严厉的考验。

对国内外的数据进行分析统计,在空间环境中发生航天器故障中,单粒子诱发发生故障率高达28.5%,所以来讲,SEE对集成电路的可靠性有着严重的危害。

从基本电力损伤原理、可靠性评价、单粒子对电路的影响等多方面来对纳米CMOS电路在SEE下的可靠性的研究进行阐述,提出了在研究中所面临的问题。

1 对单粒子效应对电路产生的影响进行分析研究软错误率(soft error rate, SER)是指SEE对电路所产生的一系列的影响,其中软错误率数值越低,则单粒子效应对集成电路的影响就越小,呈正比关系;反之,软错误率数值越高,则单粒子效应对集成电路的影响越严重。

因此,SER数值的大小就成为了衡量SEE对集成电路影响程度的一种关键性方式。

SER是元器件尺寸和临界电荷的函数,并且SER数值不会根据电子元器件尺寸的大小而发生改变。

其次,单个高能粒子的存在,使得存储器的数据改变,并且会对微纳电子电路产生致命的伤害,所以需要建立出计算SER数值的模型,即建立一个软错误率数值评估模型。

1.CMOS工艺集成电路抗辐射加固设计研究

1.CMOS工艺集成电路抗辐射加固设计研究复旦大学硕士学位论文CMOS工艺集成电路抗辐射加固设计研究姓名:沈鸣杰申请学位级别:硕士专业:微电子学与固体电子学指导教师:俞军20060510摘要摘要辐射环境可以分为自然辐射环境和人为辐射环境。

自然辐射环境主要指外太空的环境,人为辐射环境主要指核爆炸后的环境。

随着越来越多的集成电路需要在辐射环境中工作,比如:卫星中的集成电路、武器系统中的集成电路,用户需要对集成电路的抗辐射能力提出要求。

所以,如何设计抗辐射的集成电路成为一个迫切需要解决的问题。

一般来说,对集成电路进行抗辐射加固的方法可以分为两类:从工艺上进行加固和从设计上进行加固。

因为目前主流的集成电路设计流程是设计公司负责集成电路的设计(包括前端设计、后端设计),通用工艺线负责集成电路的生产。

所以作为设计公司是无法通过改变工艺的方法来获得辐射加固的集成电路,因此通过设计的方法来加固集成电路的抗辐射能力,是比较可行的方案。

而且通过工艺线来加固,目前还有它自身的缺点,在论文中会有介绍。

本文在分析辐射对集成电路的各种效应、以及辐射效应的产生机制的基础上,分析了各种在设计上可以使用的辐射加固技术,最后设计了一个辐射加固的单元库。

本论文的主要工作包括:1.了解空间辐射环境。

2.理解辐射对集成电路产生的各种效应。

3.理解集成电路的辐射效应的产生机制。

4.设计一个抗辐射的单元库。

在开展上述工作的同时,本文进行了积极的研究和探索,取得了一定的创新,可概括如下:1.对单粒子瞬变的加固,不是从加固组合电路的角度来考虑。

而是提出使用抗单粒子瞬变的触发器来解决这个问题。

这样,我们可以只对集成电路中的时序器件和存储器进行辐射加固,可以不考虑组合电路的辐射问题。

如此,把一个复杂问题简单化。

2.提出使用多位移位寄存器电路来考察触发器的单粒子效应。

3.对已有的抗辐射D触发器进行改进,从而获得更加优越的性能。

本文抗单粒子的电路均给出了仿真结果。

CMOS抗总剂量辐照原理及先进加固器件

CMOS抗总剂量辐照原理及先进加固器件【摘要】随着半导体产业的进步以及空间技术和核工程的快速发展,越老越多的CMOS集成电路被应用于辐照环境当中。

因此CMOS电路面临着更加严峻的挑战。

为了保证CMOS集成电路在严苛条件下的性能表现以及可靠性,抗辐照加固技术应运而生。

本文从抗辐照加固的基本原理出发,分析了辐照失效的机理以及几种不同的失效模式,并简单介绍了几种不同的抗辐照加固结构。

关键词CMOS电路; 总剂量辐照加固;1 辐照失效机理集成电路在辐照环境下的机理大致有以下几种形式:⑴单粒子效应⑵总剂量效应⑶中子辐射效应⑷瞬时辐射效应⑸剂量增强效应⑹低计量率效应。

其中,导致器件失效的影响较大的辐射效应为总剂量效应(TID,Total Ionizing Dose)和单粒子效应(SEE,Single Event Effects)[1]。

下文将具体介绍这两种辐照效应的产生方式及其对电路单元的影响。

1.1 总剂量效应(TID)总剂量效应是当集成电路元器件长期处于辐射环境中时,多次粒子入射将会造成正电荷积累,从而引起器件性能发生退化甚至失效。

当航天器和武器型号中所使用的电子元器件工作在电离总剂量辐射环境中时,会遭遇高能粒子及光子的轰击,其工作参数及使用寿命不可避免地会受到影响和危害,严重时可引起航天系统失效,甚至导致不可想象的航天事故。

电离总剂量辐射对半导体元器件的影响主要体现在隔离二氧化硅层中,如:MOS结构的栅氧化物、隔离氧化物和SOI器件的BOX埋氧层等等。

辐射产生的电子会在几皮秒的时间内被扫出氧化层并被栅电极收集,而空穴会在栅极电场的作用下向Si/SiO2界面处缓慢运动。

然而,有些电子还没有来得及被扫出电场就已经又和空穴复合了。

没有发生复合反应的那部分电子空穴对被称为净电荷量。

没有被复合的空穴会在氧化层中以局域态的形式向界面处做阶跃运动。

当空穴运动到界面附近时,一部分会被界面处的空穴陷阱俘获,形成带正电的氧化物陷阱电荷。

9.CMOS集成电路抗辐射加固工艺技术研究.

哈尔滨理工大学硕士学位论文CMOS集成电路抗辐射加固工艺技术研究姓名:刘庆川申请学位级别:硕士专业:仪器仪表工程指导教师:于晓洋;苏秀娣 20070101哈尔滨理工大学工程硕士学位论文CMOS集成电路抗辐射加固工艺技术研究摘要随着现代科学技术的发展,具有高速信号处理能力和强的抗辐射能力的计算机及控制部件已成为通信卫星、气象卫星、航天飞行器、现代武器等系统的核心部分。

因此,发展具有高速度、强抗辐照能力的集成电路技术是电子信息产业和国防装备系统的关键。

当前,在集成电路芯片制造中,体硅CMOS半导体工艺技术仍占据主导地位,因此,对CMOS集成电路进行加固研究就显得十分必要.由于抗辐照加固技术属于军用技术范畴。

它具有高度的保密性,因此抗辐照加固工艺必须依靠自己的力量,从基础工艺出发进行研究。

用在空间中的电路会受到各种射线的影响,要产生电离辐照效应和单粒子效应等。

本文第一部分主要讲述了CMOS电路的电离辐射效应主要介绍了界面态的产生,并详细分析了辐射感生陷阱电荷的产生过程。

并根据上述原理指导下确定了工艺、设计两方面的抗辐照加固方法,分别介绍了栅氧化层加固,源漏制备技术加固,钝化层加固,场区加固,以及栅氧后高温的影响。

第二部分主要讲述了CMOS集成电路的单粒子效应。

主要介绍了单粒子效应的模型,包括电荷聚集模型、粒子分流模型和电荷横向迁移模型;并介绍了不同的高能粒子的单粒子损伤机理;着重描述了CMOS集成电路的单粒子效应.并且根据上述的损伤机理,从设计和工艺方面提出了抗单粒子效应的方法。

最后根据上面得出的可行的方法研制了抗辐射加固电路CPU,并取得了较好的抗电离辐射和抗单粒子效应的效果。

关键词 CMOS集成电路:电离辐射效应;单粒子效应堕垒堡矍三查兰二堡璺圭兰堡鲨圣Research of CMOS Integrated Circuit Radiation Hardened ProcessAbstractWith the development of modem science technology,the computers and control parts with the ability of handle high—speed signal and strong radiation resistant have become the COre of communication satellite,weather satellite, aircraft and modem weapon ctc.So that,the key of electronics information industry and national defense is to develop high・speed strong radiation resistant integrated circuit technology.At present,in the manufacturing of IC slice,body-silicon CMOS process technology still occupy predominate position.so it is necessary to harden research CMOS IC.Because the Radiation Resistant and Hardened Technology (RRHTbelong to the military technology,it is a secret.So we must study RRHT by ourselves based on basic techniques.The circuits used for space technology,will be affected by various rays,c柚 generate ionizing radiation effect and single-event effect.It is mainly tellsionizing radiation effect and radiation resistant technology on CMOS circuit in the first part,include boundary surface state and induced trap charge of radiation;separately introduce gate oxidation layer hardness,source/drain hardness, passivation layer hardness,field areas hardness and the influence of hi讪 temperature after gate oxidation.The second part mainly tells single event effect.The single event effect model is first tells include charge collect model,particle diffluence model and charge’S transverse transfer model.Then damage effect is tells that cawed by high energy particles.Then it is describesthat the single event effect of CMOS IC.Then it is tells that the way of how to protect CMOS circuit using methods of design and process.・¨・哈尔滨理丁人学T程硕I‘学位论文The last it is also introduce development of radiation hardened IC 80C86 CPU.The anti-ionizing・radiation-effect and anti—single・event-effect achieve good result.Keywords CMOS IC;Ionizing radiation effect;Single event effect-儿l-哈尔滨理工大学工程硕|:学位论文第1章绪论1.1课题背景及研究的目的和意义随着现代科学技术的发展,具有高速信号处理能力和强抗辐射能力的计算机及控制部件已成为通信卫星、气象卫星、航天飞行器、现代武器等系统的核心部分。

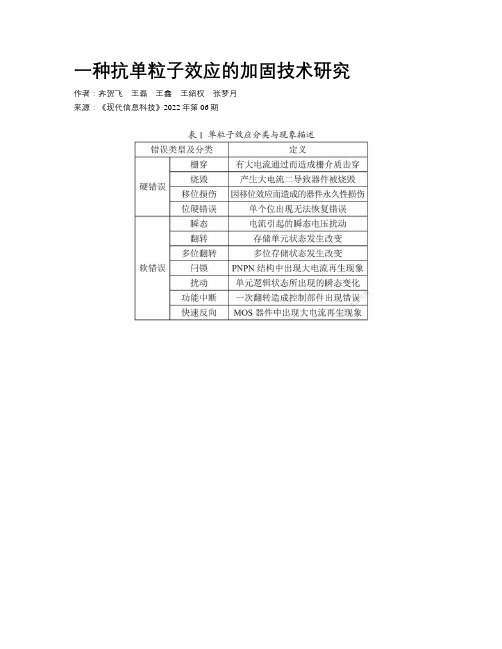

一种抗单粒子效应的加固技术研究

一种抗单粒子效应的加固技术研究作者:齐贺飞王磊王鑫王绍权张梦月来源:《现代信息科技》2022年第06期摘要:针对数字波控电路在星载控制电路应用中存在的单粒子翻转效应问题,提出了一种基于DICE单元的双稳态D触发器设计改进,设计了一种能够抵御众多类型单粒子翻转效应的D触发器,并基于该D触发器,结合电路级单粒子加固技术设计了一款串并转换芯片。

测试表明,采用改进D触发器结构的波控芯片能够抵御至少80 MeV的单粒子效应事件。

芯片峰值功耗不大于10 mA,写入速率不低于10 MHz,功耗为1 mW/MHz。

关键词:单粒子效应;抗辐照;三模冗余中图分类号:TN79 文献标识码:A文章编号:2096-4706(2022)06-0041-05Research on a Strengthening Technique against Single Event EffectQI Hefei, WANG Lei, WANG Xin, WANG Shaoquan, ZHANG Mengyue(The 13th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050051, China)Abstract: In view of the problem of single particle flip effect, which exits in the digital wave control circuit in load control circuit application, this paper puts forward a bistable D trigger design improvement based on DICE unit, designs a D trigger which can resist many types of single particle flip effect. And based on the D trigger, combined with circuit level single particle reinforcementtechnology, it designs a string and conversion chip. Tests show that a wave-control chip with an improved D-trigger structure can resist the Single Event Effect events of 80 MeV at least. The peak power consumption of the chip is not more than 10 mA, the write rate is not less than 10 MHz, and the power consumption is 1 mW/MHz.Keywords: Single Event Effect (SEE); Radiation resistance; Triple Modular Redundancy0 引言地球周围存在着大量的高能粒子射线,主要分为三大类高能粒子辐射源:银河宇宙射线、太阳宇宙射线以及地球辐射带。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

矿产资源开发利用方案编写内容要求及审查大纲

矿产资源开发利用方案编写内容要求及《矿产资源开发利用方案》审查大纲一、概述

㈠矿区位置、隶属关系和企业性质。

如为改扩建矿山, 应说明矿山现状、

特点及存在的主要问题。

㈡编制依据

(1简述项目前期工作进展情况及与有关方面对项目的意向性协议情况。

(2 列出开发利用方案编制所依据的主要基础性资料的名称。

如经储量管理部门认定的矿区地质勘探报告、选矿试验报告、加工利用试验报告、工程地质初评资料、矿区水文资料和供水资料等。

对改、扩建矿山应有生产实际资料, 如矿山总平面现状图、矿床开拓系统图、采场现状图和主要采选设备清单等。

二、矿产品需求现状和预测

㈠该矿产在国内需求情况和市场供应情况

1、矿产品现状及加工利用趋向。

2、国内近、远期的需求量及主要销向预测。

㈡产品价格分析

1、国内矿产品价格现状。

2、矿产品价格稳定性及变化趋势。

三、矿产资源概况

㈠矿区总体概况

1、矿区总体规划情况。

2、矿区矿产资源概况。

3、该设计与矿区总体开发的关系。

㈡该设计项目的资源概况

1、矿床地质及构造特征。

2、矿床开采技术条件及水文地质条件。