微机原理与接口技术(清华大学课件,全套)

合集下载

微机原理与接口技术PPT课件

(2)如果要对其他段寄存器所指出的存储区 进行直接寻址,则本条指令前必须用前缀指出 段寄存器名。

21018H 21019H

AA 数 BB 据

段

8

三、直接寻址

• 操作数的存储区是在DS段以外的段中,则应 在指令中指定段跨越前缀:

• MOV BX, ES:[2000H] 设ES=3000H,则指令执行后是将32000H

• 操作数的寻址方式有以下几种:

•

立即数寻址

寄存器寻址

直接寻址

寄存器间接寻址

寄存器相对寻址

基址加变址寻址

相对的基址加变址寻址

• 例:指令形式:

MOV AX, 0000H; AX← 0000H

助记符 目的操作数 源操作数

4

一、立即数寻址

• 操作数紧跟在操作码的后面,与操作码一起放在码段

区域,立即数可以为8位,也可以为16位。

设SS=3000H,BP=2000H, COUNT=1050H

有效地址为: EA=2000H+1050H=3050H

物理地址: 堆栈段=30000H+3050H=33050H

存储器

M

10000H 8B 代

10001H 86 码

10002H

段

AH AL BB AA

33050H 33051H

AA 堆 BB 栈

代码:8B 07

设 DS=2000H,BX=5000H CS=1000H,IP=0000H

物理地址: 代码段:CS000H 8B 代

10001H 07 码

10002H

段

数据段:DS ×16+BX=25000H

AH AL

BB AA

25000H 25001H

第2微机原理与接口技术清华大学-PPT精品

编写相应的程序段。

2020/5/17

18

源程序代码:

LEA SI,DATA

MOV DX,3F8H WATT:IN AL,DX

ATJAZENNSWDDTATAAATLLL,,,0222AHAHH CTJXZEMOSWPRTAAATALTLL,,,0282HAAHH JTJNENSZZT WAWLA,ATT2TT0H

更长字长数的移位。

2020/5/17

30

MOV SI,1000H

MOV DI,3000H MOV CX,4 BBB:MOV AL,[SI] MOV BL,AL AND AL,0FH OR AL,30H MOV [DI],AL INC DI MOV AL,BL

2020/5/17

程序例

PUSH CX MOV CL,4 SHR AL,CL OR AL,30H MOV [DI],AL INC DI INC SI POP CX DEC CX JNZ BBB HLT

2020/5/17

21

算术左移和逻辑左移

• 算术左移指令: SAL OPRD,1 SAL OPRD,CL

有符号数

• 逻辑左移指令: SHL OPRD,1

无符号数

SHL OPRD,CL

移动一位后,若CF与最高不相等,则OF=1;否则OF=0

2020/5/17

22

逻辑右移

• 格式: SHR OPRD,I

CF

0

CF

0

CF

0

24

算术右移

• 格式: SAR OPRD,I SAR OPRD,CL

有符号数 的右移

CF

2020/5/17

25

非循环移位指令的应用

• 左移可实现乘法运算 • 右移可实现除法运算

《微机原理与接口技术》教学课件 第6章

6.2 随机存取存储器

2 动态RAM 2164的工作过程

① 将要读出单元的行地 址送到地址线A0~A7上, RAS 信号有效时,在下 降沿将地址锁存在行地 址锁存器中。

② 将要读出单元的列地 址 送 到 地 址 线 A0 ~ A7 上 , CAS 信号有效时,在下降 沿将地址锁存在列地址 锁存器中。

目录 CONTENTS

存储器入门 随机存取存储器

只读存储器 高速缓冲存储器

外部存储器

3

引子

计算机之所以能自动、连续地工作,是因为采用了存储程序的原理。计算机中的所有程序和数 据都存放在存储器中,存储器是计算机必不可少的组成部件之一。存储器的性能对整个计算机 系统的性能起着至关重要的作用。本章主要介绍存储器的分类、结构和主要性能指标,并通过 典型的存储器芯片来介绍存储器的工作原理及与CPU的连接方法。

6.1 存储器入门

连续两次读写操作之间所需的最短时间间隔称为存储周期。存储器每秒钟可读写的 数据量称为存储器带宽或数据传输速率,单位为bps(或bit/s)。存取周期和存储器带宽 也常作为存储器的性能指标。

提示

6.2 随机存取存储器

随机存取存储器(Random Access Memory,RAM)也称随机读/写存储器或随机存储器,它既可以直接 从任何一个指定的存储单元中读出数据,也可以将数据写入任何一个指定的存储单元中。

6.1.2 存储器的性能指标

存储器容量:存储器中所包含存储单元的总数,单位是字节(B)。存储 器容量越大,存储的信息越多,计算机的性能也就越强。

01

02

存取时间:存储器完成一次读写操作所需的时间,单位为ns(纳秒,

1 ns=10-9 sБайду номын сангаас。

微机原理及接口技术参考PPT

IN AL,DX

;读数据

MOV [SI],AL

MOV DX,8002H

MOV AL,00H

OUT DX,AL

INC SI ;存放数据的内存地址加1

INC BL ;通道地址加1

MOV AL,BL OUT DX,AL ;送通道地址 MOV DX,8002H

DEC BH JNZ GOON POP AX

MOV AL,01H

•14

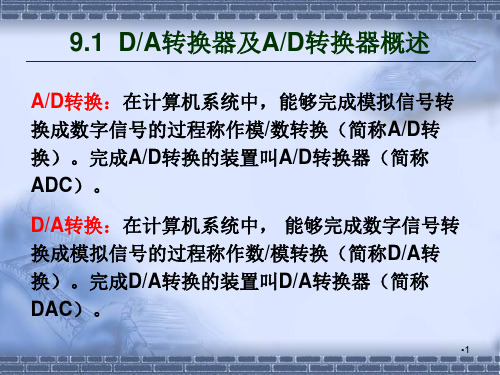

9.3 A/D转换器ADC0809及应用

➢ 采样:对连续变化的模拟量要按一定的规律和周期取出其 中的某一瞬时值。

➢ 采样频率:一般要高于或至少等于输入信号最高频率的2 倍,实际应用中采样频率一般是信号频率的4~8倍。

➢ 采样周期:相邻两次采样的间隔时间。一次A/D转换所需 要的时间必须小于采样周期。

•10

➢ 应用举例:利用D/A 转换器来构造波形发生器,如图所 示。假设地址译码输出端口为360H。

图9.8 采用DAC0832 构造的波形发生器

•11

(1) 矩形波。给DAC0832 持续256 次送数据0,然后256 次送 数据FFH,依次重复处理。输出矩形波的程序段如下:

MOV DX,360H ;设定地址译码输出端口 DD0: MOV CX,0FFH

2

多2

N位

路

电

二进制数

… …

模

阻

拟

网

开

络

N

关N

运算 放大器

图9.2 D/A转换器框图

模拟电压输出

•3

1. 加权电阻网络D/A转换器的工作原理

VREF

K1

R1

K2

R2

K3

R3

Kn

Rn

微机原理与接口技术

精品课程微机原理多媒体课件

例:

234.98D或(234.98)D 1101.11B或(1101.11)B ABCD . BFH或(ABCD . BF) H

精品课程微机原理多媒体课件

二、各种进制数间的转换

1. 非十进制数到十进制数的转换:

按相应的权表达式展开

精品课程微机原理多媒体课件

即:商=00000010B 余数=11B

精品课程微机原理多媒体课件

无符号数的表示范围:

0 ≤ X ≤ 2n-1 若运算结果超出这个范围,则产生溢出。

对无符号数:运算时,当最高位向更高位 有进位(或借位)时则产生 溢出。

精品课程微机原理多媒体课件

[例]:

最高位向前有进位,产生溢出

精品课程微机原理多媒体课件

2. 十进制到非十进制数的转换

对二进制的转换:

对整数:除2取余;

对小数:乘2取整。

对十六进制的转换:

对整数:除16取余;

对小数:乘16取整。

精品课程微机原理多媒体课件

3. 二进制与十六进制间的转换

用4位二进制数表示1位十六进制

数

精品课程微机原理多媒体课件

§1.3 二进制数的运算

无符号数

有符号数 算术运算 逻辑运算

精品课程微机原理多媒体课件

2. 符号二进制数与十进制的转换

对用补码表示的二进制数: 1)求出真值 2)进行转换

精品课程微机原理多媒体课件

二、有符号数

计算机中的符号数可表示为: 符号位+真值 机器数 表示正, 表示负。

“0” “1”

精品课程微机原理多媒体课件

[例]:

+52 = +0110100 = 0 0110100 符号位 真值

第微机原理与接口技术清华大学ppt课件

ALE

8088 CPU

地址 锁存

数据 收发

地址总线 数据总线

总线 控制器

控制总线

两种任务方式的选择方式

8088是任务在最小还是最大方式由MN/MX端形 状决议。MN/MX=0任务于最大方式,反之任务 于最小方式

二、8088CPU的引线及功能

引脚定义的方法可大致分为: 每个引脚只传送一种信息〔RD等〕; 引脚电平的高低不同的信号〔IO/M等〕; CPU任务于不同方式有不同的称号和定义

保管运算结果特征

总线接口单元

功能:

从内存中取指令到指令预取队列

担任与内存或输入/输出接口之间的数据 传送

在执行转移程序时,BIU使指令预取队列 复位,从指定的新地址取指令EU和BIU两个 部分可同时进展任务,从而

提高了CPU的效率; 降低了对存储器存取速度的要求

AX BX CX DX

AH,AL BH,BL CH,CL DH,DL

数据存放器特有的习惯用法

AX:累加器。一切I/O指令都经过AX与接口传送

信息,中间运算结果也多放于AX中;

BX:基址存放器。在间接寻址中用于存放基地址;

CX:计数存放器。用于在循环或串操作指令

中存放计数值;

DX:数据存放器。在间接寻址的I/O指令中存放

串行任务方式

8088以前的CPU采用串行任务方式:

CPU 取指令1

分析 指令1

BUS 忙碌

执行 指令1

取指令2

分析 指令2

忙碌

执行 指令2

并行任务方式

8088CPU采用并行任务方式

EUCPU

取指令1

分析 指令1

取指令2

执行 指令1

分析 指令2

微机原理与接口技术课件PPT

1 统一编址方式

从存储器空间划出一部分地址空间给I/O设备,把I/O 接口中的端口当作存储器单元一样进行访问,不设置 专门的I/O指令 优点: 访问I/O端口可实现输入/输出操作,还可以对端口内 容进行算术逻辑运算、移位等等; 能给端口有较大的编址空间,这对大型控制系统和 数据通信系统是很有意义的;

2.状态信息

CPU 在传送数据信息之前,经常需要先了解外 设当前的状态。如输入设备的数据是否准备好 、输出设备是否忙等。

用于表征外设工作状态的信息就叫做状态信息, 它总是由外设通过接口输入给CPU的。 状态信息的长度不定,可以是1个二进制位或 多个,含义也随外1 为什么要设置接口电路

CPU与外设两者的信号线不兼容,在信号线功能定义、逻 辑定义和时序关系上都不一致 两者的工作速度不兼容,CPU速度高,外设速度低

若不通过接口,而由CPU直接对外设的操作实施控制,就 会使CPU处于穷于应付与外设打交道之中,大大降低CPU的 效率 若外部设备直接由CPU控制,也会使外设的硬件结构依赖 于CPU,对外设本身的发展不利。

用来发布控制命令、控制外设工作的 信息,例如A/D转换器的启停信号。

控制信息总是CPU通过接口发出的。

返 回

5.1.3 接口的基本功能

1 . 2. 3. 4. 5. 6 . 7. 8. 数据缓冲功能 端口选择功能 信号转换功能 接收和执行CPU命令的功能 中断管理功能 可编程功能 返回外设状态的功能 数据宽度与数据格式转换的功能

I/O端口地址选用的原则

凡是被系统配置所占用了的地址一律不能使用 原则上讲,未被占用的地址,用户可以选用,但 对计算机厂家申明保留的地址,不要使用,否则 会发生I/O地址重叠和冲突,造成用户开发的产品 与系统不兼容而失去使用价值 一般,用户可使用300~31FH地址

微机原理与接口技术清华大学版第4章 ppt课件

定义字符串必须用DB伪指令

例:

DATA1 DB ‘ABCD’,66H

41H ‘ 42H A‘’ 43H B‘’ 44H C‘’

66H D’

2020/12/27

4

1. 汇编语言源程序与汇编程序

汇编语言源程序

用助记符编写

汇编程序

源程序的编译程序

汇编语言 源程序

汇编程序

机器语言 目标程序

2020/12/27

5

2. 汇编语言程序设计与执行过程

输入汇编语言源程序(EDIT) 汇编(MASM) 链接(LINK) 调试(TD)

源文件 . ASM 目标文件 .OBJ 可执行文件.EXE 最终程序

20

取值运算符

用于分析存储器操作数的属性

OFFSET SEG

取得其后变量或标号的偏移地址 取得其后变量或标号的段地址

TYPE LENGTH SIZE

取变量的类型 取所定义存储区的长度 取所定义存储区的字节数

2020/12/27

21

取值运算符例

MOV AX,SEG DATA MOV DS,AX MOV BX,OFFSET DATA

[变量名] 伪指令助记符 操作数,… ;[注释]

表示符号地址

定义变量类型

定义变量值 及区域大小

2020/12/27

29

1. 数据定义伪指令助记符

DB DW DD DQ DT

定义的变量为字节型 定义的变量为字类型(双字节) 定义的变量为双字型(4字节)

定义的变量为4字型(8字节)

定义的变量为10字节型

例:

MOV AL,8 AND 4 MOV AL,8+4-1

2020/12/27

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

64

3. 符号数的算术运算

通过引进补码,可将减法运算转换为加法运算。 即:[X+Y]补=[X]补+[Y]补

[X-Y]补=[X+(-Y)]补

=[X]补+[-Y]补 注:运算时符号位须对齐

65

[例]

X=-0110100,Y=+1110100,求X+Y=?

[X]原=10110100

将指令所在地址赋给程序计数器PC; PC内容送到地址寄存器AR,PC自动加1; 把AR的内容通过地址总线送至内存储器,经地址译码器译码, 选中相应单元。

CPU的控制器发出读命令。

在读命令控制下,把所选中单元的内容(即指令操作码)读到数 据总线DB。 把读出的内容经数据总线送到数据寄存器DR。 指令译码

37

三、无符号二进制数的运算

算术运算

无符号数 二进 制数的运算 有符号数

38

逻辑运算

主要内容

无符号二进 制数的算术运算

无符号数的表达范围 运算中的溢出问题 无符号数的逻辑运算 基本逻辑门和译码器

39

1. 无符号数的算术运算

加法运算

1+1=0(有进位)

减法运算

0-1=1(有借位)

55

[例]

X= -52 = -0110100

[X]原=1 0110100

[X]反=1 1001011

56

0的反码:

[+0]反=00000000

[-0]反 =11111111 即:数0的反码也不是唯一的。

57

补码

定义:

若X>0, 则[X]补= [X]反= [X]原

若X<0, 则[X]补= [X]反+1

H

28

2. 各种进制数间的转换

非十进制数到十进制数的转换

十进制到非十进制数的转换

二进制与十六进制数之间的转换

29

非十进制数到十进制数的转换

按相应的权值表达式展开

例:

1011.11B=1×23+0×22+1×21+1×20+1×2-1+ 1×2-2

=8+2+1+0.5+0.25 =11.75

乘法运算

除法运算

40

乘除运算例

00001011×0100

=00101100B

00001011÷0100=00000010B 即:商=00000010B

余数=11B

41

2. 无符号数的表示范围:

0 ≤ X ≤ 2n-1

若运算结果超出这个范围,则产生溢出。

对无符号数:运算时,当最高位向更高位 有进位(或借位)时则产生 溢出。

机器数

计算机中的数据

构成:

符号位 + 真值

“0” “1”

表示正 表示负

50

[例]

+52 = +0110100 = 0 0110100

符号位 真值

-52 = -0110100 = 1 0110100

符号位

真值

51

1. 符号数的表示

机器数的表示方法:

原码

反码

补码

52

原码

最高位为符号位(用‚0‛表示正,用‚1‛表 示负),其余为真值部分。

42

[例]:

最高位向前有进位,产生溢出

43

3. 逻辑运算

与、或、非、异或 掌握:

与、或、非门逻辑符号和逻辑关系(真值表);

与非门、或非门的应用。

44

“与”、“或”运算

‚与‛运算:

任何数和‚‚1‛相‚或‛,结果为1。

&

&

≥1

≥1

45

“非”、“异或”运算

《微机原理与接口技术实验指导书》(讲义) 陈文革,吴宁,夏秦编. 西安交通大学 《微机原理与接口技术题解及实验指导》(第3版). 吴宁,陈文革编. 清华大学出版社

3

第1章 微型计算机基础概论

主要内容:

微机系统的组成

计算机中的编码、数制及其转换 无符号二进制数的运算

算术运算和逻辑运算 运算中的溢出

系统软件

软件

应用软件

25

二、计算机中的数制和编码

数制和编码的表示 各种计数制之间的相互转换

26

1. 常用计数法

十进制(D) 二进制(B) 十六进制(H)

27

例:

234.98D或(234.98)D

1101.11B或(1101.11)B ABCD . BFH或(ABCD . BF)

写:

CPU将信息放入内存单元,单元中原来的内容被覆盖。

19

内存储器的分类

随机存取存储器(RAM)

按工作方 式可分为

只读存储器(ROM)

20

输入/输出接口

接口是CPU与外部设备间的桥梁

I/O

CPU 接口

外 设

21

接口的分类

串行接口 并行接口 数字接口 输入接口

输出接口

模拟接口

22

接口的功能

理解校验位的作用 熟悉0---F的ASCII码

36

ASCII码的奇偶校验

奇校验

加上校验位后编码中‚1‛的个数为奇数。 例:A的ASCII码是41H(1000001B)

以奇校验传送则为 C1H(11000001B)

偶校验

加上校验位后 编码中‚1‛的个数为偶数。

上例若以偶校验传送,则为 41H。

5B.8H=5×161+11×160+8×16-1 =80+11+0.5 =91.5

30

十进制到非十进制数的转换

到二进制的转换: 对整数:除2取余;

对小数:乘2取整。

到十六进制的转换:

对整数:除16取余;

对小数:乘16取整。

31

二进制与十六进制间的转换

用4位二进制数表示1位十六进制数 例:

34

BCD码与二进制数之间的转换

先转换为十进 制数,再转换二进 制数;反之同 样。 例:

(0001 0001 .0010 0101)BCD =11 .25 =(1011 .01)

B

35

ASCII码

西文 字符的编码,一般用7位二进 制码表示。

D7位为校验位,默认情况下为0。

要求:

因为取出的是指令的操作码,故数据寄存器DR把它送到指令寄存器 IR,然后再送到指令译码器ID 10

冯 • 诺依曼机的特点和不足

特点:

程序存储,共享数据,顺序执行 属于顺序处理机,适合于确定的算法和数值数据的 处理。 与存储器间有大量数据交互,对总线要求很高; 执行顺序有程序决定,对大型复杂任务较困难; 以运算器为核心,处理效率较低; 由PC控制执行顺序,难以进行真正的并行处理。

机器数的表示及运算 基本逻辑门及译码器

4

一、微型计算机系统

微型机的工作原理 微机系统的基本组成

5

1. 计算机的工作原理

冯

•

诺依曼计算机的工作原理

存储程序工作原理

6

存储程序原理

将计算过程描述为由许多条指令按一定顺序组 成的程序,并放入存储器保存

指令按其在存储器中存放的顺序执行;

‚非‛运算

按位求反

‚异或‛运算

相同则为0,相异则为1

46

4.

译码器

各引脚功能

输入端与输出端关系(真值表)

掌握74LS138译码器

47

74LS138译码器

主要引脚及功能 G1 G2A G2B C B Y0

• • • •

A

Y7

48

三、机器数(有符号数)的运算

49

计算机中符号数的表示

25.5 = 11001.1B = 19.8H 11001010.0110101B =CA.6AH

32

3. 计算机中的编码

BCD码

用二进制编码表示的十进制数

ASCII码

西文字符编码

33

BCD码

压缩BCD码

用4位二进制码表示一位十进制数 每4位之间有一个空格

扩展BCD码

用8位二进制码表示一位十进制数,每4位之间有一 个空格。

内存按单元组织 每单元都对应一个地址,以方便对单元的寻址

单元内容

38F04H

内存地址

10110110

17

内存容量

内存容量:

所含存储单元的个数,以字节为单位

内存容量的大小依CPU的寻址能力而定

实地址模式下为CPU地址信号线的位数

18

内存操作

读:

将内存单元的内容取入CPU,原单元内容不改变;

微机原理与接口技术

大家好!

1

课程目标

掌握:

微型计算机的基本工作原理

汇编语言程序设计方法

微型计算机接口技术 建立微型计算机系统的整体概念,形成微机系统软 硬件开发的初步能力

3. 符号数的算术运算

通过引进补码,可将减法运算转换为加法运算。 即:[X+Y]补=[X]补+[Y]补

[X-Y]补=[X+(-Y)]补

=[X]补+[-Y]补 注:运算时符号位须对齐

65

[例]

X=-0110100,Y=+1110100,求X+Y=?

[X]原=10110100

将指令所在地址赋给程序计数器PC; PC内容送到地址寄存器AR,PC自动加1; 把AR的内容通过地址总线送至内存储器,经地址译码器译码, 选中相应单元。

CPU的控制器发出读命令。

在读命令控制下,把所选中单元的内容(即指令操作码)读到数 据总线DB。 把读出的内容经数据总线送到数据寄存器DR。 指令译码

37

三、无符号二进制数的运算

算术运算

无符号数 二进 制数的运算 有符号数

38

逻辑运算

主要内容

无符号二进 制数的算术运算

无符号数的表达范围 运算中的溢出问题 无符号数的逻辑运算 基本逻辑门和译码器

39

1. 无符号数的算术运算

加法运算

1+1=0(有进位)

减法运算

0-1=1(有借位)

55

[例]

X= -52 = -0110100

[X]原=1 0110100

[X]反=1 1001011

56

0的反码:

[+0]反=00000000

[-0]反 =11111111 即:数0的反码也不是唯一的。

57

补码

定义:

若X>0, 则[X]补= [X]反= [X]原

若X<0, 则[X]补= [X]反+1

H

28

2. 各种进制数间的转换

非十进制数到十进制数的转换

十进制到非十进制数的转换

二进制与十六进制数之间的转换

29

非十进制数到十进制数的转换

按相应的权值表达式展开

例:

1011.11B=1×23+0×22+1×21+1×20+1×2-1+ 1×2-2

=8+2+1+0.5+0.25 =11.75

乘法运算

除法运算

40

乘除运算例

00001011×0100

=00101100B

00001011÷0100=00000010B 即:商=00000010B

余数=11B

41

2. 无符号数的表示范围:

0 ≤ X ≤ 2n-1

若运算结果超出这个范围,则产生溢出。

对无符号数:运算时,当最高位向更高位 有进位(或借位)时则产生 溢出。

机器数

计算机中的数据

构成:

符号位 + 真值

“0” “1”

表示正 表示负

50

[例]

+52 = +0110100 = 0 0110100

符号位 真值

-52 = -0110100 = 1 0110100

符号位

真值

51

1. 符号数的表示

机器数的表示方法:

原码

反码

补码

52

原码

最高位为符号位(用‚0‛表示正,用‚1‛表 示负),其余为真值部分。

42

[例]:

最高位向前有进位,产生溢出

43

3. 逻辑运算

与、或、非、异或 掌握:

与、或、非门逻辑符号和逻辑关系(真值表);

与非门、或非门的应用。

44

“与”、“或”运算

‚与‛运算:

任何数和‚‚1‛相‚或‛,结果为1。

&

&

≥1

≥1

45

“非”、“异或”运算

《微机原理与接口技术实验指导书》(讲义) 陈文革,吴宁,夏秦编. 西安交通大学 《微机原理与接口技术题解及实验指导》(第3版). 吴宁,陈文革编. 清华大学出版社

3

第1章 微型计算机基础概论

主要内容:

微机系统的组成

计算机中的编码、数制及其转换 无符号二进制数的运算

算术运算和逻辑运算 运算中的溢出

系统软件

软件

应用软件

25

二、计算机中的数制和编码

数制和编码的表示 各种计数制之间的相互转换

26

1. 常用计数法

十进制(D) 二进制(B) 十六进制(H)

27

例:

234.98D或(234.98)D

1101.11B或(1101.11)B ABCD . BFH或(ABCD . BF)

写:

CPU将信息放入内存单元,单元中原来的内容被覆盖。

19

内存储器的分类

随机存取存储器(RAM)

按工作方 式可分为

只读存储器(ROM)

20

输入/输出接口

接口是CPU与外部设备间的桥梁

I/O

CPU 接口

外 设

21

接口的分类

串行接口 并行接口 数字接口 输入接口

输出接口

模拟接口

22

接口的功能

理解校验位的作用 熟悉0---F的ASCII码

36

ASCII码的奇偶校验

奇校验

加上校验位后编码中‚1‛的个数为奇数。 例:A的ASCII码是41H(1000001B)

以奇校验传送则为 C1H(11000001B)

偶校验

加上校验位后 编码中‚1‛的个数为偶数。

上例若以偶校验传送,则为 41H。

5B.8H=5×161+11×160+8×16-1 =80+11+0.5 =91.5

30

十进制到非十进制数的转换

到二进制的转换: 对整数:除2取余;

对小数:乘2取整。

到十六进制的转换:

对整数:除16取余;

对小数:乘16取整。

31

二进制与十六进制间的转换

用4位二进制数表示1位十六进制数 例:

34

BCD码与二进制数之间的转换

先转换为十进 制数,再转换二进 制数;反之同 样。 例:

(0001 0001 .0010 0101)BCD =11 .25 =(1011 .01)

B

35

ASCII码

西文 字符的编码,一般用7位二进 制码表示。

D7位为校验位,默认情况下为0。

要求:

因为取出的是指令的操作码,故数据寄存器DR把它送到指令寄存器 IR,然后再送到指令译码器ID 10

冯 • 诺依曼机的特点和不足

特点:

程序存储,共享数据,顺序执行 属于顺序处理机,适合于确定的算法和数值数据的 处理。 与存储器间有大量数据交互,对总线要求很高; 执行顺序有程序决定,对大型复杂任务较困难; 以运算器为核心,处理效率较低; 由PC控制执行顺序,难以进行真正的并行处理。

机器数的表示及运算 基本逻辑门及译码器

4

一、微型计算机系统

微型机的工作原理 微机系统的基本组成

5

1. 计算机的工作原理

冯

•

诺依曼计算机的工作原理

存储程序工作原理

6

存储程序原理

将计算过程描述为由许多条指令按一定顺序组 成的程序,并放入存储器保存

指令按其在存储器中存放的顺序执行;

‚非‛运算

按位求反

‚异或‛运算

相同则为0,相异则为1

46

4.

译码器

各引脚功能

输入端与输出端关系(真值表)

掌握74LS138译码器

47

74LS138译码器

主要引脚及功能 G1 G2A G2B C B Y0

• • • •

A

Y7

48

三、机器数(有符号数)的运算

49

计算机中符号数的表示

25.5 = 11001.1B = 19.8H 11001010.0110101B =CA.6AH

32

3. 计算机中的编码

BCD码

用二进制编码表示的十进制数

ASCII码

西文字符编码

33

BCD码

压缩BCD码

用4位二进制码表示一位十进制数 每4位之间有一个空格

扩展BCD码

用8位二进制码表示一位十进制数,每4位之间有一 个空格。

内存按单元组织 每单元都对应一个地址,以方便对单元的寻址

单元内容

38F04H

内存地址

10110110

17

内存容量

内存容量:

所含存储单元的个数,以字节为单位

内存容量的大小依CPU的寻址能力而定

实地址模式下为CPU地址信号线的位数

18

内存操作

读:

将内存单元的内容取入CPU,原单元内容不改变;

微机原理与接口技术

大家好!

1

课程目标

掌握:

微型计算机的基本工作原理

汇编语言程序设计方法

微型计算机接口技术 建立微型计算机系统的整体概念,形成微机系统软 硬件开发的初步能力