VXI数模混合信号集成电路测试系统

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第 19 卷 ・ 52 ・

第2期

电子测量与仪器学报 JOURNAL OF ELECTRONIC MEASUREMENT AND INSTRUMENT

Vol .19

No .2

2005 年 4 月

! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! !

2

2.1

研发内容

VXI 数模混合信号集成电路测试系统涉及的 主要内容

图1 2.3 主控计算机子系统 测试系统必备的全部指令集。所有指令都是无缝的 (seamiess) 单测试周期。具有循环、 跳转、 子程序调 用, 且循环、 子程序调用可嵌套 ( 2 级嵌套、 64K 寻址 范围) 。系统测试周期及激励、 响应沿均可在单测试 周期内设置 ( on the fiy) 。 高分 PG 时钟产生器由锁相环构成的高稳定度、 辨率数字频率合成器产生一 1OOMHZ - 2OOMHZ 高稳 定系 统 时 钟, 由 2Obit 高 速 定 时 器 产 生 1OOHZ 到 5OMHZ 的测试周期。此高速定时器可根据时钟选择 存储器设置的 16 种测试周期动态改变 ( on the fiy) 。 起/ 停控制 器 由 一 16bit 失 效 计 数 器 及 一 24bit 步进计数器控制测试周期停止状态。起 / 停控制器 可由测试程序及由外触发信号控制测试周期产生。 高速指令译码控制电路由一高速 22bit PC 记数 器产生 4M 循址范围, 16 bit 循环记数器由循环指令 加载循 环 次 数。PC 记 数 器 及 循 环 记 数 器 匀 有 一 用于循环及子程序调用嵌套 2X16 bit 堆栈存储器, 功能。指令译码逻辑控制根据高速指令存储器中的 指令码、 操作数及失效状态、 循环记数器进位状态实 时地产生各种控制信号, 控制 PC 记数器、 循环记数

15.93 27.05 4.65 7.90

10.31 16.98 28.84 0.17 0.29 0.48

11.54 12.63 20.81 35.35 35.6 58.66 99.62

29.83 32.22

注: 资料引自: 电子仪器信息, 2004.7.8

由于目前国内测试系统的研发技术水平、 科研 经费、 企业规模与国际先进水平有较大差距, 我们采 用国际通用的开放性、 标准化 VXI, 使我们 PXI 总线, 研发的自动测试设备从低端到中高端都建立在统一 的开放性、 标准化总线结构上, 保证了产品的兼容

(1) 主控计算机 P4 微机 基本配置: CPU Pentium 4 Processor; 1O24 X 768 分辨率, 彩显; 17 ” 256M DDR 内存, 32M 显存; Ether打印机接口, 操作 net 网, USB, 1394 高速火线接口; 系统:Windows 9X/Windows 2OOO; 开发环境:NI Lab总线 VIEW 和 LabWindows/CVI 虚 拟 仪 器 开 发 平 台; 标准:PCI 标准总线,USB 通用串行总线, 1394 高速 火线及 Ethernet 网。 (2) 零槽控制器 / 高速总线接口 零槽控制器通过 1394 高速火线与主控计算机 进行通讯(4OMb/S) , 执行初始化、 自检命令, 并加载 测试激励图形及处理响应向量。系统中各模块通过 实现高速数据通讯。 VXI 寄存器基高速总线接口, 零槽控制器还提供高速触发总线、 ECL 时钟等用于 系统同步、 触发信号。 2.4 高速图形控制子系统 图 2 是高速图形控制子系统框图, 由 PG 时钟 产生器、 起 / 停控制器、 高速指令译码控制电路及指 令存储器 (指令码 + 操作数) 组成。系统实现了高速

本文于 2005 年 1 月收到。冯建科: 教授级高级工程师; 张生文: 高级工程师; 郭士瑞: 副研究员。

第2期 ・ 53 ・ VXI 数模混合信号集成电路测试系统 ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! 性、 延续性、 开放性及标准化的特点, 加快了产品的 升级换代。利用其开放性、 标准化特点, 可方便插入 各仪器制造商提供的通用 VXI, 测试模块 PXI 测量、 灵活配置 系 统。这 对 今 后 大 量 涌 现 的 数 模 混 合、 SOC 芯片测试提供了大量测试资源。能够根据测试 需求, 以最优性 / 价比配置系统。 (1) 主控计算机子系统的研制。 (2) 高速通道控制子系统的研制。 (3) 高速图形产生子系统的研制。 (4) 直流参数测试子系统研制。 (5) 机柜子系统研制。 (6) 高速、 高密、 超密封装、 多层 PCB 板设计技 术研究。 (7) 软件方案。 (8) 系统集成方案。 2.2 测试系统组成 测试系统组成见图 1

Abstract:Now the mixed signaI IC testing system has wide appIication in China . This paper introduced the digitaI and anaIog mixed signaI Test System IC based on VXI bus that is major project provided by EIectronic information technoIogy deveIopment foundation of Ministry of Information Industry . The discussion incIuded system hardware and software design based on the high speed,muItchanneIs,Iow power consumption and compact perfomannce for VXI bus reguirement,and emphasized or the upgrading the opening and standardizaton of the system. Keyword:VXI bus; digitaI and anaIog mixed signaI IC ; test system. 开放性和标准化, 使系统具有灵活配置, 不断升级,

图3 主要由时间产生器 ( TG ) 、 时间沿选择矩阵 (MUX) 、 驱动、 响应格式化器及测试向量存储器组 成。 每块高速通道板产生 16 个时间沿, 供 32 路测 试通道使用。其中 8 个激励沿、 4 个响应沿、 2 个 I/0 控制沿及两个通道复用沿。 128 pin 系统由 1 块图形板、 4 块高速通道板组 成。可产生 32 个激励沿、 16 个响应沿。 256 pin 系统由 1/2 块图形板、 8 块高速图形板 组成。可产生 64 个激励沿、 32 个响应沿。 每块高速通道板 TG 由 4 块高速门阵列组成, 每块门阵列产生 4 个时间沿。其内部由 16bit 高速 定时器 (由 TO 时钟倍频产生 2OOMHZ 定时时钟) 产 生分辨率为 2.5 nS 的定时沿。每一测试周期的定时 沿均可由定时存储器动态设置 ( On the fiy) . 高速通道板的时间沿选择矩阵 (MUX) 、 驱动、 响 应格式化器由 4 块门阵列组成。每块门阵列内实现 ( MUX) , 根据 8 个激励沿、 4 个响应沿多路选择矩阵

VXI 数模混合信号集成电路测试系统

冯建科

摘

张生文

郭士瑞

(北京自动测试技术研究所, 北京 100088) 要: 数模混合集成电路测试系统是当前我国的主流测试系统, 本文以信息产业部电子信息产业发展基金重点招议标

为例进行了介绍。论述基于 VXI 总线的高速、 高密度、 多通道、 低功 项目 (VXI 数模混合集成电路测试系统研究开发及产业化) 耗新型 ATE IC 测试系统, 介绍了系统的软硬件设计。详细论述了全面提高系统开放性、 标准化的设计思想。 关键词: 数模混合集成电路; 测试系统 VXI 总线;

ATS of D/ A Mixed Signal IC Test System Based on VXI Bus

Feng Jianke Zhang Shengwen Guo Shirui

( Institute of Automatic Test TechnoIogies,Beijing,100088,China)

・ 54 ・ 电 子 测 量 与 仪 器 学 报 2OO5 年 ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! 器、 堆栈指针、 堆栈存储器的加载、 记数及保持状态。 起 / 停控制器、 高速指令译码控制电路、 22 bit PC 记数器、 循环堆栈存储器及 16 bit 循环记数器、 PC、 指针控制电路均设计在两块大规模、 高速、 高密度门 阵列中。在此门阵列中对高速指令译码进行优化设 计: 减少指令译码链级数, 增加并行电路, 实现高速 译码时序 . 由于各记数器及堆栈存储器均在片内实 现, 从而减少了线延迟及门阵列 I/0 延迟。 以便灵活配置及升级。 PG 为单独模块设计, 系统时钟 TO、 系统测试周期 TCLK 作为整个测 试系统的高速 (1OOMHZ - 2OOMHZ) 定时参考源, 必须 确保其稳定、 低延时特性。采用 ECL 差分驱动且利 用 VXI 底板信号作为整个测试系统的定时总线。 控制信号由专用总 22bit PC 地址及失效信号、 线传送。 !"# 图2 高速通道控制子系统 高速通道板见图 3。

第2期 ・ 55 ・ VXI 数模混合信号集成电路测试系统 " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " 格式化定义数据及 F、 响 D、 M 数据产生 8 路驱动、 应、 I/O 格式化图形。 高速通道板的 PE 卡设计为子模块形式。由 4 片 PE 电路组成, 每片电路提供 8 路高速可编程 I/O (含有高速 8 驱动 / 比较 (窗口比较) 器) 。 高速通道板中提供每路 4bit( F、 D、 M、 R)最大 4M 深度的测试向量存储器, R 存储器可用于存储失 效结果也可用于存储响应向量, 便于自学习法及逻 辑分析。测试向量存储器采用通用 12 - 15ns 大容量 SRAM。 , 高速通道板中设计有算法图形产生器 ( APG) 产生 14 行 X 14 列 (64M) 图形地址, 用于动态 RAM, 静态 RAM, FLASH RAM 等 存 储 器 测 试。 可 产 生 (WALK, MARCH, CHECK, ADCOM, BFLY, DUALWC, GALPAT, SLID, RCCGAL, MASEST, IMAG, RTICK, PMCHECK) 13 种测试图形。 板中还设计有 Active Series SCAN 模式, 可将并 行数据转为串行数据, 每模块最大串行存储深度为 最大串行存储深度 32M. 如果将模块串行数据级联, 为 256M。 系统硬件资源中, PG、 TG 均设计为每一测试周 期可编程 ( On the fiy) , 且具有较多的 TG 沿。能够满 足 IC 验证 CAD 到 CAT 测试时序匹配要求。 由于设计了 Active Series SCAN 模块, 可将并行 数据转为串行数据。用于支持边界扫描及内建自测 试。 2.6 直流参数测试子系统 直流参数测试子系统用于精密参数测试。本测 试系统针对快速、 并行测试需求, 设计了多 PMU 功 能。64 管脚配备一个 4PMU 模块,128 管脚配备二 个 8 PMU 模块, 提供每 16 管脚 /PMU。 (1) 精密测量单元 ( PMU) 电流施加和测试能力。 PMU 具有 4 象限电压、 “ Keiven” 连接, 以保 PMU 和测试头之间的通道采用 证施加和测量的准确度。 PMU 有以下工作方式: 加流 / 测压 ! 加压 / 测流, ( 1 40mA, 1 1mA, 1 100LA, 1 ! 4 量程电流 10LA) ! + 7V/ - 5V 电压范围。 箝位功能。 ! 短路保护、 ! 快 速 GO/NGO 测 量。可 并 行 测 试 多 PMU GO/NGO 参数。 器件电源 (DPS) (2) 每模块可提供 2 路{ , DPS + (0 到 + 40V) DPS (0 到 - 40V) } 器件电源, 为 DUT 供电 (200mA 电流驱 动能力) 。用 “Keivin” 方法连接到测试头。 每模块还提供 4 路参考辅助双向电源 ( 1 10V, 。用于多电源器件测试及提供参考电平。 1 10mA) 每个 DPS 都具有电流测试能力, 其值可以通过 PMU 读出。 电源 2.7 机箱、 本测试系统主要采用大规模、 高密度 CMOS 门 阵列及专用电路, 使系统功耗大为降低。系统电源 功率 < 600W。机箱散热采用风冷散热。由于集成 密度提高, 使得整个测试系统集成在一个标准 VXI 槽机箱中。系统底板为 13 10 层 PCB 板。遵循 VXI 协议, 保证了底板信号的完整性和电 / 磁兼容性。 2.8 高速、 高密、 超密封装、 多层 PCB 板设计技术 研究

21 世纪是技术高度发达的信息化世纪。全球 信息化的发展正在加快步伐。在这里起关键性作用 的技术是以集成电路为核心的电子信息技术。集成 电路测试技术是集成电路产业的重要基础技术, 它 贯穿集成电路设计、 生产、 应用的全过程。 ( Automated Test 2003 年 最 大 的 自 动 测 试 设 备 应用市场为混合信号集成电路测试, 其 Eguipment) 次为存储器测试, 分别占市场比重 30% 与 26% 。根 据我国台湾地区的数据显示混合信号集成电路测试 占的比例最大。 国际上先进的测试设备制造商都针对主流测试 市场推出中、 高档测试设备, 但任何一款测试设备都 不能满足不断更新的测试需求。为解决性能、 价格 的矛盾, 适应性和复杂性的矛盾, 各大测试设备制造 商 (如泰瑞达、 爱德万公司) 都先后提出测试系统的

1

国内外 ATE 发展源自文库状

快速编程, 以适应各种测试需求, 构造出最优性/ 价 比的系统。

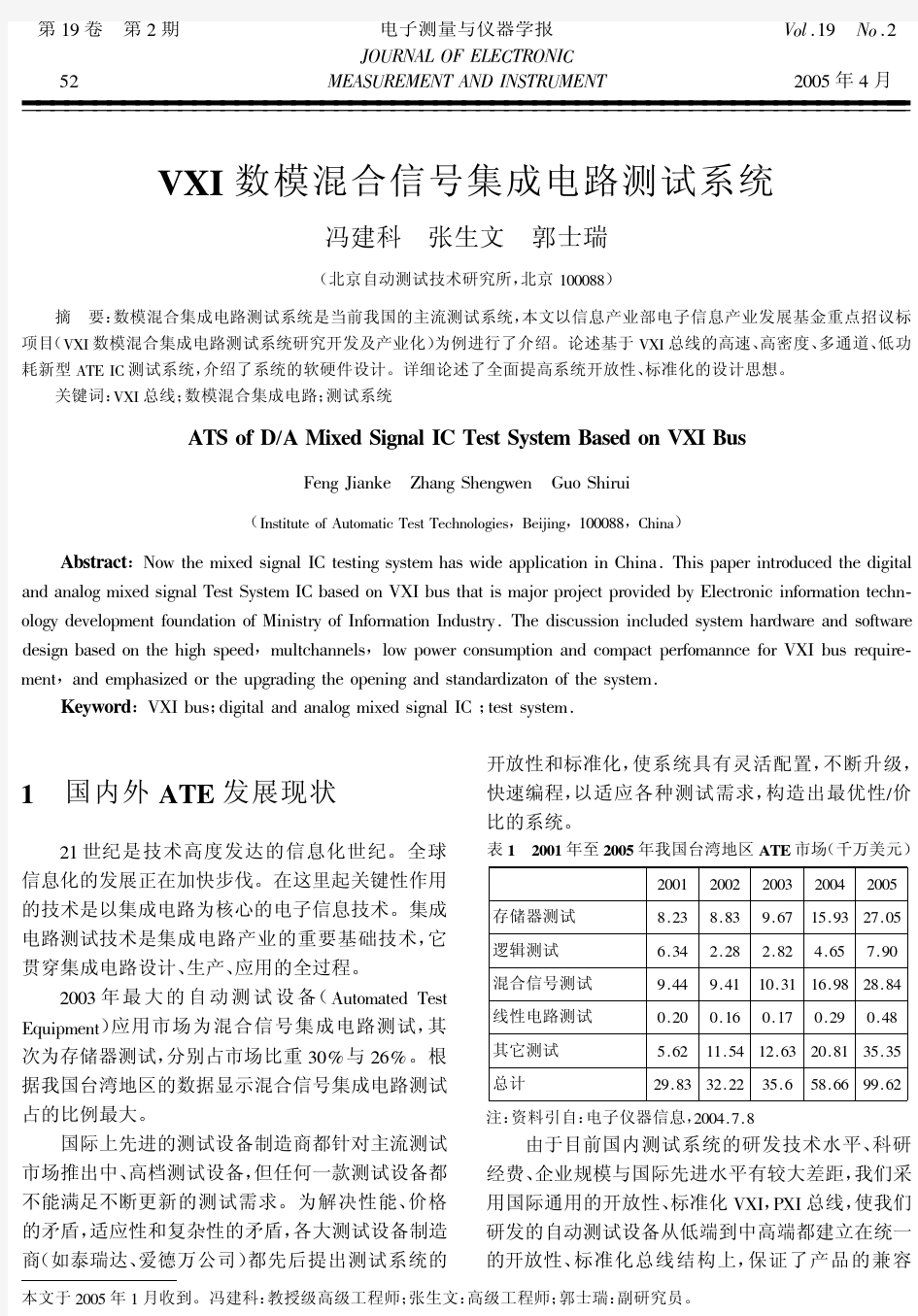

表 1 2001 年至 2005 年我国台湾地区 ATE 市场 (千万美元) 2001 存储器测试 逻辑测试 混合信号测试 线性电路测试 其它测试 总计 8.23 6.34 9.44 0.20 5.62 2002 8.83 2.28 9.41 0.16 2003 9.67 2.82 2004 2005

第2期

电子测量与仪器学报 JOURNAL OF ELECTRONIC MEASUREMENT AND INSTRUMENT

Vol .19

No .2

2005 年 4 月

! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! !

2

2.1

研发内容

VXI 数模混合信号集成电路测试系统涉及的 主要内容

图1 2.3 主控计算机子系统 测试系统必备的全部指令集。所有指令都是无缝的 (seamiess) 单测试周期。具有循环、 跳转、 子程序调 用, 且循环、 子程序调用可嵌套 ( 2 级嵌套、 64K 寻址 范围) 。系统测试周期及激励、 响应沿均可在单测试 周期内设置 ( on the fiy) 。 高分 PG 时钟产生器由锁相环构成的高稳定度、 辨率数字频率合成器产生一 1OOMHZ - 2OOMHZ 高稳 定系 统 时 钟, 由 2Obit 高 速 定 时 器 产 生 1OOHZ 到 5OMHZ 的测试周期。此高速定时器可根据时钟选择 存储器设置的 16 种测试周期动态改变 ( on the fiy) 。 起/ 停控制 器 由 一 16bit 失 效 计 数 器 及 一 24bit 步进计数器控制测试周期停止状态。起 / 停控制器 可由测试程序及由外触发信号控制测试周期产生。 高速指令译码控制电路由一高速 22bit PC 记数 器产生 4M 循址范围, 16 bit 循环记数器由循环指令 加载循 环 次 数。PC 记 数 器 及 循 环 记 数 器 匀 有 一 用于循环及子程序调用嵌套 2X16 bit 堆栈存储器, 功能。指令译码逻辑控制根据高速指令存储器中的 指令码、 操作数及失效状态、 循环记数器进位状态实 时地产生各种控制信号, 控制 PC 记数器、 循环记数

15.93 27.05 4.65 7.90

10.31 16.98 28.84 0.17 0.29 0.48

11.54 12.63 20.81 35.35 35.6 58.66 99.62

29.83 32.22

注: 资料引自: 电子仪器信息, 2004.7.8

由于目前国内测试系统的研发技术水平、 科研 经费、 企业规模与国际先进水平有较大差距, 我们采 用国际通用的开放性、 标准化 VXI, 使我们 PXI 总线, 研发的自动测试设备从低端到中高端都建立在统一 的开放性、 标准化总线结构上, 保证了产品的兼容

(1) 主控计算机 P4 微机 基本配置: CPU Pentium 4 Processor; 1O24 X 768 分辨率, 彩显; 17 ” 256M DDR 内存, 32M 显存; Ether打印机接口, 操作 net 网, USB, 1394 高速火线接口; 系统:Windows 9X/Windows 2OOO; 开发环境:NI Lab总线 VIEW 和 LabWindows/CVI 虚 拟 仪 器 开 发 平 台; 标准:PCI 标准总线,USB 通用串行总线, 1394 高速 火线及 Ethernet 网。 (2) 零槽控制器 / 高速总线接口 零槽控制器通过 1394 高速火线与主控计算机 进行通讯(4OMb/S) , 执行初始化、 自检命令, 并加载 测试激励图形及处理响应向量。系统中各模块通过 实现高速数据通讯。 VXI 寄存器基高速总线接口, 零槽控制器还提供高速触发总线、 ECL 时钟等用于 系统同步、 触发信号。 2.4 高速图形控制子系统 图 2 是高速图形控制子系统框图, 由 PG 时钟 产生器、 起 / 停控制器、 高速指令译码控制电路及指 令存储器 (指令码 + 操作数) 组成。系统实现了高速

本文于 2005 年 1 月收到。冯建科: 教授级高级工程师; 张生文: 高级工程师; 郭士瑞: 副研究员。

第2期 ・ 53 ・ VXI 数模混合信号集成电路测试系统 ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! 性、 延续性、 开放性及标准化的特点, 加快了产品的 升级换代。利用其开放性、 标准化特点, 可方便插入 各仪器制造商提供的通用 VXI, 测试模块 PXI 测量、 灵活配置 系 统。这 对 今 后 大 量 涌 现 的 数 模 混 合、 SOC 芯片测试提供了大量测试资源。能够根据测试 需求, 以最优性 / 价比配置系统。 (1) 主控计算机子系统的研制。 (2) 高速通道控制子系统的研制。 (3) 高速图形产生子系统的研制。 (4) 直流参数测试子系统研制。 (5) 机柜子系统研制。 (6) 高速、 高密、 超密封装、 多层 PCB 板设计技 术研究。 (7) 软件方案。 (8) 系统集成方案。 2.2 测试系统组成 测试系统组成见图 1

Abstract:Now the mixed signaI IC testing system has wide appIication in China . This paper introduced the digitaI and anaIog mixed signaI Test System IC based on VXI bus that is major project provided by EIectronic information technoIogy deveIopment foundation of Ministry of Information Industry . The discussion incIuded system hardware and software design based on the high speed,muItchanneIs,Iow power consumption and compact perfomannce for VXI bus reguirement,and emphasized or the upgrading the opening and standardizaton of the system. Keyword:VXI bus; digitaI and anaIog mixed signaI IC ; test system. 开放性和标准化, 使系统具有灵活配置, 不断升级,

图3 主要由时间产生器 ( TG ) 、 时间沿选择矩阵 (MUX) 、 驱动、 响应格式化器及测试向量存储器组 成。 每块高速通道板产生 16 个时间沿, 供 32 路测 试通道使用。其中 8 个激励沿、 4 个响应沿、 2 个 I/0 控制沿及两个通道复用沿。 128 pin 系统由 1 块图形板、 4 块高速通道板组 成。可产生 32 个激励沿、 16 个响应沿。 256 pin 系统由 1/2 块图形板、 8 块高速图形板 组成。可产生 64 个激励沿、 32 个响应沿。 每块高速通道板 TG 由 4 块高速门阵列组成, 每块门阵列产生 4 个时间沿。其内部由 16bit 高速 定时器 (由 TO 时钟倍频产生 2OOMHZ 定时时钟) 产 生分辨率为 2.5 nS 的定时沿。每一测试周期的定时 沿均可由定时存储器动态设置 ( On the fiy) . 高速通道板的时间沿选择矩阵 (MUX) 、 驱动、 响 应格式化器由 4 块门阵列组成。每块门阵列内实现 ( MUX) , 根据 8 个激励沿、 4 个响应沿多路选择矩阵

VXI 数模混合信号集成电路测试系统

冯建科

摘

张生文

郭士瑞

(北京自动测试技术研究所, 北京 100088) 要: 数模混合集成电路测试系统是当前我国的主流测试系统, 本文以信息产业部电子信息产业发展基金重点招议标

为例进行了介绍。论述基于 VXI 总线的高速、 高密度、 多通道、 低功 项目 (VXI 数模混合集成电路测试系统研究开发及产业化) 耗新型 ATE IC 测试系统, 介绍了系统的软硬件设计。详细论述了全面提高系统开放性、 标准化的设计思想。 关键词: 数模混合集成电路; 测试系统 VXI 总线;

ATS of D/ A Mixed Signal IC Test System Based on VXI Bus

Feng Jianke Zhang Shengwen Guo Shirui

( Institute of Automatic Test TechnoIogies,Beijing,100088,China)

・ 54 ・ 电 子 测 量 与 仪 器 学 报 2OO5 年 ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! 器、 堆栈指针、 堆栈存储器的加载、 记数及保持状态。 起 / 停控制器、 高速指令译码控制电路、 22 bit PC 记数器、 循环堆栈存储器及 16 bit 循环记数器、 PC、 指针控制电路均设计在两块大规模、 高速、 高密度门 阵列中。在此门阵列中对高速指令译码进行优化设 计: 减少指令译码链级数, 增加并行电路, 实现高速 译码时序 . 由于各记数器及堆栈存储器均在片内实 现, 从而减少了线延迟及门阵列 I/0 延迟。 以便灵活配置及升级。 PG 为单独模块设计, 系统时钟 TO、 系统测试周期 TCLK 作为整个测 试系统的高速 (1OOMHZ - 2OOMHZ) 定时参考源, 必须 确保其稳定、 低延时特性。采用 ECL 差分驱动且利 用 VXI 底板信号作为整个测试系统的定时总线。 控制信号由专用总 22bit PC 地址及失效信号、 线传送。 !"# 图2 高速通道控制子系统 高速通道板见图 3。

第2期 ・ 55 ・ VXI 数模混合信号集成电路测试系统 " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " 格式化定义数据及 F、 响 D、 M 数据产生 8 路驱动、 应、 I/O 格式化图形。 高速通道板的 PE 卡设计为子模块形式。由 4 片 PE 电路组成, 每片电路提供 8 路高速可编程 I/O (含有高速 8 驱动 / 比较 (窗口比较) 器) 。 高速通道板中提供每路 4bit( F、 D、 M、 R)最大 4M 深度的测试向量存储器, R 存储器可用于存储失 效结果也可用于存储响应向量, 便于自学习法及逻 辑分析。测试向量存储器采用通用 12 - 15ns 大容量 SRAM。 , 高速通道板中设计有算法图形产生器 ( APG) 产生 14 行 X 14 列 (64M) 图形地址, 用于动态 RAM, 静态 RAM, FLASH RAM 等 存 储 器 测 试。 可 产 生 (WALK, MARCH, CHECK, ADCOM, BFLY, DUALWC, GALPAT, SLID, RCCGAL, MASEST, IMAG, RTICK, PMCHECK) 13 种测试图形。 板中还设计有 Active Series SCAN 模式, 可将并 行数据转为串行数据, 每模块最大串行存储深度为 最大串行存储深度 32M. 如果将模块串行数据级联, 为 256M。 系统硬件资源中, PG、 TG 均设计为每一测试周 期可编程 ( On the fiy) , 且具有较多的 TG 沿。能够满 足 IC 验证 CAD 到 CAT 测试时序匹配要求。 由于设计了 Active Series SCAN 模块, 可将并行 数据转为串行数据。用于支持边界扫描及内建自测 试。 2.6 直流参数测试子系统 直流参数测试子系统用于精密参数测试。本测 试系统针对快速、 并行测试需求, 设计了多 PMU 功 能。64 管脚配备一个 4PMU 模块,128 管脚配备二 个 8 PMU 模块, 提供每 16 管脚 /PMU。 (1) 精密测量单元 ( PMU) 电流施加和测试能力。 PMU 具有 4 象限电压、 “ Keiven” 连接, 以保 PMU 和测试头之间的通道采用 证施加和测量的准确度。 PMU 有以下工作方式: 加流 / 测压 ! 加压 / 测流, ( 1 40mA, 1 1mA, 1 100LA, 1 ! 4 量程电流 10LA) ! + 7V/ - 5V 电压范围。 箝位功能。 ! 短路保护、 ! 快 速 GO/NGO 测 量。可 并 行 测 试 多 PMU GO/NGO 参数。 器件电源 (DPS) (2) 每模块可提供 2 路{ , DPS + (0 到 + 40V) DPS (0 到 - 40V) } 器件电源, 为 DUT 供电 (200mA 电流驱 动能力) 。用 “Keivin” 方法连接到测试头。 每模块还提供 4 路参考辅助双向电源 ( 1 10V, 。用于多电源器件测试及提供参考电平。 1 10mA) 每个 DPS 都具有电流测试能力, 其值可以通过 PMU 读出。 电源 2.7 机箱、 本测试系统主要采用大规模、 高密度 CMOS 门 阵列及专用电路, 使系统功耗大为降低。系统电源 功率 < 600W。机箱散热采用风冷散热。由于集成 密度提高, 使得整个测试系统集成在一个标准 VXI 槽机箱中。系统底板为 13 10 层 PCB 板。遵循 VXI 协议, 保证了底板信号的完整性和电 / 磁兼容性。 2.8 高速、 高密、 超密封装、 多层 PCB 板设计技术 研究

21 世纪是技术高度发达的信息化世纪。全球 信息化的发展正在加快步伐。在这里起关键性作用 的技术是以集成电路为核心的电子信息技术。集成 电路测试技术是集成电路产业的重要基础技术, 它 贯穿集成电路设计、 生产、 应用的全过程。 ( Automated Test 2003 年 最 大 的 自 动 测 试 设 备 应用市场为混合信号集成电路测试, 其 Eguipment) 次为存储器测试, 分别占市场比重 30% 与 26% 。根 据我国台湾地区的数据显示混合信号集成电路测试 占的比例最大。 国际上先进的测试设备制造商都针对主流测试 市场推出中、 高档测试设备, 但任何一款测试设备都 不能满足不断更新的测试需求。为解决性能、 价格 的矛盾, 适应性和复杂性的矛盾, 各大测试设备制造 商 (如泰瑞达、 爱德万公司) 都先后提出测试系统的

1

国内外 ATE 发展源自文库状

快速编程, 以适应各种测试需求, 构造出最优性/ 价 比的系统。

表 1 2001 年至 2005 年我国台湾地区 ATE 市场 (千万美元) 2001 存储器测试 逻辑测试 混合信号测试 线性电路测试 其它测试 总计 8.23 6.34 9.44 0.20 5.62 2002 8.83 2.28 9.41 0.16 2003 9.67 2.82 2004 2005