基于直接数字合成技术的高速串行信号接收端容限测试新方法

PCIE_3.0简介及信号和协议测试方法

PCIE标准是由PCI-SIG组织制定,自从推出以来,1代和2代标准已经在PC和

Server上逐渐普及,用于支持高速显卡以及其它接口卡对于高速数据传输的要求。

出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIE 3.0,即

PCIE 3代的规范。目前,PCIE 3.0已经开始出现在一些高端的Server上,而在普通

战。

三、PCIE 3.0的测试

首先要说明的一点是,由于PCIE 3代目前只颁布了Base的规范(即芯片规

范),但CEM规范(即主板和插卡的规范)和测试规范还没有正式发布,所以下

面介绍的方法是基于目前的通用做法,以后随着规范的正式发布,具体测试方法可

能还有变化。

有1代、2代设备的兼容。别看这是个简单的目的,但实现起来可不容易。

我们知道,PCIE 2代在每对差分线上的数据传输速率是5Gbps,相对于1代提

高了1倍;而3代要相对于2代把速率也提高一倍,理所当然的是把数据传输速

率提高到10Gbps。但是就是这个10Gbps把PCI-SIG给难住了,因为PC和Server

PCIE 3.0简介及信号和协议测试方法

安捷伦科技(中国)有限公司:李凯

一、前言

PCI Express(简称PCIE)总线是PCI总线的串行版本,其采用多对高速串行的

差分信号进行高速传输,每对差分线上的信号速率可以是1代的2.5Gbps、2代的

5Gbps以及现在正逐渐开始应用的3代8Gbps。

作都由示波器软件计算,会大大影响测试速度。Agilent公司的90000A/90000X示

波器内部都有硬件的通道相减及S参数运算功能,可以大大提高测试的速度和效率。

一种高速SERDES抖动容限的高效仿真验证方法

一种高速SERDES抖动容限的高效仿真验证方法邵刚;田泽;李世杰;吕俊盛【摘要】文中针对高速SERDES总线接收端的验证提出了一种抖动容限验证方法,有效降低了流片风险。

由于受温度、布线、信道寄生的影响较大,高速SERDES需要保证在恶劣信道,尤其是大的抖动干扰时仍能稳定工作,设计阶段对接收电路抗抖动特性的评估是一个复杂的验证过程,鲜有报道。

文中基于对PCIE,SRIO,FC等信道和协议的研究,提出一种快速高效的RX端抖动容限的验证评估方法。

经验证采用该模型能方便准确地评估RX的特性,经电路流片后,实际测试表明,采用该方法评估的抖动容限结果与测试结果精确符合,可在设计阶段显著优化RX的性能,并大幅降低流片的风险。

%Aiming at high speed SERDES bus validation at the receiving end,put forward a jitter tolerance verification method,effectively reducing the risk of a flow chip. For many factor can affect SERDES,such as temperature,wiring and the parasitic of channel,it needs to work stably in many cases,the assessment of jitter characteristics for the receiving circuit in design phase is a complex validation process, with few reports. Based on the protocol of PCIE,SRIO and FC,a fast and efficient verification and evaluation method is proposed for RX end jitter tolerance. The model proposed in this method can accurately assess the convenient characteristics of RX. The test result indicates that the jitter tolerance evaluated by the model can tally with the test resultsaccurately,significantly optimizing the performance of RX in design stage and reducing the risk of flow chip largely.【期刊名称】《计算机技术与发展》【年(卷),期】2015(000)007【总页数】4页(P217-220)【关键词】SERDES;抖动容限;验证;CDR;时钟恢复电路【作者】邵刚;田泽;李世杰;吕俊盛【作者单位】中航工业西安航空计算技术研究所,陕西西安 710065;中航工业西安航空计算技术研究所,陕西西安 710065;中航工业西安航空计算技术研究所,陕西西安 710065;中航工业西安航空计算技术研究所,陕西西安 710065【正文语种】中文【中图分类】tP301高速数据通路是计算机通信的基础,制约着计算机和其他通信系统的I/O处理能力,而高速SERDES接口芯片的研究是其中非常重要的部分。

PRBS7

高速串行总线的常用测试码型类别:接口电路阅读:884本文讨论了高速串行链路中常用的测试码型伪随机码流的原理,以及不同的测试码型对物理层测试结果的影响。

高速串行总线的常用测试码型在当今的电信和计算机产品上,相比传统的并行总线,电路中的串行总线越来越多,速率越来越快。

比如通信产品中的10GBase-KR、CPRI2代,计算机中的PCIeGen2、SATA6G,存储产品中的SAS6G、FC8.5G,这些串行总线都陆续的跨过了5Gbps。

由于速率比较高,使得串行总线上的相关的收发器芯片(SERDES)、连接器、单板、背板的设计面临着越来越多的挑战。

对于这些高速串行总线的物理层测试,测试码型的选用至关重要,在很多串行总线的规范中对测试码型有严格的要求。

本文将对此进行探讨。

首先,串行总线的物理层测试通常分为发射机测试和接收机测试,又称为TX测试和RX测试。

发射机测试通常包括眼图、抖动、信号波形、幅度、上升下降时间等测试项目,接收机测试通常包括误码率、抖动容限、接收机灵敏度等测试项目。

对于眼图测试、误码率和抖动容限测试,最常用的测试码是伪随机码(PseudoRandomBinarySequence,简称PRBS),主要有PRBS7、PRBS15、PRBS23和PRBS31。

除了PRBS以外,K28.5、1010、CJPAT等码型在很多串行总线的物理层测试中都很常用,特别是计算机上的串行标准(比如SATA、USB3.0、SAS)的测试码型有所不同,在本文中主要讨论最常用的测试码型——PRBS。

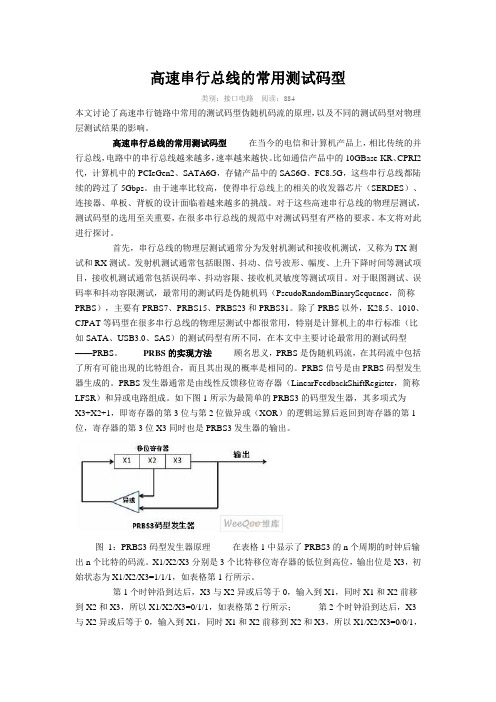

PRBS的实现方法顾名思义,PRBS是伪随机码流,在其码流中包括了所有可能出现的比特组合,而且其出现的概率是相同的。

PRBS信号是由PRBS码型发生器生成的。

PRBS发生器通常是由线性反馈移位寄存器(LinearFeedbackShiftRegister,简称LFSR)和异或电路组成。

如下图1所示为最简单的PRBS3的码型发生器,其多项式为X3+X2+1,即寄存器的第3位与第2位做异或(XOR)的逻辑运算后返回到寄存器的第1位,寄存器的第3位X3同时也是PRBS3发生器的输出。

一种SerDes的高效集成可测试性设计

一种SerDes的高效集成可测试性设计胡曙凡;田泽;邵刚【摘要】The expenses incurred in design and test for integrated circuit is more and more,along with the enhancement in operating speed and decreasing of the physical dimensions. Specially,when entering the deep sub-micron processing technique and ultra high integrated period,the function of IC is becoming more and more powerful,but it also brings out a series of design and testing problems. The theory and technology of testing and testable design have become an important research direction in VLSI field,and it is much more valuable in theory and practice. According to testing requirements on SerDes,for solving the problem of complex test of related parameters,a new plan of testability design is proposed. The realization of functions,such as loopback,test code generation,temperature detection and analog test bus,reduce a great large of the test difficulty in the test of SerDes. This method has simple structure and low consumption of re-sources,whicn is of good value.%随着集成电路工作速度的提高以及特征尺寸的缩小,芯片设计和测试的费用越来越高。

高速串行信号接收机测试

力劢

( 美国力科公 司成都代表处 , 1 0 ) 6 01 7

摘要: 本文 讨论 了高速 串行信 号接 收机测 试 的必要 性和 方法 , 绍 了一种针 对 当前 主 流 串行信 号标 准 的 介

测 试 仪 器 P R 3 ET 。

关键词 ; 高速 串行 信 号; 收机测试 ; 接 误码 率 测试; 动容 限测试 ; 抖 力科 P R 3 E T

这种仪器一般是误码率测试仪 ( i r r a Bt r t oR e E

Ts rB R 。简 单 地说 , et ,E T) e 误码 率 测 试 就是 发 送 已

知 数据 给被 测接 收 机芯 片 ,通过量 化 被错误 判 决数 据 的 比例来 衡量 接 收机 芯片 的性 能 。 在功 能上 , 误码

Hi h S e d S ra i n l c i e si g g p e e i lS g a Re ev r Te t n

W AN i ma L- i

( e ryC roai h n d fc ,1 0 7 L Co op rt nC eg uOf e 0 1 ) o i 6

它包 含 :

信 号检测 ( 大 , 衡 ) 放 均 ; 基 于锁相 环 ( L 的时 钟恢 复 ; P L)

判决 电路 ( 并转 串 , 线路 码解 码 ) 。 对接 收机 性 能 的测试 实 际就是 对 以上 三个 主要

环 , 图 5 aenG nrtr 出带 有 “ 如 。Ptr eea 发 t o 干扰 ”的信

行 接 收机测 试 。

{

1 可 以识 别 出多 小 幅度 的信 号 ,即接 收 灵 敏 )

度;

2) 时 钟恢 复 电路 中的锁 相 环 能否 去 除低 频 抖 动; 3) 够正 确识 别 出带有 多 大抖 动 的数 据 , 能 即抖

DDS外文翻译

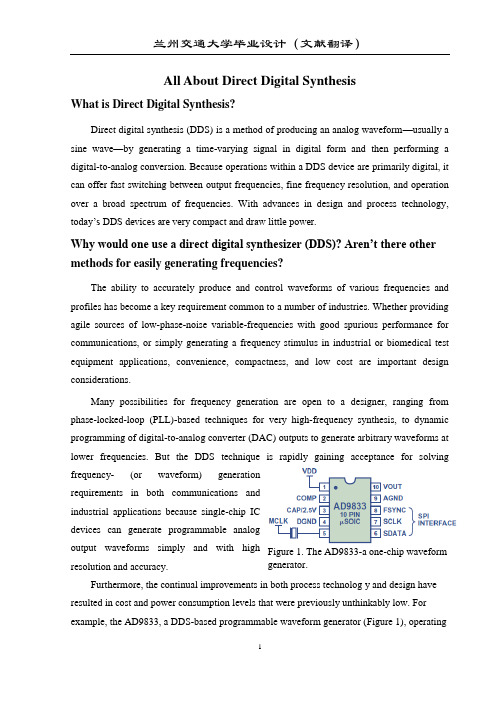

All About Direct Digital SynthesisWhat is Direct Digital Synthesis?Direct digital synthesis (DDS) is a method of producing an analog waveform —usually a sine wave —by generating a time-varying signal in digital form and then performing a digital-to-analog conversion. Because operations within a DDS device are primarily digital, it can offer fast switching between output frequencies, fine frequency resolution, and operation over a broad spectrum of frequencies. With advances in design and process technology, today’s DDS devices are very compact and draw little power.Why would one use a direct digital synthesizer (DDS)? Aren’t there other methods for easily generating frequencies?The ability to accurately produce and control waveforms of various frequencies and profiles has become a key requirement common to a number of industries. Whether providing agile sources of low-phase-noise variable-frequencies with good spurious performance for communications, or simply generating a frequency stimulus in industrial or biomedical test equipment applications, convenience, compactness, and low cost are important design considerations.Many possibilities for frequency generation are open to a designer, ranging from phase-locked-loop (PLL)-based techniques for very high-frequency synthesis, to dynamic programming of digital-to-analog converter (DAC) outputs to generate arbitrary waveforms at lower frequencies. But the DDS technique is rapidly gaining acceptance for solving frequency- (or waveform) generationrequirements in both communications andindustrial applications because single-chip ICdevices can generate programmable analogoutput waveforms simply and with high resolution and accuracy.Furthermore, the continual improvements in both process technolog y and design have resulted in cost and power consumption levels that were previously unthinkably low. For example, the AD9833, a DDS-based programmable waveform generator (Figure 1), operatingFigure 1. The AD9833-a one-chip waveformgenerator.at 5.5 V with a 25-MHz clock, consumes a maximum power of 30 milliwatts.What are the main benefits of using a DDS?DDS devices like the AD9833 are programmed through a high speed serial peripheral-interface (SPI), and need only an external clock to generate simple sine waves. DDS devices are now available that can generate frequencies from less than 1 Hz up to 400 MHz (based on a 1-GHz clock). The benefits of their low power, low cost, and single small package, combined with their inherent excellent performance and the ability to digitally program (and re-program) the output waveform, make DDS devices an extremely attractive solution—preferable to less-flexible solutions comprising aggregations of discrete elements. What kind of outputs can I generate with a typical DDS device?DDS devices are not limited to purelysinusoidal outputs. Figure 2 shows thesquare-, triangular-, and sinusoidal outputsavailable from an AD9833.How does a DDS device create asine wave?Here’s a breakdown of the internalcircuitry of a DDS device: its maincomponents are a phase accumulator, ameans of phase-to-amplitude conversion(often a sine look-up table), and a DAC. These blocks are represented in Figure 3.A DDS produces a sine waveat a given frequency. The frequency depends on two variables, the reference-clock frequency and the binar y number programmed into the Figure 2. Square-, triangular-, and sinusoidal outputs from a DDS.Figure 3. Components of a direct digital synthesizer.frequency register (tuning word).The binary number in the frequency register provides the main input to the phase accumulator. If a sine look-up table is used, the phase accumulator computes a phase (angle) address for the look-up table, which outputs the digital value of amplitude—corresponding to the sine of that phase angle—to the DAC. The DAC, in turn, converts that number to a corresponding value of analog voltage or current. To generate a fixed-frequency sine wave, a constant value (the phase increment—which is determined by the binary number) is added to the phase accumulator with each clock cycle. If the phase increment is large, the phase accumulator will step quickly through the sine look-up table and thus generate a high frequency sine wave. If the phase increment is small, the phase accumulator will take many more steps, accordingly generating a slower waveform.What do you mean by a complete DDS?The integration of a D/A converter and a DDS onto a single chip is commonly known as a complete DDS solution, a property common to all DDS devices from ADI.Let’s talk some more about the phase accumulator. How does it work?Continuous-time sinusoidal signals have a repetitive angular phase range of 0 to 2.The digital implementation is no different. The counter’scarry function allows the phase accumulator to act asa phase wheel in the DDS implementation.To understand this basic function, visualize thesine-wave oscillation as a vector rotating around aphase circle (see Figure 4). Each designated point onthe phase wheel corresponds to the equivalent pointon a cycle of a sine wave. As the vector rotatesaround the wheel, visualize that the sine of the anglegenerates a corresponding output sine wave. OneFigure 4. Digital phase wheel. revolution of the vector around the phase wheel, at aconstant speed, results in one complete cycle of the output sine wave. The phase accumulator provides the equally spaced angular values accompanying the vector’s linear rotation aroundthe phase wheel. The contents of the phase accumulator correspond to the points on the cycle of the output sine wave.The phase accumulator is actually a modulo- M counter that increments its stored number each time it receives a clock pulse. The magnitude of the increment is determined by the binary-coded input word (M). This word forms the phase step size between reference-clock updates; it effectively sets how many points to skip around the phase wheel. The larger the jump size, the faster the phase accumulator overflows and completes its equivalent of a sine-wave cycle. The number of discrete phase points contained in the wheel is determined by the resolution of the phase accumulator (n), which determines the tuning resolution of the DDS. For an n = 28-bit phase accumulator, an M value of 0000...0001 would result in the phase accumulator overflowing after 28 reference-clock cycles (increments). If the M value is changed to 0111...1111, the phase accumulator will overflow after only 2 reference-clock cycles (the minimum required by Nyquist). This relationship is found in the basic tuning equation for DDS architecture:n C out f M f 2⨯= where:fOUT = output frequency of the DDSM = binary tuning wordfC = internal reference clock frequency (system clock)n = length of the phase accumulator, in bitsChanges to the value of M result in immediate and phase-continuous changes in the output frequency. No loop settling time is incurred as in the case of a phase-locked loop.As the output frequency is increased, the number of samples per cycle decreases. Since sampling theory dictates that at least two samples per cycle are required to reconstruct the output waveform, the maximum fundamental output frequency of a DDS is fC/2. However, for practical applications, the output frequency is limited to somewhat less than that, improving the quality of the reconstructed waveform and permitting filtering on the output.When generating a constant frequency, the output of the phase accumulator increaseslinearly, so the analog waveform it generates is inherently a ramp.Then how is that linear output translated into a sine wave?A phase -to - amplitude lookup table is used to convert the phase-accumulator’sinstantaneous output value (28 bits for AD9833)—with unneeded less-significant bits eliminated by truncation—into the sine-wave amplitude information that is presented to the (10 -bit) D/A converter. The DDS architecture exploits the symmetrical nature of a sine wave and utilizes mapping logic to synthesize a complete sine wave from one-quarter-cycle of data from the phase accumulator. The phase-to- amplitude lookup table generates the remainingdata by reading forward then back through the lookup table. This is shown pictorially in Figure 5.Figure 5. Signal flow through the DDS architecture.关于直接数字频率合成器什么是直接数字频率合成器?直接数字频率合成器(DDS)是一种通过产生一个以数字形式时变的信号,然后执行由数字至模拟转换的方法。

高速信号反射问题分析及端接解决方案

关于高速信号的反射问题分析及端接解决方案摘要:随着现在信息化程度不断加深,数字信号的传输速度加快,信号的工作频率也在不断提高,信号完整性问题日益突出。

本文针对高速pcb设计中容易出现的反射问题,对反射产生的现象和原理进行相关分析,并讨论几种减弱反射的阻抗匹配和端接方案,分析每个方法的电路组成和使用优点和缺点。

关键词:信号完整性;高速信号;反射;端接中图分类号:tn79 文献标识码:a 文章编号:1007-9599 (2012)23-0000-02在电子行业迅速发展的今天,高速化和集成化已经涉及到了生活的各个方面。

随着信号频率的提高,电路板的集成度增加,pcb层数的增加,导致各种信号完整性问题。

在数字电路中,反射引起的信号过冲和下冲,主要容易导致电路噪声容限降低和输入输出延迟等问题,严重时更是会击穿元器件。

1 反射的形成和机理在信号传输过程中,路径上的每一步都有相应的瞬态阻抗,如果信号沿互联线传播时受到的瞬态阻抗发生变化,一部分信号将会被反射,另一部分发生失真并继续传播下去。

主要引起的原因就是阻抗不匹配,阻抗失配越严重,反射影响就越大。

在这里,定义反射系数为ρ,表示信号反射的大小。

计算公式为:。

式中:是反射电压;是入射电压;是传输线瞬态阻抗;是反射处瞬态阻抗。

做设计时,当信号源内阻小于传输线阻抗时,源端出现负反射,引起常说的振铃现象,也叫做过衰减。

当信号源内阻大于传输线阻抗时,源端发生正反射,信号会有攀升现象,也叫欠衰减。

在高速pcb设计时,当出现反射引起的信号完整性问题,如何根据问题波形处理阻抗匹配是关键。

2 阻抗匹配与端接方案对于阻抗不匹配引起的信号反射,目标是根据传输线的特性阻抗的值,在源端或者终端进行阻抗匹配,使电路满足源反射系数或者负载反射系数为0.常用的有两种方法:(1)使负载阻抗与传输线阻抗匹配,即并行端接;(2)使源阻抗与传输线阻抗匹配,即串行端接。

只要负载端或源端有一个达到反射匹配,反射将被消除。

通用宽带信号产生和分析方案

Models

Bandwidth

DPO7354C

3.5 GHz

DPO7254C

2.5 GHz

DPO7104C

1 GHz

DPO7054C

500 MHz

Sample Rate

(3, 4 ch) (2 ch) (1 ch)

10 GS/s 20 GS/s 40 GS/s

10 GS/s 20 GS/s 40 GS/s

AWG7000C

8 GS/s 和12 GS/s,每通道64M点深度 1 和2 通道 在两通道型号上可选的 16 & 24 GS/s 交 叉功能 10/8 bit 垂直分辨率 2 或 4 个标尺输出 序列,子序列和动态跳转能力 1GHz带宽下54dBc无杂散动态范围 调制带宽高达3.5GHz(1dB)

40M 20M 10M 200M / 100M / 50M >250,000 TekVPI

40M 20M 10M 200M / 100M / 50M >250,000 TekVPI

Max opt Record Length (1/2/3,4) Max Waveform Capture Rate Probing Interface

– – – – 支持射频校准——用户指定校准频率范围 支持中频校准——同时校准中频和混频器频响 基带校准——同时校准调制器和基带频响 实测校准结果:± 0.5dB的平坦度

14

完善简洁的预失真技术

15

校准

16

AWG在高速串行数字信号中的应用

Digital Patterns

1111100001111100000 Clk 01101001101101001 DATA 00101101100101101 DATA 10111001010111001 DATA n

基于14_nm_FinFET_工艺的高速串行收发器IP_核设计与实现

文章编号:2095-6835(2023)21-0001-05基于14nm FinFET工艺的高速串行收发器IP核设计与实现唐重林(牛芯半导体(深圳)有限公司上海分公司,上海201210)摘要:基于SMIC(中芯国际)14nm CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)工艺,设计实现了速率最高可达28Gb/s的串行收发器IP核(Intellectual Property core,一种具有知识产权的特定电路功能模组)。

为了能够处理复杂应用场景,损耗高于30dB的信号链路,发送端引入了多Tap(抽头系数)的FFE(Feed Forward Equalization,前向反馈均衡器),接收端引入连续线性均衡器和自适应的多Tap数字DFE(Decision Feedback Equalization,判决反馈均衡器),2种均衡相互配合,实现高速传输信号的均衡需求;为了降低功耗,发送器的驱动器避免使用传统的电流模结构,采用新型SST(Source-Series Terminated,源端串联端接)的驱动器结构,实现高速的同时,可以充分利用FinFET(Fin Field-Effect Transistor,鳍式场效应晶体管)的工艺特性,降低功耗且缩小芯片面积。

测试表明,该高速串行收发器IP核每通道面积为0.53mm2,每通道功耗为275mW,发送和接收电气特性均符合协议要求。

关键词:高速;串行收发器;均衡;IP核中图分类号:TN43文献标志码:A DOI:10.15913/ki.kjycx.2023.21.001在当今移动和通信系统中,高速串行接口已几乎全部取代并行拓扑结构,广泛应用于高速通信领域,如电脑显示互连、高速背板互连和存储数据交换、高速网络等。

高速接口中最核心的串行收发器即SerDes (Serializer/Deserializer,串行器/解串器)技术决定了整个串行数据通信的性能和质量。

一种高速Serdes接口测试的ATE设计

Abstract:TWith the rapid development of the integrated circuit industry, standard serial interfaces such as PCI-Express bus, 100 GBASE Ethernet, OIF-CEI backplane transmission are widely used in integrated circuits, and the interface transmission rate has reached 16 Gbps to 56 Gbps. The mainstream integrated circuit automatic test equipment in the market is no longer able to meet such high-speed Serdes interface test requirements. Therefore, in order to ensure full speed testing and high coverage parameter level testing of Serdes interface, a new automatic testing system is designed in this paper. With combines automatic test equipment (ATE) and BERT to test key parameters such as eye diagram, jitter, ber and jitter tolerance of high-speed Serdes interface, and improves chip test coverage and result reliability. Key words:serdes; ATE;BERT; loopback; SmarTest; SCPI

一种数字体制测控系统高速数据传输方法

一种数字体制测控系统高速数据传输方法田之俊1,王涛2,康宁1(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.中国人民解放军63769部队,陕西西安710043)收稿日期:2021-12-100引言航天测控系统是航天工程的重要组成部分,是天地联系的唯一通道,是保障飞行器正常运行、充分发挥其应用效能不可或缺的保证[1]。

传统的测控系统都是模拟体制,信道设备量大、运行模式单一、可靠性较差。

随着数字技术的发展,人们的研究方向逐步转入到基于软件无线电技术的全数字系统。

根据软件无线电的要求,信号在天线后端直接数字化,即对射频信号直接采样,在数字域中灵活完成各种相关的信号处理算法[2]。

数字化方案的提出,除了对射频采样技术提出了更高的要求,同时对宽带数据的高速传输也提出了更高的挑战。

特别是随着航天测控技术不断发展,遥测、数传的数据量不断增加,测控带宽也越来越高,对高速数据传输的速率、效率、可靠性和扩展性等要求也逐步提高。

1常用高速数据传输方法目前常用的高速数据传输大都采用高速串行接口协议,包括PCI-Express 、RapidIO 、万兆以太网和Aurora 等,其中前2种协议大都用于短距离的板间通信、交换方式传输[3-4],万兆以太网和Aurora 可通过光纤完成较远距离的传输。

1.1万兆以太网万兆以太网是以太网的最新技术,其传输速度是千兆以太网的10倍,理论最高传输速度为l0Gbps,可以满足高速传输系统对传输速率的要求[5]。

万兆以太网主要使用光纤作为传输介质,非常适合海量数据的高速、低损耗和远距离传输。

由于同属IEEE802.3协议,万兆网协议继承了先前以太网标准的优点,并且具有良好的向前兼容性,保留了传统以太网协议中MAC层的功能以及帧格式[6]。

万兆以太网以其良好的通用性在多种领域得到了广泛应用。

但由于其协议的复杂性,同时带来一系列问题,如实现难度大、协议开销大等[7]。

特别是在测控系统中,需要考虑100MHz 带宽的数据传输,按照数据采样位数16bit估算,根据那奎斯特采样定理,数据规模大于5Gbps,对万兆以太网的有效数据传输效率提出了很大挑战,而且在此情况下数据传输带宽余量不足,扩展性较差。

泰克面向高速串行数据总线测试推新品

能够 生 成高 速 、真 实 波 形 的 AWG,包 括 预 加 重 / 去 加重 以及 高 达 1 Gb s的多 电 平 信 号 。 0 p

该解 决 方 案 中包 括 4个模 块 。8 El 双 通道 真 差 分 0 0 T DR模 块可 提 供 1 p 入 射 和 1 p 反 射 T 2s 5s DR上升 时 间 、

泰克 新 型 A G 0 0系列 任 意 波形 发 生器 具 有 业 产 品 线总 经 理 B inM. ec W 70 r R ih表 示 ,“ 是 ,T a 但 DR方 案

内最 快速 度 , 围最 高 为 7 d 0 B,不 如 传 统 VNA 8 d 0 B的动 态

数 千 兆 串 行标 准 的 出 现使 得 功 率预 算和 时序 容 限

系 统 时面 临 着 巨大 的技 术 挑 战。 针对 与 此 , 克 公 司推 下 降 , 此 , 确 分 析 时 域和 频 域 中 的信 号 路径 和互 连 泰 因 准 出 最新 的任 意 波 形 发 生 器 和 数 字 串 行 分 析 示 波器 ,以 情 况 ,对 于 全 面 了 解 高速 串行 设 计 中 信 号 损失 和 串扰 满足 高 速 串行 数 据 总 线 的设 计 和 测试 要 求 。

射 频设 备 的 测 试 要求 而 设 计 。凭 借 58 H 的带 宽 、1 范 围 。不 过 7 d . z G 0 0 B非 常 适合 串行 数 据 应 用 ,而 VN A更

位分 辨 率 以及 高达 2 GSs 0 /的取 样 速 率 , AW G7 0 是 唯 适 于微 波 和 R 00 F应 用 。 ”

维普资讯

泰克面 向高速 串行数 据总线测 试推新 品

数 字通 信 技 术 正 在 从 并 行 结 构 转 为 串 行 结 构 ,工

一种高速Serdes接口测试的ATE设计

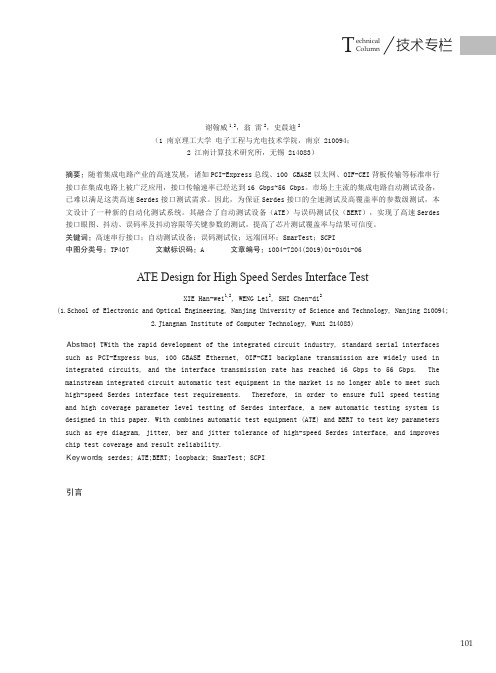

一种高速Serdes接口测试的ATE设计谢翰威;翁雷;史晨迪【摘要】随着集成电路产业的高速发展,诸如PCI-Express总线、100 GBASE以太网、OIF-CEI背板传输等标准串行接口在集成电路上被广泛应用,接口传输速率已经达到16 Gbps~56 Gbps.市场上主流的集成电路自动测试设备,已难以满足这类高速Serdes接口测试需求.因此,为保证Serdes接口的全速测试及高覆盖率的参数级测试,本文设计了一种新的自动化测试系统.其融合了自动测试设备(ATE)与误码测试仪(BERT),实现了高速Serdes接口眼图、抖动、误码率及抖动容限等关键参数的测试,提高了芯片测试覆盖率与结果可信度.【期刊名称】《环境技术》【年(卷),期】2019(037)001【总页数】6页(P101-106)【关键词】高速串行接口;自动测试设备;误码测试仪;远端回环;SmarTest;SCPI 【作者】谢翰威;翁雷;史晨迪【作者单位】南京理工大学电子工程与光电技术学院,南京 210094;江南计算技术研究所,无锡 214083;江南计算技术研究所,无锡 214083;江南计算技术研究所,无锡214083【正文语种】中文【中图分类】TP407引言在摩尔定律的指引下,集成电路大多向着高密度、高速率的方向发展,电路间的数据传输要求显得越来越高。

以Serdes接口为主的串行通信技术利用差分传输和时钟数据恢复上的优势,逐步成为了主流的高速IO接口,在以太网、背板传输、设备总线等技术中被广泛应用。

因此,对这类Serdes接口测试技术的研究也就显得十分重要。

由于常用的自动测试设备(如V93000、J750等)因其测试速率、定时精度、抖动注入等均不能够满足高速Serdes接口的测试需求,市面上通常采用了由“设计保证”、“功能验证”的方式来判定芯片的好坏。

但随着信号工作速率越来越高,对抖动及噪声的敏感度越来越严苛,均衡、去加重等技术的引入也增加了电路的复杂程度,仅依靠功能测试的方式已经显得不够可靠,基于参数级的性能测试需求变得越来越迫切。

如何准确进行PCIe5.0高速测试及误码分析

如何准确进⾏PCIe5.0⾼速测试及误码分析为应对信号衰减问题,PCIe 5.0对信道和连接器损耗与反射提出了更严格的要求,并且对接收器和发送器的均衡也做了⼀些修改。

此外,数据速率从16 GT/s提升⾄32 GT/s,翻了⼀番,但对上升/下降时间变陡、单位间隔(UI)变窄以及插⼊损耗变⼤所引起的问题,却没有提出什么创新的⽅法来补偿。

那么GT/s的提升意味着什么呢?进⾏全⾯Serdes测试的必要要确保PCIe 5.0设计符合规范,即所设计产品要通过PCI-SIG主持的合规性⼯作间的PCI-SIG互操作性测试,⼯程师们必须进⾏全⾯的Serdes测试。

PCIe 5.0测试需要的设备包括:误码率测试仪(BERT)脉冲模式发⽣器(PPG),⽤于⾼精度的特定信号损伤测量;BERT误码检测器(ED),⽤以分析Serdes输出的误码率(BER);另外还会⽤到采样带宽⼤于50 GHz的实时⽰波器。

⽽对于最复杂的Serdes测试,即链路均衡训练,BERT需要仿真⼀个参考Serdes。

PPG和ED必须在PCIe 5.0协议栈的PHY逻辑⼦块级别与被测设备(DUT)进⾏交互(图1)。

图1:PCIe 5.0多层协议栈32 GT/s时NRZ⾯临的挑战从16 GT/s的PCIe 4.0架构升级到32 GT/s的PCIe 5.0架构,其最⼤挑战是在BER≤10-12的条件下,能够在⾼达36dB的损耗下⼯作。

为了解决与损耗相关的问题,⼤多数运⾏速度超过30 GT/s 的标准都采⽤PAM-4,以将⼯作带宽减少两倍,但代价是信噪⽐降低了9.5 dB以上。

不过,PCIe 5.0技术仍然采⽤逻辑仿真和基带⾮归零(NRZ)调制⽅案,以⾼电平表⽰逻辑 1 ,低电平表⽰逻辑 0 。

损耗过⼤可能导致基于PCIe 5.0架构的后均衡眼图开启电压低⾄10 mV。

如此⼩的电压摆幅需要⾮常灵敏的电压限幅器。

⽽且,为了容纳较长的电路板,当损耗超过-36 dB或信号通过两个或多个连接器传播时,还需要重新配置定时器。

高速信号抖动容限测试技术

Pre-Emphasis BitAlyzer • 基本的误码仪和示 • 配合BERTScope 码型发生器使用 波器 • 最低码速率100K, • 提高输出加重以克 服通道损耗 适合于卫通应用 • Rx端容限中使用 Linear Equalizator • 复杂线性均衡 • 信道模拟

ቤተ መጻሕፍቲ ባይዱ1.5G/1.6G

Vertical slice

Eye height at 1012 BER level

Beyond the BERT...

使用BERTScope深入分析误码率事件

规范要求的接口一致性验证

模板测试

看到BER Contour之后,可以进行Mask测试,看看是否满足一定误码率 前提下的Mask要求。 如果BER Contour压到Mask的话,可以通过将设置BERTScope的 sampler到压点的位置上,进而深入分析误码出现的规律。

BERTScope

PatternPro

PPG4001 40 Gb/s Pattern Generator

X

X X

X X X

03/2014 ©Tektronix 65W-28713-3

27

误码率分析工具带来的启示 – 误码定位

如果是数字调制呢?

误码率分析工具带来的启示 – 误码率带状图

误码率分析工具带来的启示 – 无误码间隔图 (Error Free Interval)

将busrt中的最小无误码长度 设为1,实际观察的就是连续 出现误码的统计 如果连续出现的误码不相关? 判定连续误码的相关,找到系 统问题 1500 bit的前向纠错 突发长度统计中基本都是 1500bit的倍数 FEC算法出现问题

USB3.0认证的新测试要求和应对措施详解

USB3.0认证的新测试要求和应对措施详解【导读】随着主流市场演进到SuperSpeed USB,许多设计团队正力图加快设计认证。

但是你了解USB3.0认证的最新测试要求么?只有掌握好游戏规则,才能赢得游戏。

本文将为您提供专家建议参考,帮助您轻松完成这一过程。

尽管市场上已经出现了早期的USB 3.0产品,但主流市场转向SuperSpeed USB还有待时日。

部分原因在于,USB 2.0接口无所不在,且生产成本低廉。

高带宽设备(如摄像机和存储设备)已经率先演进到SuperSpeed USB。

但就目前而言,基于成本因素考虑,USB3.0实施仍限于较高端的产品。

大规模部署任何新的行业标准(包括USB3.0)都存在内在挑战。

此外,USB2.0到USB 3.0并非简单的跳跃,其性能提高了十倍之多。

尽管性能得到大幅度提升,但消费者对低成本互连设备的预期并没有改变。

这就给工程师们带来了明显的压力,需要在一个原本速度很低的信号通道上传输高速率信号,同时要在各种条件下保证可靠性、互操作能力和高性能。

为保证物理层(PHY)一致性和认证,测试变得空前关键或重要。

USB 3.0拥有许多其它高速串行技术(如PCI Express和串行ATA)共有的特点:8b/10b编码,明显的通道衰减,扩频时钟。

本文将介绍一致性测试方法及怎样对发射机、接收机及线缆和互连进行最精确的、可重复的测量。

在掌握了这些窍门之后,您便可以更有效地准备SuperSpeed PIL(Platform Integration Lab)之行了。

High Speed Vs. SuperSpeedUSB 3.0满足了市场对于更高带宽下实时体验应用的需求。

目前USB设备达数十亿,因而USB 3.0也提供了向下兼容能力,支持传统USB 2.0设备。

然而,USB 2.0和3.0在物理层有多种差异(表1)。

表1. USB 2.0 和SuperSpeed USB物理层区别SuperSpeed USB一致性测试已经有明显变化,以适应更高速接口带来的新挑战。

高速串行信号的接收端测试

Tቤተ መጻሕፍቲ ባይዱansmitter

Pre-emphasis De-emphasis Pre-overshoot

Serial Data Transfer Link

Receiver

Amplifier,Equalization

Serializer; 8B/10B Encode;

Scramble; Transimit FIFO

并行数据转换成串行数据并辅以相应的编码,可以以 LVDS 或者 CML 等差分电平的方 式实现高速、高可靠的传输,传输通道结构也可实现极大的简化。从上述结构图中我们可以 看出,串行数据传输链路中是没有专门的时钟信号传输的,那么接收端如何实现对串行数据 的解串、解码呢?事实上接收端会有专门的 CDR(Clock Data Recovery )电路用以从串行 数据中恢复出时钟。因此,一个最典型的串行数据链路的发送端的内部结构至少应包括:串 行化(Serializer)电路、8B/10B 编码电路(通常在 8B/10B 编码电路之前还有一级 Scramble 编码电路以减小信号的高频谐波分量及信号失真);接收端应至少包括解串电路 (Deserializer)、8B/10B 解码电路、CDR 时钟数据恢复电路等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

般的数字信号 源能 够对 比较单一 公式或者算 法去任意定义 。

升时间 , 均可以通过泰克的S r l p es ei X rs a

的规 律性变化的数字信号进行模拟 ,如

直接合成信号源除 了能够 合成含任 软件方便快捷的进行定义 ,并可以实时

信号中含有随机噪声 ,或者信号 的抖 动 何抖动规律 或者噪声的信号 ,建立随机 模拟实现效果 ,如 图 3 所示。 以单一的正弦规 律或 者三角波规律 变化 抖 动和确定性 抖动 的影 响模 型 , 以定量 对于去加重信号的直接合成方法完

技术正在 改变这一切 , 接合成工具 可 成一 个 测 试信 号 ,拥有 所 需 的全 部 时 在相对 宽的频率范 围内 ,而降低频谱 的 直

S( 。 以帮助设计人 员创建现实程度更高 的信 序 、幅度和失真 特点 ,而不是像一 般的 尖峰值 ,一般称为 S C 扩 频时钟)

号 ,并 极 大 地 减 少 复 杂 的 测 试 设 置 和 多 数字信号 源那…

一

维普资讯

专题特写:高速串行数据测试

传 统数 字信 号源 对串行信 号特性 进行模 以定义任 何波形 ,这些样点可 以从示波

拟 的方 法

一

对于合成信号的速率 、抖动注入的

器 采 集 的 实 际 波 形 中 获 得 ,也 可 以 采 用 频 率 和 幅 度 、噪 声 的 幅 度 以 及 信 号 的 上

改善接收机 串行信号完 全 由简单 的二 进制数 l 实际工作环境中高速串行信号的模拟特性 偿传输线对高频分量的衰减 ,

和0 组成 。为什 么要 使用直接数 字合成

由于传输介 质的衰减 以及反射会导 输入上的信号保真度。 但必须在设计阶段

在调 模拟波形来表 示数字数据呢 ?这是 因为 致信号 不同程度 的劣化 ,具体 表现为抖 全面评估串行设备对去加重的响应 。 调节去加 在数字信号 中隐含 的是 模拟事件 。书本 动 的增 大 ,信号 幅度 的衰 减等 。在实 际 试过程中可 以根据实际的情况 , 上理想的数 字信号的零上升时 间和完美 工作环境 中 ,随着信号速 率的提高 ,传 重的比例以获得最好的传输效果。

为 了减 少传输介质的衰减而造成 的

种设备 共用可能 引入 的测量误差 。

理 想 信 号 ,然 后 再 通 过 各 种 组 合 去 劣 化 波形的畸变和 II S 的抖动成分的增加 ,提

信号来 模拟真实 环境 。

直接数字合成方式产生信号 的意 义

高传输过程 中的信号完整性 。 业界普遍使 用 了去加重(e mp ai) d —e h s 的技术 ,以补 s

由于时钟 芯片的抖动影 响 ,电源平

用高速 串行信号标 准的芯片的接收端测 其他缺点 ,每 个缺点都 会给信号带 来影 面 的波动干扰 ,以及 串行信号 周边低频

试都需要激励 信号源 ,一直以 来 ,设 计 响。直接 合成 信号源 的优 点是能够 完全 但 高能量的信号 的 串扰 ,这些 都会导致 人 员几乎 完全依赖数字信 号发生器 ,为 “ 模仿 ” 际信号 的模拟特 点 , 实 可以 任意 串行信号发 生时序上的变化 ,这种变化 串行测试生成 二进制信号 。他们在数 字 控 制 信 号 的 上 升 时 间 、 冲 形 状 、 迟 、 表 现为信号边沿 的抖 动有规律的跟随着 脉 延

信号 中运 用输 入信号 的幅度调节 、注 入 畸变 、抖动变化规 律等 ,这正是严 格的 干扰信号 的变化而变化 ;或者 为了减少 MI 抖动 、相位偏 移调节等 手段来进行 比较 串 行 总 线 测 试 所 需 的 操 作 。 泰 克 的 E 的辐射 ,特意在时钟 信号 上叠加一 恶劣 的工作环境的模拟 ,以考验接收端 AWG7 0 是使用直接 数字合成 的方 个低频 的调 制 ,使信号 的频 率随着调制 0 0就 的接收容 限。但是 ,信 号源领域 中的新 式产生信号 的任意波 形发生器 ,可以生 信号而 有规 律的升高或 降低 ,频谱扩散

引言

一

般会随信号速率和传输路径 长度成比

例 劣 化 。在 大 规 模 的 工 程 化 生 产制 造 过

程 中 ,可能 会牺 牲 P CB、连接 器、线缆

的性能来换取成 本的优势 ,这 就更增加

的 “ 平顶”都是虚拟 的 ,实际的工作 环 了接收端的容 限要求 。

在系统或者 芯片的验证过 程 中,使 境具 有噪声 、串扰 、反射 、电源变化 和

的情况。可以用 多个仪器混 合注 入不同 方式和 定性 方式改变施加 的效应 外,还 全不 同于数 字信号源 ,但得到的结果确

特性的抖动和噪声实现 。但如果信 号的 能模拟信号在传输时 由于特定 介质的不 完全相 同。AWG存储 的信号 已经包含

劣化是不规则的或者以比较复杂的规律 同特性导 致的衰减 、反射 、串扰等信号 “ 去加重” 特性 , 因此不需要生成及外部 变化的 ,如在正弦抖动 中含有 电源 或者 的畸 变 。而 且 不 需 要 使 用 复 杂 的外 部 设 组合两条数据流 ,以得到合成信号 如 其他高能量信号干扰 引起 的抖动 ,数字 备去注 入抖动或者噪声 ,所有 的信号特 图 4中单一通 道的输 出就可以实现。而

维普资讯

专题特写:高速串行数据测试

基于直接数字合成技术的高速串行信号 接收端容限测试新方法

泰 克科技 ( 中国)有限公 司高级应用工程 师 曾 志

输 介质对信号 的影响越来越 明显 ,信号

主要 介绍 串行信 号 的特性 .传 统数 字信 号源 实现 串行信 号 接 收端容 限测试 的方法及 其局 限 .直接 合成信 号 源的 实现 方法 及 其优 势 l以及模拟 信号 源 直接合成 的方式在 |前 比较 流行 的 串行 标 准 中如 S A.Ds l ot D 等 的实 际 应用 AT i a Pr py H MI