规格书:H27U1G8F2B (Rev0.1)-nand flash

HY27UF081G2A_NAND_Flash数据手册

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for use of circuits described. No patent licenses are implied.Rev 0.4 / Jun. 2007 1HY27UF(08/16)1G2A Series1Gbit (128Mx8bit / 64Mx16bit) NAND Flash1Gb NAND FLASHHY27UF081G2A HY27UF161G2ARev 0.4 / Jun. 200721Gbit (128Mx8bit / 64Mx16bit) NAND FlashDocument Title1Gbit (128Mx8bit / 64Mx16bit) NAND Flash Memory Revision HistoryRevision No.History Draft DateRemark0.01Initial Draft.Dec. 28. 2005Preliminary0.11) Change NOP2) Change AC CharacteristicsMay. 18. 2006Preliminary0.21) Delete Memory array map 2) Change AC Characteristics3) Correct copy back function Oct. 02. 2006Preliminary0.31) Change 1Gb Package Type- FBGA package is added - Figure & dimension are changed 2) Delet PreliminaryNov. 23. 20060.41) Correct figure 19Jun. 11. 2007tOH Before 12After10tCStCEA tREA Before 253525After202520Rev 0.4 / Jun. 200731Gbit (128Mx8bit / 64Mx16bit) NAND FlashFEATURES SUMMARYHIGH DENSITY NAND FLASH MEMORIES - Cost effective solutions for mass storage applications NAND INTERFACE - x8 or x16 bus width.- Multiplexed Address/ Data- Pinout compatibility for all densitiesSUPPLY VOLTAGE- VCC = 2.7 to 3.6V : HY27UFxx1G2A Memory Cell Array= (2K+64) Bytes x 64 Pages x 1,024 Blocks = (1K+32) Bytes x 64 Pages x 1,024 BlocksPAGE SIZE- x8 device : (2K+64 spare) Bytes : HY27UF081G2A - x16 device : (1K+32 spare) Bytes : HY27UF161G2ABLOCK SIZE- x8 device: (128K + 4K spare) Bytes - x16 device: (64K + 2K spare) Words PAGE READ / PROGRAM - Random access: 25us (max.) - Sequential access: 30ns (min.) - Page program time: 200us (typ.)COPY BACK PROGRAM MODE- Fast page copy without external bufferingCACHE PROGRAM- Internal (2048+64) Byte buffer to improve the program throughputFAST BLOCK ERASE- Block erase time: 2ms (Typ.)STATUS REGISTER ELECTRONIC SIGNATURE - 1st cycle: Manufacturer Code - 2nd cycle: Device Code- 3rd cycle: Internal chip number , Cell Type, Number of Simultaneously Programmed Pages.- 4th cycle: Page size, Block size, Organization, Spare sizeSERIAL NUMBER OPTION CHIP ENABLE DON’T CARE - Simple interface sith microcontrollerDATA RETENTION- 100,000 Program/Erase cycles (with 1bit/528byte ECC) - 10 years Data RetentionPACKAGE- HY27UF(08/16)1G2A-T(P): 48-Pin TSOP1 (12 x 20 x 1.2 mm)- HY27UF(08/16)1G2A-T (Lead)- HY27UF(08/16)1G2A-TP (Lead Free)- HY27UF081G2A-S(P): 48-Pin USOP1 (12 x 17 x 0.65 mm)- HY27UF081G2A-S (Lead)- HY27UF081G2A-SP (Lead Free) - HY27UF081G2A-F(P): 63-Ball FBGA (9 x 11 x 1.0 mm)- HY27UF081G2A-F (Lead)- HY27UF081G2A-FP (Lead Free)Rev 0.4 / Jun. 200741Gbit (128Mx8bit / 64Mx16bit) NAND Flash1. SUMMARY DESCRIPTIONThe Hynix HY27UF(08/16)1G2A series is a 128Mx8bit with spare 4Mx8 bit capacity. The device is offered in 3.3V Vcc Power Supply.Its NAND cell provides the most cost-effective solution for the solid state mass storage market. The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased.The device contains 1024 blocks, composed by 64 pages consisting in two NAND structures of 32 series connected Flash cells.A program operation allows to write the 2112-byte page in typical 200us and an erase operation can be performed in typical 2ms on a 128K-byte(X8 device) block.Data in the page can be read out at 30ns cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input. This interface allows a reduced pin count and easy migration towards different densities, without any rearrangement of footprint.Commands, Data and Addresses are synchronously introduced using CE, WE, ALE and CLE input pin. The on-chip Pro-gram/Erase Controller automates all program and erase functions including pulse repetition, where required, and inter-nal verification and margining of data.The modify operations can be locked using the WP input pin or using the extended lock block feature described later .The output pin R/B (open drain buffer) signals the status of the device during each operation. In a system with multi-ple memories the R/B pins can be connected all together to provide a global status signal.Even the write-intensive systems can take advantage of the HY27UF(08/16)1G2A extended reliability of 100K pro-gram/erase cycles by providing ECC (Error Correcting Code) with real time mapping-out algorithm.The chip could be offered with the CE don’t care function. This function allows the direct download of the code from the NAND Flash memory device by a microcontroller , since the CE transitions do not stop the read operation.The copy back function allows the optimization of defective blocks management: when a page program operation fails the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase.The cache program feature allows the data insertion in the cache register while the data register is copied into the flash array. This pipelined program operation improves the program throughput when long files are written inside the memory. A cache read feature is also implemented. This feature allows to dramatically improve the read throughput when consecutive pages have to be streamed out.The HYNIX HY27UF(08/16)1G2A series is available in 48 - TSOP1 12 x 20 mm, 48 - USOP 12 x 17 mmm, FBGA 9 x 11 mm.1.1 Product ListPART NUMBER ORIZATIONVCC RANGE PACKAGEHY27UF081G2A x8 2.7V - 3.6 Volt63FBGA / 48TSOP1 / 48USOP1HY27UF161G2Ax1648TSOP1Rev 0.4 / Jun. 200751Gbit (128Mx8bit / 64Mx16bit) NAND FlashIO15 - IO8Data Input / Outputs (x16 only)IO7 - IO0Data Inputs / Outputs CLE Command latch enable ALE Address latch enable CE Chip Enable RE Read Enable WE Write Enable WP Write Protect R/B Ready / Busy Vcc Power Supply Vss Ground NCNo ConnectionTable 1: Signal NamesRev 0.4 / Jun. 200761Gbit (128Mx8bit / 64Mx16bit) NAND FlashFigure 2. 48TSOP1 Contactions, x8 and x16 DeviceFigure 3. 48USOP1 Contactions, x8Rev 0.4 / Jun. 200771Gbit (128Mx8bit / 64Mx16bit) NAND FlashFigure 4. 63FBGA Contactions, x8 Device (Top view through package)Rev 0.4 / Jun. 200781Gbit (128Mx8bit / 64Mx16bit) NAND Flash1.2 PIN DESCRIPTIONPin Name DescriptionIO0-IO7IO8-IO15(1)DATA INPUTS/OUTPUTSThe IO pins allow to input command, address and data and to output data during read / program operations. The inputs are latched on the rising edge of Write Enable (WE). The I/O buffer float to High-Z when the device is deselected or the outputs are disabled.CLECOMMAND LATCH ENABLEThis input activates the latching of the IO inputs inside the Command Register on the Rising edge of Write Enable (WE).ALEADDRESS LATCH ENABLEThis input activates the latching of the IO inputs inside the Address Register on the Rising edge of Write Enable (WE).CECHIP ENABLEThis input controls the selection of the device. When the device is busy CE low does not deselect the memory.WEWRITE ENABLEThis input acts as clock to latch Command, Address and Data. The IO inputs are latched on the rise edge of WE.REREAD ENABLEThe RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.WP WRITE PROTECTThe WP pin, when Low, provides an Hardware protection against undesired modify (program / erase)operations.R/B READY BUSYThe Ready/Busy output is an Open Drain pin that signals the state of the memory.VCC SUPPLY VOLTAGEThe VCC supplies the power for all the operations (Read, Write, Erase). VSS GROUNDNCNO CONNECTIONTable 2: Pin DescriptionNOTE:1. A 0.1uF capacitor should be connected between the Vcc Supply Voltage pin and the Vss Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.Rev 0.4 / Jun. 200791Gbit (128Mx8bit / 64Mx16bit) NAND FlashIO0IO1IO2IO3IO4IO5IO6IO71st Cycle A0A1A2A3A4A5A6A72nd Cycle A8A9A10A11L (1)L (1)L (1)L (1)3rd Cycle A12A13A14A15A16A17A18A194th CycleA20A21A22A23A24A25A26A27Table 3: Address Cycle Map(x8)NOTE:1. L must be set to Low.IO0IO1IO2IO3IO4IO5IO6IO7IO8-IO151st Cycle A0A1A2A3A4A5A6A7L (1)2nd Cycle A8A9A10L (1)L (1)L (1)L (1)L (1)L (1)3rd Cycle A11A12A13A14A15A16A17A18L (1)4th CycleA19A20A21A22A23A24A25A26L (1)Table 4: Address Cycle Map(x16)NOTE:1. L must be set to Low.FUNCTION1st CYCLE2nd CYCLE3rd CYCLE4th CYCLEAcceptable commandduring busyREAD 100h 30h --READ FOR COPY-BACK 00h 35h --READ ID 90h ---RESETFFh ---YesPAGE PROGRAM 80h 10h --COPY BACK PGM 85h 10h --BLOCK ERASE60h D0h --READ STATUS REGISTER 70h ---YesCACHE PROGRAM 80h 15h --RANDOM DATA INPUT 85h ---RAMDOM DATA OUTPUT 05h E0h --CACHE READ START 00h 31h --CACHE READ EXIT34h---Table 5: Command SetRev 0.4 / Jun. 2007101Gbit (128Mx8bit / 64Mx16bit) NAND FlashCLE ALE CE WE RE WP MODE H L L Rising H X Read ModeCommand Input L H L Rising H X Address Input(4 cycles)H L L Rising H H Write ModeCommand Input L H L Rising H HAddress Input(4 cycles)L L L Rising H H Data Input L L L (1)H Falling X Sequential Read and Data Output L L L H H X During Read (Busy)X X X X X H During Program (Busy)X X X X X HDuring Erase (Busy)X X X X X L Write Protect XXHXX0V/Vcc Stand ByTable 6: Mode SelectionNOTE:1. With the CE high during latency time does not stop the read operationRev 0.4 / Jun. 2007111Gbit (128Mx8bit / 64Mx16bit) NAND Flash2. BUS OPERATIONThere are six standard bus operations that control the device. These are Command Input, Address Input, Data Input, Data Output, Write Protect, and Standby.Typically glitches less than 5 ns on Chip Enable, Write Enable and Read Enable are ignored by the memory and do not affect bus operations.2.1 Command Input.Command Input bus operation is used to give a command to the memory device. Command are accepted with Chip Enable low, Command Latch Enable High, Address Latch Enable low and Read Enable High and latched on the rising edge of Write Enable. Moreover for commands that starts a modify operation (write/erase) the Write Protect pin must be high. See figure 6 and table 13 for details of the timings requirements. Command codes are always applied on IO7:0, disregarding the bus configuration (X8/X16).2.2 Address Input.Address Input bus operation allows the insertion of the memory address. To insert the 28 addresses needed to access the 1Gbit 4 clock cycles (x8 version) are needed. Addresses are accepted with Chip Enable low, Address Latch Enable High, Command Latch Enable low and Read Enable High and latched on the rising edge of Write Enable. Moreover for commands that starts a modify operation (write/erase) the Write Protect pin must be high. See figure 7 and table 16 for details of the timings requirements. Addresses are always applied on IO7:0, disregarding the bus configuration (X8/X16).2.3 Data Input.Data Input bus operation allows to feed to the device the data to be programmed. The data insertion is serially and timed by the Write Enable cycles. Data are accepted only with Chip Enable low, Address Latch Enable low, Command Latch Enable low, Read Enable High, and Write Protect High and latched on the rising edge of Write Enable. See figure 8 and table 13 for details of the timings requirements.2.4 Data Output.Data Output bus operation allows to read data from the memory array and to check the status register content, the lock status and the ID data. Data can be serially shifted out toggling the Read Enable pin with Chip Enable low, Write Enable High, Address Latch Enable low, and Command Latch Enable low. See figures 9,10,12,13 and table 13 for details of the timings requirements.2.5 Write Protect.Hardware Write Protection is activated when the Write Protect pin is low. In this condition modify operation do not start and the content of the memory is not altered. Write Protect pin is not latched by Write Enable to ensure the pro-tection even during the power up.2.6 Standby.In Standby mode the device is deselected, outputs are disabled and Power Consumption is reduced.Rev 0.4 / Jun. 2007121Gbit (128Mx8bit / 64Mx16bit) NAND Flash3. DEVICE OPERATION3.1 Page Read.Upon initial device power up, the device defaults to Read mode. This operation is also initiated by writing 00h and 30h to the command register along with four address cycles. In two consecutive read operations, the second one does need 00h command, which four address cycles and 30h command initiates that operation. Second read operation always requires setup command if first read operation was executed using also random data out command.Two types of operations are available: random read. The random read mode is enabled when the page address is changed. The 2112 bytes (X8 device) or 1056 words (X16 device) of data within the selected page are transferred to the data registers in less than 25us(tR). The system controller may detect the completion of this data transfer (tR) by analyzing the output of R/B pin. Once the data in a page is loaded into the data registers, they may be read out in 30ns cycle time (3.3V device) by sequentially pulsing RE. The repetitive high to low transitions of the RE clock make the device output the data starting from the selected column address up to the last column address.The device may output random data in a page instead of the consecutive sequential data by writing randomdata output command. The column address of next data, which is going to be out, may be changed to the address which follows random data output command.Random data output can be operated multiple times regardless of how many times it is done in a page.Random data output is not available in cache read.3.2 Page Program.The device is programmed basically by page, but it does allow multiple partial page programming of a word or consec-utive bytes up to 2112 (X8 device) or words up to 1056 (X16 device), in a single page program cycle.The number of consecutive partial page programming operation within the same page without an intervening erase operation must not exceed 8; for example, 4 times for main array (X8 device:1time/512byte, X16 device:1time 256word) and 4 times for spare array (X8 device:1time/16byte ,X16 device:1time/8word).The addressing should be done in sequential order in a block. A page program cycle consists of a serial data loading period in which up to 2112 bytes (X8 device) or 1056 words (X16 device) of data may be loaded into the data register , followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.The serial data loading period begins by inputting the Serial Data Input command (80h), followed by the four cycle address inputs and then serial data. The words other than those to be programmed do not need to be loaded. The device supports random data input in a page. The column address of next data, which will be entered, may bechanged to the address which follows random data input command (85h). Random data input may be operated multi-ple times regardless of how many times it is done in a page.The Page Program confirm command (10h) initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the programming process. The P/E/R controller automatically executes the algorithms and timings necessary for program and verify, thereby freeing the system controller for other tasks. Once . The system controller can detect the completion of a program cycle by monitoring the R/B output, or the Status bit (I/O 6) of the Status Register . Only the Read Status command and Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status Bit (I/O 0) may be checked. The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command register remains in Read Status command mode until another valid command is written to the command register . Figure 14 details the sequence.Rev 0.4 / Jun. 2007131Gbit (128Mx8bit / 64Mx16bit) NAND Flash3.3 Block Erase.The Erase operation is done on a block basis. Block address loading is accomplished in two cycles initiated by an Erase Setup command (60h). Only address A18 to A27 (X8) or A17 to A26 (X16) is valid while A12 to A17 (X8) or A11 to A16 (X16) are ignored. The Erase Confirm command (D0h) following the block address loading initiates the internal erasing process. This two-step sequence of setup followed by execution command ensures that memory contents are not acci-dentally erased due to external noise conditions. At the rising edge of WE after the erase confirm command input, the P/E/R controller handles erase and erase-verify. Once the erase process starts, the Read Status Register command may be entered to read the status register . The system controller can detect the completion of an erase by monitoring the R/B output, or the Status bit (I/O 6) of the Status Register . Only the Read Status command and Reset command are valid while erasing is in progress. When the erase operation is completed, the Write Status Bit (I/O 0) may be checked. Figure 18 details the sequence.3.4 Copy-Back Program.The copy-back program is configured to quickly and efficiently rewrite data stored in one page without utilizing an exter-nal memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system perfor-mance is improved. The benefit is especially obvious when a portion of a block is updated and the rest of the block also need to be copied to the newly assigned free block. The operation for performing a copy-back program is a sequential execution of page-read without serial access and copyingprogram with the address of destination page. A read opera-tion with "35h" command and the address of the source page moves the whole 2112byte (X8 device) or 1056word (X16 device) data into the internal data buffer .As soon as the device returns to Ready state, Copy Back command (85h) with the address cycles of destination page may be written. The Program Confirm command (10h) is required to actually begin the programming operation. Data input cycle for modifying a portion or multiple distant portions of the source page is allowed as shown in Figure 16."When there is a program-failure at Copy-Back operation, error is reported by pass/fail status. But, if Copy-Back operations are accumulated over time, bit error due to charge loss is not checked by external error detection/correction scheme. For this reason, two bit error correction is recommended for the use of Copy-Back operation."Figure 16 shows the command sequence for the copy-back operation.The Copy Back Program operation requires three steps:1. The source page must be read using the Read A command (one bus write cycle to setup the command and then 4 bus write cycles to input the source page address). This operation copies all 2KBytes from the page into the Page Buffer .2. When the device returns to the ready state (Ready/Busy High), the second bus write cycle of the command is given with the 4bus cycles to input the target page address.3. Then the confirm command is issued to start the P/E/R Controller .Note:1. On the same plane.2. It’s prohibited to operate copy-back program from an odd address page (source page) to an even address page (target page) or from an even address page (source page) to an odd address page (target page). Therefore, the copy-back program is permitted just between odd address pages or even address pages.Rev 0.4 / Jun. 2007141Gbit (128Mx8bit / 64Mx16bit) NAND Flash3.5 Read Status Register.The device contains a Status Register which may be read to find out whether read, program or erase operation is com-pleted, and whether the program or erase operation is completed successfully. After writing 70h command to the com-mand register , a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of CE or RE, whichever occurs last. This two line control allows the system to poll the progress of each device in multiple memory connections even when R/B pins are common-wired. RE or CE does not need to be toggled for updated status. Refer to Table 14 for specific Status Register definitions, and Figure 10 for specific timings requirements . The command reg-ister remains in Status Read mode until further commands are issued to it. Therefore, if the status register is read dur-ing a random read cycle, the read command (00h) should be given before starting read cycles.3.6 Read ID.The device contains a product identification mode, initiated by writing 90h to the command register , followed by an address input of 00h. Four read cycles sequentially output the 1st cycle (ADh), and 2nd cycle (the device code) and 3rd cycle ID, 4th cycle ID, respectively. The command register remains in Read ID mode until further commands are issued to it. Figure 19 shows the operation sequence, while Tables 16 explain the byte meaning.3.7 Reset.The device offers a reset feature, executed by writing FFh to the command register . When the device is in Busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased.The command register is cleared to wait for the next command, and the Status Register is cleared to value E0h when WP is high. Refer to table 14 for device status after reset operation. If the device is already in reset state a new reset command will not be accepted by the command register . The R/B pin transitions to low for tRST after the Reset com-mand is written.Rev 0.4 / Jun. 2007151Gbit (128Mx8bit / 64Mx16bit) NAND Flash3.8 Cache programCache Program is an extension of Page Program, which is executed with 2112byte (X8 device) or 1056word (X16 device) data registers, and is available only within a block. Since the device has 1 page of cache memory, serial data input may be executed while data stored in data register are programmed into memory cell. After writing the first set of data up to 2112byte (X8 device) or 1056word (X16 device) into the selected cache registers, Cache Program com-mand (15h) instead of actual Page Program (10h) is input to make cache registers free and to start internal program operation. To transfer data from cache registers to data registers, the device remains in Busy state for a short period of time (tCBSY) and has its cache registers ready for the next data-input while the internal programming gets started with the data loaded into data registers. Read Status command (70h) may be issued to find out when cache registers become ready by polling the Cache- Busy status bit (I/O 6). Pass/fail status of only the previous page is available upon the return to Ready state.When the next set of data is input with the Cache Program command, tCBSY is affected by the progress of pending internal programming. The programming of the cache registers is initiated only when the pending program cycle is finished and the data registers are available for the transfer of data from cache registers. The status bit (I/O5) for internal Ready/Busy may be polled to identify the completion of internal programming.If the system monitors the progress of programming only with R/B, the last page of the target programming sequence must be programmed with actual Page Program command (10h). If the Cache Program command (15h) is used instead, status bit (I/O5) must be polled to find out when the last programming is actually finished before starting other operations such as read. Pass/fail status is available in two steps. I/O 1 returns with the status of the previous page upon Ready or I/O6 status bit changing to "1", and later I/O 0 with the status of current page upon true Ready (returning from internal programming) or I/O 5 status bit changing to "1". I/O 1 may be read together when I/O 0 is checked. See Fig. 18 for more details.NOTE : Since programming the last page does not employ caching, the program time has to be that of Page Program. However , if the previous program cycle with the cache data has not finished, the actual program cycle of the last page is initiated only after completion of the previous cycle, which can be expressed as the following formula.tPROG=Program time for the last page + Program time for the (last-1)page - (Program command cycle time + Last page data loading time)Rev 0.4 / Jun. 2007161Gbit (128Mx8bit / 64Mx16bit) NAND Flash3.9 Cache ReadCache read operation allows automatic download of consecutive pages, up to the whole device. Immediately after 1st latency end, while user can start reading out data, device internally starts reading following page.Start address of 1st page must be at page start (A<10:0>=00h) : in this way after 1st latency time (tr) , automatic data download will be uninterrupted. In fact latency time is 25us, while download of a page require at least 100us for x8 device (50us for x16 device).Cache read operation command is like standard read, except for confirm code (30h for standard read, 31h for cache read) user can check operation status using :- R/B ( ‘0’ means latency ongoing, download not possible, ‘1’ means download of n page possible, even if device in ternally is active on n+1 page- Status register (SR<6> behave like R/B, SR<5> is ‘0’ when device is internally reading and ‘1’ when device is idle)To exit cache read operation, a cache read exit command (34h) must be issued. This command can be given any time (both device idle and reading).If device is active (SR<5>=0) it will go idle within 5us, while if it is not active, device itself will go busy for a time shorter then tCBSY before becoming again idle and ready to accept any further commands. Figure 17 describes how to handle Cache Read through Status register .If user reads last byte/word of the memory array, then he has to stop by giving a cache read exit command. In general,if user wants to terminate a cache read, then he must give a cache read exit command (or reset command) before starting any new operation.Random data output is not available in cache read.Cache read operation must be done only block by block if system needs to avoid reading also from invalid blocks.Rev 0.4 / Jun. 2007171Gbit (128Mx8bit / 64Mx16bit) NAND Flash4. OTHER FEATURES4.1 Data Protection for Power on/off SequenceThe device is designed to offer protection from any involuntary program/erase during power-transitions. An internal voltage detector disables all functions whenever Vcc is below about 2.0V (3.3V version). WP pin provides hardware protection and is recommended to be kept at VIL during power-up and power-down. A recovery time of minimum 10us is required before internal circuit gets ready for any command sequences as shown in Figure 24. The two-step com-mand sequence for program/erase provides additional software protection.If the power is dropped during the ready read/write/erase operation, Power protection function may not guaranteed the data. Power protection function is only available during the power on/off sequence.4.2 Ready/Busy.The device has a Ready/Busy output that provides method of indicating the completion of a page program, erase, copy-back, cache program and random read completion. The R/B pin is normally high and goes to low when the device is busy (after a reset, read, program, erase operation). It returns to high when the P/E/R controller has finished the operation. The pin is an open-drain driver thereby allowing two or more R/B outputs to be Or-tied. Because pull-up resistor value is related to tr(R/B) and current drain during busy (Ibusy), an appropriate value can be obtained with the following reference chart (Figure 25). Its value can be determined by the following guidance.。

H27UG8T2B_F20 64Gb B MLC_Legacy_Rev1.2_120621

F20 64Gb MLCNAND Flash MemoryLegacy LGA52This document is a general product description and is subject to change without notice. SK hynix does not assume any responsibility for use of circuits described. No patent licenses are implied.Document Title64Gbit(8192M x 8bit) NAND Flash MemoryRevision HistoryRevision No.History Draft Date Remark0.0 Initial Draft Mar.07.2011 Preliminary0.1 Modified some numbers Mar.18.2011 Preliminary0.2 Revised errata Sep.22.2011 Preliminary0.3 Add paired page address table Oct.12.2011 Preliminary1.0 1.0 Released Oct.21.20111.1 CLE, ALE Hold Time Changed Nov.18.20111.2 Correct No. of Valid Blocks Jun.21.2012Product Feature■ Multi Level Cell (MLC) Technology■ Power Supply Voltage- VCC / VCCq= 2.7V ~ 3.6V■ Organization- Page Size : 16,384 + 1,280(Spare) bytes- Block Size : 4M + 320K bytes, 256pages- Plane Size : 1024 + 42(Extended) blocks- Device Size : 2048 + 84(Extended) blocks■ Page Read Time- Random Read Time (tR) : TBD- Sequential Access (tRC/tWC) : 16ns(Min.)■ Page Write Time- Page Program Time : 1500 (Typ.)■ Block Erase Time- Block Erase Time : 5.0ms(Typ.)■ Hardware Data Protection- Program/Erase locked during power transitions ■ Package- Package type : VLGA- Chip count : SDP- Pin(Ball) count : 52 ball- Size : 14mm x 18mm x 1mm■ Electronic Signature- 1st cycle : Manufacturer code- 2nd cycle : Device code- 3rd cycle : Internal chip number, Cell type,Number of simultaneously programmed pages - 4th cycle : Page size, Block size, Organization, Spare size- 5th cycle : Multi-plane information- 6th cycle : Technology, EDO, Interface ■ Reliability- TBD1. Summary Description …………………………………………………………………………………………….. 1.1. Product List ……..…………………………………………………………………..………………………….…. 1.2. Pin Descriptions ..…………………………………………………………………..…………………..……..... 1.3. Pin Diagram ............................................................................................................................... 1.4. Pin Assignments ………………………………………………………………………..……..…………..…….. 1.5. Block Diagram ............................................................................................................................ 1.6. Array Organization ..................................................................................................................... 1.7. Addressing ................................................................................................................................. 1.8. Extended Blocks Arrangement .................................................................................................. 1.9. Command Set ……………………………………………………………………………….………………..…… 1.10. Mode Selection …………………………………………………………………………….…………………..…. 1.11. Bad Block Management ………………………………………………………………….……………………. 1.12. Bad Block Replacement …………………………………………………………………….…………………. 2. Electrical Characteristics ……………………………………………………………………...………………… 2.1. Valid Blocks …………………………………………………………………………………………….………….. 2.2. Absolute Maximum Rating ………………………………………………………………………….…………. 2.3. DC and Operating Characteristics ……………………………………………………………….…………… 2.4. AC Test Conditions …………………………………………………………………………………….…………. 2.5. Pin Capacitance (T A =25℃, F=1.0㎒) .......................................................................................... 2.6. Program/ Read / Erase Characteristics ..................................................................................... 2.7. AC Timing Characteristics ………………………………………………………………………….………….. 2.8. Status Register Coding ……………………………………………………………………………………….… 2.8.1. Status Register Coding For 70h/78h command ………….…………………………………….….. 2.8.2. Status Register Coding For 75h command ……………………….……………………………….… 2.9. Device Identifier Coding …………………………………………………………………………………….…. 2.10. Read ID Data Table ………………………………………………………………………………………….… 2.10.1. 3rd Byte of Device Identifier Description …………………………………………………………… 2.10.2. 4th Byte of Device Identifier Description …………………………………………………………… 2.10.3. 5th Byte of Device Identifier Description …………………………………………………………… 2.10.4. 6th Byte of Device Identifier Description …………………………………………………………… 3. Timing Diagram ………………………………………………………………………………………….………..… 3.1. Command Latch Cycle Timings ……………………………………………………………………….……….. 3.2. Address Latch Cycle Timings .………………………………………………………………………….………. 3.3. Input Data Latch Cycle Timings …………………………………………………………………….………… 3.4. Data Output Cycle Timings …………………………………………………………………………….………. 3.5. Data Output Cycle Timings (EDO type) ……………………………………………………………….……… 3.6. Read Status Cycle Timings …………………………………………………………………………….………. 3.7. Multi Plane Read Status Timings …………………………………………………………………….………. 3.8. Page Read Operation Timings .……………………………………………………………………….………. 3.9. Page Read Operation Timings (Intercepted by CE#) ………………………………………………….…… 3.10. Page Read Operation Timings with CE# don’t care …………………………………………….……… 3.11. Random Data Output Timings ………………………………………………………………………….……. 3.12. Multi Plane Page Read Operation with Random Data output Timings ……………………….…… 3.13. Cache Read Operation Timings ……………………………………………………………………….…….. 3.14. Multi Plane Cache Read Operation Timings ……………………………………………………….…….. 3.15. Read ID Operation Timings ……………………………………………………………………………….…. 3.16. Page Program Operation Timings ……………………………………………………………………….…. 3.17. Page Program Operation Timings with CE# don’t care ………………………………………………..66 7 8 9 11 11 12 12 13 14 15 16 17 17 17 18 18 19 19 20 21 21 22 22 23 23 23 24 24 25 25 25 26 26 27 27 28 28 29 29 30 30 31 32 33 33 34Table of Contents3.18. Random Data Input Timings …………………………………………………………………………………3.19. Multi Plane Page Program Operation Timings …………………………………………………………..3.20. Copy-Back Program Operation Timings with Random Date Input .………………………………..3.21. Cache Program Operation Timings …………………………………………………………………………3.22. Multi Plane Cache Program Operation Timings ………………………………………………………….3.23. Block Erase Operation Timings ………………………………………………………………………………3.24. Multi Plane Erase Operation Timings ......................................................................................3.25. Reset Timings ……………………………………………………………………………………………………4. Device Operation ……………………………………………………………………………………………………4.1. Page Read …………………………………………………………………………………………………………..4.2. Cache Read …………………………………………………………………………………………………………4.3. Cache Read Enhanced …………………………………………………………………………………………..4.4. Multi Plane Page Read …………………………………………………………………………………………..4.5. Multi Plane Cache Read ………………………………………………………………………………………...4.6. Multi Plane Cache Read Enhanced …………………………………………………………………………..4.7. Read ID ……………………………………………………………………………………………………………..4.8. Read Status Register …………………………………………………………………………………………….4.9. Page Program ……………………………………………………………………………………………………..4.10. Multi Plane Program ……………………………………………………………………………………………4.11. Cache Program .………………………………………………………………………………………………….4.12. Multi Plane Cache Program .………………………………………………………………………………….4.13. Copy-Back Program …………………………………………………………………………………………….4.14. Multi-Plane Copy-Back Program …………………………………………………………………………….4.15. Block Erase ………………………………………………………………………………………………………..4.16. Multi Plane Block Erase ………………………………………………………………………………………..4.17. Reset ……………………………………………………………………………………………………………….5. Other Features …………………………………………………………………………………………………………5.1. Data Protection & Power on/off Sequence …………………………………………………………………5.2. Ready / Busy .………………………………………………………………………………………………………5.3. Write Protect Operation …………………………………………………………………………………………6. Application Notes and Comments ...…………….……………………….………………………………………6.1. Paired Page Address Information (34)35363637373838393940404142424343444546484950515252535354555657Table 1 : List of supported versions / packagesPART NUMBER ORGANIZATIONOPERATING RANGEPACKAGE H27UCG8T2BYR-BCX82.7 to3.6V52-LGA1. Summary DescriptionThe product part No. H27UCG8T2BYR-BC is a single 3.3V 64Gbit NAND flash memory. The Device contains 2planes in a single die. Each plane is made up of the 1066 blocks. Each block consists of 256 programmable pages. Each page contains 17,664 bytes. The pages are subdivided into an 16,384 byte main data storage area with a spare 1,280 byte district.Page program operation can be performed in typical 1500us, and a single block can be erased in typical 5ms.1.1. Product ListPin Name DescriptionI/O 0― I/O 7DATA INPUTS/OUTPUTSThe I/O pins is used to COMMAND LATCH cycle, ADDRESS INPUT cycle, and DATA in-out cycles during read / write operations. The I/O pins float to High-Z when the device is deselected or the outputs are disabled.CLECOMMAND LATCH ENABLEThis input activates the latching of the I/O inputs inside the Command Register on the Rising edge of Write Enable (WE#).ALEADDRESS LATCH ENABLEThis input activates the latching of the I/O inputs inside the Address Register on the Rising edge of Write Enable (WE#).CE#CHIP ENABLEThis input controls the selection of the device. When the device is busy, CE# low does not deselect the memory. The device goes into Stand-by mode when CE# goes High during the device is in Ready state. The CE# signal is ignored when device is in Busy state, and will not enter Standby mode even if the CE# goes high.WE#WRITE ENABLEThis input acts as clock to latch Command, Address and Data. The I/O inputs are latched on the rise edge of WE#.RE#READ ENABLEThe RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE# which also increments the internal column address counter by one.WP#WRITE PROTECTThe WP# pin, when Low, provides a hardware protection against undesired write operations. Hardware Write Protection is activated when the Write Protect pin is low. In this condition modify operation do not start and the content of the memory is not altered. Write Protect pin is not latched by Write Enable to ensure the protection even during the power up phases. R/B# READY / BUSYThe Ready/Busy output is an Open Drain pin that signals the state of the memory. V CC Q SUPPLY VOLTAGE FOR I/O BUFFER V SS Q GROUND FOR I/O BUFFERV CC SUPPLY VOLTAGEThe VCC supplies the power for all the operations. (Read, Write, and Erase). V SS GROUND NCNO CONNECTEDNOTE: A 0.1uF capacitor should be connected between the Vcc (Supply Voltage) pin and the Vss (Ground) pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.Table 2 : Signal descriptions1.2. Pin DescriptionsFigure 1 : Pin diagram(SDP)VCC ALE CLE VSS R/B#IO0~IO7CE#WE#RE#WP#VSSQVCCQ1.3. Pin Diagram1.4. Pin AssignmentsFigure 2 : 52-VLGAFigure 3 : Package Mechanical DataFigure 3 : Block diagram(SDP)Figure 4 : Array organization1.5. Block Diagram1.6. Array OrganizationVccQ VssQ17,664 bytes8 , 832 8 , 192 8 , 832 1,280 I / O 0I / O 71 B lock 1 B lockPlane 0 Plane 11024 blocks / plane2132 blocks / deviceCache register Data register1 Page = (16,384 + 1,280) bytes1 Block = (16,384 + 1,280) bytes x 256 pages = (4M+ 320K) bytes1 Device = (16,384 + 1,280) bytes x 256 pages x 2,132 blocks1066 b locks/plane 2132 blocks/device Cache register Data register 16,384 16,38416,384 1,2801,280 1,28017,664 bytes 16,384A15-A34A0-A14Bus cycle I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 1st Cycle A0 A1 A2 A3 A4 A5 A6 A7 2nd Cycle A8 A9 A10 A11 A12 A13 A14 L (1) 3rd Cycle A15 A16 A17 A17 A19 A20 A21 A22 4th Cycle A23 A24 A25 A26 A27 A28 A29 A30 5th CycleA31A32A33A34L (1)L (1)L (1)L (1)Notes:1. L must be set to Low.2. The device ignores any additional address input cycle than required.3. The Address consists of column address (A0~A14), page address (A15 ~ A22), plane address (A23), and block address (A24 ~ the last address).1.7. Addressing1.8. Extended Blocks ArrangementThe device offers 84 extended blocks to increase valid blocks. These blocks can be accessed when the block address A34 is …High‟.Block 0 Block 1 Block 2 Block 3 Block 4 Block 5· · · Block 2045 Block 2046 Block 2047 Block 2048 Block 2049· · · Block 2130 Block 21310000h 0001h 0002h 0003h 0004h 0005h· · ·07FDh 07FEh 07FFh 0800h 0801h· · ·0852h 0853h 0853hRow Address (Hexadecimal)Main Blocks (2048 Blocks)Extended Blocks (84 Blocks)FUNCTION 1stCycle NumberofAddresscyclesDataInputcycles2ndCycleNumberofAddresscyclesDatainputcycles3rdCycleAcceptablecommandDuringbusyPAGE READ 00h 5 - 30h - - - No READ FOR COPY-BACK 00h 5 - 35h - - - No RANDOM DATA OUTPUT1)05h 2 - E0h - - - No SINGLE/MULTI-PLANECACHE READ 5)31h - - - - - - No SINGLE/MULTI-PLANECACHE READ END 5)3Fh - - - - - - No READ ID 90h 1 - - - - - No READ STATUS REGISTER 70h - - - - - - Yes PAGE PGM (start)/CACHE PGM 5) (end) 80h 5 Yes 10h - - - No RANDOM DATA INPUT1)85h 2 Yes - - - - No COPY-BACK PGM 85h 5 option 10h - - - No CACHE PGM (start)5)80h 5 Yes 15h - - - No BLOCK ERASE 60h 3 - D0h - - - No RESET FFh - - - - - - Yes MULTI-PLANE PAGE READ 60h 3 - 60h 3 - 30h No MULTI-PLANE CACHE READSTART 5) 6)60h 3 - 60h 3 - 33h No MULTI-PLANE READ FORCOPY-BACK 60h 3 - 60h 3 - 35h No MULTI-PLANE BLOCK ERASE 60h 3 - 60h 3 - D0h No MULTI-PLANE RANDOMDATA OUTPUT 1) 3)00h 5 - 05h 2 - E0h No MULTI-PLANE READSTATUS REGISTER 78h 3 - - - - - Yes MULTI-PLANE READSTATUS REGISTER (legacy) 75h - - - - - - Yes MULTI-PLANE PAGE PGM/MULTI-PLANE CACHE PGM(end)80h 5 Yes 11h-81h 2) 5 Yes 10h NoMULTI-PLANE COPY-BACKPGM 85h 5 option 11h-81h 2) 5 option 10h No MULTI-PLANE CACHE PGM(start) 5)80h 5 Yes 11h-81h 2) 5 Yes 15h No CACHE READ ENHANCED 00h 5 - 31h - - - No MULTI-PLANE CACHE READENHANCED 60h 3 - 60h 3 - 31h No 1.9. Command SetNotes:1. Random Data Input/Output must be performed in a selected page.2. Any command between 11h and 81h is prohibited except 70h, 78h, 75h and FFh.3. Multi-plane Random data-out must be used after multi-plane read operations(Multi-plane Page Read, Multi-plane Cache Read and Multi-plane Read for Copy Back). 4. Do not change plane address order when using all multi-plane operations.5. All cache operation (cache program, cache read) is available only within a block.6. It‟s possible to confirm the multi -plane cache read first step using both 30h and 33h.Caution:1. Any undefined command inputs are prohibited except for above command set.2. Multi-plane page read, multi-plane cache read, and multi-plane read for copy-back must be usedafter multi-plane programmed page, multi-plane cache program, and multi-plane copy-back program.CLE ALE CE# WE# RE# WP# MODE H L L H X Read ModeCommand Input L H L H X Address Input (5 Cycles) H LL H H Write Mode Command Input L HL H H Address Input (5 Cycles)L LL HH Data InputL LL HXSequential Read and Data Output X XX HHX During Read (Busy) X XX X X H During Program (Busy) X X X X X H During Erase (Busy) X X X X X LWrite ProtectXXHXX0V/Vcc Stand-ByNotes:1. X can be V IL or V IH . H = Logic level “High”. L = Logic level “Low”.2. WP# should be biased to CMOS high or CMOS low for stand-by mode.3. WE# and RE# during Read Busy must be keep on high to prevent unplannedcommand/address/data input or to avert unintended data out. In this time, only Reset, Read Status, and Multi-plane Read Status can be inputted to the device.1) 1) 1) 3) 3) 2) 1.10. Mode SelectionFigure 5 : Bad block management flow chartNotes:1. Do not try to erase the detected bad blocks, because the bad bock information will be lost.2. Do not perform program and erase operation in invalid block, it is impossible to guarantee the input data and to ensure that the function is normal.1.11. Bad Block ManagementDevices with Bad Blocks have the same quality level and the same AC and DC characteristics as devices where all the blocks are valid. A Bad Block does not affect the performance of valid blocks because it is isolated from the bit line and common source line by a select transistor. The devices are supplied with all the locations inside valid blocks erased (FFh). The Bad Block Information is written prior to shipping. Any block where the 1st Byte in the spare area of the first and last page does not contain FFh is a Bad Block. The Bad Block Information must be read before any erase is attempted as the Bad Block Information may be erased. For the system to be able to recognize the Bad Blocks based on the original information it is recommended to create a Bad Block tablefollowing the flowchart shown in Figure 5. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block at the time of shipment.16,38416,384Table 4 : Block failureFigure 6 : Block replacementNotes:1. An error occurs on nth page of the Block A during Program or Erase operation.2. Data in Block A is copied to same location in Block B which is valid block.3. Nth page of block A which is in controller buffer memory is copied into nth page of Block B4. Bad block table should be updated to prevent from erasing or programming Block A.1.12. Bad Block ReplacementThis device may have the invalid blocks when shipped from factory. An invalid block is one that contains one or more bad bits. Over the lifetime of the device additional Bad Blocks may develop. In this case, the block has to be replaced by copying the data to a valid block. These additional Bad Blocks can be identified as attempts to program or erase them will give errors in the Status Register.The failure of a page program operation does not affect the data in other pages in the same block. Bad block can be replaced by re-programming the current data and copying the rest of the replaced block to an available valid block. Refer to Table 4 and Figure 6 for the recommended procedure to follow if an error occurs during an operation.Operation Recommended ProcedureErase Block Replacement Program Block ReplacementReadECCSymbolMin TypMax Unit Valid Block NumberN VB20462132BlocksNotes:1. The 1st block is guaranteed to be a valid block at the time of shipment.2. This single device has a maximum of 86 invalid blocks.3. Invalid blocks are one that contains one or more bad bits. The device may contain bad blocks on shipment.SymbolParameterValue Unit Min T AAmbient Operating Temperature (Commercial Temperature Range) 0 to 70 ℃ Ambient Operating Temperature (Extended Temperature Range) -25 to 85 ℃ Ambient Operating Temperature (Industrial Temperature Range)-40 to 85 ℃ T BIAS Temperature Under Bias -50 to 125 ℃ T STG Storage Temperature -65 to 150 ℃ V IO Input or Output Voltage-0.6 to 4.6 V V CCSupply Voltage-0.6 to 4.6VNotes:1. Except for the rating “Operating Temperature Range”, stresses above those listed in the Table“Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.Refer also to the SK hynix SURE Program and other relevant quality documents.2. Minimum voltage may undershoot to -2V during transition and for less than 20ns during transitions. Maximum voltage may overshoot to Vcc+2V during transition and for less than 20ns during transitions.2. Electrical Characteristics2.1. Valid Blocks2.2. Absolute Maximum RatingParameterSymbolTest Conditions 3.3VUnitsMin Typ Max Power on reset currentI CC0FFh command input after power on --50 per devicemAOperating CurrentReadI CC1 t RC = t RC (min), CE#=V IL , I OUT =0 ㎃- - 50 mA Program I CC2 - - 50 mA EraseI CC3 -- 50 mA Stand-by Current(TTL)I CC4 CE#=V IH , WP#=0V/V CC - - 1 mA Stand-by Current(CMOS) I CC5CE#=V CC -0.2, WP#=0V/V CC - 10 50 uA Input Leakage Current V IN =0 to V CC(MAX)- - ±10 uA Output Leakage Current I LO V OUT =0 to V CC(MAX)- - ±10 uA Input High Voltage V IH - Vccx0.8 - Vcc+0.3 V Input Low Voltage V IL - -0.3 - 0.2xVccV Output High Voltage Level V OH I OH =-400 ㎂ 2.4 - - V Output Low Voltage Level V OL I OL =2.1 ㎃ - - 0.4 V Output Low Current (R/B#)I OL (R/B#)V OL =0.4V810-mAParameter Value2.7V ≤ VccQ ≤3.6VInput Pulse Levels 0 V to V CC Input Rise and Fall Times 5 ㎱ Input and Output Timing LevelsV CC / 2Output Load (2.7V-3.6V)1 TTL GATE and CL=50㎊Note:These parameters are verified device characterization and are not 100% tested.2.3. DC and Operating Characteristics2.4. AC Test ConditionsSymbol Parameter Test ConditionMin Max Unit C IN Input Capacitance V IN = 0V - 10 pF C I/OInput/Output CapacitanceV IL = 0V-10pFParameterSymbol Min Typ Max Unit Program (following 10h) t PROG - 1500 4000 us Cache Program (following 15h)t CBSYW - - 4000 us Multi-plane Program / Multi-plane Cache Program / Multi-plane Copy-back Program (following 11h) t DBSY -0.5 3 us Cache Read / Multi-plane Cache Read (following 31h/3Fh)t CBSYR 3 90 us Block Erase / Multi-plane Block Eraset BERS - 5 10 ms Number of partial Program Cycles in the same pageNOP- -1cyclesNotes:Typical value is measured at V CC =3.3V, T A =25℃. Not 100% tested.2.5. Pin Capacitance (T A =25℃, F=1.0㎒)2.6. Program/ Read / Erase CharacteristicsParameter Symbol3.3VUnit Min MaxCLE setup time t CLS 6 nsCLE Hold time t CLH 3 nsCE# setup time t CS20 nsCE# hold time t CH 5 nsWE# pulse width t WP8 nsALE setup time t ALS 6 nsALE hold time t ALH 3 nsData setup time t DS 6 nsData hold time t DH 2 nsWrite cycle time t WC16 nsWE# high hold time t WH 6 ns Data transfer from cell to register t R90 us ALE to RE# delay t AR10 nsCLE to RE# delay t CLR10 nsReady to RE# low t RR20 nsRE# pulse width t RP8 nsWE# high to busy t WB100 nsRead cycle time t RC16 nsRE# access time t REA16 ns RE# high to output high Z t RHZ100 nsCE# high to output high Z t CHZ50 nsRE# high to output hold t RHOH15 nsRE# low to output hold t RLOH 5 ns RE# or CE# high to output hold t COH15 ns RE# high hold time t REH 6 nsWE# high to RE# low t WHR80 ns WE# high to RE# low for Random data out t WHR2200 ns RE# high to WE# low t RHW100 nsOutput high Z to RE# low t IR0 ns CE# low to RE# low t CR10 ns Address to data loading time t ADL200 ns Device resetting time (Read/Program/Erase) t RST20/30/500 us Write protection time t WW100 ns 2.7. AC Timing CharacteristicsNotes:1. If Reset Command (FFh) is written at Ready state, the device goes into Busy for maximum 5us.2. Program / Erase Enable Operation: WP# high to WE# High. Program / Erase Disable Operation: WP# Low to WE# High.3. The transition of the corresponding control pins must occur only while WE# is held low.4. t ADL is the time from the WE# rising edge of final address cycle to the WE# rising edge of first data cycle.I/O Page Program Block Erase Read Cache Read Cache Program Coding 70h / 78h 0 Pass / Fail Pass / Fail N/A N/A Pass / Fail (N) N pagePass : …0‟ Fail : …1‟ 1 N/A N/A N/A N/A Pass / Fail (N-1) N -1 page Pass : …0‟ Fail : …1‟2 N/A N/A N/A N/A N/A …0‟3 N/A N/A N/A N/A N/A …0‟4 N/A N/A N/A N/A N/A …0‟5 N/A N/A N/A Ready / Busy Ready / Busy Ready / Busy Busy : …0‟ Ready : …1‟6 Ready / Busy Ready / Busy Ready / Busy Ready / Busy Ready / Busy Data Cache Ready / Busy Busy : …0‟ Ready : …1‟7Write ProtectWrite ProtectWrite ProtectWrite ProtectWrite ProtectProtected : …0‟ Not Protected : …1‟Notes:1. I/O0 : This bit is only valid for Program and Erase operations. During Cache Program operations, this bit is only valid when I/O5 is set to one.2. I/O1 : This bit is only valid for cache program operations. This bit is not valid until after the second 15h command or the 10h command has been transferred in a Cache program sequence. When Cache program is not supported, this bit is not used.3. I/O5 : If set to one, then there is no array operation in progress. If cleared to zero, then there is a command being processed (I/O6 is cleared to zero) or an array operation in progress. When overlapped interleaved operations or cache commands are not supported, this bit is not used.4. I/O6 : If set to one, then the device or interleaved address is ready for another command and all other bits in the status value are valid. If cleared to zero, then the last command issued is not yet complete and Status Register bits<5:0> are invalid value. When cache operations are in use, then this bit indicates whether another command can be accepted, and I/O5 indicates whether the last operation is complete.2.8. Status Register Coding2.8.1. Status Register Coding For 70h/78h commandI/O Page Program Block Erase Read Cache Read Cache Program Coding 75h 0/ Fail / Fail N/AN/AChip Pass / Fail (N) N pagePass : …0‟ Fail : …1‟ 1 Plane 0 Pass / Fail Plane 0 Pass / Fail N/A N/APlane 0 Pass / Fail (N) N pagePass : …0‟ Fail : …1‟ 2 Plane 1 Pass / Fail Plane 1 Pass / Fail N/A N/APlane 1 Pass / Fail (N) N page Pass : …0‟ Fail : …1‟ 3 N/AN/AN/A N/APlane 0 Pass / Fail (N-1) N -1 page Pass : …0‟ Fail : …1‟ 4 N/A N/A N/A N/A Plane 1 Pass / Fail (N-1) N -1 page Pass : …0‟ Fail : …1‟ 5 N/A N/A N/A Ready / Busy Ready / Busy Ready / Busy Busy : …0‟ Ready : …1‟ 6Ready / Busy Ready / Busy Ready / Busy Ready / Busy Ready / Busy Data Cache Ready / Busy Busy : …0‟ Ready : …1‟ 7Write ProtectWrite ProtectWrite ProtectWrite ProtectWrite ProtectProtected : …0‟ Not Protected : …1‟Parameter Symbol Device Identifier ByteDescription 1st Manufacturer Code 2nd Device Identifier3rd Internal chip number, cell Type, Number of Simultaneously Programmed Pages, Interleaved Program, Write Cache.4th Page size, Block size, Redundant area size5th Plane Number, ECC Level6thTechnology (Design Rule), EDO, Interface2.8.2. Status Register Coding For 75h command2.9. Device Identifier CodingPart Number Voltage BusWidth ManufactureCodeDeviceCode3rd4th5th6thH27UCG8T2B 3.3V X8 ADh DEh 94h EBh 74h 44h 3rd cycle Description I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0Internal Chip Number / CE 12481111Cell Type 2 Level Cell4 Level Cell8 Level Cell16 Level Cell1111Number of Simultaneously Programmed Pages 12481111Interleaved Program Between Multiple dieNotSupported1Write Cache NotSupported 0 12.10. Read ID Data Table2.10.1. 3rd Byte of Device Identifier Description2.10.2. 4th Byte of Device Identifier Description4th cycle Description I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0Page Size (Without Spare Area) 2KB4KB8KB16KB1111Block Size (Without Spare area)128KB256KB512KB768KB1MB2MB4MBReserved111111111111Redundant Area Size /8KB 640Bytes448Bytes224Bytes128Bytes64Byte32Byte16ByteReserved111111111111。

H27UCG8T2MYR_REV0.0 现代 8GB FLASH 芯片规格书

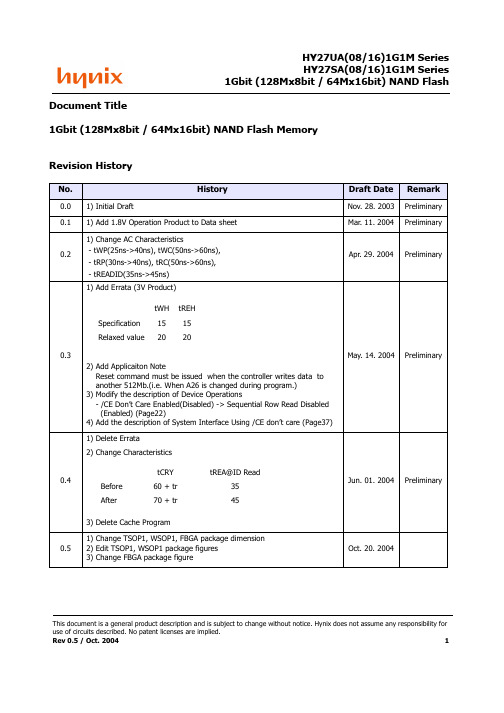

Revision History

Revision No.

0.0

Initial Draft.

1.0

Finalize

History

Draft Date Remark Apr. 27. 2010 Preliminary Aug. 17. 2010 Advanced

Rev 1.0 / Aug. 2010

2

Product Feature

COMMAND LATCH ENABLE

CLE

This input activates the latching of the I/O inputs inside the Command Register on the Rising edge of Write

Enable (WE#).

ADDRESS LATCH ENABLE

■ Organization - Page size : 8,640 Bytes(8,192+448 bytes) - Block size : 256 pages(2M+112K bytes) - Plane size : 2,048 blocks - Chip size : 2 planes (4,096 blocks)

ALE

This input activates the latching of the I/O inputs inside the Address Register on the Rising edge of Write

Enable (WE#).

CHIP ENABLE

This input controls the selection of the device. When the device is busy, CE# low does not deselect the

HYNIX_Databook_Q2'2015_NAND

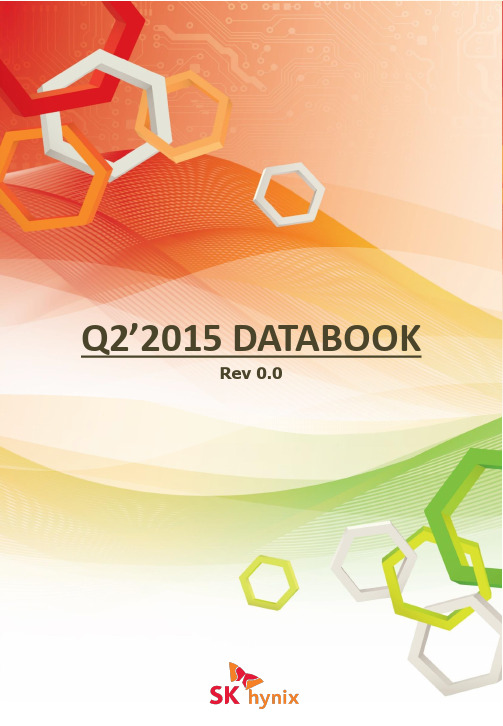

Q2’2015 DATABOOKRev 0.0PRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H27U1G8F2B4xnm1Gb128KB SDP 3.3V / x8TSOP / FBGA Now-H27S1G8F2B4xnm1Gb128KB SDP 1.8V / x8FBGA Now-H27U1G8F2C3xnm1Gb128KB SDP 3.3V / x8TSOP Now-H27U2G8F2C4ynm2Gb128KB SDP 3.3V / x8TSOP Now-H27S2G8F2C4ynm2Gb128KB SDP 1.8V / x8FBGA Now-H27U2G8F2D3xnm2Gb128KB SDP 3.3V / x8TSOP Now-H27U4G8F2D4ynm4Gb128KB SDP 3.3V / x8TSOP Now-H27U4G8F2E3xnm4Gb128KB SDP 3.3V / x8TSOP Now-H27U8G8G5D4ynm8Gb128KB DDP 3.3V / x8TSOP Now-SLCPRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H27UCG8T2A2ynm64Gb2MB SDP 3.3V / x8TSOP Now-H27UCG8T2B2ynm64Gb4MB SDP 3.3V / x8TSOP /FGBA(132ball) Now-H27UBG8T2C2ynm32Gb2MB SDP 3.3V / x8TSOP Now-H27UAG8T2C2ynm16Gb2MB SDP 3.3V / x8TSOP / PGD2Now-H27QDGDUDB2ynm128Gb4MB DDP 3.3V / x8FGBA(132ball)Now HS(ONFi3.0) H27QEGDVEB2ynm256Gb4MB QDP 3.3V / x8FGBA(132ball)Now HS(ONFi3.0) H27QFGDYEB2ynm512Gb4MB ODP 3.3V / x8FGBA(132ball)Now HS(ONFi3.0) H27UCG8T2E1xnm64Gb4MB SDP 3.3V / x8TSOP Now -H27QCG8T2E1xnm64Gb4MB SDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QDG8UDE1xnm128Gb4MB DDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QEG8VEE1xnm256Gb4MB QDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QFG8YEE1xnm512Gb4MB ODP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QCG8T2F1xnm64Gb4MB SDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QDG8UDF1xnm128Gb4MB DDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QEG8VEF1xnm256Gb4MB QDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QFG8YEF1xnm512Gb4MB ODP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QDG8T2B1xnm128Gb4MB SDP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27QEG8UDB1xnm256Gb4MB DDP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27QFG8VEB1xnm512Gb4MB QDP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27Q1T8YEB1xnm1024Gb4MB ODP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27QFG8VQB1xnm512Gb4MB QDP 3.3V / x8FGBA(316ball)Now HS(Toggle2.0) H27Q1T8YQB1xnm1024Gb4MB ODP 3.3V / x8FGBA(316ball)Now HS(Toggle2.0) H27Q2T8CQB1xnm2048Gb4MB HDP 3.3V / x8FGBA(316ball)Now HS(Toggle2.0) H27QFG84EB1xnm512Gb4MB QDP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27Q1T85EB1xnm1024Gb4MB ODP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27Q2T87EB1xnm2048Gb4MB HDP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27QFG8PEM1xnm512Gb4MB QDP 3.3V / x8FGBA(152ball)Now HS(Toggle2.0) H27Q1T8QEM1xnm1024Gb4MB ODP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QDG8UDA2ynm128Gb2MB DDP 3.3V / x8FGBA(132ball)Now HS(ONFi2.2) H27QEG8VEA2ynm256Gb2MB QDP 3.3V / x8FGBA(132ball)Now HS(ONFi2.2) H27QFG8YEA2ynm512Gb2MB ODP 3.3V / x8FGBA(132ball)Now HS(ONFi2.2) MLCPRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H27QDG8M2M1xnm128Gb4MB SDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QEG8NDM1xnm256Gb4MB DDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QFG8PEM1xnm512Gb4MB QDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27Q1T8QEM1xnm1Tb4MB ODP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QCG882M1xnm64Gb6MB SDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) H27QDG89DM1xnm128Gb6MB DDP 3.3V / x8FGBA(132ball)Now HS(Toggle2.0) TLCPRODUCT DENSITYBASE COMPONENTVCC/ORG VERSION AVAIL. REMARKTECH. DENSITY STACKH26M31001HPR4GB1xnm32Gb1 3.3V / x4, x8MMC 4.5Now 11.5x13x0.8 H26M41103HPR 8GB1xnm64Gb1 3.3V / x4, x8MMC 5.0Now11.5x13x0.8 H26M52103FMR 16GB1xnm64Gb2 3.3V / x4, x8MMC 5.0Now11.5x13x1.0 H26M64103EMR32GB1xnm64Gb4 3.3V / x4, x8MMC 5.0Now11.5x13x1.0 H26M78103CCR64GB1xnm64Gb8 3.3V / x4, x8MMC 5.0Now 11.5x13x1.2 H26M41208HPR 8GB1xnm64Gb1 3.3V / x4, x8MMC 5.1Q2'1511.5x13x0.8 H26M52208FMR 16GB1xnm64Gb2 3.3V / x4, x8MMC 5.1Q2'1511.5x13x0.8 H26M64208EMR32GB1xnm64Gb4 3.3V / x4, x8MMC 5.1Q2'1511.5x13x1.0 H26M78208CMR64GB1xnm64Gb8 3.3V / x4, x8MMC 5.1Q2'1511.5x13x1.0 eMMCPRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H2JTCG8T21BMR1xnm64Gb4MB1 3.0V, 3.3V / x8WLGA Now Non Shielded H2JTDG8UD1BMR1xnm128Gb4MB2 3.0V, 3.3V / x8WLGA Now Non Shielded H2JTEG8VD1BMR1xnm256Gb4MB4 3.0V, 3.3V / x8WLGA Now Non Shielded H2JTFG8YD1BMR1xnm512Gb4MB8 3.0V, 3.3V / x8WLGA Now Non Shielded H2JTDG8UD1BMS1xnm128Gb4MB2 3.0V, 3.3V / x8WLGA Now EMI Shielded H2JTEG8VD1BMS1xnm256Gb4MB4 3.0V, 3.3V / x8WLGA Now EMI Shielded H2JTFG8YD1BMS1xnm512Gb4MB8 3.0V, 3.3V / x8WLGA Now EMI Shielded H2JTCG8T21CMR 1xnm64Gb4MB1 3.0V, 3.3V / x9WLGA Now Non Shielded H2JTDG8UD1CMR 1xnm128Gb4MB2 3.0V, 3.3V / x10WLGA Now Non Shielded H2JTEG8VD1CMR 1xnm256Gb4MB4 3.0V, 3.3V / x11WLGA Now Non Shielded H2JTFG8YD1CMR 1xnm512Gb4MB8 3.0V, 3.3V / x12WLGA Now Non Shielded H2JTDG8UD1CMS 1xnm128Gb4MB2 3.0V, 3.3V / x13WLGA Now EMI Shielded H2JTEG8VD1CMS 1xnm256Gb4MB4 3.0V, 3.3V / x14WLGA Now EMI Shielded H2JTFG8YD1CMS 1xnm512Gb4MB8 3.0V, 3.3V / x15WLGA Now EMI Shielded H2JTFG8PD1MMR 1xnm512Gb4MB4 3.0V, 3.3V / x16WLGA Now Non Shielded H2JT1T8QD1MMR 1xnm1024Gb4MB8 3.0V, 3.3V / x17WLGA Now Non Shielded H2JTFG8PD1MMS 1xnm512Gb4MB4 3.0V, 3.3V / x18WLGA Now EMI Shielded H2JT1T8QD1MMS 1xnm1024Gb4MB8 3.0V, 3.3V / x19WLGA Now EMI Shielded E2NAND3.0SSD : Standard 2.5” 7mm Form FactorPRODUCT DENSITYNAND COMPONENTForm Factor I/F. AVAIL. TECH.DENSITY STACKHFS064G32MNB-2200A64GB2ynm64Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MNB-2200A128GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS256G32MNB-2200A256GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS512G32MNB-2200A512GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS060G32MNB-2000A60GB2ynm64Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS120G32MNB-2000A120GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS240G32MNB-2000A240GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS480G32MNB-2000A480GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS060G32MEB-2400A60GB2ynm64Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS120G32MEB-2400A120GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS240G32MEB-2400A240GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS480G32MEB-2400A480GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MND-2200A128GB1xnm128Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS256G32MND-2200A256GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS512G32MND-2200A512GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MNC-2200A128GB1xnm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MND-3310A128GB1xnm128Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS256G32MND-3310A256GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS512G32MND-3310A512GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MNC-3310A128GB1xnm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G3BMND-3310A128GB1xnm128Gb2STD. SSD 2.5"/5mm SATA Ⅲ (6Gbps)Now HFS256G3BMND-3310A256GB1xnm128Gb4STD. SSD 2.5"/5mm SATA Ⅲ (6Gbps)Now HFS512G3BMND-3310A512GB1xnm128Gb4STD. SSD 2.5"/5mm SATA Ⅲ (6Gbps)Now HFS250G32TND-3310A250GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS500G32TND-3310A500GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS120G32MED-3410A120GB1xnm128Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS240G32MED-3410A240GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS480G32MED-3410A480GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS960G32MED-3410A960GB1xnm128Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS1T9G32MED-3410A1920GB1xnm128Gb16STD. SSD 2.5”SATA Ⅲ (6Gbps)Q2'15 HFS400G32EED-3410A400GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Q3'15 HFS800G32EED-3410A800GB1xnm128Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Q3'15 HFS1T6G32EED-3410A1600GB1xnm128Gb16STD. SSD 2.5”SATA Ⅲ (6Gbps)Q3'15SSD : mSATAPRODUCT DENSITYNAND COMPONENTForm Factor I/F. AVAIL. TECH.DENSITY STACKHFS032G3AMNB-2200A32GB2ynm64Gb2mSATA SATA Ⅲ (6Gbps)Now HFS064G3AMNB-2200A64GB2ynm64Gb2mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMNB-2200A128GB2ynm64Gb4mSATA SATA Ⅲ (6Gbps)Now HFS256G3AMNB-2200A256GB2ynm64Gb8mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMND-2200A128GB1xnm128Gb2mSATA SATA Ⅲ (6Gbps)Now HFS256G3AMND-2200A256GB1xnm128Gb4mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMNC-2200A128GB1xnm64Gb4mSATA SATA Ⅲ (6Gbps)Now HFS064G3AMND-3310A64GB1xnm128Gb2mSATA SATA Ⅲ (6Gbps)Q2'15 HFS128G3AMND-3310A128GB1xnm128Gb2mSATA SATA Ⅲ (6Gbps)Now HFS256G3AMND-3310A256GB1xnm128Gb4mSATA SATA Ⅲ (6Gbps)Now HFS512G3AMND-3310A512GB1xnm128Gb8mSATA SATA Ⅲ (6Gbps)Now HFS064G3AMNC-3310A64GB1xnm64Gb2mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMNC-3310A128GB1xnm64Gb4mSATA SATA Ⅲ (6Gbps)NowSSD : NGFF (M.2)PRODUCT DENSITYNAND COMPONENTForm Factor I/F. AVAIL. TECH.DENSITY STACKHFS032G34MNB-2200A 32GB2ynm64Gb4M.2 2242 SATA Ⅲ (6Gbps)Now HFS128G36MNB-2300A128GB2ynm64Gb4M.2 2260 SATA Ⅲ (6Gbps)Now HFS256G36MNB-2300A256GB2ynm64Gb8M.2 2260 SATA Ⅲ (6Gbps)Now HFS064G38MNB-2200A64GB2ynm64Gb4M.2 2280SATA Ⅲ (6Gbps)Now HFS128G38MNB-2200A128GB2ynm64Gb4M.2 2280 SATA Ⅲ (6Gbps)Now HFS256G38MNB-2200A256GB2ynm64Gb8M.2 2280 SATA Ⅲ (6Gbps)Now HFS256G39MND-2300A256GB1xnm128Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS032G34MNC-2200A32GB1xnm64Gb4M.2 2242 Double SATA Ⅲ (6Gbps)Now HFS128G39MNC-2300A128GB1xnm64Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS128G39MND-3310A128GB1xnm128Gb4M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS256G39MND-3310A256GB1xnm128Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS512G39MND-3310A512GB1xnm128Gb16M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS128G39MND-3510A128GB1xnm128Gb4M.2 2280 Single SATA Ⅲ (6Gbps)Q2'15 HFS064G39MNC-3510A64GB1xnm64Gb4M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS128G39MNC-3510A128GB1xnm64Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS128G39MNC-3310A128GB1xnm64Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS256GA6MND-4210A256GB1xnm128Gb8M.2 2260 Double PCIe Gen2x2Q2'15 HFS512GA6MND-4210A512GB1xnm128Gb16M.2 2260 Double PCIe Gen2x2Q2'15 HFS256GB9MND-4210A256GB1xnm128Gb8M.2 2280 Single PCIe Gen2x4Now HFS512GB9MND-4210A512GB1xnm128Gb16M.2 2280 Single PCIe Gen2x4Now HFS512GA9MND-4210A512GB1xnm128Gb16M.2 2280 Single PCIe Gen2x2Now。

Databook_Q4'2014_NAND

Q4’2014 DATABOOKRev 0.0PRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H27U1G8F2B4xnm class1Gb128KB SDP 3.3v/X8TSOP/FBGA Now-H27S1G8F2B4xnm class1Gb128KB SDP 1.8v/X8FBGA Now-H27U1G8F2C3xnm class1Gb128KB SDP3,3v/X8TSOP/FBGA Now-H27S1G8F2C3xnm class1Gb128KB SDP 1.8v/X8FBGA Now-H27U2G8F2C4ynm class2Gb128KB SDP 3.3v/X8TSOP/FBGA Now-H27S2G8F2C4ynm class2Gb128KB SDP 1.8v/X8FBGA Now-H27U2G8F2D3xnm class2Gb128KB SDP 3.3v/X8TSOP Now-H27U4G8F2D4ynm class4Gb128KB SDP 3.3v/X8TSOP Now-H27U4G8F2E3xnm class4Gb128KB SDP 3.3v/X8TSOP Now-H27U4G8F2F2xnm class4Gb256KB SDP 3.3v/X8TSOP Now -H27S4G8F2F2xnm class4Gb256KB SDP 1.8v/X8TSOP Now -H27U8G8G5D4ynm class8Gb128KB DDP 3.3v/X8TSOP Now-PRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H27UCG8T2A2ynm class64Gb2MB SDP 3.3v/X8TSOP Now-H27UCG8T2B2ynm class64Gb4MB SDP 3.3v/X8TSOP/FBGA-132 Now-H27UBG8T2C2ynm class32Gb2MB SDP 3.3v/X8TSOP Now-H27UAG8T2C2ynm class16Gb2MB SDP 3.3v/X8TSOP/PGD2Now-H27QCGDT2B2ynm class64Gb4MB SDP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QDGDUDB2ynm class128Gb4MB DDP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QEGDVEB2ynm class256Gb4MB QDP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QFGDYEB2ynm class512Gb4MB ODP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27UCG8T2E1xnm class64Gb4MB SDP 3.3v/x8TSOP Now -H27QCG8T2D1xnm class64Gb2MB SDP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QDG8UDD1xnm class128Gb2MB DDP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QEG8VED1xnm class256Gb2MB QDP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QFG8YED1xnm class512Gb2MB ODP 3.3v/x8FBGA-132Now HS(ONFi3.0) H27QCG8T2E1xnm class64Gb4MB SDP 3.3v/x8FBGA-132Now HS(Toggle2.0) H27QDG8UDE1xnm class128Gb4MB DDP 3.3v/x8FBGA-132Now HS(Toggle2.0) H27QEG8VEE1xnm class256Gb4MB QDP 3.3v/x8FBGA-132Now HS(Toggle2.0) H27QFG8YEE1xnm class512Gb4MB ODP 3.3v/x8FBGA-132Now HS(Toggle2.0) H27QCG8T2F1xnm class64Gb4MB SDP 3.3v/x8FBGA-132Q4'14HS(Toggle2.0) H27QDG8UDF1xnm class128Gb4MB DDP 3.3v/x8FBGA-132Q4'14HS(Toggle2.0) H27QEG8VEF1xnm class256Gb4MB QDP 3.3v/x8FBGA-132Q4'14HS(Toggle2.0) H27QFG8YEF1xnm class512Gb4MB ODP 3.3v/x8FBGA-132Q4'14HS(Toggle2.0) H27QDG8T2B1xnm class128Gb4MB SDP 3.3v/x8FBGA-152Now HS(Toggle2.0) H27QEG8UDB1xnm class256Gb4MB DDP 3.3v/x8FBGA-152Now HS(Toggle2.0) H27QFG8VEB1xnm class512Gb4MB QDP 3.3v/x8FBGA-152Now HS(Toggle2.0) H27Q1T8YEB1xnm class1024Gb4MB ODP 3.3v/x8FBGA-152Now HS(Toggle2.0) H27QEG8T2M3D-V2 class256Gb9MB SDP 3.3v/x8FBGA-132Q2'15HS(Toggle2.0) H27QFG8UDM3D-V2 class512Gb9MB DDP 3.3v/x8FBGA-132Q2'15HS(Toggle2.0) H27Q1T8VEM3D-V2 class1Tb9MB QDP 3.3v/x8FBGA-132Q2'15HS(Toggle2.0) H27Q2T8YEM3D-V2 class2Tb9MB ODP 3.3v/x8FBGA-132Q2'15HS(Toggle2.0) H27QCG8T2A2ynm class64Gb2MB SDP 3.3v/x8FBGA-132Now HS(ONFi2.2) H27QDG8UDA2ynm class128Gb2MB DDP 3.3v/x8FBGA-132Now HS(ONFi2.2) H27QEG8VEA2ynm class256Gb2MB QDP 3.3v/x8FBGA-132Now HS(ONFi2.2) H27QFG8YEA2ynm class512Gb2MB ODP 3.3v/x8FBGA-132Now HS(ONFi2.2)PRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H27QDG8M2M1xnm class128Gb4MB SDP 3.3v/X8FBGA-132Q4'14 (TBD)HS(Toggle2.0) H27QEG8NDM1xnm class256Gb4MB DDP 3.3v/X8FBGA-132Q4'14 (TBD)HS(Toggle2.0) H27QFG8PEM1xnm class512Gb4MB QDP 3.3v/X8FBGA-132Q4'14 (TBD)HS(Toggle2.0) H27Q1T8QEM1xnm class1Tb4MB ODP 3.3v/X8FBGA-132Q4'14 (TBD)HS(Toggle2.0)eMMCPRODUCT DENSITYBASE COMPONENTVCC/ORG VERSION AVAIL. REMARK TECH. DENSITY STACKH26M21001FPR2GB2ynm class16Gb1 3.3V/x8/x4MMC4.41Now11.5x13x0.8 H26M21001FRR2GB2ynm class16Gb1 3.3V/x8/x4MMC4.41Now11x10x0.8 H26M31002GPR4GB2ynm class32Gb1 3.3V/x8/x4MMC4.41EOL11.5x13x0.8 H26M31002GRR4GB2ynm class32Gb1 3.3V/x8/x4MMC4.41EOL11x10x0.8 H26M31003GMR4GB2ynm class32Gb1 3.3V/x8/x4MMC4.5EOL11.5x13x1.0 H26M31001HPR4GB1xnm Class32Gb1 3.3V/x8/x4MMC4.5Now 11.5x13x0.8 H26M42003GMR8GB2ynm class32Gb2 3.3V/x8/x4MMC4.5EOL11.5x13x1.0 H26M41001HPR8GB1xnm Class64Gb1 3.3V/x8/x4MMC4.5EOL11.5x13x0.8 H26M41103HPR 8GB1xnm Class64Gb1 3.3V/x8/x4MMC5.0Now11.5x13x0.8 H26M52003EQR16GB2ynm class64Gb2 3.3V/x8/x4MMC4.5EOL12x16x1.0 H26M54003EMR16GB2ynm class32Gb4 3.3V/x8/x4MMC4.5EOL11.5x13x1.0 H26M52001FMR16GB1xnm class64Gb2 3.3V/x8/x4MMC4.5EOL11.5x13x1.0 H26M52001FPR 16GB 1xnm class64Gb2 3.3V/x8/x4MMC5.0EOL11.5x13x0.8 H26M52103FPR 16GB1xnm class64Gb2 3.3V/x8/x4MMC5.0Now11.5x13x0.8 H26M52103FMR 16GB1xnm class64Gb2 3.3V/x8/x4MMC5.0Now11.5x13x1.0 H26M64003DQR32GB2ynm class64Gb4 3.3V/x8/x4MMC 4.5EOL12x16x1.0 H26M64001EMR32GB1xnm class64Gb4 3.3V/x8/x4MMC 4.5EOL11.5x13x1.0 H26M64103EMR32GB1xnm class64Gb4 3.3V/x8/x4MMC 5.0Now11.5x13x1.0 H26M78003BFR64GB2ynm class64Gb8 3.3V/x8/x4MMC 4.5EOL12x16x1.2 H26M78103CMR 64GB1xnm class64Gb8 3.3V/x8/x4MMC 5.0EOL11.5x13x1.0 H26M78103CCR64GB1xnm class64Gb8 3.3V/x8/x4MMC 5.0Now 11.5x13x1.2 H26M41208HPR 8GB1xnm class64Gb1 3.3V/x8/x4MMC 5.1Q1'1511.5x13x0.8 H26M52208FMR 16GB1xnm class64Gb2 3.3V/x8/x4MMC 5.1Q1'1511.5x13x0.8 H26M64208EMR32GB1xnm class64Gb4 3.3V/x8/x4MMC 5.1Q1'1511.5x13x1.0 H26M78208CMR64GB1xnm class64Gb8 3.3V/x8/x4MMC 5.1Q1'1511.5x13x1.0E2NAND3.0PRODUCT TECH. DENSITY BLOCK SIZE STACK VCC/ORG PKG. AVAIL. REMARK H2JTCG8T21BMR1xnm class64Gb4MB1 3.0V,3.3V/x8WLGA Now Non Shielded H2JTDG8UD1BMR1xnm class128Gb4MB2 3.0V,3.3V/x8WLGA Now Non Shielded H2JTEG8VD1BMR1xnm class256Gb4MB4 3.0V,3.3V/x8WLGA Now Non Shielded H2JTFG8YD1BMR1xnm class512Gb4MB8 3.0V,3.3V/x8WLGA Now Non Shielded H2JTDG8UD1BMS1xnm class128Gb4MB2 3.0V,3.3V/x8WLGA Now EMI Shielded H2JTEG8VD1BMS1xnm class256Gb4MB4 3.0V,3.3V/x8WLGA Now EMI Shielded H2JTFG8YD1BMS1xnm class512Gb4MB8 3.0V,3.3V/x8WLGA Now EMI ShieldedStandard 2.5" 7mm Form FactorPRODUCT DENSITYNAND COMPONENTForm Factor I/F. AVAIL. TECH.DENSITY STACKHFS064G32MNB-2200A64GB2ynm64Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MNB-2200A128GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS256G32MNB-2200A256GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS512G32MNB-2200A512GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS250G32MNB-2000A250GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)EOL HFS500G32MNB-2000A500GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)EOL HFS060G32MNB-2000A60GB2ynm64Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS120G32MNB-2000A120GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS240G32MNB-2000A240GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS480G32MNB-2000A480GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS060G32MEB-2400A60GB2ynm64Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS120G32MEB-2400A120GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS240G32MEB-2400A240GB2ynm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS400G32MEB-2420A400GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)EOL HFS480G32MEB-2400A480GB2ynm64Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MND-2200A128GB1xnm128Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS256G32MND-2200A256GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS512G32MND-2200A512GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MNC-2200A128GB1xnm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Now HFS128G32MND-3310A128GB1xnm128Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS256G32MND-3310A256GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS512G32MND-3310A512GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS128G32MNC-3310A128GB1xnm64Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS250G32TND-3300A250GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS500G32TND-3300A500GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS120G32MED-3400A120GB1xnm128Gb2STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS240G32MED-3400A240GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS480G32MED-3400A480GB1xnm128Gb4STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14 HFS960G32MED-3400A960GB1xnm128Gb8STD. SSD 2.5”SATA Ⅲ (6Gbps)Dec'14mSATAPRODUCT DENSITYNAND COMPONENTForm Factor I/F. AVAIL. TECH.DENSITY STACKHFS032G3AMNB-2200A32GB2ynm64Gb2mSATA SATA Ⅲ (6Gbps)Now HFS064G3AMNB-2200A64GB2ynm64Gb2mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMNB-2200A128GB2ynm64Gb4mSATA SATA Ⅲ (6Gbps)Now HFS256G3AMNB-2200A256GB2ynm64Gb8mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMND-2200A128GB1xnm128Gb2mSATA SATA Ⅲ (6Gbps)Now HFS256G3AMND-2200A256GB1xnm128Gb4mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMNC-2200A128GB1xnm64Gb4mSATA SATA Ⅲ (6Gbps)Now HFS128G3AMND-3310A128GB1xnm128Gb2mSATA SATA Ⅲ (6Gbps)Dec'14 HFS256G3AMND-3310A256GB1xnm128Gb4mSATA SATA Ⅲ (6Gbps)Dec'14 HFS512G3AMND-3310A512GB1xnm128Gb8mSATA SATA Ⅲ (6Gbps)Dec'14 HFS128G3AMNC-3310A128GB1xnm64Gb4mSATA SATA Ⅲ (6Gbps)Dec'14NGFF (M.2)PRODUCT DENSITYNAND COMPONENTForm Factor I/F. AVAIL. TECH.DENSITY STACKHFS032G34MNB-2200A 32GB2ynm64Gb4M.2 2242 SATA Ⅲ (6Gbps)Now HFS128G36MNB-2300A128GB2ynm64Gb4M.2 2260 SATA Ⅲ (6Gbps)Now HFS256G36MNB-2300A256GB2ynm64Gb8M.2 2260 SATA Ⅲ (6Gbps)Now HFS064G38MNB-2200A64GB2ynm64Gb4M.2 2280SATA Ⅲ (6Gbps)Now HFS128G38MNB-2200A128GB2ynm64Gb4M.2 2280 SATA Ⅲ (6Gbps)Now HFS256G38MNB-2200A256GB2ynm64Gb8M.2 2280 SATA Ⅲ (6Gbps)Now HFS128G39MND-2200A128GB1xnm128Gb4M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS256G39MND-2200A256GB1xnm128Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS128G39MNC-2200A128GB1xnm64Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Now HFS128G39MND-3310A128GB1xnm128Gb4M.2 2280 Single SATA Ⅲ (6Gbps)Dec'14 HFS256G39MND-3310A256GB1xnm128Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Dec'14 HFS512G39MND-3310A512GB1xnm128Gb16M.2 2280 Single SATA Ⅲ (6Gbps)Dec'14 HFS128G39MNC-3310A128GB1xnm64Gb8M.2 2280 Single SATA Ⅲ (6Gbps)Dec'14 HFS256GA6MND-4210A256GB1xnm128Gb8M.2 2260 Double PCIe Gen2x2Nov'14 HFS512GA6MND-4210A512GB1xnm128Gb16M.2 2260 Double PCIe Gen2x2Dec'14 HFS128GB9MND-4210A128GB1xnm128Gb4M.2 2280 Single PCIe Gen2x4Nov'14 HFS256GB9MND-4210A256GB1xnm128Gb8M.2 2280 Single PCIe Gen2x4Nov'14 HFS512GB9MND-4210A512GB1xnm128Gb16M.2 2280 Single PCIe Gen2x4Dec'14 HFS128GB9MNC-4210A128GB1xnm64Gb8M.2 2280 Single PCIe Gen2x4Dec'14 HFS256GB9MNC-4210A256GB1xnm64Gb16M.2 2280 Single PCIe Gen2x4Dec'14。

HY27UF081G2A NAND Flash数据手册