FSMC静态存储器控制器

FSMC配置

一、基本概念(详细内容见st网站stm32应用笔记AN2784)1. FSMC配置控制一个NOR闪存存储器,需要FSMC提供下述功能:●选择合适的存储块映射NOR闪存存储器:共有4个独立的存储块可以用于与NOR闪存、SRAM和PSRAM存储器接口,每个存储块都有一个专用的片选管脚。

●使用或禁止地址/数据总线的复用功能。

●选择所用的存储器类型:NOR闪存、SRAM或PSRAM。

●定义外部存储器的数据总线宽度:8或16位。

●使用或关闭同步NOR闪存存储器的突发访问模式。

●配置等待信号的使用:开启或关闭,极性设置,时序配置。

●使用或关闭扩展模式:扩展模式用于访问那些具有不同读写操作时序的存储器。

因为NOR闪存/SRAM控制器可以支持异步和同步存储器,用户只须根据存储器的参数配置使用到的参数。

FSMC提供了一些可编程的参数,可以正确地与外部存储器接口。

依存储器类型的不同,有些参数是不需要的。

当使用一个外部异步存储器时,用户必须按照存储器的数据手册给出的时序数据,计算和设置下列参数:●ADDSET:地址建立时间●ADDHOLD:地址保持时间●DATAST:数据建立时间●ACCMOD:访问模式这个参数允许FSMC可以灵活地访问多种异步的静态存储器。

共有4种扩展模式允许以不同的时序分别读写存储器。

在扩展模式下,FSMC_BTR用于配置读操作,FSMC_BWR用于配置写操作。

(译注:如果读时序与写时序相同,只须使用FSMC_BTR即可。

)如果使用了同步的存储器,用户必须计算和设置下述参数:●CLKDIV:时钟分频系数●DATLAT:数据延时如果存储器支持的话,NOR闪存的读操作可以是同步的,而写操作仍然是异步的。

当对一个同步的NOR闪存编程时,存储器会自动地在同步与异步之间切换;因此,必须正确地设置所有的参数。

2. 时序计算如上所述,对于异步NOR闪存存储器或类似的存储,有不同的访问协议。

首先要确定对特定存储器所需要使用的操作协议,选择的依据是不同的控制信号和存储器在读或写操作中的动作。

FSMC

机制

配置存储器基本特征

通过对FSMC特殊功能寄存器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应控制位的设置,FSMC根据不同存 储器特征可灵活地进行工作方式和信号的调整。

结语

STM32作为新一代ARM Cortex-M3核处理器,其卓越的性能和功耗控制能够适用于广泛的应用领域;而其特 殊的可变静态存储技术FSMC具有高度的灵活性,对于存储容量要求较高的嵌入式系统设计,能够在不增加外部分 立器件的情况下,扩展多种不同类型和容量的存储芯片,降低了系统设计的复杂性,提高了系统的可靠性。

FSMC技术优势

①支持多种静态存储器类型。STM32通过FSMC可以与SRAM、ROM、PSRAM、NOR Flash和NANDFlash存储器的 引脚直接相连。

②支持丰富的存储操作方法。FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存 储器的同步突发访问方式。

内部集成256 KB以上FlaSh,后缀为xC、xD和xE的高存储密度微控制器特有的存储控制机制。之所以称为 “可变”,是由于通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据//控制 信号类型以匹配信号的速度,从而使得STM32系列微控制器不仅能够应用各种不同类型、不同速度的外部静态存 储器,而且能够在不增加外部器件的情况下同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产 品体积以及成本的综合要求。

STM32 FSMC-LCD的FSMC配置

FSMC全称“静态存储器控制器”。

使用FSMC控制器后,可以把FSMC提供的FSMC_A[25:0]作为地址线,而把FSMC提供的FSMC_D[15:0]作为数据总线。

(1)当存储数据设为8位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_8b)地址各位对应FSMC_A[25:0],数据位对应FSMC_D[7:0](2)当存储数据设为16位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_16b)地址各位对应FSMC_A[24:0],数据位对应FSMC_D[15:0] FSMC 包括4个模块:(1)AHB接口(包括FSMC配置寄存器)(2)NOR闪存和PSRAM控制器(驱动LCD的时候LCD就好像一个PSRAM的里面只有2个16位的存储空间,一个是DATA RAM 一个是CMD RAM)(3)NAND闪存和PC卡控制器(4)外部设备接口注:FSMC可以请求AHB进行数据宽度的操作。

如果AHB操作的数据宽度大于外部设备(NOR或NAND或LCD)的宽度,此时FSMC将AHB操作分割成几个连续的较小的数据宽度,以适应外部设备的数据宽度。

FSMC对外部设备的地址映像从0x6000 0000开始,到0x9FFF FFFF 结束,共分4个地址块,每个地址块256M字节。

可以看出,每个地址块又分为4个分地址块,大小64M。

对NOR的地址映像来说,我们可以通过选择HADDR[27:26]来确定当前使用的是哪个64M的分地址块,如下页表格。

而这四个分存储块的片选,则使用NE[4:1]来选择。

数据线/地址线/控制线是共享的。

NE1 ->Bank1 NE2->Bank2 NE3->Bank3 NE4->Bank4若NE1 连接,则每小块NOR/PSRAM 64M第一块:6000 0000h--63ff ffffh (DATA长度为8位情况下,由地址线FSMC_A[25:0]决定;DATA长度为16位情况下,由地址线FSMC_A[24:0]决定)第二块:6400 0000h--67ff ffffh第二块:6800 0000h--6bff ffffh第三块:6c00 0000h--6fff ffffh注:这里的HADDR是需要转换到外部设备的内部AHB地址线,每个地址对应一个字节单元。

基于FSMC接口的CF卡数据存储系统设计

基于FSMC接口的CF卡数据存储系统设计作者:刘振海骆冬根王改董浩洪津来源:《现代电子技术》2019年第10期摘 ;要:针对现有的嵌入式存储系统中存在的存储速度慢、接口复杂等问题,提出并实现一种基于Compact FLASH(CF)卡和STM32微处理器的数据存储系统,并进行了FatFs文件系统移植。

该系统通过STM32微处理器带有的灵活的静态存储器控制器(FSMC)接口实现Memory模式下CF卡存储器的扩展,同时,测试并分析实现最大写入速度的条件。

测试结果表明,在CF卡Memory模式下,每次申请扇区数为128时,可以达到最大10 MB/s的平均连续写入速度;该方案存储速度快、实现简单,适用于对存储速度和容量均有要求的场合。

关键词:数据存储系统; STM32微处理器; FSMC接口; Compact FLASH卡; Memory模式; FatFs中图分类号: TN919⁃34; TP274; TP216 ; ; ; ; ;文献标识码: A ; ; ; ; ; ; ; ; 文章编号:1004⁃373X(2019)10⁃0015⁃04Design of CF card data storage system based on FSMC interfaceLIU Zhenhai1,2, LUO Donggen1, WANG Gai1, DONG Hao1, HONG Jin1(1. Key Laboratory of Optical Calibration and Characterization, Anhui Institute of Optics and Fine Mechanics, Chinese Academy of Sciences, Hefei 230031, China; 2. University of Chinese Academy of Sciences, Beijing 100039, China)Abstract: In allusion to the slow storage speed and complex interface problems existing in the current embedded storage system, a data storage system based on the Compact FLASH (CF) card and STM32 microprocessor is proposed and implemented, and the FatFs file system is transplanted. In the system, the CF card memory expansion in the Memory mode is realized by using the flexible static memory controller (FSMC) interface provided by the STM32 microprocessor. The conditions for achieving the maximum write⁃in speed are tested and analyzed. The test results show that the average continuous write⁃in speed of the system can reach up to 10 MB/s as the sector number applied for each time is 128 in the Memory mode of the CF card, and the scheme has a fast storage speed, is easy to be implemented, and applicable in occasions where both the storage speed and capacity requirements are needed.Keywords: data storage system; STM32 microprocessor; FSMC interface; Compact FLASH card; Memory mode; FatFsSD卡和Micro SD卡工作模式类似,支持SD和SPI两种操作模式,硬件电路接口简单,但软件协议复杂,且支持SD模式的控制器较少,一般应用中采用SPI模式[1⁃5]。

零死角玩转stm32-高级篇4、FSMC详解(3.2寸液晶触摸画板)

0、友情提示《零死角玩转STM32》系列教程由初级篇、中级篇、高级篇、系统篇、四个部分组成,根据野火STM32开发板旧版教程升级而来,且经过重新深入编写,重新排版,更适合初学者,步步为营,从入门到精通,从裸奔到系统,让您零死角玩转STM32。

M3的世界,与野火同行,乐意惬无边。

另外,野火团队历时一年精心打造的《STM32库开发实战指南》将于今年10月份由机械工业出版社出版,该书的排版更适于纸质书本阅读以及更有利于查阅资料。

内容上会给你带来更多的惊喜。

是一本学习STM32必备的工具书。

敬请期待!4、液晶触摸画板4.1实验简介本实验向大家介绍如何使用STM32的FSMC接口驱动LCD屏,及使用触摸屏控制器检测触点坐标。

4.2 LCD控制器简介LCD,即液晶显示器,因为其功耗低、体积小,承载的信息量大,因而被广泛用于信息输出、与用户进行交互,目前仍是各种电子显示设备的主流。

因为STM32内部没有集成专用的液晶屏和触摸屏的控制接口,所以在显示面板中应自带含有这些驱动芯片的驱动电路(液晶屏和触摸屏的驱动电路是独立的),STM32芯片通过驱动芯片来控制液晶屏和触摸屏。

以野火3.2寸液晶屏(240*320)为例,它使用ILI9341芯片控制液晶屏,通过TSC2046芯片控制触摸屏。

4.2.1 ILI9341控制器结构液晶屏的控制芯片内部结构非常复杂,见错误!未找到引用源。

最主要的是位于中间GRAM(Graphics RAM),可以理解为显存。

GRAM中每个存储单元都对应着液晶面板的一个像素点。

它右侧的各种模块共同作用把GRAM存储单元的数据转化成液晶面板的控制信号,使像素点呈现特定的颜色,而像素点组合起来则成为一幅完整的图像。

框图的左上角为ILI9341的主要控制信号线和配置引脚,根据其不同状态设置可以使芯片工作在不同的模式,如每个像素点的位数是6、16还是18位;使用SPI接口还是8080接口与MCU进行通讯;使用8080接口的哪种模式。

灵活的静态可变存储器控制器FSMC

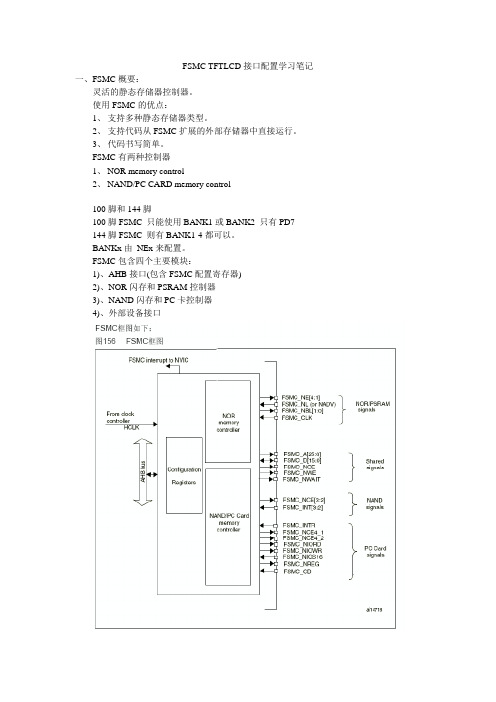

FSMC框图

FSMC 的bank 分布

4个Bank各占256M字节

Bank1分为4个region

用来连接NOR、PSRAM、LCD

Bank2和Bank3

每个Bank连接一块NAND Bank4 用来连接PC Card 每个Bank和Region有独立的寄存器 对所连存储器进行配置

NOR/PSRAM地址映射

NOR/PSRAM是”static memory map”设备:256M 字节的空间需要28根地址线寻址。

无论外接8位/16位宽度设备,FSMC_A[0]永远连接外 部设备的地址A[0]

FSMC控制读写SRAM

From: 北方工业大学嵌入式实验室

FOR: 新闻 分类信息

灵活的静态存储控制器(F实验室

FOR: 新闻 分类信息

指导老师 :吴 # 报 告 人 :李##

版权所有,未经授权请勿改动

目录

FSMC特性简介

FSMC框图 FSMC 的bank 分布 NOR/PSRAM地址映射 STM32的FSMC应用例子

版权所有,未经授权请勿改动

2012-12-10

可以在这些外部存储执行代码

LCD接口

支持8080和6800模式

NANDFlash和16位PCCard

NAND Flash具有硬件ECC

FSMC特性简介

FSMC框图

四个子模块: 1. 包含FSMC配置寄存器的AHB接口 2. NOR Flash/PSRAM控制器 3. NAND Flash/PC Card控制器 4. 和外部存储器的接口信号

FSMC控制读写SRAM FSMC连接LCD

FSMC特性简介

FSMC管理1GB空间,拥有4个Bank连接外 部存储器 每个Bank有独立的片选信号 每个Bank有独立的时序配置 同步批量传输访问最高频率可达60MHz

FSMC学习笔记

FSMC TFTLCD接口配置学习笔记一、FSMC概要:灵活的静态存储器控制器。

使用FSMC的优点:1、支持多种静态存储器类型。

2、支持代码从FSMC扩展的外部存储器中直接运行。

3、代码书写简单。

FSMC有两种控制器1、NOR memory control2、NAND/PC CARD memory control100脚和144脚100脚FSMC 只能使用BANK1或BANK2 只有PD7144脚FSMC 则有BANK1-4都可以。

BANKx由NEx来配置。

FSMC包含四个主要模块:1)、AHB接口(包含FSMC配置寄存器)2)、NOR闪存和PSRAM控制器3)、NAND闪存和PC卡控制器4)、外部设备接口二、LCD接口LCD目前大多是接到SRAM/NOR控制器上的非地址锁存,所以不能接到NAND 直接用。

LCD8080和6800接口比较8080模式:RSCSRDWRD0-D156800模式:RSCSER/WD0-D15比较明显8080和6800接口上,仅仅是读写线的差别。

参考AN2790E脚接与非门或者用普通IO口连接使用!还没有应用过6800的液晶,字符型液晶用的口没有CS脚,只有V o 、E 、RS 、RW和A、K。

三、下面根据程序做讲解:当RS接FSMC_A16 , CS接FSMC_NE1那么(*((volatile unsigned short *) 0x60000000)) /* RS = 0 */(*((volatile unsigned short *) 0x60020000)) /* RS = 1 */因为CS接FSMC_NE1 所以HADDR[27:26]为00因为RS接FSMC_A16,第17位置1,所以RS=0为0x60000000, RS=1 0x60020000。

对应的程序也是需要修改:FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;。

STM32F103-HD(高密度)中文参考手册-STM32F103xCDE_DS_CH_V5

− 51/80/112个多功能双向的I/O口,所有I/O口 可以映像到16个外部中断;几乎所有端口均 可容忍5V信号

■ 多达11个定时器

− 多达4个16位定时器,每个定时器有多达4个 用于输入捕获/输出比较/PWБайду номын сангаас或脉冲计数的 通道和增量编码器输入

− 2个16位带死区控制和紧急刹车,用于电机 控制的PWM高级控制定时器

− 转换范围:0至3.6V − 三倍采样和保持功能 − 温度传感器

■ 2 通道 12 位 D/A 转换器

■ DMA:12 通道 DMA 控制器

− 支持的外设:定时器、ADC、DAC、SDIO、 I2S、SPI、I2C和USART

■ 调试模式 − 串行单线调试(SWD)和JTAG接口 − Cortex-M3内嵌跟踪模块(ETM)

2.3.1 ARM®的Cortex™-M3核心并内嵌闪存和SRAM .................................................................. 6 2.3.2 内置闪存存储器.................................................................................................................. 6 2.3.3 CRC(循环冗余校验)计算单元............................................................................................. 7 2.3.4 内置SRAM ..................................................

stm32芯片资料

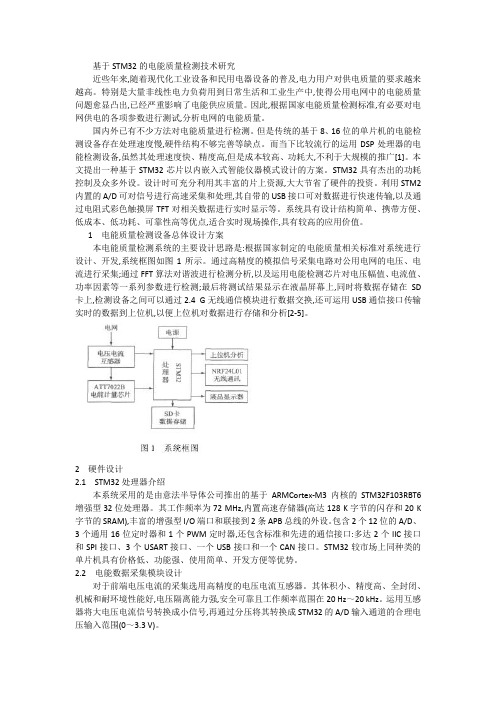

基于STM32的电能质量检测技术研究近些年来,随着现代化工业设备和民用电器设备的普及,电力用户对供电质量的要求越来越高。

特别是大量非线性电力负荷用到日常生活和工业生产中,使得公用电网中的电能质量问题愈显凸出,已经严重影响了电能供应质量。

因此,根据国家电能质量检测标准,有必要对电网供电的各项参数进行测试,分析电网的电能质量。

国内外已有不少方法对电能质量进行检测。

但是传统的基于8、16位的单片机的电能检测设备存在处理速度慢,硬件结构不够完善等缺点。

而当下比较流行的运用DSP处理器的电能检测设备,虽然其处理速度快、精度高,但是成本较高、功耗大,不利于大规模的推广[1]。

本文提出一种基于STM32芯片以内嵌入式智能仪器模式设计的方案。

STM32具有杰出的功耗控制及众多外设。

设计时可充分利用其丰富的片上资源,大大节省了硬件的投资。

利用STM2内置的A/D可对信号进行高速采集和处理,其自带的USB接口可对数据进行快速传输,以及通过电阻式彩色触摸屏TFT对相关数据进行实时显示等。

系统具有设计结构简单、携带方便、低成本、低功耗、可靠性高等优点,适合实时现场操作,具有较高的应用价值。

1电能质量检测设备总体设计方案本电能质量检测系统的主要设计思路是:根据国家制定的电能质量相关标准对系统进行设计、开发,系统框图如图1所示。

通过高精度的模拟信号采集电路对公用电网的电压、电流进行采集;通过FFT算法对谐波进行检测分析,以及运用电能检测芯片对电压幅值、电流值、功率因素等一系列参数进行检测;最后将测试结果显示在液晶屏幕上,同时将数据存储在SD 卡上,检测设备之间可以通过2.4 G无线通信模块进行数据交换,还可运用USB通信接口传输实时的数据到上位机,以便上位机对数据进行存储和分析[2-5]。

2硬件设计2.1STM32处理器介绍本系统采用的是由意法半导体公司推出的基于ARMCortex-M3内核的STM32F103RBT6增强型32位处理器。

STM32的FSMC接口直接驱动TFT屏中文版手册

2.5 TFT-LCD背光控制

在这两种显示模式,在TFT背光也通过一个定时器和一个ADC通道控制。 计时器(TIM4)被配置为生成关于PB61 KHz的PWM信号输出,可以用来作为PWM用于TFT背 光控制器使能信号。在TFT-LCD背光控制是通过改变旋转安装在MB672 STM3210E-EVAL评估 板RV1电位器PWM的占空比使能信号来实现。 有关电位器硬件的详细信息,请参阅MB672 STM3210E-EVAL评估板用户手册。

2.2图像格式和分辨率

STM32的FSMC的16位数据总线可以驱动无控制器的24位LCD模块。只有16 FMSC内存总线上 的数据线,接口是565格式的RGB。QVGA的TFT-LCD用剩下的线悬空。这些图像在外部SRAM 内存中加载的565格式,以避免转换开销为STM32。 从性能的角度来看,在内存中转换后的图像可提供快速的数据传输到TFT接口的好处。因此,更 快的图像刷新速率可以得到支持。

3硬件参考设计

该STEVAL-CCM002V1评估板,旨在作为一个子板MB672 STM3210E-EVAL评估板。该 STEVAL-CCM002V1板具有QVGA TFT3.5“(CT05350DW0000T(薄膜晶体管液晶显示器))。 下表提供了CT05350DW0000T TFT信号的描述时, 与STM32F103ZET6连接。

FSMC编译报错问题

FSMC (flexible static memory controller) 可变静态存储控制器FSMC是STM32系列中内部集成256kb以上Flash,后缀为xC、xD和xE的高存储密度微控制器特有的存储控制机制。

通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据/地址/控制信号类型以匹配信号的速度,从而使STM32系列微控制器能够在不增加外部器件的情况下,同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产品体积及成本的综合要求。

支持多种静态存储器类型。

STM32通过FSMC可以与SRAM、ROM、PSRAM、NOR Flash和NAND Flash存储器的引脚直接相连。

报错问题:添加了STM32F4资料\STM32F4xx_DSP_StdPeriph_Lib_V1.3.0\Libraries\STM32F4xx_StdPeriph_Driv er\src\中的库文件,编译时报错,报错如下:..\Lib\src\stm32f4xx_fsmc.c(129): error: #20: identifier "FSMC_Bank1" is undefinedFSMC_Bank1->BTCR[FSMC_Bank] = 0x000030DB;..\Lib\src\stm32f4xx_fsmc.c(134): error: #20: identifier "FSMC_Bank1" is undefinedFSMC_Bank1->BTCR[FSMC_Bank] = 0x000030D2;..\Lib\src\stm32f4xx_fsmc.c(136): error: #20: identifier "FSMC_Bank1" is undefinedFSMC_Bank1->BTCR[FSMC_Bank + 1] = 0x0FFFFFFF;..\Lib\src\stm32f4xx_fsmc.c(137): error: #20: identifier "FSMC_Bank1E" is undefinedFSMC_Bank1E->BWTR[FSMC_Bank] = 0x0FFFFFFF;..\Lib\src\stm32f4xx_fsmc.c(173): error: #20: identifier "FSMC_Bank1" is undefinedFSMC_Bank1->BTCR[FSMC_NORSRAMInitStruct->FSMC_Bank] =..\Lib\src\stm32f4xx_fsmc.c(210): error: #20: identifier "FSMC_Bank1E" isundefinedFSMC_Bank1E->BWTR[FSMC_NORSRAMInitStruct->FSMC_Bank] = ..\Lib\src\stm32f4xx_fsmc.c(220): error: #20: identifier "FSMC_Bank1E" is undefinedFSMC_Bank1E->BWTR[FSMC_NORSRAMInitStruct->FSMC_Bank] = 0x0FFFFFFF;..\Lib\src\stm32f4xx_fsmc.c(281): error: #20: identifier "FSMC_Bank1" is undefinedFSMC_Bank1->BTCR[FSMC_Bank] |= BCR_MBKEN_SET;..\Lib\src\stm32f4xx_fsmc.c(286): error: #20: identifier "FSMC_Bank1" is undefinedFSMC_Bank1->BTCR[FSMC_Bank] &= BCR_MBKEN_RESET;..\Lib\src\stm32f4xx_fsmc.c(354): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->PCR2 = 0x00000018;..\Lib\src\stm32f4xx_fsmc.c(363): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->PCR3 = 0x00000018;..\Lib\src\stm32f4xx_fsmc.c(422): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->PCR2 = tmppcr;..\Lib\src\stm32f4xx_fsmc.c(429): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->PCR3 = tmppcr;..\Lib\src\stm32f4xx_fsmc.c(481): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->PCR2 |= PCR_PBKEN_SET;..\Lib\src\stm32f4xx_fsmc.c(485): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->PCR3 |= PCR_PBKEN_SET;..\Lib\src\stm32f4xx_fsmc.c(493): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->PCR2 &= PCR_PBKEN_RESET;..\Lib\src\stm32f4xx_fsmc.c(497): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->PCR3 &= PCR_PBKEN_RESET;..\Lib\src\stm32f4xx_fsmc.c(521): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->PCR2 |= PCR_ECCEN_SET;..\Lib\src\stm32f4xx_fsmc.c(525): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->PCR3 |= PCR_ECCEN_SET;..\Lib\src\stm32f4xx_fsmc.c(533): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->PCR2 &= PCR_ECCEN_RESET;..\Lib\src\stm32f4xx_fsmc.c(537): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->PCR3 &= PCR_ECCEN_RESET;..\Lib\src\stm32f4xx_fsmc.c(557): error: #20: identifier "FSMC_Bank2" is undefinedeccval = FSMC_Bank2->ECCR2;..\Lib\src\stm32f4xx_fsmc.c(562): error: #20: identifier "FSMC_Bank3" is undefinedeccval = FSMC_Bank3->ECCR3;..\Lib\src\stm32f4xx_fsmc.c(617): error: #20: identifier "FSMC_Bank4" is undefinedFSMC_Bank4->PCR4 = 0x00000018;..\Lib\src\stm32f4xx_fsmc.c(653): error: #20: identifier "FSMC_Bank4" is undefinedFSMC_Bank4->PCR4 =(uint32_t)FSMC_PCCARDInitStruct->FSMC_Waitfeature |..\Lib\src\stm32f4xx_fsmc.c(716): error: #20: identifier "FSMC_Bank4" is undefinedFSMC_Bank4->PCR4 |= PCR_PBKEN_SET;..\Lib\src\stm32f4xx_fsmc.c(721): error: #20: identifier "FSMC_Bank4" is undefinedFSMC_Bank4->PCR4 &= PCR_PBKEN_RESET;..\Lib\src\stm32f4xx_fsmc.c(767): error: #20: identifier "FSMC_Bank2" is undefinedFSMC_Bank2->SR2 |= FSMC_IT;..\Lib\src\stm32f4xx_fsmc.c(772): error: #20: identifier "FSMC_Bank3" is undefinedFSMC_Bank3->SR3 |= FSMC_IT;..\Lib\src\stm32f4xx_fsmc.c(777): error: #20: identifier "FSMC_Bank4" is undefinedFSMC_Bank4->SR4 |= FSMC_IT;原因:在stm32f4xx.h中有针对不同型号的FSMC应用个定义:#if defined (STM32F40_41xxx)/*!< FSMC Bankx registers base address */#define FSMC_Bank1_R_BASE (FSMC_R_BASE + 0x0000)#define FSMC_Bank1E_R_BASE (FSMC_R_BASE + 0x0104)#define FSMC_Bank2_R_BASE (FSMC_R_BASE + 0x0060)#define FSMC_Bank3_R_BASE (FSMC_R_BASE + 0x0080)#define FSMC_Bank4_R_BASE (FSMC_R_BASE + 0x00A0)#endif /* STM32F40_41xxx */#if defined (STM32F427_437xx) || defined (STM32F429_439xx) /*!< FMC Bankx registers base address */#define FMC_Bank1_R_BASE (FMC_R_BASE + 0x0000)#define FMC_Bank1E_R_BASE (FMC_R_BASE + 0x0104)#define FMC_Bank2_R_BASE (FMC_R_BASE + 0x0060)#define FMC_Bank3_R_BASE (FMC_R_BASE + 0x0080)#define FMC_Bank4_R_BASE (FMC_R_BASE + 0x00A0)#define FMC_Bank5_6_R_BASE (FMC_R_BASE + 0x0140)#endif /* STM32F427_437xx || STM32F429_439xx */可能对该型号并未定义,那我们就直接不把这个文件加入编译吧!右键stm32f4xx_fsmc.c options for file 'stm32f4xx_fsmc.c'把以下勾都"去掉"include in tartet buildalways buildgenerate asembler src fileassenble src file。

stm32f103中文手册[1]

![stm32f103中文手册[1]](https://img.taocdn.com/s3/m/0ec05994dc3383c4bb4cf7ec4afe04a1b071b08c.png)

STM32F103中文手册概述32位ARM® Cortex®-M3内核,最高运行频率72 MHz从16 KB到1 MB的闪存,从6 KB到96 KB的SRAM从36到144个引脚的不同封装,支持LQFP、BGA、TFBGA、UFBGA和V FQFPN等从1.65 V到3.6 V的宽电源电压范围,支持低功耗模式和电池供电从-40°C到+105°C的工作温度范围多达11个通信接口,包括3个USART、2个UART、2个I2C、2个SPI、1个CAN和1个USB 2.0全速多达15个定时器,包括7个16位通用定时器、2个16位基本定时器、2个16位高级定时器、2个32位定时器和2个看门狗定时器多达3个12位模数转换器(ADC),每秒可采样1.2 M次两路12位数模转换器(DAC)多达80个外部中断/事件源多达112个GPIO端口,支持5 V耐压CRC计算单元,用于检测数据传输错误实时时钟(RTC),支持日历功能和闹钟功能嵌入式内存保护单元(MPU),用于增强应用程序安全性嵌入式调试支持,包括串行线调试(SWD)和JTAG接口7层DMA控制器,支持所有外设数据传输可选的双银行闪存模式,支持实时软件更新存储器映射STM32F103系列单片机的存储器映射如下图所示:![存储器映射]代码区:包括闪存和系统存储器。

闪存用于存储用户程序代码和数据。

系统存储器用于存储引导加载程序(bootloader)和设备标识符。

SRAM区:包括SRAM1和SRAM2。

SRAM1用于存储用户程序数据和堆栈。

SRAM2用于存储备份寄存器和备份域。

外设区:包括APB1外设、APB2外设和AHB外设。

APB1外设和APB2外设是通过两个高速总线矩阵连接到内核的低速外设。

AHB外设是通过一个高速总线矩阵连接到内核的高速外设。

外部设备区:包括FSMC区域、NOR/PSRAM区域和NAND/CF区域。

基于STM32单片机FSMC接口驱动LCD的配置与分析

修稿日期: 2018-03-13 作者简介: 李 良 ,硕 士 ,毕业于南开大学。主要研究方向:嵌入式 系统设计。

FSMC_NE4 > FSMC_NWE >

FSMC_D1 > FSMC_D3 >

> FSMC_D5

FSMC_D7 > FSMC_D9 > FSMC_D11 > FSMC_D13 > FSMC_D15 >-

存是通过三总线形式进行访问的,即地址总线、数据总线 和控制总线,只是对于不同的控制芯片总线宽度不一样而

已。STM3 2 的 FSMC[1]就 像 5 1 系列单片机的外部总线一 样 ,只不过性能更好,速度更快。本文主要分析基于STM32 芯 片 FSMC接口的ILI9341液晶显示屏的控制过程。

1 硬件连接关系

李 良 ,王 德 生 ,王 小 康 ,姜小存

(火箭军士官学校,山 东 青 州 262500)

摘 要 :液 晶 显 示 无 论 是 在 物 联 网 领 域 还 是 人 们 的 日 常 生 活 中 用 到 的 越 来 越 频 繁 ,液 晶 显 示 器 的 接 口 也 有

多 种 方 式 ,而 FSM C接 口 作 为 驱 动 L C D 显 示 的 一 种 形 式 被 广 泛 应 用 。论 文 主 要 分 析 基 于 STM3 2 单片机 FSMC接 口 的 地 址 映 射 关 系 ,并 对 FSMC接 口 的 软 件 配 置 进 行 总 结 ,为 驱 动 不 同 LC D 提 供 参 考 。 关键词:STM32; FSMC接 口 配 置 ;LCD 显示 中图分类号:TP37 文献标识码: A d〇i:10.3969/j .issn.1002-6673.2018.04.025

灵活的静态存储控制器FSMC

15

NAND/PC Card地址映射(2)

NAND的Common和Attribute空间又可细分为

Data section(第一个64KB空间)

软件从这个空间的任何地方执行读、写数据操作

Command section(第二个64KB空间)

软件往这个空间里任何地方写入命令字节 这个空间任何地址都是Addr[16]=1(CLE为高电平)

NAND/PC card控制器

19

FSMC模块的AHB接口

AHB总线上的主设备通过它访问外部静态存储器

32位的AHB读写访问转换成连续的

8位读写操作,如果访问8位宽度存储器 16位读写操作,如果访问16位宽度存储器

FSMC模块的参考时钟:HCLK

所有输出控制信号都在HCLK的上升沿改变

可以在这些外部存储执行代码

LCD接口

支持8080和6800模式

NANDFlash和16位PCCard

NAND Flash具有硬件ECC

4

FSMC框图

四个子模块:

1. 包含FSMC配置寄存器的 AHB接口 2. NOR Flash/PSRAM控制 器 3. NAND Flash/PC Card控 制器 4. 和外部存储器的接口信号

13

NOR/PSRAM地址映射的使用(2)

举例1:在Bank1的region2挂了一个16位宽度的NOR Flash

FSMC_NOR_WriteByte(u32 WriteAddr, u8 Data)

/* 1. */ NOR_WRITE(ADDR_SHIFT(0x5555), 0xAA); NOR_WRITE(ADDR_SHIFT(0x2AAA), 0x55); NOR_WRITE(ADDR_SHIFT(0x5555), 0xA0); /* 2. 往目标地址写入目标数据 */ NOR_WRITE((Bank1_NOR2_ADDR + WriteAddr), Data); /* 3. 等待NOR内部写逻辑完成 */ ……

mpu6050中文数据手册 STM32F103CDE_DS_中文数据手册_V5

mpu6050中文数据手册STM32F103CDE_DS_中文数据手册_V5导读:就爱阅读网友为您分享以下“STM32F103CDE_DS_中文数据手册_V5”的资讯,希望对您有所帮助,感谢您对92to 的支持!STM32F103xC, STM32F103xD, STM32F103xE数据手册55.1电气特性测试条件除非特别说明,所有电压的都以VSS为基准。

5.1.1 最小和最大数值除非特别说明,在生产线上通过对100%的产品在环境温度TA=25°C和TA=TAmax下执行的测试(TAmax与选定的温度范围匹配),所有最小和最大值将在最坏的环境温度、供电电压和时钟频率条件下得到保证。

在每个表格下方的注解中说明为通过综合评估、设计模拟和/或工艺特性得到的数据,不会在生产线上进行测试;在综合评估的基础上,最小和最大数值是通过样本测试后,取其平均值再加减三倍的标准分布(平均±3∑)得到。

5.1.2 典型数值除非特别说明,典型数据是基于TA=25°C和VDD=3.3V(2V ≤ VDD ≤ 3.3V电压范围)。

这些数据仅用于设计指导而未经测试。

典型的ADC精度数值是通过对一个标准的批次采样,在所有温度范围下测试得到,95%产品的误差小于等于给出的数值(平均±2∑)。

5.1.3 典型曲线除非特别说明,典型曲线仅用于设计指导而未经测试。

5.1.4 负载电容测量引脚参数时的负载条件示于图10中。

图10引脚的负载条件5.1.5 引脚输入电压引脚上输入电压的测量方式示于图11中。

图11引脚输入电压参照2009年3月STM32F103xCDE数据手册英文第5版(本译文仅供参考,如有翻译错误,请以英文原稿为准)29/87STM32F103xC, STM32F103xD, STM32F103xE数据手册5.1.6 供电方案图12供电方案注:上图中的4.7μF电容必须连接到VDD3。

浅析STM32 FSMC操作LCD的过程

浅析STM32 FSMC操作LCD的过程FSMC称为灵活的静态存储器,它能够与同步或异步存储器和16位PC存储器卡连接,(STM32)F4的FSMC(接口)支持包括S(RAM)、NAND FLASH、NOR FLASH和PSRAM等存储器。

FSMC框图从FSMC框图可以看到,FSMC将外部设备分为2类:NOR/PSRAM设备和NAND/PC卡设备。

所有外部存储器共享地址、数据和控制(信号),但有各自的片选信号。

FSMC 一次只能访问一个外部器件。

这里将LCD的片选接口与FSMC_NE4相连,即利用FSMC_NE4实现对LCD的片选;另外SRAM(芯片)的片选接口与FSMC_NE3相连,即利用FSMC_NE3实现对SRAM芯片的片选。

FSMC本身就是静态存储器(控制器),通过FSMC接口访问SRAM是理所当然的事,这里能将LCD也连接到FSMC,显然说明LCD在操作上与SRAM有相似之处。

SRAM的控制一般有:地址线(如A18A0)、数据线(如D15D0)、写信号(WE)、读信号(OE)、片选信号(CS),如果SRAM支持字节控制,那么还有UB/LB信号。

LCD的信号则包括:(寄存器)选择((RS))、数据线(D15-D0)、写信号(WE)、读信号(OE)、片选信号(CS)、复位信号RST和背光BL。

除去与访问过程无关的信号RST、BL,则两者的控制信号是极度的一致,区别仅在于SRAM有地址线(A18-A0),而LCD有RS信号线,从作用上看,两者也是一致的,都决定访问数据的位置。

若假定SRAM仅一根地址线A0,则说明数据位置仅有两个,通过A0取0和取1,区分访问的数据到底在哪个地址空间;而LCD的RS取0和取1,也说明有两个存储空间,即ILI9341的寄存器的GRAM。

显然,当把RS理解成一根地址线时,LCD就等效成SRAM了。

RS与地址线A6进行相连,因此通过把地址线中的A6置0可以访问ILI9341的寄存器,而把A6置1则可以访问GRAM。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

STM32 FSMC学习笔记FSMC全称“静态存储器控制器”。

使用FSMC控制器后,可以把FSMC提供的FSMC_A[25:0]作为地址线,而把FSMC提供的FSMC_D[15:0]作为数据总线。

(1)当存储数据设为8位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_8b)地址各位对应FSMC_A[25:0],数据位对应FSMC_D[7:0](2)当存储数据设为16位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_ 16b)地址各位对应FSMC_A[24:0],数据位对应FSMC_D[15:0]FSMC 包括4个模块:(1)AHB接口(包括FSMC配置寄存器)(2)NOR闪存和PSRAM控制器(驱动LCD的时候LCD就好像一个PSRAM的里面只有2个16位的存储空间,一个是DA TA RAM 一个是CMD RAM)(3)NAND闪存和PC卡控制器(4)外部设备接口注:FSMC可以请求AHB进行数据宽度的操作。

如果AHB操作的数据宽度大于外部设备(NOR或NAND或LCD)的宽度,此时FSMC将AHB操作分割成几个连续的较小的数据宽度,以适应外部设备的数据宽度。

FSMC对外部设备的地址映像从0x6000 0000开始,到0x9FFF FFFF结束,共分4个地址块,每个地址块256M字节。

可以看出,每个地址块又分为4个分地址块,大小64M。

对NOR的地址映像来说,我们可以通过选择HADDR[27:26]来确定当前使用的是哪个64M的分地址块,如下页表格。

而这四个分存储块的片选,则使用NE[4:1]来选择。

数据线/地址线/控制线是共享的。

NE1 ->Bank1 NE2->Bank2 NE3->Bank3 NE4->Bank4若 NE1 连接,则每小块NOR/PSRAM 64M第一块:6000 0000h--63ff ffffh (DATA长度为8位情况下,由地址线FSMC_A[25:0]决定;DATA长度为16位情况下,由地址线FSMC_A[24:0]决定)第二块:6400 0000h--67ff ffffh第二块:6800 0000h--6bff ffffh第三块:6c00 0000h--6fff ffffh注:这里的HADDR是需要转换到外部设备的内部AHB地址线,每个地址对应一个字节单元。

因此,若外部设备的地址宽度是8位的,则HADDR[25:0]与STM32的CPU引脚FSMC_A[25:0]一一对应,最大可以访问64M字节的空间。

若外部设备的地址宽度是16位的,则是HADDR[25:1]与STM32的CPU引脚FSMC_A[24:0]一一对应。

在应用的时候,可以将F SMC_A总线连接到存储器或其他外设的地址总线引脚上。

例:STM32F10XX FCMS控制LCD的驱动FSMC提供了所有的LCD控制器的信号:FSMC_D[16:0] 16bit的数据总线FSMC NEx:分配给NOR的256M,再分为4个区,每个区用来分配一个外设,这四个外设的片选分为是NE1-NE4,对应的引脚为:PD7—NE1,PG9—NE2,PG10-NE3,PG12—NE4FSMC NOE:输出使能,连接LCD的RD脚。

FSMC NWE:写使能,连接LCD的RW脚。

FSMC Ax:用在LCD显示RAM和寄存器之间进行选择的地址线,即该线用于选择LCD的RS脚,该线可用地址线的任意一根线,范围:FSMC_A[25:0]。

注:RS =0时,表示读写寄存器;RS =1表示读写数据RAM。

举例1:选择NOR的第一个存储区,并且使用FSMC_A16来控制LCD的RS引脚,则我们访问LCD显示RAM的基址为0 x6002 0000,访问LCD寄存器的地址为:0x6000 0000。

因为数据长度为16bit ,所以FSMC_A[24:0]对应HADDR[2 5:1] 所以显示RAM的基址=0x60000000+2^16*2=0x60000000+0x2 0000=0x60020000举例2:选择NOR的第四个存储区,使用FSMC_A0控制LCD的RS脚,则访问LCD显示RAM的基址为0x6c00 0002,访问LCD寄存器的地址为:0x6c00 0000。

例:FSMC_D[15:0],连16bit数据线;FSMC_NE1,连片选:只有bank1可用FSMC NOE:输出使能FSMC NEW:FSMC写使能FSMC Ax:连接RS,可用范围FSMC_A[24:0]一般使用模式B来做LCD的接口控制,不适用外扩模式。

并且读写操作的时序一样。

此种情况下,我们需要使用三个参数:A DDSET,DATAST,ADDHOLD。

这三个参数在位域FSMC_TCRx中设置。

当HCLK的频率是72MHZ,使用模式B,则有如下时序:地址建立时间:0x1地址保持时间:0x0数据建立时间:0x2注:这里地址建立地址保持数据建立三个时间不知道怎么设出来的。

我是根据别人的经验来设定的。

高手知道这个设置不同有什么区别的话,请指教,谢谢:)/******************************************************************************** 函数名: LCD_CtrlLinesConfig* 参数: 无* 返回: 无* 功能: 配置LCD控制口线,FSMC管脚设置为复用功能*/static void LCD_CtrlLinesConfig(void){GPIO_InitTypeDef GPIO_InitStructure;/* 使能 FSMC, GPIOD, GPIOE, GPIOF, GPIOG 和 AFIO 时钟 */RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC, ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB | RCC_APB2Periph_GPIOD | RCC_APB2Periph_GPIOE |RCC_APB2Periph_GPIOF | RCC_APB2Periph_GPIOG |RCC_APB2Periph_AFIO, ENABLE);/* 设置 PD.00(D2), PD.01(D3), PD.04(NOE), PD.05(NWE), PD.08(D13), PD.09(D14),PD.10(D15), PD.14(D0), PD.15(D1) 为复用推挽输出 */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_4 | GPIO_Pin_5 |GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_14 |GPIO_Pin_15; // | GPIO_Pin_7;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_Init(GPIOD, &GPIO_InitStructure);/* 设置 PE.07(D4), PE.08(D5), PE.09(D6), PE.10(D7), PE.11(D8), PE.12(D9), PE.13(D10),PE.14(D11), PE.15(D12) 为复用推挽输出 *//* PE3,PE4 用于A19, A20, STM32F103ZE-EK(REV 2.0)必须使能 *//* PE5,PE6 用于A19, A20, STM32F103ZE-EK(REV 2.0)必须使能 */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 |GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 | GPIO_Pin_14 |GPIO_Pin_15 | GPIO_Pin_3 | GPIO_Pin_4 | GPIO_Pin_5 | GPIO_Pin_6; GPIO_Init(GPIOE, &GPIO_InitStructure);/* 设置 PF.00(A0 (RS)) 为复用推挽输出 */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0;GPIO_Init(GPIOF, &GPIO_InitStructure);/* 设置 PG.12(NE4 (LCD/CS)) 为复用推挽输出 - CE3(LCD /CS) */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_12;GPIO_Init(GPIOG, &GPIO_InitStructure);GPIO_InitStructure.GPIO_Pin = GPIO_Pin_1;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(GPIOB, &GPIO_InitStructure);GPIO_SetBits(GPIOB, GPIO_Pin_1);}static void LCD_FSMCConfig(void){FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;FSMC_NORSRAMTimingInitTypeDef FSMC_NORSRAMTimingInitStructure;/*-- FSMC Configuration ------------------------------------------------------*/ /*----------------------- SRAM Bank 4 ----------------------------------------*/ /* FSMC_Bank1_NORSRAM4 configuration */FSMC_NORSRAMTimingInitStructure.FSMC_AddressSetupTime = 1;FSMC_NORSRAMTimingInitStructure.FSMC_AddressHoldTime = 0;FSMC_NORSRAMTimingInitStructure.FSMC_DataSetupTime = 2;FSMC_NORSRAMTimingInitStructure.FSMC_BusTurnAroundDuration = 0;FSMC_NORSRAMTimingInitStructure.FSMC_CLKDivision = 0;FSMC_NORSRAMTimingInitStructure.FSMC_DataLatency = 0;FSMC_NORSRAMTimingInitStructure.FSMC_AccessMode = FSMC_AccessMode_B;/* Color LCD configuration ------------------------------------LCD configured as follow:- Data/Address MUX = Disable- Memory Type = SRAM- Data Width = 16bit- Write Operation = Enable- Extended Mode = Enable- Asynchronous Wait = Disable */FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState; FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &FSMC_NORSRAMTimingInitStructure; FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &FSMC_NORSRAMTimingInitStructure;FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);/* - BANK 3 (of NOR/SRAM Bank 0~3) is enabled */FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM4, ENABLE);}。