DC使用全书(Design_Compiler)

Design Compiler 一般问题解答

Design Compiler 一般问题解答1.1 什么是DC?DC(Design Compiler)是Synopsys公司的logical synthesis工具,它根据design description 和design constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如HDL、Schematics、Netlist等,并能生成多种性能report,在reducing design time的同时提高了设计的性能。

1.2 DC能接受多少种输入格式?支持.db、.v、.vhd、.edif、.vgh、.lib等,.db一般是厂商的单元库;.v是veilog的后缀;.vhd 是VHDL的后缀;.edif 和.vhd是两种形式的netlist。

1.3 DC提供多少种输出格式?提供.db、.v、.vhd、edif、.vgh等,并可以输出sdc、sdf等相关格式文件。

1.4 DC的主要功能或者主要作用是什么?DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing、area、power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证。

1.5 如何寻找帮助?帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令(我最喜欢这种)3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档?SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,如:工艺库,目标库,标志库等等。

要在.synopsys_dc.setup上设置好这些参数。

而.synopsys_dc.setup要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

DesignCompiler一般问题解答

DesignCompiler一般问题解答Design Compiler 一般问题解答1.1 什么是DC?DC(Design Compiler)是Synopsys公司的logical synthesis工具,它根据design description 和design constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如HDL、Schematics、Netlist等,并能生成多种性能report,在reducing design time的同时提高了设计的性能。

1.2 DC能接受多少种输入格式?支持.db、.v、.vhd、.edif、.vgh、.lib等,.db一般是厂商的单元库;.v是veilog的后缀;.vhd 是VHDL的后缀;.edif 和.vhd是两种形式的netlist。

1.3 DC提供多少种输出格式?提供.db、.v、.vhd、edif、.vgh等,并可以输出sdc、sdf等相关格式文件。

1.4 DC的主要功能或者主要作用是什么?DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing、area、power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证。

1.5 如何寻找帮助?帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令(我最喜欢这种)3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档?SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,如:工艺库,目标库,标志库等等。

要在.synopsys_dc.setup上设置好这些参数。

使用Design Compiler进行电路综合

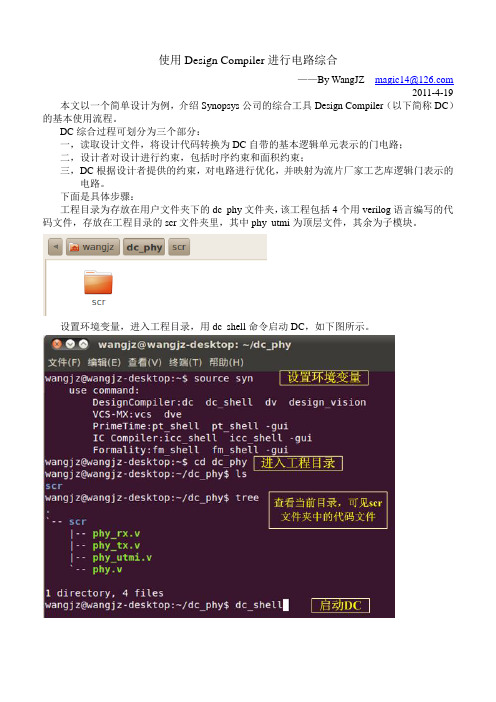

使用Design Compiler进行电路综合——By WangJZ magic14@2011-4-19 本文以一个简单设计为例,介绍Synopsys公司的综合工具Design Compiler(以下简称DC)的基本使用流程。

DC综合过程可划分为三个部分:一,读取设计文件,将设计代码转换为DC自带的基本逻辑单元表示的门电路;二,设计者对设计进行约束,包括时序约束和面积约束;三,DC根据设计者提供的约束,对电路进行优化,并映射为流片厂家工艺库逻辑门表示的电路。

下面是具体步骤:工程目录为存放在用户文件夹下的dc_phy文件夹,该工程包括4个用verilog语言编写的代码文件,存放在工程目录的scr文件夹里,其中phy_utmi为顶层文件,其余为子模块。

设置环境变量,进入工程目录,用dc_shell命令启动DC,如下图所示。

使用set search_path命令设置搜索路径,用set target_library命令设置目标库(流片厂所提供的工艺库)所在路径,用set link_library命令设置链接库路径,如下图所示。

用read_verilog命令读取设计文件,虽然设计文件并不在当前目录dc_phy中,但由于设置了搜索路径(set search_path “$ search_path ./scr”),所以DC仍能找scr文件夹中的设计文件,如下图所示。

用current_design命令告知DC,设计的顶层模块为phy_utmi,并用link命令链接到工艺库,如下图所示:对设计进行时序约束和面积,由于本设计比较简单,所以仅进行几个简单约束作为演示。

约束完后使用compile命令进行综合,如下图所示:综合完成后,使用write命令输出门级网表,使用write_sdc命令输出设计约束,获取门级网表和约束文件后,就可以使用Cadence公司的Encounter软件进行自动布局布线了。

过程如下图所示。

Design Compiler使用简要说明

Design Compiler 使用简要说明Design Compiler可以针对层次化的组合电路或者时序电路的速度、面积和可布性进行优化。

按照所定义的电路的测量特征所要达到的目标,Design Compiler综合一个电路并将其放入目标库中,这样可以生成适用于你的计算机辅助设计工程(CAE)工具的原理图或网表。

综合的过程如下图:•读入设计及其子设计。

•设置顶层的设计特性参数•设置实际时序和面积目标参数•执行check_design验证设计,识别并且更正错误•进行Design Compiler优化在db、verilog、vhdl文件夹下设计内容都是一样的,只是形式不一样。

Db文件夹:ALARM_BLOCK.db ALARM_COUNTER.db ALARM_SM.dbALARM_STATE_MACHINE.db COMPARATOR.dbHOURS_FILTER.db MUX.db TIME_BLOCK.dbTIME_COUNTER.dbTIME_STATE_MACHINE.db CONVERTOR.pla CONVERTOR_CKT.db TOP.dbVerilog文件夹:ALARM_BLOCK.v ALARM_COUNTER.v ALARM_SM.vALARM_STATE_MACHINE.v COMPARATOR.vHOURS_FILTER.v MUX.vTIME_BLOCK.vTIME_COUNTER.vTIME_STATE_MACHINE.v CONVERTOR.pla CONVERTOR_CKT.v TOP.vVhdl文件夹:ALARM_BLOCK.vhd ALARM_BLOCK.vhd ALARM_SM.vhdALARM_STATE_MACHINE.vhd COMPARATOR.vhdHOURS_FILTER.vhd MUX.vhd TIME_BLOCK.vhdTIME_COUNTER.vhdTIME_STATE_MACHINE.vhd CONVERTOR.pla CONVERTOR_CKT.vhd TOP.vhd设置path参数将 Synopsys_installroot/arch/syn/bin加到.cshrc文件中。

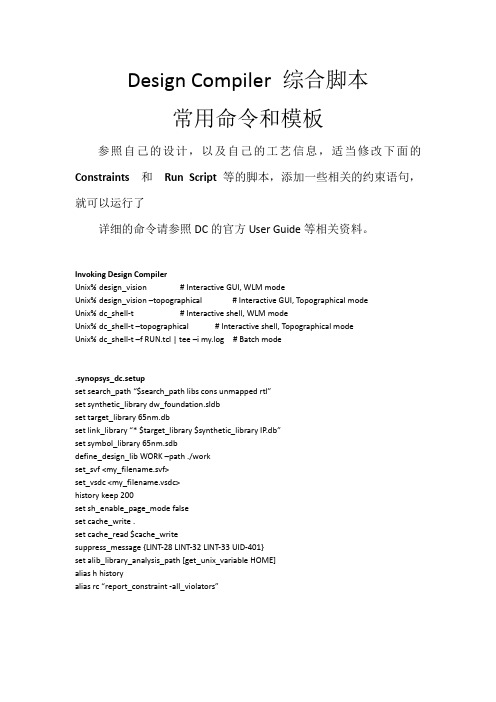

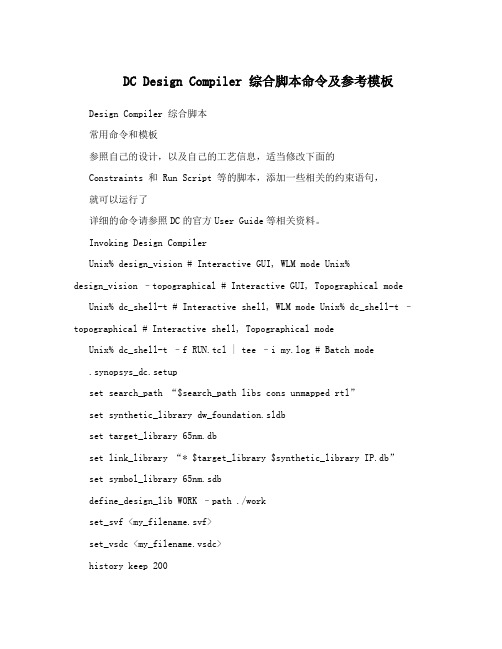

DC Design Compiler 综合脚本命令及参考模板

Design Compiler 综合脚本常用命令和模板参照自己的设计,以及自己的工艺信息,适当修改下面的Constraints和Run Script 等的脚本,添加一些相关的约束语句,就可以运行了详细的命令请参照DC的官方User Guide等相关资料。

Invoking Design CompilerUnix% design_vision # Interactive GUI, WLM modeUnix% design_vision –topographical # Interactive GUI, Topographical modeUnix% dc_shell-t # Interactive shell, WLM modeUnix% dc_shell-t –topographical # Interactive shell, Topographical modeUnix% dc_shell-t –f RUN.tcl | tee –i my.log # Batch mode.synopsys_dc.setupset search_pa th “$search_path libs cons unmapped rtl”set synthetic_library dw_foundation.sldbset target_library 65nm.dbset link_library “* $target_library $synthetic_library IP.db”set symbol_library 65nm.sdbdefine_design_lib WORK –path ./workset_svf <my_filename.svf>set_vsdc <my_filename.vsdc>history keep 200set sh_enable_page_mode falseset cache_write .set cache_read $cache_writesuppress_message {LINT-28 LINT-32 LINT-33 UID-401}set alib_library_analysis_path [get_unix_variable HOME]alias h historyalias rc “report_constraint -all_violators”TCL Commands and Constructsset PER 2.0 # Define a variable and its valueecho $PER # Variable substitution → 2.0set MARG 0.95expr $PER * $MARG # expr: *, /, +, -, >, <, =, <=, >=set pci_ports [get_ports A] # Imbedded commandset pci_ports [get_ports “Y??M Z*”]# Wildcardsecho “Effctv P = \ # Soft quotes → 1.9[expr $PERIOD * $MARGIN]”echo {Effctv P = \ # Hard quotes[expr $PERIOD * $MARGIN]} # → Effctv P = [expr $PER * $MARG] # Comment lineset COMMENT in_line; # In-line commentset MY_DESIGNS {B1.v ... B26.v} # foreach loopforeach DESIGN $MY_DESIGNS {read_verilog $DESIGN}for {set i 1} {$i < 27} {incr i} { # for loopread_verilog BLOCK_$i.v}Helpful UNIX-like DC-shell commandspwdcdlshistory!!!7!reportsh <UNIX_command>printenvget_unix_variable ARCHConstraintsreset_designset_max_area 0create_clock -period 2 –name Main_Clk [get_ports Clk1]create_clock –period 2.5 –waveform {2 3.5} [get_ports Clk2]create_clock –period 3.5 –name V_Clk; # VIRTUAL clockset_clock_uncertainty –setup 0.14 [get_clocks *]set_clock_uncertainty –setup 0.21 –from [get_clocks Main_Clk] –to [get_clocks Clk2]set_clock_latency –max 0.6 [get_clocks Main_Clk]set_clock_latency –source –max 0.3 [get_clocks Main_Clk]set_clock_transition 0.08 [get_clocks Main_Clk]set_input_delay -max 0.6 -clock Main_Clk [all_inputs]set_input_delay –max 0.3 –clock Clk2 –clock_fall –add_delay [get_ports “B E”]set_input_delay -max 0.5 -clock –network_latency_included V_Clk [get_ports “A C F”]set_output_delay -max 0.8 -clock –source_latency_included Main_Clk [all_outputs]set_output_delay -max 1.1 -clock V_Clk [get_ports “OUT2 OUT7]set_max_capacitance 1.2 [all_inputs]set_load 0.080 [all_outputs]set_load [expr [load_of slow_proc/NAND2_3/A] * 4] [get_ports OUT3]set_load 0.12 [all_inputs]set_input_transition 0.12 [remove_from_collection [all_inputs][get_ports B]]set_driving_cell –lib_cell FD1 –pin Q [get_ports B]set_operating_conditions –max WCCOMset auto_wire_load_selection falseset_wire_load_model –name 1.6MGatesset_wire_load_mode enclosedset_wire_load_model –name 200KGates [get_designs “SUB1 SUB2”]set_wire_load_model –name 3.2MGates [get_ports IN_A]set_port_fanout_number 8 [get_ports IN_A]set_false_path -from [get_clocks Asynch_CLKA] -to [get_clocks Asynch_CLKB]set_multicycle_path –setup 4 –from –from A_reg -through U_Mult/Out –to B_regset_multicycle_path –hold 3 –from –from A_reg -through U_Mult/Out –to B_regset_isolate_ports –type inverter [all_outputs]set_ideal_network [get_ports reset* select*]set_ideal_network [get_pins FF_SET_reg/Q]set_ideal_network –no_propagate [get_nets CTRL]set_ideal_latency 1.4 [get_ports reset* select*]set_ideal_transition 0.5 [get_pins FF_SET_reg/Q]set_scan_configuration -style <multiplexed_flip_flop | clocked_scan | lssd | aux_clock_lssd>Checking and Removing Constraints and Directivesreport_clock; report_clock -skewreport_designreport_port –verbosereport_wire_loadreport_path_groupsreport_timing_requirements (–ignored)report_auto_ungroupreport_isolate_portswrite_script –output <constraints.tcl>check_timingreset_path –from FF1_regremove_clockremove_clock_transitionremove_clock_uncertaintyremove_input_delayremove_output_delayremove_driving_cellremove_wire_load_modelSyntax CheckingUnix% dcprocheck constr_file.conPhysical Constraints – Topographical Modeset_aspect_ratioset_utilizationset_placement_areaset_rectilinear_outlineset_port_sideset_port_locationset_cell_locationcreate_placement_keepoutMisc. Reports# Generate A library report fileread_db library_file.dblist_libsredirect –file reports/lib.rpt {report_lib <libname>} report_hierarchy [-noleaf]# Arithmetic implementation and# resource-sharing inforeport_resources# List area for all cells in the designreport_cell [get_cells –hier *]Run Scriptread_verilog {A.v B.v TOP.v} orread_vhdl {A.vhd B.vhd TOP.vhd} orread_ddc MY_TOP.ddc oracs_read_hdl MY_TOP oranalyze –format verilog {A.v B.v TOP.v}elaborate MY_TOP –parameters “A_WIDTH=8, B_WIDTH=16”current_design MY_TOPlinkif {[check_design] ==0} {echo “Check Design Error”exit # Exits DC if a check-design error is encountered} # Continue if NO problems encounteredwrite –f ddc –hier –out unmappedd/TOP.ddcredirect –tee –file reports/precompile.rpt {source –echo -verbose TOP.con}redirect –append –tee –file reports/precompile.rpt {check_timing}source <Physical_Constraints_TCL_file> or # Source tcl constraints, if available, or extract_physical_constraints <DEF_file> # Extract and apply from an existing # DEF floorplan filegroup_path -name CLK1 -critical_range <10% of CLK1 Period> –weight 5group_path -name CLK2 -critical_range <10% of CLK2 Period> –weight 2group_path –name INPUTS –from [all_inputs]group_path –name OUTPUTS –to [all_outputs]group_path –name COMBO –from [all_inputs] –to [all_outputs]set_fix_multiple_port_nets –all –buffer_constants********************************************************** ** Insert Expert, Ultra or ACS compile flow here ** **********************************************************check_designreport_constraint –all_violatorsreport_timing –delay –to –from –through –input_pins –max_paths \–nworst –nets –cap –sig –groupreport_areareport_qorset verilogout_no_tri truechange_names –rule verilog –hierwrite –f verilog –hier –out mapped/TOP.vwrite –f ddc –hier –out mapped/TOP.ddcwrite_sdc TOP.sdcwrite_scan_def –out TOP_scan.defwrite_physical_constraints –output TOP_PhysConstr.tcl exitObject Retrieval and Manipulation (Collection Commands) get_ports, get_pins, get_designsget_cells, get_nets, get_clocksget_nets –of_objects [get_pins FF1_reg/Q]get_libs <lib_name>get_lib_cells <lib_name/cell_names>get_lib_pins <lib_name/cell_name/pin_names>all_inputs, all_outputs, all_clocks, all_registersall_connectedall_fanin, all_fanoutall_ideal_netsset pci_ports [get_ports pci_*]echo $pci_ports # → _sel184 query_objects $pci_ports # → {pci_1 pci_2 ...} get_object_name $pci_ports # → pci_1 pci_2 ... sizeof_collection $pci_ports # → 37set pci_ports [add_to_collection $pci_ports \[get_ports CTRL*]]set all_inputs_except_clk [remove_from_collection \ [all_inputs] [get_ports CLK]]compare_collectionsindex_collectionsort_collectionforeach_in_collection my_cells [get_cells -hier * \ -filter “is_hierarchical == true”] {echo “Instance [get_object_name $cell] is hierarchical”}# Filtering operators: ==, !=, >, <, >=, <=, =~, !~filter_collection [get_cells *] “ref_name =~ AN*”get_cells * -filter “dont_touch == true”get_clocks * -filter “period < 10”# List all cell attributes and redirect output to a fileredirect –file cell_attr \{list_attributes –application –class cell}# Grep the file for cell attributes starting with dont_UNIX% grep dont_ cell_attr | more# List the value of the attribute dont_touchget_attribute <cell_name> dont_touchUltra Compile Flow - Topographical or WLM ModeUltra + DesignWare and DFTC licenses available# In “topo” mode (dc_shell-t –topo) specify Milkyway reference and design libraries create_mw_lib –tech <technology_file> -mw_reference_library <mw_reference_libraries> \<mw_design_library_name>open_mw_lib <mw_design_library_name>set_tlu_plus_files -max_tluplus <max_tluplus_file> -tech2itf_map <mapping_file>set compile_auto_ungroup_delay_num_cells 99999999set compile_auto_ungroup_count_leaf_cells trueset compile_auto_ungroup_override_wlm trueset_ungroup <top_level_and/or_pipelined_blocks> false# OPTIONAL: Disable unconditional auto-ungrouping# of DesignWare hierarchy (not usually recommended)set compile_ultra_ungroup_dw false# If design contains pipelined sub-designs and the pipeline registers# are grouped together at the input or output, relax timingset_multicycle_path –setup <#_stages> -from U_Pipeline/R3_reg* –to U_Pipeline/R7_reg* # In “ topo” mode, if the floorplan is available, apply or extract the physical constraints source <physical_constraints_file> ORextract_physical_constraints <DEF_file># OPTIONAL: Exclude specific cells/design from adaptive retiming (-retime)set_dont_retime <cells_or_designs> true# First compilecompile_ultra –scan –retime –timing|-area# The design hierarchy may have changed due to auto-ungrouping/-uniquifyingreset_path -from U_Pipeline/R3_reg* -to U_Pipeline/R7_reg*# OPTIONAL: Maintain registered pipeline outputs if requiredset_dont_touch [get_cells U_Pipeline/R12_reg*] true# Optimize registers if pipeline violates timing; Skip if no pipeline issues:set_optimize_registers true –design My_Pipeline_Subdesignoptimize_registers –only_attributed_designs# Continue if design is NOT meeting all constraints:# Apply more focus on violating critical paths, as necessarygroup_path –name <group_name> -from <path_start> -to <path_end> \–critical range <10% of max delay goal> -weight 5# Select appropriate second compile# In “topo” mode in DC v2006.06, or any mode in DC v2007.03 or latercompile_ultra –scan –incremental# In “WLM” mode in DC v2006.06set_ultra_optimization truecompile –boundary –scan –map_effort high –incremental (-area_effort medium|low|none) # In “topo” mode prior to DC v2007.03: Write out updated physical constraintswrite_physical_constraints –output PhysConstr.tclDFT Flow – Expert or UltraDFTC license available# Prior to the first compile set the# scan cell styleset_scan_configuration –style ..# Perform the first test-ready compilecompile –boundary –map high –scan # ORcompile_ultra –timing -scan# Continue before the next compile:# Read in the scan specification filesource scan_spec.tcl# Check for DFT rule violationsdft_drc# Preview the scan chainspreview_dft# Insert and optimize scaninsert_dft******************************************************* * * Execute additional Ultra/Expert optimization ** techniques, as needed ** * ******************************************************# After the final compile check the DFT QoR# and write out the scan DEF filedft_drc –coverage_estimatewrite_scan_def -out <my_design.def>Some Scan Specification Commandsset_scan_state test_readyset_dft_configuration ...set_dft_signal ...set_scan_path ...set_scan_configuration ...create_test_protocolExpert Compile FlowNo Ultra license available; DFTC license availablecompile –boundary –scan –map_effort high# Continue if NOT meeting constraints# Note: -scan requires DFTC licensecompile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Continue if NOT meeting constraints:# Increase max-delay priority if OK to postpone DRC fixingset_cost_priority –delay# Note: The design hierarchy may have changed due to auto- # uniquifying# Apply more focus on violating critical paths, as necessary group_path –name <group_name> -from <path_start> \-to <path_end> –critical range <10% of max delay goal> -weight 5 # Repartition if design is poorly partitionedgroup –design <NEW_DESIGN> -cell_name <U_NEW_CELL> \{U2 U7 ...}ungroup –start_level 2 U_NEW_CELLcompile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Or, can ungroup all hierarchy in lieu of group/ungroup# commands with –ungroup_allcompile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none) –ungroup_all“Pseudo Ultra” Compile FlowUltra license available; No DesignWare license availableset compile_auto_ungroup_delay_num_cells 99999999set compile_auto_ungroup_area_num_cells 99999999set compile_auto_ungroup_count_leaf_cells trueset compile_auto_ungroup_override_wlm trueset_ungroup <top_level_and/or_pipelined_blocks> false# OPTIONAL: Disable unconditional auto-ungrouping# of DesignWare hierarchy (not usually recommended)set compile_ultra_ungroup_dw false# If design contains pipelined sub-designs and the pipeline registers# are grouped together at the input or output, relax timingset_multicycle_path –setup <#_stages> \-from U_Pipeline/R3_reg* –to U_Pipeline/R7_reg*# Enable Ultra optimizations available for compileset_ultra_optimization –no_auto_dwlib trueset hlo_disable_datapath_optimization trueset compile_slack_driven_buffering truecompile –boundary –scan –map_effort high –auto_ungroup delay|area \ (-area_effort medium|low|none)# Note: The design hierarchy may have changed due to auto-# ungrouping and auto-uniquifyingreset_path -from U_Pipeline/R3_reg* -to U_Pipeline/R7_reg*# OPTIONAL: Maintain registered pipeline outputs if requiredset_dont_touch [get_cells U_Pipeline/R12_reg*] true# Optimize registers if pipeline violates timing; Skip if no pipeline issues:set_optimize_registers true –design My_Pipeline_Subdesignoptimize_registers –only_attributed_designs# Continue if design is NOT meeting all constraints:compile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Continue if NOT meeting all constraints:set_cost_priority –delay# Ungroup DesignWare components amid combinational logicungroup <DesignWare_components># Apply more focus on violating critical paths, as necessarygroup_path –name <group_name> -from <path_start> -to <path_end> \–critical range <10% of max delay goal> -weight 5compile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)。

design-compiler的安装和使用资料

的,该文件在scl目录下)

的实际路劲

修改主机名

用记事本打开“synopsys.dat”,将第一行修改为:SERVER 主机名 MAC地址 27000。其中主机名是Linux系统下的主机名,可在Linux的终端中用“uname -a”命 令查看,默认一般为“localhost.localdomain”;MAC地址就是网卡地址,后面的 27000是默认需要的。本文中该行信息为“SERVER localhost.localdomain 000c2916d785 27000”

Design_Compiler_2008.09_common.tar

Design_compiler_2008.09_linux.tar 3.安装DC2008需要用到SCL软件包

scl_v10.9.3_common.tar

scl_v10.9.3_linux.tar 4.安装平台 在linux4.6上安装(如果要使用虚拟机,则使用vmware6.5,使用虚拟机有 很多方便,可以在虚拟机中随时读取windows下的文件,资料复制都很方便 (可以直接往linux系统里面拖资料!),而且对于在只有一台电脑的情况下, 可以利用windows平台查看课件,查资料等)

3.利用KeyGen得到得到FEATURE SSS信息 ,运行“KeyGen.exe”,在“SECRET DATA” 栏中填入得到的SECRET DATA码,在“HOST ID”中填入你的MAC地址。

我们刚才得到的SECRET DATA

你的MAC地址

点击Generate后,会在此文件夹中生成一个license.dat的文件。

众多,为了方便,最好分类安放,下面是我文件夹内部的目录结构,仅供参考以 及便于后面的说明。建议安装的时候也参考这样。

DC使用说明

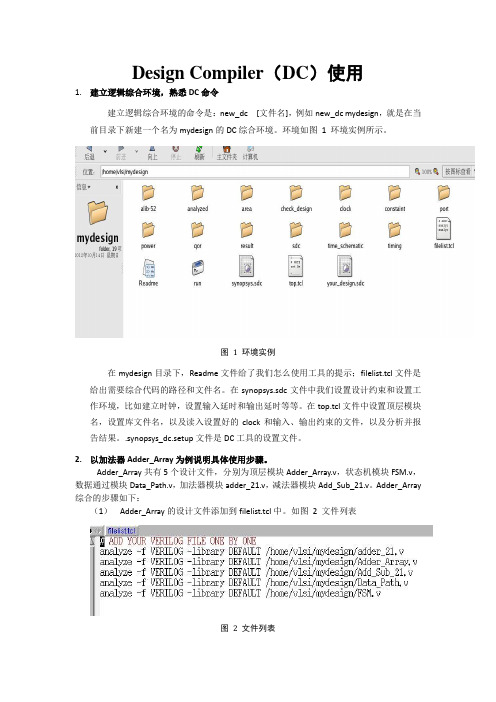

Design Compiler(DC)使用1.建立逻辑综合环境,熟悉DC命令建立逻辑综合环境的命令是:new_dc [文件名],例如new_dc mydesign,就是在当前目录下新建一个名为mydesign的DC综合环境。

环境如图1 环境实例所示。

图1 环境实例在mydesign目录下,Readme文件给了我们怎么使用工具的提示;filelist.tcl文件是给出需要综合代码的路径和文件名。

在synopsys.sdc文件中我们设置设计约束和设置工作环境,比如建立时钟,设置输入延时和输出延时等等。

在top.tcl文件中设置顶层模块名,设置库文件名,以及读入设置好的clock和输入、输出约束的文件,以及分析并报告结果。

.synopsys_dc.setup文件是DC工具的设置文件。

2.以加法器Adder_Array为例说明具体使用步骤。

Adder_Array共有5个设计文件,分别为顶层模块Adder_Array.v,状态机模块FSM.v,数据通过模块Data_Path.v,加法器模块adder_21.v,减法器模块Add_Sub_21.v。

Adder_Array 综合的步骤如下:(1)Adder_Array的设计文件添加到filelist.tcl中。

如图2 文件列表图2 文件列表(2)在top.tcl中将顶层模块设置为Adder_Array。

如图3修改顶层模块名图3 修改顶层模块名(3)修改synopsys.sdc实现以下设计约束:时钟周期1.2ns,input_delay设置为0.5ns,output_delay设置为0.5ns。

如果使用者想增加其他的设计约束可以在此文件中增添。

(4)进入刚才建好的综合环境,在终端中执行run命令,调用Design Compiler执行逻辑综合。

打开终端:cd [建好的环境路径],进入后输入run,即可。

(5)等逻辑综合执行完毕后,查看123.log,对其中的error和warning进行确认,如果有问题修改设计或综合脚本后重新综合,直至没有问题。

综合工具-DesignCompiler学习教程

综合⼯具-DesignCompiler学习教程Design Compiler 13讲中的部分内容:1、逻辑综合的概述DC⼯作流程分为三步2、DC的三种启动⽅式GUIdc_shellBatch mode3、DC-Tcl语⾔的基本结构1、⾼层次设计的流程图2、DC在设计流程中的位置3、使⽤DC进⾏基本的逻辑综合的流程图与相应的命令①准备设计⽂件②指定库⽂件③读⼊设计④定义设计环境⑤设置设计约束⑥选择编译策略⑦编译⑧分析及解决设计中存在的问题⑨存储设计数据(1)启动环境配置简述(2).synopsys_dc.setup配置⽂件的书写(3).synopsys_dc.setup的讲解(1)标准单元库①概述⼀个ASIC综合库包括如下信息:·⼀系列单元(包括单元的引脚)。

·每个单元的⾯积(在深亚微⽶中,⼀般⽤平⽅微⽶表⽰,在亚微⽶⼯艺下,⼀般⽤门来称呼,⾄于具体的单位,可以咨询半导体制造商)。

·每个输出引脚的逻辑功能。

·每个输⼊到输出的传递延时,输出到输出的传递延时;inout到输出的传递延时。

②内容与结构Synopsys的⼯艺库是⼀个.lib⽂件,经过LC编译后,产⽣.db⽂件。

⼯艺库⽂件主要包括如下信息:·单元(cell)(的信息):(主要有)功能、时间(包括时序器件的约束,如建⽴和保持)、⾯积(⾯积的单位不在⾥⾯定义,可按照规律理解,⼀般询问半导体⼚商)、功耗、测试等。

·连线负载模型(wire load models):电阻、电容、⾯积。

·⼯作环境/条件(Operating conditions):制程(process)(电压和温度的⽐例因数k,表⽰不同的环境之间,各参数缩放的⽐例)·设计规则约束(Design ):最⼤最⼩电容、最⼤最⼩转换时间、最⼤最⼩扇出。

⼯艺库的结构如下所⽰:(2)DC的设计对象在了解了综合库之后,下⾯介绍⼀下DC的设计对象,虽然这个设计对象相对于综合库没有那么重要,但是还是要了解⼀下的。

逻辑综合工具designCompiler使用教程

逻辑综合工具Design Compiler使用教程编者:适用专业:电子科学与技术沈阳理工大学信息学院2010年6月图形界面design vision操作示例逻辑综合主要是将HDL语言描述的电路转换为工艺库器件构成的网表的过程。

综合工具目前比较主流的是synopsys公司Design Compiler,我们在设计实践过程中采用这一工具。

Design compiler有两种工作模式,一种是tcl模式,另一种为图形模式。

在设计中为增强直观性,采用图形界面design vision。

TCL命令行模式可在设计过程中摸索熟悉,并使之成为习惯。

tcl模式在启动工具之前,准备工作有四项:设计的HDL源文件、采用的工艺库文件、设计的约束文件、工具的启动文件。

图形界面模式最少需要前两项,这里不作多说明。

1. 启动工具登陆Linux之后进入的目录即是用户的家目录,在家目录下建立dcLab作为本次实验dc的操作主目录。

在dcLab目录下,建立设计存放目录如source、约束文件目录如constrn、输出网表文件目录ntlst、报告输出目录rpt、log文件目录log、dc启动目录work,等等。

实验室中的工作站存放有umc公司和tsmc公司的0.18um标准单元库的所有文件,存放在目录:/usr/eda/designKit/下面,设计过程中需要查找的话注意路径与示例中的图片上所示路径稍有不同。

Design compiler工具在工作站中已经安装完毕,且用户的环境变量和license 也已设置完成,登录之后直接启动工具即可。

如果打开终端之后无法启动工具,可能就是license没有启动,需要首先采用命令:start_slic启动license,然后design vision才能正常开启与工作。

建立相关的工程目录之后,进入本次实验的工作目录:~/dcLab/work后,采用启动命令:design_vision&,启动工具后相应的界面如下图1所示。

Design Compiler使用笔记_DC中文笔记

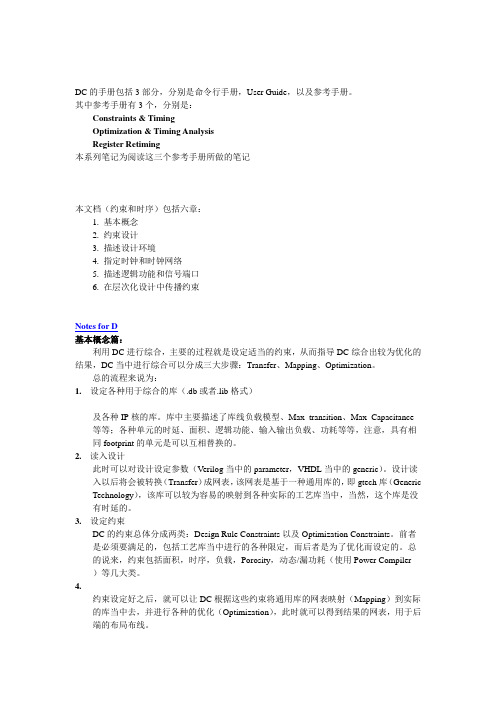

DC的手册包括3部分,分别是命令行手册,User Guide,以及参考手册。

其中参考手册有3个,分别是:Constraints & TimingOptimization & Timing AnalysisRegister Retiming本系列笔记为阅读这三个参考手册所做的笔记本文档(约束和时序)包括六章:1. 基本概念2. 约束设计3. 描述设计环境4. 指定时钟和时钟网络5. 描述逻辑功能和信号端口6. 在层次化设计中传播约束Notes for D基本概念篇:利用DC进行综合,主要的过程就是设定适当的约束,从而指导DC综合出较为优化的结果,DC当中进行综合可以分成三大步骤:Transfer、Mapping、Optimization。

总的流程来说为:1.设定各种用于综合的库(.db或者.lib格式)及各种IP核的库。

库中主要描述了库线负载模型、Max_transition、Max_Capacitance 等等;各种单元的时延、面积、逻辑功能、输入输出负载、功耗等等,注意,具有相同footprint的单元是可以互相替换的。

2.读入设计此时可以对设计设定参数(Verilog当中的parameter,VHDL当中的generic)。

设计读入以后将会被转换(Transfer)成网表,该网表是基于一种通用库的,即gtech库(Generic Technology),该库可以较为容易的映射到各种实际的工艺库当中,当然,这个库是没有时延的。

3.设定约束DC的约束总体分成两类:Design Rule Constraints以及Optimization Constraints。

前者是必须要满足的,包括工艺库当中进行的各种限定,而后者是为了优化而设定的。

总的说来,约束包括面积,时序,负载,Porosity,动态/漏功耗(使用Power Compiler )等几大类。

4.约束设定好之后,就可以让DC根据这些约束将通用库的网表映射(Mapping)到实际的库当中去,并进行各种的优化(Optimization),此时就可以得到结果的网表,用于后端的布局布线。

第二章 Design Compiler简介

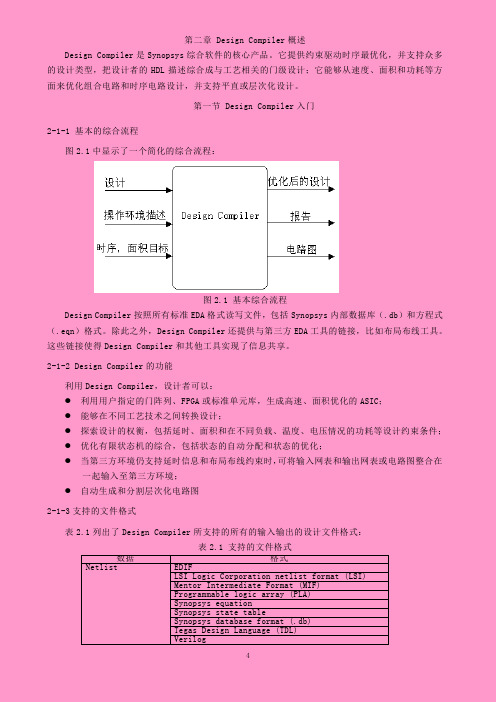

第二章 Design Compiler概述Design Compiler是Synopsys综合软件的核心产品。

它提供约束驱动时序最优化,并支持众多的设计类型,把设计者的HDL描述综合成与工艺相关的门级设计;它能够从速度、面积和功耗等方面来优化组合电路和时序电路设计,并支持平直或层次化设计。

第一节 Design Compiler入门2-1-1 基本的综合流程图2.1中显示了一个简化的综合流程:图2.1 基本综合流程Design Compiler按照所有标准EDA格式读写文件,包括Synopsys内部数据库(.db)和方程式(.eqn)格式。

除此之外,Design Compiler还提供与第三方EDA工具的链接,比如布局布线工具。

这些链接使得Design Compiler和其他工具实现了信息共享。

2-1-2 Design Compiler的功能利用Design Compiler,设计者可以:●利用用户指定的门阵列、FPGA或标准单元库,生成高速、面积优化的ASIC;●能够在不同工艺技术之间转换设计;●探索设计的权衡,包括延时、面积和在不同负载、温度、电压情况的功耗等设计约束条件;●优化有限状态机的综合,包括状态的自动分配和状态的优化;●当第三方环境仍支持延时信息和布局布线约束时,可将输入网表和输出网表或电路图整合在一起输入至第三方环境;●自动生成和分割层次化电路图2-1-3支持的文件格式表2.1列出了Design Compiler所支持的所有的输入输出的设计文件格式:表2.1 支持的文件格式数据格式Netlist EDIFLSI Logic Corporation netlist format (LSI)Mentor Intermediate Format (MIF)Programmable logic array (PLA)Synopsys equationSynopsys state tableSynopsys database format (.db)Tegas Design Language (TDL)VerilogVHDLTiming Standard Delay Format (SDF)Command Script dcsh, TclCell Clustering Physical Design Exchange Format (PDEF)Library Synopsys library source (.lib)Synopsys database format (.db)Parasitics dc_shell command scripts2-1-4 设计类型、输入格式和输出格式设计类型:设计可以是分层的或平直的,时序的或组合的;输入格式:支持VHDL和Verilog作为设计描述的输入格式,也支持开编程逻辑阵列(PLA)和EDIF 200格式;输出格式:除了Synopsys二进制格式(.db),还支持VHDL、Verilog、EDIF 200、方程式、大规模集成(large-scale integration)、Mentor图形、PLA、状态表和Tegas格式。

Design Compiler ,DC,使用方法

课前说明: 在进行下面的演示之前需要大家拷一个文件夹 dc_example , 里面有本 节课需要用到的文件(包括本讲义) 。这个文件夹在 /home/eda236 目录下,大家 把它们拷贝到自己的帐号目录下,以备使用。

拷贝命令:cp –r ../eda236/dc_example

点 OK ,设置完成。 3. 读入 verilog 文件 选择 File---�Read

在打开文件对话框中选中要打开的文件,在这里我们选中 example1.v 文件。

在 Log 框中出现 successfully 字样表明读入文件成功。相应命令:read_file

点击红色箭头所指的按钮可以查看该电路的 symbol 图。

点击 OK ,相应命令:compile

在 Log 框中出现 Optimization Complete 字样表明优化完成,如下图所示。

6. 查看报告 6.1 查看面积报告

选择 Design-----�Report Area

点击 OK ,相应命令:report_area。

报告总面积为 180.223999,单位是平方微米。

4. 设置约束条件 4.1 设置时钟约束 在 symbol 图上选中 clk 端口

选择 Attributes-----�Specify Clock

出来设置时钟约束的对话框,按下图设置,给时钟取名为 clock,周期 20ns,上升沿 0ns , 下降沿 10ns 。

点击 OK ,时钟约束设置完成。相应命令:creat_clock 4.2 设置复位信号约束 在 symblo 图中选中 rst_n 端口(在本例中它是复位端口) ,选择 Attributes-----�Optimization Directives-----�Input Port

Design Compiler Lab Guide自学笔记——快速入门DC

Design Compiler Lab Guide自学笔记——快速入门DCfrom Monchy(蒙奇)在2020年秋招前根据Synopsys的Design Compiler Lab Guide2012自学综合工具Synplify,在此分享第一章章详细的学习笔记,几乎是指南的中文翻译,大量的过程截图对初学者很友好。

虽然只有一章,但是对于掌握DC流程的初学者特别重要,共10个任务,很多的设置一旦出错了就卡那了。

本笔记可以帮你避免走弯路。

Design Compiler Lab Guide2012是Synopsys给出的DC综合官方入门指南,里面包涵源码和实验指导,可以在网上自行下载。

1Setup and Synthesis Flow1学习内容描述本实验中使用的三个DC 设置文件中每个文件的内容。

更新common_setup.tcl 文件完全指定逻辑和物理库以及工艺文件在Design Vision 中探索符号和原理图视图通过地形模式下的基本综合步骤进行设计并生成报告访问SolvNet 以浏览《Design Vision 》用户手册2实验指导任务1检查并修改setup 文件1将1ab1目录作为工作目录并列出以下内容文件:#cd /home/IC/Desktop/DC/lab1#ls -al.synopsys*查看所有前面以”.synopsys”开头的关键字的隐藏文件#ls -al *setup*查看所有只要包含有关键字”setup”的文件.synopsys_dc.setup 文件(.开头为隐藏文件)定义别名,source 另外两个设置文件:common_setup.tcl 和dc_setup.tcl 。

(source 报错,不知道怎么弄)common_setup.tcl 文件包含用户自定义的变量,用于指定工艺文件和目录名。

这些变量在dc_setup.tcl 中使用。

在终端中显示echo 打印的内容dc_setup.tcl文件使用common_setup.tcl中的变量执行命令以加载必要的逻辑和物理工艺数据。

Synopsys综合工具DesignCompiler(DC)

Synopsys综合工具DesignCompiler(DC)Synopsys 综合工具Design Compiler(DC)简介一.约束的基本概念:约束就是对用户的设计中可度量的电路参数(如时序、面积以及电容等)进行声明。

没有约束,工具(本文为DC)就不能有效地优化电路,以满足要求。

当DC对设计进行优化时,使用了两类约束:1)设计规则约束(Design Rule Constraints,DRC):此类约束是工具固有的,由工艺库(technology library)来定义。

此类约束是设计功能正确的必要条件,通过库应用于所有设计上。

当然,你可以将它们定义的更紧。

2)优化约束(Optimization Constraints):它们是由用户定义的,前提是可实现的。

用户在使用DC时,可以通过命令行或编写约束文件(.scr)来定义约束。

下图给出DC 主要的DRC及优化约束,以及相关的DC命令(dc_shell接口命令)。

DRC:最大转换时间(Max Transition Time):对于一条连线(net)来说,是其驱动pin逻辑值转化的最长时间。

最大扇出(Max Fanout):对于驱动pin来讲。

最大/最小电容(Max/Min Capacitance):用来控制连线的电容值。

器件退化(Cell Degradation):某些工艺库包括器件退化表,它列举了某一器件可驱动的最大电容,是该器件输入pin最大转换时间的函数。

优化约束:时序约束:包括输入/输出延迟(Input/Output Delay):同步路径最大/最小延迟(Minimum/Maximum Delay):异步路径最大面积(门数):最小孔隙度(Min porosity):可布线性二.约束报告约束报告提供了设计规则和优化约束的信息。

可采用如下命令产生相应报告:report_constraintreport_portreport_clockreport_attributereport_timing_requirements用户可通过输出相应报告,来分析设计是否满足了约束。

Tcl与DesignCompiler(三)——DC综合的流程

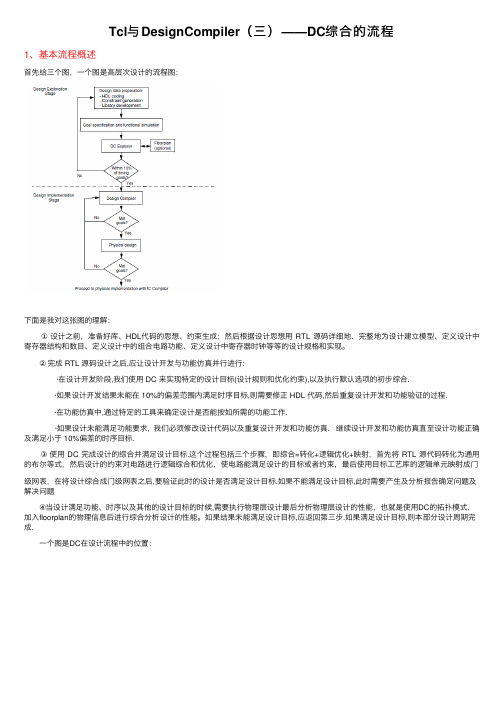

Tcl与DesignCompiler(三)——DC综合的流程1、基本流程概述⾸先给三个图,⼀个图是⾼层次设计的流程图:下⾯是我对这张图的理解: ①设计之前,准备好库、HDL代码的思想、约束⽣成;然后根据设计思想⽤ RTL 源码详细地、完整地为设计建⽴模型、定义设计中寄存器结构和数⽬、定义设计中的组合电路功能、定义设计中寄存器时钟等等的设计规格和实现。

②完成 RTL 源码设计之后,应让设计开发与功能仿真并⾏进⾏: ·在设计开发阶段,我们使⽤ DC 来实现特定的设计⽬标(设计规则和优化约束),以及执⾏默认选项的初步综合. ·如果设计开发结果未能在 10%的偏差范围内满⾜时序⽬标,则需要修正 HDL 代码,然后重复设计开发和功能验证的过程. ·在功能仿真中,通过特定的⼯具来确定设计是否能按如所需的功能⼯作. ·如果设计未能满⾜功能要求, 我们必须修改设计代码以及重复设计开发和功能仿真. 继续设计开发和功能仿真直⾄设计功能正确及满⾜⼩于 10%偏差的时序⽬标. ③使⽤ DC 完成设计的综合并满⾜设计⽬标.这个过程包括三个步骤,即综合=转化+逻辑优化+映射,⾸先将 RTL 源代码转化为通⽤的布尔等式,然后设计的约束对电路进⾏逻辑综合和优化,使电路能满⾜设计的⽬标或者约束,最后使⽤⽬标⼯艺库的逻辑单元映射成门级⽹表,在将设计综合成门级⽹表之后,要验证此时的设计是否满⾜设计⽬标.如果不能满⾜设计⽬标,此时需要产⽣及分析报告确定问题及解决问题 ④当设计满⾜功能、时序以及其他的设计⽬标的时候,需要执⾏物理层设计最后分析物理层设计的性能,也就是使⽤DC的拓扑模式,加⼊floorplan的物理信息后进⾏综合分析设计的性能。

如果结果未能满⾜设计⽬标,应返回第三步.如果满⾜设计⽬标,则本部分设计周期完成. ⼀个图是DC在设计流程中的位置: 这个图将上⾯的流程图细化,着重与DC的部分,描述了使⽤DC进⾏逻辑综合时要做的事,同时,也是对前⾯的流程图解说的图形概述。

Synopsys_Design_Compiler使用

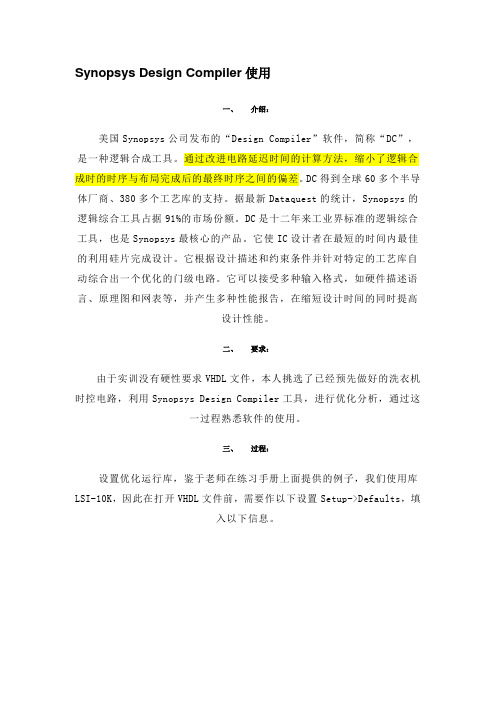

Synopsys Design Compiler使用一、介绍:美国Synopsys公司发布的“Design Compiler”软件,简称“DC”,是一种逻辑合成工具。

通过改进电路延迟时间的计算方法,缩小了逻辑合成时的时序与布局完成后的最终时序之间的偏差。

DC得到全球60多个半导体厂商、380多个工艺库的支持。

据最新Dataquest的统计,Synopsys的逻辑综合工具占据91%的市场份额。

DC是十二年来工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

二、要求:由于实训没有硬性要求VHDL文件,本人挑选了已经预先做好的洗衣机时控电路,利用Synopsys Design Compiler工具,进行优化分析,通过这一过程熟悉软件的使用。

三、过程:设置优化运行库,鉴于老师在练习手册上面提供的例子,我们使用库LSI-10K,因此在打开VHDL文件前,需要作以下设置Setup->Defaults,填入以下信息。

在File->read打开要分析优化的VHDL文件,这里我选择一个洗衣机时控电路NewWasher.vhd 如下所示(分别为不同层次的视图:顶层、器件、门级电路)在Tools->Design Optimization中设置好兼顾平衡的约束条件(左图),确定编译后,产生了右边经过优化的门级电路图。

接下来,把优化过的图形转换为VHDL文件和DB文件输出,另存到指定位置File->Save As如右图,生成了新的DB文件和vhd文件。

接下来,是要设定CLK的周期,根据分析、优化、编译出来的Slack Time 松弛数值和Area面积数值,选取最合适的平衡点。

DC逻辑综合(Design Compiler)

DC综合1.概述1.1. 综合的目的综合是完成从RTL代码到门级电路的转换。

如果在综合时,链接了厂家的库文件,则门级电路使用的器件是厂家库文件中提供的器件。

综合在整个IC设计中,起到的作用如图1所示。

图 1 综合在IC设计中的作用由于目前IC设计规模日益增大,设计难度不断提高,设计人员必须通过综合工具实现综合任务。

目前IC所采用的是综合工具是Synopsys公司的Design Compiler。

本讲义紧密结合了Design Compiler的应用。

1.2. 综合的特性1.2.1. 综合是由约束驱动的对于一个设计来说,在进行综合前,需要给这个设计加上约束,约束也就是综合的目标,综合工具会竭力满足约束,以实现综合的目标。

约束可分为多方面,如时序方面的约束、面积方面的约束、环境属性方面的约束、驱动和负载方面的约束等。

其中最重要的约束是对时钟等与时序相关的属性进行约束。

在综合时,约束的各个方面可能存在一定的矛盾,如对速度和面积的约束,见图2所示。

综合的过程就是找到一个最好的平衡点,满足各个方面的约束。

图 2 约束中速度与面积间的关系好的、合理的约束,是综合成功的关键。

不同的约束会导致不同的综合效果。

1.2.2. 综合是基于path分析的在整个综合的过程中,完成是基于path进行时序分析的,因此path的概念非常重要。

何谓path?如下图所示。

图 3 Timing Path的概念Path是综合工具进行时序分析的基本单位。

对于一条path而言,它的起点只能是输入端口,或者触发器/寄存器的时钟端;终点只能是输出端口,或者触发器/寄存器的数据输入端(对D触发器而言,就是D端)。

结合图3而言,其中共有4条path,分别为:1)输入端口A -> FF2的D端;2)FF2的CK端-> FF3的D端;3)FF3的CK端-> 输出端口Z;4)输入端口A -> 输出端口Z。

同一个时钟域多条path,组成一个组,称为path group。

DC综合过程,Design Compiler

Design Compiler 使用简要说明Design Compiler可以针对层次化的组合电路或者时序电路的速度、面积和可布性进行优化。

按照所定义的电路的测量特征所要达到的目标,Design Compiler综合一个电路并将其放入目标库中,这样可以生成适用于你的计算机辅助设计工程(CAE)工具的原理图或网表。

综合的过程如下图:•读入设计及其子设计。

•设置顶层的设计特性参数•设置实际时序和面积目标参数•执行check_design验证设计,识别并且更正错误•进行Design Compiler优化在db、verilog、vhdl文件夹下设计内容都是一样的,只是形式不一样。

Db文件夹:ALARM_BLOCK.db ALARM_COUNTER.db ALARM_SM.dbALARM_STATE_MACHINE.db COMPARATOR.dbHOURS_FILTER.db MUX.db TIME_BLOCK.dbTIME_COUNTER.dbTIME_STATE_MACHINE.db CONVERTOR.pla CONVERTOR_CKT.db TOP.dbVerilog文件夹:ALARM_BLOCK.v ALARM_COUNTER.v ALARM_SM.vALARM_STATE_MACHINE.v COMPARATOR.vHOURS_FILTER.v MUX.vTIME_BLOCK.vTIME_COUNTER.vTIME_STATE_MACHINE.v CONVERTOR.pla CONVERTOR_CKT.v TOP.vVhdl文件夹:ALARM_BLOCK.vhd ALARM_BLOCK.vhd ALARM_SM.vhdALARM_STATE_MACHINE.vhd COMPARATOR.vhdHOURS_FILTER.vhd MUX.vhd TIME_BLOCK.vhdTIME_COUNTER.vhdTIME_STATE_MACHINE.vhd CONVERTOR.pla CONVERTOR_CKT.vhd TOP.vhd设置path参数将 Synopsys_installroot/arch/syn/bin加到.cshrc文件中。

DC使用全书(Design_Compiler)

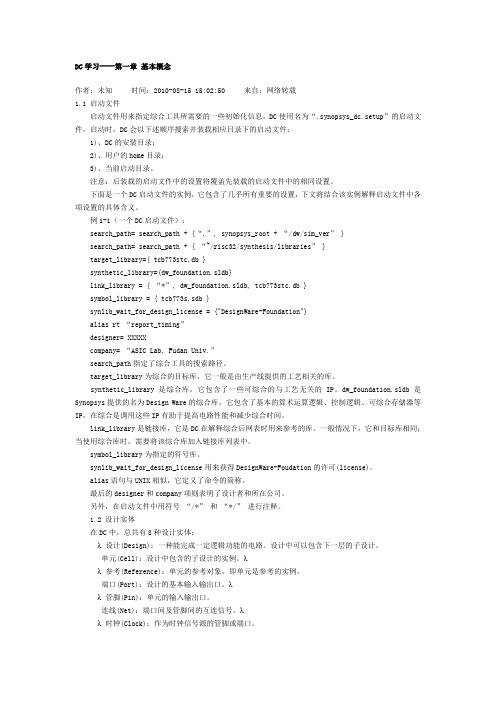

DC学习----第一章基本概念作者:未知时间:2010-08-15 15:02:50 来自:网络转载1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

下面是一个DC启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各项设置的具体含义。

例1-1(一个DC启动文件):search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db }symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXcompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

DC Design Compiler 综合脚本命令及参考模板

DC Design Compiler 综合脚本命令及参考模板Design Compiler 综合脚本常用命令和模板参照自己的设计,以及自己的工艺信息,适当修改下面的Constraints 和 Run Script 等的脚本,添加一些相关的约束语句,就可以运行了详细的命令请参照DC的官方User Guide等相关资料。

Invoking Design CompilerUnix% design_vision # Interactive GUI, WLM mode Unix%design_vision –topographical # Interactive GUI, Topographical mode Unix% dc_shell-t # Interactive shell, WLM mode Unix% dc_shell-t –topographical # Interactive shell, Topographical mode Unix% dc_shell-t –f RUN.tcl | tee –i my.log # Batch mode.synopsys_dc.setupset search_path “$search_path libs cons unmapped rtl”set synthetic_library dw_foundation.sldbset target_library 65nm.dbset link_library “* $target_library $synthetic_library IP.db”set symbol_library 65nm.sdbdefine_design_lib WORK –path ./workset_svf <my_filename.svf>set_vsdc <my_filename.vsdc>history keep 200set sh_enable_page_mode falseset cache_write .set cache_read $cache_writesuppress_message {LINT-28 LINT-32 LINT-33 UID-401} setalib_library_analysis_path [get_unix_variable HOME] alias h history alias rc “report_constraint -all_violators”TCL Commands and Constructsset PER 2.0 # Define a variable and its value echo $PER # Variable substitution , 2.0set MARG 0.95expr $PER * $MARG # expr: *, /, +, -, >, <, =, <=, >=set pci_ports [get_ports A] # Imbedded command set pci_ports[get_ports “Y??M Z*”] # Wildcardsecho “Effctv P = \ # Soft quotes , 1.9[expr $PERIOD * $MARGIN]”echo {Effctv P = \ # Hard quotes[expr $PERIOD * $MARGIN]} # , Effctv P = [expr $PER * $MARG] # Comment lineset COMMENT in_line; # In-line comment set MY_DESIGNS {B1.v ...B26.v} # foreach loop foreach DESIGN $MY_DESIGNS {read_verilog $DESIGN}for {set i 1} {$i < 27} {incr i} { # for loopread_verilog BLOCK_$i.v}Helpful UNIX-like DC-shell commandspwdcdlshistory!!!7!reportsh <UNIX_command>printenvget_unix_variable ARCHConstraintsreset_designset_max_area 0create_clock -period 2 –name Main_Clk [get_ports Clk1]create_clock –period 2.5 –waveform {2 3.5} [get_ports Clk2]create_clock –period 3.5 –name V_Clk; # VIRTUAL clockset_clock_uncertainty –setup 0.14 [get_clocks *]set_clock_uncertainty –setup 0.21 –from [get_clocks Main_Clk] –to [get_clocks Clk2] set_clock_latency –max 0.6 [get_clocks Main_Clk] set_clock_latency –source –max 0.3 [get_clocks Main_Clk]set_clock_transition 0.08 [get_clocks Main_Clk] set_input_delay -max 0.6-clock Main_Clk [all_inputs] set_input_delay –max 0.3 –clock Clk2 –clock_fall –add_delay [get_ports “B E”]set_input_delay -max 0.5 -clock –network_latency_included V_Clk [get_ports “A C F”]set_output_delay -max 0.8 -clock –source_latency_included Main_Clk [all_outputs]set_output_delay -max 1.1 -clock V_Clk [get_ports “OUT2 OUT7]set_max_capacitance 1.2 [all_inputs]set_load 0.080 [all_outputs]set_load [expr [load_of slow_proc/NAND2_3/A] * 4] [get_ports OUT3] set_load 0.12 [all_inputs]set_input_transition 0.12 [remove_from_collection[all_inputs][get_ports B]]set_driving_cell –lib_cell FD1 –pin Q [get_ports B]set_operating_conditions –max WCCOMset auto_wire_load_selection falseset_wire_load_model –name 1.6MGatesset_wire_load_mode enclosedset_wire_load_model –name 200KGates [get_designs “SUB1 SUB2”] set_wire_load_model –name 3.2MGates [get_ports IN_A]set_port_fanout_number 8 [get_ports IN_A] set_false_path -from[get_clocks Asynch_CLKA] -to [get_clocks Asynch_CLKB]set_multicycle_path –setup 4 –from –from A_reg -throughU_Mult/Out –to B_regset_multicycle_path –hold 3 –from –from A_reg -throughU_Mult/Out –to B_regset_isolate_ports –type inverter [all_outputs]set_ideal_network [get_ports reset* select*] set_ideal_network[get_pins FF_SET_reg/Q] set_ideal_network –no_propagate [get_nets CTRL] set_ideal_latency 1.4 [get_ports reset* select*]set_ideal_transition 0.5 [get_pins FF_SET_reg/Q] set_scan_configuration -style <multiplexed_flip_flop | clocked_scan | lssd | aux_clock_lssd> Checking and Removing Constraints and Directivesreport_clock; report_clock -skewreport_designreport_port –verbosereport_wire_loadreport_path_groupsreport_timing_requirements (–ignored) report_auto_ungroupreport_isolate_ports write_script –output <constraints.tcl>check_timingreset_path –from FF1_regremove_clockremove_clock_transition remove_clock_uncertainty remove_input_delay remove_output_delay remove_driving_cell remove_wire_load_modelSyntax CheckingUnix% dcprocheck constr_file.conPhysical Constraints – Topographical Modeset_aspect_ratioset_utilizationset_placement_areaset_rectilinear_outline set_port_sideset_port_locationset_cell_locationcreate_placement_keepoutMisc. Reports# Generate A library report fileread_db library_file.dblist_libsredirect –file reports/lib.rpt {report_lib <libname>}report_hierarchy [-noleaf]# Arithmetic implementation and# resource-sharing info report_resources# List area for all cells in the design report_cell [get_cells –hier *]Run Scriptread_verilog {A.v B.v TOP.v} orread_vhdl {A.vhd B.vhd TOP.vhd} orread_ddc MY_TOP.ddc oracs_read_hdl MY_TOP oranalyze –format verilog {A.v B.v TOP.v}elaborate MY_TOP –parameters “A_WIDTH=8, B_WIDTH=16”current_design MY_TOPlinkif {[check_design] ==0} {echo “Check Design Error”exit # Exits DC if a check-design error is encountered } # Continue if NO problems encounteredwrite –f ddc –hier –out unmappedd/TOP.ddcredirect –tee –file reports/precompile.rpt {source –echo -verbose TOP.con} redirect –append –tee –file reports/precompile.rpt{check_timing} source <Physical_Constraints_TCL_file> or # Source tcl constraints, if available, orextract_physical_constraints <DEF_file> # Extract and apply from an existing# DEF floorplan filegroup_path -name CLK1 -critical_range <10% of CLK1 Period> –weight 5group_path -name CLK2 -critical_range <10% of CLK2 Period> –weight 2group_path –name INPUTS –from [all_inputs]group_path –name OUTPUTS –to [all_outputs]group_path –name COMBO –from [all_inputs] –to [all_outputs]set_fix_multiple_port_nets –all –buffer_constants********************************************************* * ** Insert Expert, Ultra or ACS compile flow here * * **********************************************************check_designreport_constraint –all_violatorsreport_timing –delay –to –from –through –input_pins –max_paths \–nworst –nets –cap –sig –groupreport_areareport_qorset verilogout_no_tri truechange_names –rule verilog –hierwrite –f verilog –hier –out mapped/TOP.vwrite –f ddc –hier –out mapped/TOP.ddcwrite_sdc TOP.sdcwrite_scan_def –out TOP_scan.defwrite_physical_constraints –output TOP_PhysConstr.tcl exitObject Retrieval and Manipulation (Collection Commands)get_ports, get_pins, get_designsget_cells, get_nets, get_clocksget_nets –of_objects [get_pins FF1_reg/Q] get_libs <lib_name>get_lib_cells <lib_name/cell_names> get_lib_pins<lib_name/cell_name/pin_names> all_inputs, all_outputs, all_clocks,all_registers all_connectedall_fanin, all_fanoutall_ideal_netsset pci_ports [get_ports pci_*]echo $pci_ports # , _sel184query_objects $pci_ports # , {pci_1 pci_2 ...} get_object_name $pci_ports # , pci_1 pci_2 ...sizeof_collection $pci_ports # , 37set pci_ports [add_to_collection $pci_ports \[get_ports CTRL*]]set all_inputs_except_clk [remove_from_collection \[all_inputs] [get_ports CLK]]compare_collectionsindex_collectionsort_collectionforeach_in_collection my_cells [get_cells -hier * \-filter “is_hierarchical == true”] {echo “Instance [get_object_name $cell] is hierarchical”}# Filtering operators: ==, !=, >, <, >=, <=, =~, !~filter_collection [get_cells *] “ref_name =~ AN*”get_cells * -filter “dont_touch == true”get_clocks * -filter “period < 10”# List all cell attributes and redirect output to a fileredirect –file cell_attr \{list_attributes –application –class cell}# Grep the file for cell attributes starting with dont_UNIX% grep dont_ cell_attr | more# List the value of the attribute dont_touchget_attribute <cell_name> dont_touchUltra Compile Flow - Topographical or WLM ModeUltra + DesignWare and DFTC licenses available# In “topo” mode (dc_shell-t –topo) specify Milkyway reference and design libraries create_mw_lib –tech <technology_file> -mw_reference_library <mw_reference_libraries> \<mw_design_library_name>open_mw_lib <mw_design_library_name>set_tlu_plus_files -max_tluplus <max_tluplus_file> -tech2itf_map <mapping_file> set compile_auto_ungroup_delay_num_cells 99999999 set compile_auto_ungroup_count_leaf_cells trueset compile_auto_ungroup_override_wlm trueset_ungroup <top_level_and/or_pipelined_blocks> false# OPTIONAL: Disable unconditional auto-ungrouping# of DesignWare hierarchy (not usually recommended) setcompile_ultra_ungroup_dw false# If design contains pipelined sub-designs and the pipeline registers# are grouped together at the input or output, relax timingset_multicycle_path –setup <#_stages> -from U_Pipeline/R3_reg* –to U_Pipeline/R7_reg*# In “ topo” mode, if the floorplan is available, apply or extract the physical constraintssource <physical_constraints_file> ORextract_physical_constraints <DEF_file># OPTIONAL: Exclude specific cells/design from adaptive retiming (-retime) set_dont_retime <cells_or_designs> true# First compilecompile_ultra –scan –retime –timing|-area# The design hierarchy may have changed due to auto-ungrouping/-uniquifying reset_path -from U_Pipeline/R3_reg* -to U_Pipeline/R7_reg* # OPTIONAL: Maintain registered pipeline outputs if requiredset_dont_touch [get_cells U_Pipeline/R12_reg*] true# Optimize registers if pipeline violates timing; Skip if nopipeline issues: set_optimize_registers true –designMy_Pipeline_Subdesignoptimize_registers –only_attributed_designs# Continue if design is NOT meeting all constraints:# Apply more focus on violating critical paths, as necessarygroup_path –name <group_name> -from <path_start> -to <path_end> \ –critical range <10% of max delay goal> -weight 5# Select appropriate second compile# In “topo” mode in DC v2006.06, or any mode in DC v2007.03 or latercompile_ultra –scan –incremental# In “WLM” mode in DC v2006.06set_ultra_optimization truecompile –boundary –scan –map_effort high –incremental (-area_effort medium|low|none)# In “topo” mode prior to DC v2007.03: Write out updated physical constraintswrite_physical_constraints –output PhysConstr.tclDFT Flow – Expert or UltraDFTC license available# Prior to the first compile set the# scan cell styleset_scan_configuration –style ..# Perform the first test-ready compilecompile –boundary –map high –scan # ORcompile_ultra –timing -scan# Continue before the next compile:# Read in the scan specification filesource scan_spec.tcl# Check for DFT rule violationsdft_drc# Preview the scan chainspreview_dft# Insert and optimize scaninsert_dft****************************************************** * ** Execute additional Ultra/Expert optimization * * techniques, as needed * * *******************************************************# After the final compile check the DFT QoR# and write out the scan DEF filedft_drc –coverage_estimatewrite_scan_def -out <my_design.def>Some Scan Specification Commandsset_scan_state test_readyset_dft_configuration ...set_dft_signal ...set_scan_path ...set_scan_configuration ...create_test_protocolExpert Compile FlowNo Ultra license available; DFTC license available compile –boundary –scan –map_effort high# Continue if NOT meeting constraints# Note: -scan requires DFTC licensecompile –boundary –scan –map_effort high –incremental \(-area_effort medium|low|none)# Continue if NOT meeting constraints:# Increase max-delay priority if OK to postpone DRC fixingset_cost_priority –delay# Note: The design hierarchy may have changed due to auto-# uniquifying# Apply more focus on violating critical paths, as necessarygroup_path –name <group_name> -from <path_start> \-to <path_end> –critical range <10% of max delay goal> -weight 5 # Repartition if design is poorly partitioned group –design<NEW_DESIGN> -cell_name <U_NEW_CELL> \{U2 U7 ...}ungroup –start_level 2 U_NEW_CELLcompile –boundary –scan –map_effort high –incremental \(-area_effort medium|low|none)# Or, can ungroup all hierarchy in lieu of group/ungroup# commands with –ungroup_allcompile –boundary –scan –map_effort high –incremental \(-area_effort medium|low|none) –ungroup_all“Pseudo Ultra” Compile FlowUltra license available; No DesignWare license available set compile_auto_ungroup_delay_num_cells 99999999 setcompile_auto_ungroup_area_num_cells 99999999 setcompile_auto_ungroup_count_leaf_cells trueset compile_auto_ungroup_override_wlm trueset_ungroup <top_level_and/or_pipelined_blocks> false# OPTIONAL: Disable unconditional auto-ungrouping# of DesignWare hierarchy (not usually recommended) set compile_ultra_ungroup_dw false# If design contains pipelined sub-designs and the pipeline registers# are grouped together at the input or output, relax timing set_multicycle_path –setup <#_stages> \-from U_Pipeline/R3_reg* –to U_Pipeline/R7_reg*# Enable Ultra optimizations available for compileset_ultra_optimization –no_auto_dwlib trueset hlo_disable_datapath_optimization trueset compile_slack_driven_buffering truecompile –boundary –scan –map_effort high –auto_ungroup delay|area \ (-area_effort medium|low|none)# Note: The design hierarchy may have changed due to auto- # ungrouping and auto-uniquifyingreset_path -from U_Pipeline/R3_reg* -to U_Pipeline/R7_reg* # OPTIONAL: Maintain registered pipeline outputs if required set_dont_touch [get_cells U_Pipeline/R12_reg*] true # Optimize registers if pipeline violates timing; Skip if no pipeline issues:set_optimize_registers true –design My_Pipeline_Subdesign optimize_registers –only_attributed_designs# Continue if design is NOT meeting all constraints: compile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Continue if NOT meeting all constraints:set_cost_priority –delay# Ungroup DesignWare components amid combinational logic ungroup <DesignWare_components># Apply more focus on violating critical paths, as necessary group_path –name <group_name> -from <path_start> -to <path_end> \ –critical range <10% of max delay goal> -weight 5 compile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DC学习----第一章基本概念作者:未知时间:2010-08-15 15:02:50 来自:网络转载1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

下面是一个DC启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各项设置的具体含义。

例1-1(一个DC启动文件):search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db } symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXcompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware 的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

link_library是链接库,它是DC在解释综合后网表时用来参考的库。

一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

symbol_library为指定的符号库。

synlib_wait_for_design_license用来获得DesignWare-Foudation的许可(license)。

alias语句与UNIX相似,它定义了命令的简称。

最后的designer和company项则表明了设计者和所在公司。

另外,在启动文件中用符号“/*” 和“*/” 进行注释。

1.2 设计实体在DC中,总共有8种设计实体:λ设计(Design):一种能完成一定逻辑功能的电路。

设计中可以包含下一层的子设计。

单元(Cell):设计中包含的子设计的实例。

λλ参考(Reference):单元的参考对象,即单元是参考的实例。

端口(Port):设计的基本输入输出口。

λλ管脚(Pin):单元的输入输出口。

连线(Net):端口间及管脚间的互连信号。

λλ时钟(Clock):作为时钟信号源的管脚或端口。

库(Library):直接与工艺相关的一组单元的集合。

λ1.3 寻找设计实体在DC中使用find命令寻找设计实体,其语法为:find<实体类型><名称列表>-hierarchyλ <实体类型>:上节所述的8种类型λ <名称列表>:用来匹配的关键词,其中可带“*” 统配符λ -hierarchy:指令DC搜索所有设计层次例1-2(find命令的使用):find (cell, *U*)find (net, “*”)find (design, {A_*, B_*} -hierarchy)另外,使用all_inputs()和all_outputs()可以得到设计所有的输入端口和输出端口。

1.4 编译器指示语句有时,可以利用HDL描述中的一些特定的注释语句来控制综合工具的工作,从而弥补仿真环境和综合环境之间的差异,这些注释语句称为编译器指示语句(Compiler Directives)。

1.4.1 Verilog编译器指示语句1) translate_off/ translate_on这组语句用来指示DC停止翻译“//synopsys translate_off”之后的Verilog描述,直至出现“//synopsys translate_on”。

当Verilog代码钟含有供仿真用的不可综合语句时,这项功能能使代码方便地在仿真工具与综合工具之间移植。

例1-3(translate_off/ translate_on指示语句的使用)://synopsys translate_off/*仅供仿真用语句……*///synopsys translate_on/*可综合语句……*/2) parallel_case/ full_caseDC可能使用带优先级的结构来综合Verilog的case语句,为避免这种情况,可以使用“//synopsys parallel_case”指示DC将case 语句综合为并行的多路选择器结构。

例 1-4(parallel_case指示语句的使用):always @ (state)begincase (state) //synopsys parallel_case2’b00: new_state = 2’b01;2’b01: new_state = 2’b10;2’b10: new_state = 2’b00;default: new_state = 2’b00;endcaseend另外,Verilog允许case语句不覆盖所有可能情况,当这样的代码由DC综合时将产生锁存器。

为避免这种情况,可以使用“//synopsys full_case”指示DC所有可能已完全覆盖。

例 1-5(full_case指示语句的使用):always @ (sel or a1 or a2)begincase (sel) //synopsys full_case2’b00: z = a1;2’b01: z = a2;2’b10: z = a1 & a2;endcaseend1.4.2 VHDL编译器指示语句1) translate_off/ translate_on作用同Verilog,注意需要使用符合VHDL语法的注释:--synopsys translate_off--synopsys translate_on也可以使用:--pragma translate_off--pragma translate_on需要注意的是,在VHDL中使用了以上编译指示语句后,DC仍会对translate_off/on之间的描述进行语法检查,若想避免这一点,可以改变以下变量的值:hdlin_translate_off_skip_text = true2) synthesis_off/ synthesis_on其作用和语法均类似于translate_off和translate_on,只是它的作用不受上述变量控制。

DC学习---第二章设计入口作者:未知时间:2010-08-15 15:04:19 来自:网络转载2.1 软件的启动在UNIX下执行dc_shell即可启动DC的命令行界面,执行design_analyzer& 即可启动相应的图形界面。

启动以后的图形界面如图2-1所示。

在图形界面中若需要执行命令行,可以用Setup->Command Window菜单打开命令行功能,如图2-2所示。

在软件启动时,启动文件中所定义的变量均已加载,若希望改变其他变量的值,可以在Setup->Variable中进行,如图2-3所示。

2.2 设计的读入设计的读入有两种方法:analyze + elaborate和read。

2.2.1 analyze + elaborateanalyze命令用以分析、翻译RTL代码,并将中间结果存入指定的库中。

其语法为:analyze-library <库名称>-format <文件类型><文件名列表>-libraryλ <库名称>:指定中间结果所存放的库,即UNIX下的一个目录,缺省为当前目录(WORK)-formatλ <文件类型>:RTL源文件的类型,即Verilog或vhdl λ <文件名列表>:所有需要分析的源文件名,若有多个文件,则用“{}”括起例 2-1 (将直接数字频率合成器的所有设计源文件读入lib1库中):hdlin_enable_presto = false /*禁止Presto编译器功能*/define_design_lib lib1 -path “./lib1” /*将目录 ./lib1 映射为一个设计库*/analyze –library lib1 –format verilog {croma.v, cromb.v, ddfs.v, froma.v, fromb.v}在图形界面中,选择File -> Analyze,在弹出的Analyze File 对话框的File域中填入源文件名,并在Library域中填入“lib1”,选中“Create New Library if it Doesn’t Exist” 复选框,点OK即可(如图2-4所示)。

Elaborate命令用于为设计建立一个结构级的与工艺无关的描述,为下一步的工艺映射做好准备。

命令的一般格式为:elaborate<设计名>-library <库名称>-architecture <构造体名>-parameters <参数列表>-updateλ <设计名>:需要描述的设计-libraryλ <库名称>:设计的分析结果所在的库-architectureλ <构造体名>:需要分析的构造体,针对VHDL描述中同一个实体对应多个构造体的情况;对于Verilog描述,改选项可缺省或为verilogλ-parameters <参数列表>:在这里给设计中的参数重新赋值,若省略则参数使用缺省值λ -update:要求综合器自动更新所有过期的文件例 2-2 (将先前读入的设计产生结构级描述,并设置相应的参数值):elaborate ddfs –library lib1 –architecture “verilog” –parameters “PAL_sub = 32'h20098ACB,\ NTSC_sub = 32'h06F07BD6” –update由于重置了参数值,顶层的设计名称变为“ddfs_20098acb_06f07bd6”,为方便起见,将顶层设计名改为“ddfs”:rename_design ddfs_20098acb_06f07bd6 ddfs在图形界面中,选择 File -> Elaborate 菜单,在弹出的“Elaborate Design” 对话框的Library域中选择lib1,在Design 域中选择ddfs,填入相应的参数值并选择“Re-Analyze Out-of-Date Libraries” 复选框后点OK(如图2-5所示)。