英飞凌tricore用户手册 第12章 灵活CRC引擎 FCE

英飞凌MCU新手入门应用笔记中文版

新手导1. 82.163.32声明:英飞凌社区应用笔记部分资料内容来源英飞凌社区请来信告知。

本人尊重原创作者。

2012/6新手导航中文版位单片机介绍位单片机介绍位单片机介绍凌社区热心网友奉献资料整理和网络,应用笔记心得整理,内容仅供参考。

如果侵犯Infineon (MCU 新手门篇)英飞凌社区新导航笔记 Ken2012/6/3 果侵犯你的版权,新手入社区新手关于英飞凌总部位于德国纽必堡的英飞凌科技股份公司,为现代社会的三大科技挑战领域——高能效、移动性和安全性提供半导体和系统解决方案。

2010财年(截止到9月30日),公司实现销售额40亿欧元,在全球拥有约26,000名雇员。

英飞凌科技公司的业务遍及全球,在美国苗必达、亚太地区的新加坡和日本东京等地拥有分支机构。

英飞凌公司目前在法兰克福股票交易所(股票代码:IFX)和美国柜台交易市场(OTCQX)International Premier(股票代号:IFNNY)挂牌上市英飞凌在中国英飞凌科技股份公司于1995年正式进入中国市场。

自1996年在无锡建立第一家企业以来,英飞凌的业务取得非常迅速的增长,在中国拥有1300多名员工,已经成为英飞凌亚太乃至全球业务发展的重要推动力。

英飞凌在中国建立了涵盖研发、生产、销售、市场、技术支持等在内的完整的产业链,并在销售、技术研发、人才培养等方面与国内领先的企业、高等院校开展了深入的合作。

☺☞Infineon XC800系列8位元MCU(8位单片机)超级耐高温150℃工业级 8位MCU XC800专为汽车应用设计XC800 150℃系列是汽车产品的理想之选,例如涡轮增压器、发动机风扇、节流阀或阀控制装置、EPS、燃料/燃油传感器以及水/机油/燃油泵等。

潜在的工业应用包括加热控制装置、锅炉系统或电机内部的电子控制系统等。

AEC-Q100是由汽车电子设备委员会(AEC)制定的可靠性压力测试标准。

测试表明,英飞凌全新推出的系列高温微控制器,经过符合AEC-Q100 Grade 0 (-40℃至150℃)标准要求的测试和认证。

英飞凌tricore用户手册 第16章 片上调试支持 OCDS

片上调试支持(OCDS)16片上调试支持本章概述了有关TC1728的调试功能。

这一章不详细介绍TC1728的调试功能和方法。

有关片上调试支持(OCDS)功能(如需工具供应商提供)的详细信息请联系当地的英飞凌代表。

16.1概览TC1728支持OCDS级别1和OCDS级别3。

∙OCDS级别1OCDS级别1主要用于系统软件调试的目的,其需要低成本标准调试硬件。

OCDS级别1基于一种调试接口,其用于通过外部的调试硬件与系统进行通信。

片上Cerberus模块控制调试接口与芯片模块之间相互作用,并特别允许访问设备的整个地址空间。

内存映射的片上调试资源使其可能由指令和数据地址触发以及控制用户程序执行(运行/停止、断点,单步执行)。

∙OCDS级别3OCDS级别3基于使用仿真设备的多核调试解决方案(MCDS)。

此设备具有达到高端仿真的目的所需的以下功能:∙仿真设备在具有和TC1728相同封装的产品系列里可用∙跟踪和重叠RAM引起的高电流消耗是唯一的差别∙Tricore程序跟踪∙Tricore数据跟踪(无寄存器文件跟踪)∙PCP所有权追踪∙PCP程序跟踪∙PCP数据写入PRAM跟踪(无寄存器文件跟踪)∙内部外设总线(SPB)的完全可视性∙本地存储器总线(LMB)的完全可视性∙所有资源的时间对齐平行追踪∙基于普通事件产生逻辑的断点和观察点∙工作在指令指针和存储器地址的比较器:A<=IP<=B∙工作在数据总线上的屏蔽比较器:DATA=“xxxx55xx”∙顺序事件逻辑:由事件驱动并带有界限比较器的计数器被用作断点和追踪质量的事件源∙缓冲追踪数据的优化压缩∙从仿真内存读取代码和数据片上调试支持(OCDS)∙高精度复杂的资格-和触发机制∙事件前和事件后追踪缓冲(“数字示波器”)∙行为计数器∙可进行高达主机接口带宽的持续追踪记录和追踪数据采集∙中间时间戳单元关联从不同的内核或来源的追踪∙同时或有选择性的启动和停止所有内核的中央机制∙追踪内存已满时停止系统仿真设备包括使用额外的仿真硬件扩展的产品芯片部分。

英飞凌单片机选型

程序 [PS RAM] 数据 Mem [DS RAM]

双端口[DPRAM]

Trace Mem for MCDS SB RAM CAN Standby 通道数

2

2

4

2

2

2

2

2

8 最多6

8 最多6

8 最多6

1 最多5

8 最多6 最多2 -

ADC

通道数

24

最多10 0 1 4 最多2 QFP 100 / 144

PMI 48 kB SPRAM 16 kB ICACHE

FPU TriCore (TC-1M) CPS PBCU

Program Local Memory Bus PLMB Data Local Memory Bus DLMB

24kB

Vector Computer

16kB NEW 8kB NEW

XC836

Vector Computer

XC866

PWM unit

XC866

PWM unit

4kB

2kB

XC822

MDU

XC836

Vector Computer

XC866

PWM unit

XC822

MDU

TSSOP16 TSSOP28 TSSOP38 VQFN48

•与8051内核兼容 •于1978年推出的全球第一款 用于动力总成系统的单片机 •高性能的8位单片机,其每条指令周期为两个 机器周期

•在动力总成系统中广泛使用的内 •曾占有50% 的欧洲汽车市场及 30% 的全球市场份额 •每年2500万片的产量

04.05.2012

XC800 家族成员

NEW 64kB

24 / 30/40

英飞凌tricore用户手册 第 章 通用定时器GPT

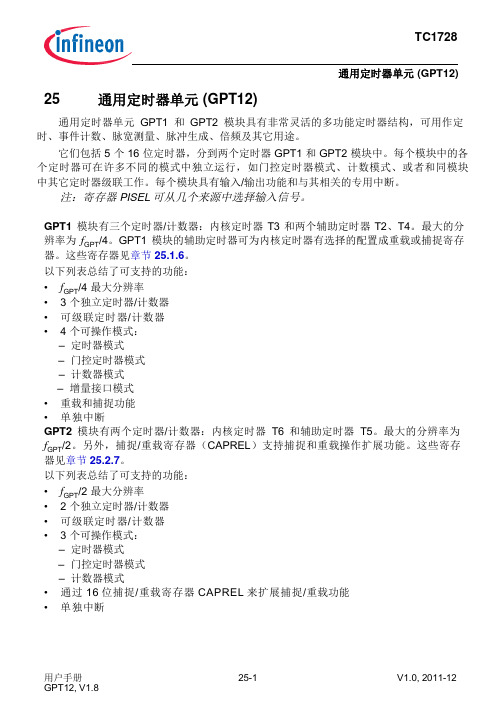

25通用定时器单元(GPT12)通用定时器单元GPT1和GPT2模块具有非常灵活的多功能定时器结构,可用作定时、事件计数、脉宽测量、脉冲生成、倍频及其它用途。

它们包括5个16位定时器,分到两个定时器GPT1和GPT2模块中。

每个模块中的各个定时器可在许多不同的模式中独立运行,如门控定时器模式、计数模式、或者和同模块中其它定时器级联工作。

每个模块具有输入/输出功能和与其相关的专用中断。

注:寄存器PISEL可从几个来源中选择输入信号。

GPT1模块有三个定时器/计数器:内核定时器T3和两个辅助定时器T2、T4。

最大的分辨率为f GPT/4。

GPT1模块的辅助定时器可为内核定时器有选择的配置成重载或捕捉寄存器。

这些寄存器见章节25.1.6。

以下列表总结了可支持的功能:•f GPT/4最大分辨率•3个独立定时器/计数器•可级联定时器/计数器•4个可操作模式:–定时器模式–门控定时器模式–计数器模式–增量接口模式•重载和捕捉功能•单独中断GPT2模块有两个定时器/计数器:内核定时器T6和辅助定时器T5。

最大的分辨率为f/2。

另外,捕捉/重载寄存器(CAPREL)支持捕捉和重载操作扩展功能。

这些寄存GPT器见章节25.2.7。

以下列表总结了可支持的功能:•f GPT/2最大分辨率•2个独立定时器/计数器•可级联定时器/计数器•3个可操作模式:–定时器模式–门控定时器模式–计数器模式•通过16位捕捉/重载寄存器CAPREL来扩展捕捉/重载功能•单独中断25.1定时器GPT1模块GPT1(T2,T3,T4)模块的三个定时器均可运行于4个基本模式中:定时器模式、门控定时器模式、计数器模式或者增量接口模式。

所有定时器可以递增或递减计数。

GPT1的每个定时器通过一个单独的控制寄存器TxCON来控制。

每个定时器都有一个相关的输入引脚TxIN(具有引脚功能),在门控定时器模式中提供门控服务,或者在计数器模式中作为计数输入。

英飞凌tricore用户手册 第15章 总线管理单元

总线监控单元(BMU)15总线监控单元(BMU)本文档描述了总线监控单元(BMU)的功能。

BMU主要用于高集成度安全应用。

它提供了基本的硬件机制以简化安全应用需要实现的监控功能。

BMU的核心功能包括记录外设总线的写操作。

所记录的信息存储在一个本地缓冲区,该缓冲区作为一个循环缓冲区被管理。

在非安全应用里,BMU可以用来作为PCP数据存储器扩展。

BMU作为一个标准的FPI总线从外设运行,并且完全可以通过一组配置寄存器和控制寄存器控制。

此外,一个专用的从机接口允许对记录的信息的突发访问。

本章由如下内容组成:∙BMU特性(见15.2节)∙BMU模块的操作概述(见15.3节)∙BMU模块的功能描述(见15.4节)∙BMU模块的接口(见15.5节)∙BMU模块的寄存器描述(见15.6节)总线监控单元(BMU)15.1相关文档输入文档∙[D1]PRO-SIL Safety Concept for Microcontrollers相关标准和规范∙[S1]IEC61508standard.Functional safety of electrical/electronic/programmable electronic safety-related systems Parts2,7.∙[S2]ISO26262standard.Road vehicles-Functional safety-Part5:Product development:hardware level总线监控单元(BMU)15.2BMU特性BMU具有如下特性:∙运行于外设总线时钟频率的完全同步模块∙实现一个连接到Tricore和PCP中断总线的标准中断服务节点—每个内部中断请求可被特定的状态标志位标识,并只能通过软件清零。

带有有效状态标志位的新中断事件不引发新中断。

∙记录对软件可选外设地址空间的写操作—使用片上系统地址解码器来选择确定目标外设(不是内部地址空间解码器)的线路实现一个总线事务FIFO(BTF),它可以由FPI从接口通过使用BTR2、BTR4或者BTR8FPI突发读来访问。

英飞凌tricore用户手册 第1章 简介

1.简介本用户手册描述了TC1728,一种基于英飞凌TriCore架构的新型32位微控制器DSP。

该文档涵盖了不同封装的TC1728和TC1724的特性。

1.1关于本手册本用户手册的主要读者定位为设计工程师和软件工程师。

手册对TC1728的功能单元、相关寄存器、相关指令及异常情况处理进行了详细描述。

TC1728微控制器用户手册所描述的TC1728特性和TriCore架构紧密相关。

若TC1728直接实现了TriCore架构功能,手册中将其简称为TC1728特性。

手册在描述TC1728特性时若不提及TriCore架构,即表明TC1728直接实现了TriCore架构功能;若TC1728实现的特性是TriCore架构特性的子集,手册会在说明TC1728具体实现的同时指出它与TriCore架构的差别。

这些差别会在相关章节中予以说明。

1.1.1相关文档TriCore架构的详尽描述可参见文档“TriCore架构手册”。

由于TriCore具有可配置性,不同版本的架构包括的系统组成可能因此不同,因此有必要对TC1728架构进行单独说明。

本用户手册和“TriCore架构手册”一起有助于用户完全理解TC1728微控制器的功能。

1.1.2命名规则本手册使用下面的规则来命名TC1728的组成单元:•TC1728的功能单元用大写表示。

例如:“SSC支持全双工和半双工同步通信”。

•低电平有效的引脚,符号上方加横杠表示。

例如:“外部复位引脚,ESR0,具有双重功能”。

•寄存器中的位域和位通常表示为“模块_寄存器名称・位域”或“模块_寄存器名称・位”。

例如大多数寄存器名包括模块名前缀,用下划线“_”和真正的寄存器名分开(例如“ASCO_CON”中“ASCO”是模块名前缀,“CON”是内核寄存器名)。

在描述外设模块的内核时,通常引用内核寄存器名;在描述外设模块的实现时,通常引用外带有模块前缀的寄存器名。

•变量出现在大小写混用中,用来表示一组处理单元或寄存器。

英飞凌tricore用户手册 第5章 程序管理单元

通过重叠 RAM 控制寄存器 OVRCON 控制 OVRAM 的 OLDA 功能和 ECC 保护。位保护允许 OLDA 和 ECC 功 能的独立控制。只有在管理员模式 SV 下才能执行对这个寄存器的写访问,在用户模式或者 SV 下可以执行读访 问。OVRCON 寄存器通过应用(等级 3)复位清零。 如果检测到 ECC 错误,SCU 控制触发一个 NMI 陷阱。 寄存器被定义如下:

5-6

V1.0, 2011-12

TC1728

程序存储器单元(PMU)

5.3

仿真存储器接口

在仿真设备中,提供一个可通过程序存储器或者 OLDA 重叠用于校准的仿真存储器(EMEM)。它的基地址是 A/8FF0 0000H。对于 Flash 和 OVRAM 访问,缓存(段 8H)和非缓存(段 AH)访问都可通过 PMU 用于访问 EMEM。 图 5-1 中显示的仿真存储器接口是 64 位宽度的存储器接口,它控制 CPU 对仿真设备中的仿真存储器进行的访 问。支持所有宽度的写访问(字节、半字、字、双字)。不支持 CPU 控制的载人-修改—保存访问(以 LDMST 指令)。 在 TC1728 生产设备中,EMEM 接口总是被禁止。来自仿真存储器区域的 CPU 读访问引起 DSE 陷阱和 LMB 总线错误。如果仿真存储器区域读访问通过 SPB 主机初始化(例如,PCP),将额外产生 SPB 错误中断。默认 地,任何主机对仿真存储器的写访问在生产设备中导致一个 LMB 总线错误陷阱。 在仿真设备中,如果 EMEM 不能处理 CPU 访问(例如,CPU 访问 EMEM 中的一个存储器跟踪器件时), PMU 报告一个 LMB 总线错误陷阱。在这种情况下,PMU 中止 EMEM 访问。 和内部 8KB OVRAM 相似,EMEM 也可用于内部程序 Flash 和虚拟 OLDA 存储器中的专用重叠块,以将 (DMI 中的)Flash/OLDA 地址重定向到仿真存储器。外部存储器也被支持重定向到 EMEM 中的块。

英飞凌AURIXTC3XX系列车控芯片架构介绍

英飞凌AURIXTC3XX系列车控芯片架构介绍1999年,英飞凌推出了第一代AUDO(AUtomotive unifieD processOr)系列。

基于统一的RISC/MCU/DSP处理器内核,这种32位的TriCore微控制器是一匹计算的良驹。

此后,该公司一直在发展和优化这一概念--最终形成了现在的第六代TriCore。

由于TriCore系列具有高实时性能、嵌入式安全和安保功能,它是广泛的汽车应用的理想平台。

这些应用包括动力系统的发动机管理和变速器、电动和混合动力汽车、底盘域、制动系统、电动助力转向系统、安全气囊、智能网联和驾驶辅助系统,以支持自主、清洁和互联汽车的趋势。

基于TriCore的产品还具有工业、CAV和运输领域所需的多功能性,在优化电机控制应用和信号处理方面表现出色。

英飞凌广泛的产品组合允许工程师从各种存储器、外围设备、频率、温度和封装选项中进行选择。

而这一切都具有跨时代的高度兼容性。

TriCore的成功故事随着AURIX TC2xx多核系列的推出而继续。

AURIX在一个高度可扩展的产品系列中结合了易于使用的功能安全支持、强大的性能和经过验证的未来安全解决方案。

在性能方面的下一个自然演进是AURIX TC3xx,它采用40纳米嵌入式闪存技术制造,为在恶劣的汽车环境中实现终极可靠性而设计。

和以前的AURIX一样,双前端的概念确保了持续供应。

一个广泛的生态系统可用,包括英飞凌自2005年以来一直在开发的AUTOSAR库。

此外,还提供安全软件,帮助制造商满足SIL/ASIL安全标准。

本文将简单介绍AURIX TC3xx系统架构和相关知识,欢迎大家一起学习。

1.功能安全和信息安全 SMU 和HSM在功能安全领域,SMU(Safety Monitoring Unit)和HSM (HardwareSecurity Module)是两个不同的概念和组件。

SMU(Safety MonitoringUnit):SMU是功能安全系统中的一个模块或单元,主要用于监控系统的安全性和运行状态。

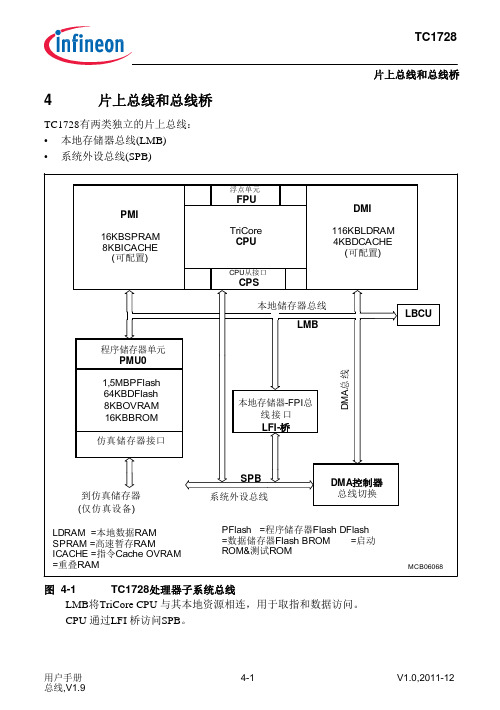

英飞凌tricore用户手册 第4章 片上总线和总线桥

请求/授权

地址周期

数据周 期

MCA06109

图 4-2 基 本 L M B 传 送

传送1由三个周期组成,任何LMB传送均由这三个周期组成:

1. 请求/授权周期:LMB主设备准备执行读或写传送、请求LMB。若LMB可用,在 同一个周期内LMB主设备获得LMB控制器授权。

2. 地址周期:在请求/授权周期之后,主设备将地址送至LMB,所有LMB从设备 检查是否自身被寻址。

图4-4

LMB 总线控制单元寄存器

注: 表4-4地址栏中“偏移地址”是word(32-位)型地址。

中断寄存器 L BCU _SR C

LBCU_reg_its

表4-3

LBCU –寄存器地址空间

模块

起始地址

结束地址

注

LBCU

F87F FE00H

F87F FEFFH

表4-4 缩略名

LBCU_ID

LBCU 模块控制寄存器概览

用户手册 总线,V1.9

4-7

V1.0,2011-12

TC1728

片上总线和总线桥 4.3.4 LMB总线控制单元寄存器

图4-4和表4-4说明了LMB总线控制单元寄存器(LBCU)模块的所有地址映射。

LBCU单元寄存器概览

ID寄存器 LBCU_ID

控制寄存器 LBCU_LEATT

地址/数据寄存 器

表4-2

主设备优先级

优先级

LMB主设备

注

最高

DMA,高优先级

来自模块的DMA请求: -Cerberus高优先级1) -DMA 通道高优先级2)

LFI桥

DMA,中等优先级 数据存储器接口(DMI)

来自模块的DMA请求: -DMA 通道中优先级2)

英飞凌CAN功能系列MCU介绍

Page 4

CAN出现之前 – 点对点连线

空调 引擎 控制 防抱死 制动 照明 电控 门锁

仪表 盘 气囊 电控 车窗

变速箱 控制

主动 悬架

电控 座椅

Page 5

CAN总线拓扑图

空调 引擎 控制 CAN 高速 防抱死 制动 CAN CAN 仪表盘 CAN 照明 CAN CAN 低速 CAN CAN 变速箱 控制 CAN 主动 悬架 电控 座椅 CAN 电控 车窗 CAN 气囊 电控 门锁 CAN

收发器 CAN未规定必须使用哪种收发器

¬ 由于有许多不同类型的CAN收发器,因此微控制器未集成收发器

通常使用双绞线 有些CAN收发器使用单线,有些CAN收发器具有容错能力

2009-11-17

Copyright © Infineon Technologies 2009. All rights reserved.

报文1

报文2

报文3

报文4

源总线 速度A

节点A

无 需

MultiCAN/TwinCAN

节点B

CP U干 预

目标总线 速度B

报文1

报文2

报文3

报文4

至FIFO 对象n

2009-11-17

至FIFO 对象n+1

至FIFO 对象n+2

至FIFO 对象n+3

Page 19

Copyright © Infineon Technologies 2009. All rights reserved.

英飞凌哪些MCU器件具有 -- Bosch CAN? C161JC C161CS

2x Bosch CAN

C164CM C164CI C505CA C515C C164CL C167CR C167CS

英飞凌tricore用户手册 第25章 通用定时器GPT12

25通用定时器单元(GPT12)通用定时器单元GPT1和GPT2模块具有非常灵活的多功能定时器结构,可用作定时、事件计数、脉宽测量、脉冲生成、倍频及其它用途。

它们包括5个16位定时器,分到两个定时器GPT1和GPT2模块中。

每个模块中的各个定时器可在许多不同的模式中独立运行,如门控定时器模式、计数模式、或者和同模块中其它定时器级联工作。

每个模块具有输入/输出功能和与其相关的专用中断。

注:寄存器PISEL可从几个来源中选择输入信号。

GPT1模块有三个定时器/计数器:内核定时器T3和两个辅助定时器T2、T4。

最大的分辨率为f GPT/4。

GPT1模块的辅助定时器可为内核定时器有选择的配置成重载或捕捉寄存器。

这些寄存器见章节25.1.6。

以下列表总结了可支持的功能:•f GPT/4最大分辨率•3个独立定时器/计数器•可级联定时器/计数器•4个可操作模式:–定时器模式–门控定时器模式–计数器模式–增量接口模式•重载和捕捉功能•单独中断GPT2模块有两个定时器/计数器:内核定时器T6和辅助定时器T5。

最大的分辨率为f/2。

另外,捕捉/重载寄存器(CAPREL)支持捕捉和重载操作扩展功能。

这些寄存GPT器见章节25.2.7。

以下列表总结了可支持的功能:•f GPT/2最大分辨率•2个独立定时器/计数器•可级联定时器/计数器•3个可操作模式:–定时器模式–门控定时器模式–计数器模式•通过16位捕捉/重载寄存器CAPREL来扩展捕捉/重载功能•单独中断25.1定时器GPT1模块GPT1(T2,T3,T4)模块的三个定时器均可运行于4个基本模式中:定时器模式、门控定时器模式、计数器模式或者增量接口模式。

所有定时器可以递增或递减计数。

GPT1的每个定时器通过一个单独的控制寄存器TxCON来控制。

每个定时器都有一个相关的输入引脚TxIN(具有引脚功能),在门控定时器模式中提供门控服务,或者在计数器模式中作为计数输入。

英飞凌 tricore TC297 用户手册 中文版

英飞凌tricore TC297 用户手册中文版简介1.简介本用户手册描述了TC1728,一种基于英飞凌TriCore架构的新型32位微控制器DSP。

该文档涵盖了不同封装的TC1728和TC1724的特性。

1.1关于本手册本用户手册的主要读者定位为设计工程师和软件工程师。

手册对TC1728的功能单元、相关寄存器、相关指令及异常情况处理进行了详细描述。

TC1728微控制器用户手册所描述的TC1728特性和TriCore架构紧密相关。

若TC1728直接实现了TriCore架构功能,手册中将其简称为TC1728特性。

手册在描述TC1728特性时若不提及TriCore架构,即表明TC1728直接实现了TriCore架构功能;若TC1728实现的特性是TriCore架构特性的子集,手册会在说明TC1728具体实现的同时指出它与TriCore 架构的差别。

这些差别会在相关章节中予以说明。

1.1.1相关文档TriCore架构的详尽描述可参见文档“TriCore架构手册”。

由于TriCore具有可配置性,不同版本的架构包括的系统组成可能因此不同,因此有必要对TC1728架构进行单独说明。

本用户手册和“TriCore架构手册”一起有助于用户完全理解TC1728微控制器的功能。

1.1.2………命名规则本手册使用下面的规则来命名TC1728的组成单元:TC1728的功能单元用大写表示。

例如:“SSC支持全双工和半双工同步通信”。

低电平有效的引脚,符号上方加横杠表示。

例如:“,具有双重功能”。

寄存器中的位域和位通常表示为“模块_寄存器名称・位域”或“模块_寄存器名称・位”。

例如大多数寄存器名包括模块名前缀,用下划线“_”和真正的寄存器名分开(例如“ASCO_CON”中“ASCO”是模块名前缀,“CON”是内核寄存器名)。

在描述外设模块的内核时,通常引用内核寄存器名;在描述外设模块的实现时,通常引用外带有模块前缀的寄存器名。

英飞凌tricore用户手册 第 章 通用定时器GPT

25通用定时器单元(GPT12)通用定时器单元GPT1和GPT2模块具有非常灵活的多功能定时器结构,可用作定时、事件计数、脉宽测量、脉冲生成、倍频及其它用途。

它们包括5个16位定时器,分到两个定时器GPT1和GPT2模块中。

每个模块中的各个定时器可在许多不同的模式中独立运行,如门控定时器模式、计数模式、或者和同模块中其它定时器级联工作。

每个模块具有输入/输出功能和与其相关的专用中断。

注:寄存器PISEL可从几个来源中选择输入信号。

GPT1模块有三个定时器/计数器:内核定时器T3和两个辅助定时器T2、T4。

最大的分辨率为f GPT/4。

GPT1模块的辅助定时器可为内核定时器有选择的配置成重载或捕捉寄存器。

这些寄存器见章节25.1.6。

以下列表总结了可支持的功能:•f GPT/4最大分辨率•3个独立定时器/计数器•可级联定时器/计数器•4个可操作模式:–定时器模式–门控定时器模式–计数器模式–增量接口模式•重载和捕捉功能•单独中断GPT2模块有两个定时器/计数器:内核定时器T6和辅助定时器T5。

最大的分辨率为f/2。

另外,捕捉/重载寄存器(CAPREL)支持捕捉和重载操作扩展功能。

这些寄存GPT器见章节25.2.7。

以下列表总结了可支持的功能:•f GPT/2最大分辨率•2个独立定时器/计数器•可级联定时器/计数器•3个可操作模式:–定时器模式–门控定时器模式–计数器模式•通过16位捕捉/重载寄存器CAPREL来扩展捕捉/重载功能•单独中断25.1定时器GPT1模块GPT1(T2,T3,T4)模块的三个定时器均可运行于4个基本模式中:定时器模式、门控定时器模式、计数器模式或者增量接口模式。

所有定时器可以递增或递减计数。

GPT1的每个定时器通过一个单独的控制寄存器TxCON来控制。

每个定时器都有一个相关的输入引脚TxIN(具有引脚功能),在门控定时器模式中提供门控服务,或者在计数器模式中作为计数输入。

英飞凌tricore用户手册 第8章 存储映射

PCP存储器(表 8-5)。

• 移动段15内的SCU地址映射,因为SCU现需求2×256字节。

• 移动段15内的ADC和FADC地址映射,因为那些模块现需要要更多的256字节片段。

• 调整了存储器和flash大小(SPRAM, LDRAM, CRAM, PRAM, PFlash, DFlash)。

• 增加了指令/数据Cache配置说明。

保留

8FE7 0000H - 32 Kbyte 在线数据获取

8FE7 7FFFH

(OLDA)

8FE7 8000H - 32 Kbyte 保留 8FE7 FFFFH

访问类型

读

写1)

MPN 强制中 MPN 强制

断

中断

SPBBE SPBBE

访问

访问1)

LMBBE & SPBBE

LMBBE & SPBBE

LMBBE & SPBBE

TC1728

存储映射

8

存储映射

本章将概述TC1728的存储映射,并从两种不同片上总线的角度描述各单元、存储器和 保留区域的地址分配和访问权限。

TC1728中包含以下存储器单元

• 程序存储器单元(PMU)包含: – 1.5Mbyte 程序Flash 存储器(PFLASH) – 64 KB 数据Flash 存储器(DFLASH) – 16 KB Boot ROM(BROM) – 8KB 重叠存储器 (OVRAM1))

1)DMA 包括: DMA 移动引擎 以及类似于MLI模块的连接到DMA外设接口

用户手册

8-3

存储映射, V1.91

V1.0, 2011-12

TC1728

表8-2 到表8-4 中地址映射所使用的缩写和术语定义见表8-1。

英飞凌tricore用户手册_第18章_同步串行口SSC

18同步串行接口(SSC)同步串行接口(SSC)本章描述TC1728的四个高速同步串行接口SSC0,SSC1,SSC2和SSC3。

包括以下内容:•SSC 内核功能描述,适用于SSC0,SSC1,SSC2和SSC3模块(见页18-1)•SSC 内核寄存器描述,描述所有SSC 内核专用寄存器(见页18-27)•TC1728中SSC 模块具体实现及SSC0/SSC1/SSC2模块寄存器(端口连接和控制、中断控制、地址译码、时钟控制,(见页18-43)注:章节18.2中给出的SSC 内核寄存器在TC1728用户手册其它章节引用时,需要分别添加模块名前缀“SSC0_”,“SSC1_”和“SSC2_”。

18.1SSC 内核描述图18-1为SSC 接口框图。

图18-1SSC接口基本框图同步串行接口(SSC) 18.1.1概述SSC支持波特率高达55.0Mbit/s的全双工和半双工串行同步通信(@110.0MHz模块时钟,主模式)。

串行时钟信号由SSC模块自身产生(主模式),或从外部主机接收(从模式)。

数据宽度、移位方向、时钟极性和相位均可编程设定,从而支持与SPI兼容器件通信。

数据发送和接收双缓存。

移位时钟产生器为SSC提供独立的串行时钟信号。

从模式操作具有7个从机选择输入。

主模式支持8个可编程从机选择输出(片选)。

特性:•主模式和从模式操作–全双工或半双工工作–可进行自动引出端控制•灵活的数据格式–数据位个数可编程:2至16位(奇偶性使能:1至15数据位)–移位方向可编程:LSB或MSB在先–时钟极性可编程:移位时钟低电平空闲或高电平空闲–时钟/数据相位可编程:在移位时钟的前沿或后沿进行数据移位•波特率产生:–主模式:55.0Mbit/s到839.3bit/s(@110MHz模块时钟)–从模式:27.0Mbit/s到839.3bit/s(@110MHz模块时钟)•中断产生–发送缓存寄存器已空的情况–接收缓存寄存器已满的情况–出错情况(接收、相位、波特率、发送错误,奇偶性错误)•排队SSC模式支持通过DMA控制器的控制和数据处理•灵活的SSC引脚配置•硬件支持奇偶性模式–可独立选择传送和接收帧数–奇偶性选择•从模式下,7个从机选择输入SLSI[7:1]•主模式下,8个可编程从机选择输出SLSO[7:0]–自动产生SLSO,时序可编程设置–有效电平和使能控制可编程–与其他SSC模块的SLSO输出信号组合18.1.2一般操作SSC支持高达55.0Mbit/s的全双工和半双工串行同步通信(@110.0MHz模块时钟)。

英飞凌tricore用户手册 第13章 中断系统INT

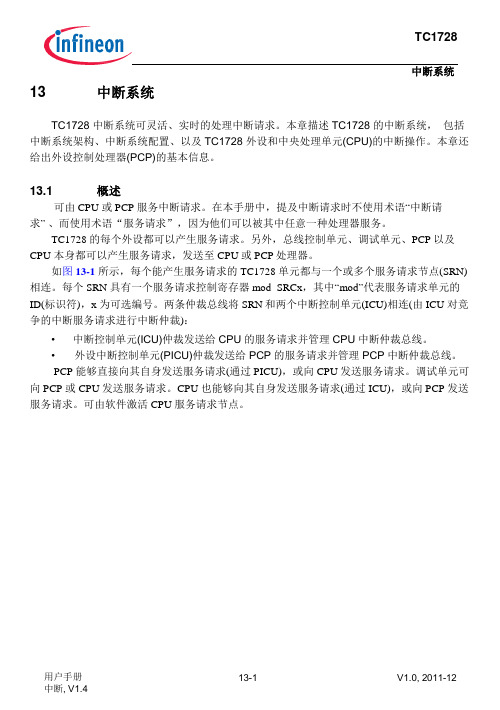

13中断系统TC1728中断系统可灵活、实时的处理中断请求。

本章描述TC1728的中断系统,包括中断系统架构、中断系统配置、以及TC1728外设和中央处理单元(CPU)的中断操作。

本章还给出外设控制处理器(PCP)的基本信息。

13.1概述可由CPU或PCP服务中断请求。

在本手册中,提及中断请求时不使用术语“中断请求”、而使用术语“服务请求”,因为他们可以被其中任意一种处理器服务。

TC1728的每个外设都可以产生服务请求。

另外,总线控制单元、调试单元、PCP以及CPU本身都可以产生服务请求,发送至CPU或PCP处理器。

如图13-1所示,每个能产生服务请求的TC1728单元都与一个或多个服务请求节点(SRN)相连。

每个SRN具有一个服务请求控制寄存器mod_SRCx,其中“mod”代表服务请求单元的ID(标识符),x为可选编号。

两条仲裁总线将SRN和两个中断控制单元(ICU)相连(由ICU对竞争的中断服务请求进行中断仲裁):•中断控制单元(ICU)仲裁发送给CPU的服务请求并管理CPU中断仲裁总线。

•外设中断控制单元(PICU)仲裁发送给PCP的服务请求并管理PCP中断仲裁总线。

PCP能够直接向其自身发送服务请求(通过PICU),或向CPU发送服务请求。

调试单元可向PCP或CPU发送服务请求。

CPU也能够向其自身发送服务请求(通过ICU),或向PCP发送服务请求。

可由软件激活CPU服务请求节点。

图13-1TC1728中断系统框图SET R CLRRSRR SRE0TOS0SRPN13.2服务请求节点每个SRN具有一个服务请求控制寄存器和接口逻辑(通过接口逻辑将SRN和触发单元以及两条中断仲裁总线相连)。

TC1728一些外设单元具有多个SRN。

13.2.1服务请求控制寄存器TC1728中的所有服务请求控制寄存器具有相同的格式。

这些寄存器通常包含:•使能/禁止信息•优先级信息•中断服务处理器(PCP或CPU)•选择服务请求状态位•软件控制的服务请求置位和清零位除了通过相关触发单元硬件激活之外,每个SRN还可通过软件控制的服务请求由软件置位或复位。

Magic-ICE 仿真器用户手册

Magic-ICE™ARM 仿真器用户手册深圳市英贝德科技有限公司(2005-8-26)第一章概述 (3)1.1 系统配置要求 (3)1.2 设备连接 (4)1.3 电源的使用 (4)1.4 Magic-ICE™的优点 (4)1.5 内核支持................................................................................................... (5)第二章JTAG 口介绍 (6)2.1 接口连接.................................................................................. (6)2.2 接口电平...................................................................................... .. (7)2.3 TCK 信号频率设置.................................................................... (8)2.4 目标系统设计指南..................................................................... (9)2.5 RTCK 时钟.................................................................................. . (10)2.6 JTAG 连接转换座.......................................................................... . (10)第三章 Magic-ICE™介绍 (12)3.1 系统功能层次划分................................................................................. . (12)3.2 软件架构............................................................................................... (12)3.3 远程调试功能...................................................................................................…..... .133.4 Server 配置.........................................................................................................….... .143.4.1 自动配置.......................................................................................................…...... .143.4.2 手动配置 (14)3.4.3 IR 长度文件 (15)3.4.4 配置过程 (16)3.5 多内核目标系统 (16)3.6 系统组成结构 (18)第四章Server program 使用指南 (20)4.1 启动Server program (20)4.2 Server program菜单介绍................................................................................…..... .214.2.1 工具栏 (21)4.2.2 文件菜单 (22)4.2.3 视图菜单 (22)4.2.4 控制菜单 (23)4.2.5 连接菜单 (24)4.2.6 设置菜单 (24)4.3 Server 状态指示 (24)4.3.1 配置后的状态 (25)4.3.2 连接后的状态 (26)4.3.3 激活时的状态 (27)4.4 并口设置 (28)4.5 时钟设置 (28)4.6 运行控制 (29)4.6.1 指定各个设备之间的交互方式 (29)4.6.2 设置轮询频率 (31)4.7 启动选项设置 (32)附录一TCK 频率与设置值转换表 (34)附录二TCK 设置值与频率转换表 (37)附录三常见问题 (40)第一章概述本章简单介绍Magic-ICE™ ARM 仿真器的一些基本概念。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

12灵活的CRC引擎(FCE)该章描述了灵活的CRC引擎(FCE)模块。

FCE提供一个或多个循环冗余码(CRC)算法的并行执行。

TC1728当前的FCE版本实现了IEEE802.3、ethernet CRC32和Castagnoli CRC32多项式标准。

FCE的通用结构允许其能够通过多个多项式扩展。

FCE的首要目标是利用CRC签名作为软件应用程序或操作系统服务(与Autosar CRC“CRC例程的规范”兼容)的硬件加速引擎。

CRC算法普遍应用于计算唯一的信息签名,这些签名用于在通信线路如内部总线或者微处理器之间的接口的传输时检查信息的可靠性。

CRC签名也同样适用于签署存放在可变或者不可变存储单元里的数据块。

基于多项式除法计算的签名提供非常高的位错误检测能力。

FCE作为标准FPI总线从外设工作,并且完全由一组配置和控制寄存器控制。

该章由以下内容构成:∙页12-3“FCE特性”∙页12-4“操作概览”∙页12-6“FCE功能描述”∙页12-14“FCE模块寄存器”∙页12-13“FCE模块的接口”∙页12-28“编程指南”∙页12-31“CRC代码的属性”注意:在页12-14“FCE模块寄存器”中描述的FCE内核寄存器名称在用户手册中引用时要加上模块名称前缀“FCE_”。

注意:FCE在将来极有可能也使用在16位微控制器上。

目前还没有这样的需求,但是这个扩展在研发阶段已经被考虑进去了。

12.1相关文档∙输入文档•[D1]A painless guide to CRC Error Detection Algorithms,Ross N.Williams•[D2]Autosar R3.1Rev0001,Specification of CRC Routines V3.0.2•[D3]32-Bit Cyclic Redundancy Codes for Internet Applications,Philip Koopman,International Conference on Dependable Systems and Networks(DSN),2002∙相关标准与规范[S1]IEEE802.3Ethernet32-bits CRC12.2FCE特性FCE提供了如下特性:•构架提供了高达4个不同的CRC多项式。

当前FCE版本执行:—IEEE802.3CRC32ethernet多项式:0x82608EDB(CRC内核0)—CRC32Castagonoli多项式:0x8F6E37A0(CRC内核1)•并行CRC执行(32位宽度)—FCE计算的数据块应是一个32位的倍数—FCE计算的数据块的开始地址,应至少32位对齐•只允许对内核的输入寄存器的32位写访问—对配置寄存器的8位或者16位写访问也是支持的•寄存器接口符合CRC例程的Autosar规范。

可以通过基于软件的保存/恢复机制支持可重入软件例程。

•扩展寄存器接口控制FCE执行的可靠性。

•控制FCE操作的关键寄存器冗余地实现以捕捉瞬态错误。

•通过特定中断节点的错误通知机制:—瞬态错误检测:带有本地状态寄存器(由软件清零)的错误中断产生(可屏蔽的)—校验和失败:带有本地状态寄存器(由软件清零)的错误中断产生(可屏蔽的).FCE实现其中断服务节点。

12.3操作概览FCE是标准的FPI从模块。

FCE与FPI总线同步并且运行在1:1的时钟比例下。

其与微控制器的FPI外设总线相连。

图12-1FCE系统集成:单个CRC内核FCE操作是由一组内存映射寄存器控制的。

主要目的是作为需要CRC校验和计算的软件应用程序的硬件加速。

寄存器组旨在使能FCE。

根据硬件配置,FCE可能实现更多带有不同的CRC多项式的CRC内核。

产品的具体配置将在产品自定义章节里描述。

每个CRC内核将有相同的硬件和软件体系结构。

此文档的其余部分将仅侧重介绍普通CRC内核体系结构。

图12-2显示多内核配置。

图12-2FCE系统集成:多CRC内核在多内核实现中,中断线路进行或运算,FCE对系统只有一个中断节点。

每个crc内核有一个状态寄存器,以使能软件确定哪个中断源处于激活状态。

状态和中断处理请参阅STS寄存器的详细描述。

12.4FCE功能描述图12-3CRC内核架构以下属性的特点是一种基于CRC多项式除法的校验和算法:[1]多项式级数(例如32,表示两个多项式的最高权重)[2]多项式(例如0x04C11DB7:第33位省略,因为总是等于1)[3]初始值:CRC寄存器的初始值[4]输入数据反射:指示输入的并行数据的每个字节被用来计算CRC之前是否被反射[5]结果数据反射:表示CRC的最终值是否被反射[6]XOR值:指示返回CRC结果之前是否进行最后的XOR运算一旦选择了一个多项式,所有的属性是静态的。

不过FCE具有通过控制两个反射步骤以及最终xor操作的功能,如图12-3所示。

复位值是与实现算法兼容的。

最终的xor控制使能选择0xFFFFFFFF或0x00000000与POST_CRC1进行xor运算(见图12-3)。

这两个值是最常见的CRC多项式所经常使用的。

注意:反射步骤和最终XOR不修改基于错误检测的CRC算法的属性,只有CRC最后的签名受到影响。

CRC操作软件必须首先确保CRC内核配置正确,尤其是通过CRC寄存器写入的CRC寄存器的初始值。

如果想要软件实现在每个报文末尾进行自动签名检查,LENGTH和CHECK寄存器必须分别根据报文的长度(即为32位字的数量)和期望的签名(CHECK)进行配置。

CHECK值受到CRC反射和XOR操作的影响。

自检查由E位域使能。

属性:如果输入报文M1由报文M0及其CRC签名组成,那么M1的CRC签名应为0。

.根据报文的长度,可多次软件写入IR寄存器,如果E位置位,每一次写IR寄存器,LENGTH寄存器减1。

当LENGTH寄存器已经为0,但是软件依然对IR寄存器进行写操作(错误操作),LENGTH寄存器的每一位都应该被置1,并且保持该值直到软件重新初始化新的报文。

在这样的情况下,STS.MLF(报文长度标志位)应被置位,并且如果CFG.MLE(报文长度错误)置位产生一个中断。

硬件监控LENGTH寄存器从1到0的跳变,以检测报文的结束,并进行POST_CRC2(见图12-3)与CHECK寄存器值的比较。

下面两个图是对CRC内核的控制和状态特性的概览。

图12-4CRC内核配置寄存器图12-5CRC内核状态寄存器寄存器保护和监控方法寄存器监控:适用于CFG和CHECK寄存器因为CFG和CHECK寄存器是CRC操作的关键,提供了一些用于检测和记录瞬态错误的机制。

瞬态错误的早期检测可以改善错误检测时间并且减小错误的严重性。

使用两个冗余实例的监测机制被执行,如图12-6所示。

图12-6寄存器监控方案为<REG>指派CFG或者CHECK寄存器。

当对<REG>进行写操作时,冗余寄存器的复制也发生更新。

软件上冗余寄存器不可见。

<REG>的保留位不具有存储功能,并且不用于冗余。

比较逻辑持续比较两个保存的值,并且给出一个信号,指示比较是否成功。

所有比较块的结果被进行或运算从而得到一个单独标志位信息。

如果发现比较结果不符,STS.CEF位(配置错误标志位)置位。

对于比较逻辑的实时验证,给出强制寄存器不符合位(CTR.FRM_<REG>)。

当冗余寄存器被软件置1,冗余寄存器向左移一位(冗余位0总是被逻辑0值代替),并且代替冗余寄存器值输入给比较逻辑。

这使能检查比较逻辑。

通过使用移动位模式,软件可以完全检查比较逻辑的全部操作。

寄存器访问保护:适用于LENGTH和CHECK寄存器为了减少对CHECK和LENGTH寄存器的错误配置的可能性(在自动检查被使用的情况下),对CHECK和LENGTH寄存器的写访问必须遵循图12-7所示的流程。

图12-7对CHECK寄存器的访问控制为<REG>指派CFG或者CHECK寄存器。

在能够对一个CRC内核的CHECK寄存器中配置一个新值<value>之前,软件必须首先对CHECK地址写值0xFACECAFE。

0xFACECAFE不是写入CHECK寄存器中。

下一个写操作将如同正常FPI写操作一样进行。

这个过程将在每次软件试图配置新的<REG>值时被重复。

如果软件在写0xFACECAFE后读CHECK寄存器,其返回当前<REG>内容,而不是0xFACECAFE。

对<REG>的读访问对保护机制没有影响。

FCE中断每个FCE CRC内核提供一个内部中断源。

每个CRC内核的中断线路相或,其结果发送到实现标准中断节点逻辑和寄存器的FCE中断控制块。

当一个FCE中有多个CRC内核时,每个CRC内核的中断线路相或,以向中断控制块提供单一中断源。

如果来自FCE的中断被仲裁,FCE中断处理器必须使用位于每个CRC内核的STS状态寄存器的状态信息。

每个CRC内核提供如下中断源:.CRC不匹配中断。

由CFG.CMI位域控制并可通过状态位STS.CMF(CRC不匹配标志位)观察。

.配置错误中断。

由CFG.CEI位域控制并可通过状态位STS.CEF(配置错误标志位)观察。

.长度错误中断。

由CFG.LEI位域控制并可通过状态位STS.LEF(长度错误标志位)观察。

.FPI错误中断。

由CFG.FEI位域控制并可通过状态位STS.FEF(FPI错误标志位)观察。

中断产生规则状态标志位应通过软件向相应位写1来清零。

.如果状态标志位被置位,并且新的硬件条件发生,内核没有产生新的中断:STS.<FLAG>掩码从相同的源产生一个新的中断。

如果发生软件访问以清除中断状态位并且在同一周期中硬件试图设置该位,硬件条件赢得仲裁。

由于所有中断都是由错误条件引起的,因此应该由一个错误管理软件层处理中断。

使用FCE作为加速引擎的软件服务可能不直接处理错误条件,但让上层使用这项服务来进行错误处理。

12.5FCE模块接口FCE模块实现了自己的中断节点,进而实现对Tricore和PCP中断控制器的接口。

出于保护目的,它使用EINIT信息来控制关键源的配置。

EINIT保护在寄存器章节里进行描述。

表12-1普遍FCE数字连接信号来自/连接到模块对FCE来说输入/输出EINIT SCU输入12.6FCE模块寄存器图12-8和表12-3显示了所有与FCE CRC内核相关联寄存器。

该节中描述所有FCE内核寄存器的名称。

他们应该在产品规范的上下文中使用前缀"FCE_"。

寄存器通过索引来编号,以指示相关的FCE CRC内核(m=0-1)。