NXP ARM MCU Introduction - Cortex Core - 20100113_R

手机处理器架构进化历程

手机CPU处理器架构进化历程随着智能手机越来越普及,消费者在选购手机的时候也越来越理性化,除了关心价格和外观之外,手机的性能也成为了人们最关心的因素,大家都知道,处理器是影响手机性能的最关键的因素,像德州仪器、高通、英伟达以及三星等主流的处理器厂商,大家都已经耳熟能详。

但是很多人并不知道,其实它们采用的都是同一个架构——ARM架构,实际上,处理器采用的架构才是影响处理器性能的关键因素。

今天,笔者就和大家一起,聊一聊ARM的那些事。

ARM架构简介ARM架构简介ARM(Advanced RISC Machine的缩写)架构,被称作进阶精简指令集机器,是一个32位精简指令集(RISC)处理器架构,其广泛地使用在许多嵌入式系统设计。

由于低成本、高效能、低耗电的特性,ARM处理器非常适用于移动通讯领域。

为了大家更好的理解,我们不妨做个比喻,ARM架构就像是一座建筑的结构设计部分,而处理器就相当于一个完整的建筑,只有有了稳定的结构作为基础,才能建造出各式各样的房子。

换句话说,ARM架构只相当于一座建筑的框架,至于最后建造出来的房子长什么样,舒适度如何,就是由处理器厂商自己决定了。

不过有一点需要说明,假如结构的设计值是十层,容纳人数的上限是100人,那么最后建好的房子也不能超过这个上限。

这也就是说,采用相同架构的处理器,性能基本上已经锁定在一定的范围之内,不会有本质的区别。

所以,看处理器的性能要先看架构。

ARM架构ARM授权方式ARM公司是一家知识产权供应商,本身并不参与终端处理器芯片的制造和销售,而是通过向其它芯片厂商授权设计方案,来获取收益。

ARM提供了多样的授权方式,ARM公司可以向芯片厂商单纯的转让设计方案的使用及销售权,比如德州仪器,其旗下的OMAP处理器是在原始ARM架构的基础上设计的,这种方式费用一般比较低,所以,德州仪器的芯片售价也相对较低。

对于一些具备自有设计技术的客户,他们希望能对原始的ARM架构进行优化,以便更好的适应到自己研发的芯片,这样就会牵扯到授权架构修改的费用,而且这项费用也是相当昂贵的。

ARM-Cortex各系列处理器分类比较

Cortex—M系列M0:Cortex—M0是目前最小的ARM处理器,该处理器的芯片面积非常小,能耗极低,且编程所需的代码占用量很少,这就使得开发人员可以直接跳过16位系统,以接近8 位系统的成本开销获取32 位系统的性能。

Cortex—M0 处理器超低的门数开销,使得它可以用在仿真和数模混合设备中。

M0+:以Cortex-M0 处理器为基础,保留了全部指令集和数据兼容性,同时进一步降低了能耗,提高了性能.2级流水线,性能效率可达1。

08 DMIPS/MHz。

M1:第一个专为FPGA 中的实现设计的ARM 处理器。

Cortex—M1 处理器面向所有主要FPGA 设备并包括对领先的FPGA 综合工具的支持,允许设计者为每个项目选择最佳实现.M3:适用于具有较高确定性的实时应用,它经过专门开发,可使合作伙伴针对广泛的设备(包括微控制器、汽车车身系统、工业控制系统以及无线网络和传感器)开发高性能低成本平台。

此处理器具有出色的计算性能以及对事件的优异系统响应能力,同时可应实际中对低动态和静态功率需求的挑战。

M4:由ARM 专门开发的最新嵌入式处理器,用以满足需要有效且易于使用的控制和信号处理功能混合的数字信号控制市场。

M7:在ARM Cortex—M 处理器系列中,Cortex—M7 的性能最为出色。

它拥有六级超标量流水线、灵活的系统和内存接口(包括AXI 和AHB)、缓存(Cache)以及高度耦合内存(TCM),为MCU 提供出色的整数、浮点和DSP 性能.互联:64位AMBA4 AXI, AHB外设端口(64MB 到512MB)指令缓存:0 到64kB,双路组相联,带有可选ECC数据缓存:0 到64kB,四路组相联,带有可选ECC指令TCM:0 到16MB,带有可选ECC数据TCM:0 到16MB,带有可选ECCCortex-A系列:ARM Cortex—A 系列是一系列用于复杂操作系统和用户应用程序的应用程序处理器。

NXP i.MX RT500双核ARM MCU嵌入应用开发方案

NXP i.MX RT500双核ARM MCU嵌入应用开发方案NXP公司的i.MX RT500是嵌入应用的双核微控制器(MCU),包括Arm Cortex-M33 CPU和CadenceRXtensaR Fusion F1音频数字信号处理器CPU. Cortex-M33 CPU包括两个硬件协处理器,提供增强性能,用于一系列复杂算法和带有LCD接口和MIPI DSI PHY的2D失量GPU.该系列具有丰富的外设和非常低的功耗.器件有多达5MB SRAM,两个FlexSPIs (Octal/Quad SPI 接口),每个有32KB缓存,以及一个动态加密,高速USB器件/主+PHY,12位1MSps ADC,模拟比较器,支持8 DMIC通路的音频子系统,2D GPU 和LCD控制器以及MIPI DSI PHY, SDIO/eMMC; FlexIO; AES/SHA/Crypto M33协处理器和PUF键发生器.控制处理器Arm Cortex-M33工作频率高达200MHz,并内置了嵌套中断向量控制器(NVIC),主外接电源1.8V ± 5%, Vddcore电源从0.6V到1.1V可调,模拟电源1.71-3.6 V,五个VDDIO电源为1.71 - 3.6 V,USB电源为3.0-3.6 V.主要用在工业领域,智能可穿戴市场以及,智能家庭,物联网(IOT)和玩具与棋类游戏.本文介绍了i.MX RT500主要特性,框图和评估板i.MX RT500 EVK (MIMXRT595-EVK) 技术和功能指标以及电路图. The i.MX RT500 is a family of dual-core microcontrollers forembedded applications featuring an Arm Cortex-M33 CPUcombined with a CadenceRXtensaR Fusion F1 Audio DigitalSignal Processor CPU. The Cortex-M33 includes two hardwarecoprocessors providing enhanced performance for an array ofcomplex algorithms along with a 2D Vector GPU with LCDInterface and MIPI DSI PHY. The family offers a rich set ofperipherals and very low power consumption. The device has upto 5 MB SRAM, two FlexSPIs(Octal/Quad SPI Interfaces) eachwith 32 KB cache, one with dynamic decryption, high-speed USBdevice/host + PHY, 12-bit 1 MS/s ADC, Analog Comparator,Audio subsystems supporting up to 8 DMIC channels, 2D GPUand LCD Controller with MIPI DSI PHY, SDIO/eMMC; FlexIO;AES/SHA/Crypto M33 coprocessor and PUF key generationi.MX RT500主要特性:Control processor core• Arm Cortex-M33 processor, running at frequencies ofup to 200 MHz• Arm TrustZone• Arm Cortex-M33 built-in Memory Protection Unit (MPU)supporting eight regions• Single-precision Hardware Floating Point Unit (FPU).• Arm Cortex-M33 built-in Nested Vectored InterruptController (NVIC).• Non-maskable Interrupt (NMI) input.• Two coprocessors for the Cortex-M33: a hardwareaccelerator for fixed and floating point DSP functions(PowerQuad) and a Crypto/FFT engine (Casper).TheDSP coprocessor uses a bank of four dedicated 2 KBSRAMs. The Crypto/FFT engine uses a bank of two 2KB SRAMs that are also AHB accessible by the CPUand the DMA engine.• Serial Wire Debug with eight break points, four watchpoints, and a debug timestamp counter. It includesSerial Wire Output (SWO) trace and ETM trace.• Cortex-M33 System tick timerDSP processor core• Cadence Tensilica Fusion F1 DSP processor, runningat frequencies of up to 200 MHz.• Hardware Floating Point Unit.• Serial Wire Debug (shared with Cortex-M33 ControlDomain CPU).Communication interface• 9 configurable universal serial interface modules(Flexcomm Interfaces). Each module contains anintegrated FIFO and DMA support. Each of the ninemodules can be configured as:• A U SART with dedicated fractional baud rategeneration and flow-control handshakingsignals. The USART can optionally be clockedat 32 kHz and operated when the chip is inreduced power mode, using either the 32 kHzclock or an externally supplied clock. TheUSART also provides partial support forLIN2.2.• An I2C-bus interface with multiple addressrecognition, and a monitor mode. It supports400 Kb/sec Fast-mode and 1 Mb/sec FastmodePlus. It also supports 3.4 Mb/sec highspeedwhen operating in slave mode.• An SPI interface.• An I2S (Inter-IC Sound) interface for digitalaudio input or output. Each I2S supports up tofourchannel-pairs.• Two additional high-speed SPI interfaces supporting50 MHz operation• One additional I2C interface with open-drain pads• Two I3C bus interfaces• A digital microphone interface supporting up to 8channels with associated decimators and VoiceFive I/O Power Rails• Five independent supplies powering different clustersof pins to permit interfacing directly tooff-chipperipherals operating at different supply levels.On-chip memory• Up to 5 MB of system SRAM accessible by both CPUs,both DMA engines, the Graphics Subsystem and allother AHB masters.• Additional SRAMs for USB traffic (16 KB), Cortex-M33co-processors (4 x 2 KB), SDIO FIFOs (2 x 512 B dualport),PUF secure key generation (2 KB), FlexSPIcaches (32 KB each), SmartDMA commands (32 KB),and a variety of dual and single port RAMs forgraphics.• 16 kbits OTP fuses• Up to 192 KB ROM memory for factory-programmeddrivers and APIs• System boot from High-speed SPI, FlexSPI Flash, HSUSB, I2C, UART or eMMC via on-chip bootloadersoftware included in ROM. FlexSPI boot mode willinclude an option for Execute-in-placestart-up for nonsecureboot.Digital peripherals• Two general purpose DMA engines, each with 37channels and up to 27 programmablerequest/triggersources.• Can be configured such that one DMA is secureand the other non-secure and/or one can bedesignated for use by the M33 CPU and theother by the DSP• Smart DMA Controller with d edicated 32KB code RAM• USB high-speed host/device controller with on-chipPHY and dedicated DMA controller.• Two FlexSPI (Octal/Quad) Interfaces up to 200 MHzDDR/SDR (target). 32 KB caches with selectablecache policies based on programmable addressregions. One of the FlexSPI interface will include onthe-fly decryption for execute-in-place and addressremappingto support dual-image boot. DMA supported(both modules).• Two SD/eMMC memory card interfaces with dedicatedDMA controllers. One supports eMMC 5.0 withHS400/DDR operation.Analog peripherals• One 12-bit ADC with sampling rates of 1 Msamples/secand an enhanced ADC controller. It supports up to 10single-ended channels or 5 differential channels. TheADC supports DMA.• Temperature sensor.• Analog compar atorActivation Detect. One pair of channels can bestreamed directly to I2S. The DMIC supports DMA.Timers• One 32-bit SCTimer/PWM module (SCT). Multipurposetimer with extensiveevent-generation,match/compare, and complex PWM and outputcontrol features.• 10 general-purpose/PWM outputs, 8 generalpurposeinputs• It supports DMA and can trigger external DMAevents• It supports fractional match values for highresolution• Five general purpose, 32-bit timer/counter moduleswith PWM capability• 24-bit multi-rate timer module with 4 channels eachcapable of generating repetitive interrupts atdifferent, programmable frequencies.• Two Windowed Watchdog Timers (WDT) withdedicated watchdog oscillator (1 MHz LPOSC)• Frequency measurement module to determine thefrequen cy of a selection of on-chip or off-chip clocksources.• Real-Time Clock (RTC) with independent powersupply and dedicated oscillator. Integratedwake-uptimer can be used to wake the device up from lowpowermodes. The RTC resides in the “always-on”voltage do main. RTC includes eight 32-bit generalpurposeregisters which can retain contents whenpower is removed from the rest of the chip.• Ultra-low power micro-tick Timer running from theWatchdog oscillator with capture capability fortimestamping. Can be used to wake up the devicefrom low-power modes.• 64-bit OS/Event Timer common to both processorswith individual match/capture and interruptgeneration logic. Enabled on PORClocks• Crystal oscillator with an operating range of 4 MHzto 26 MHz.• Dual trim option: Internal 192/96 MHz FROoscillator. Trimmed to 1% accuracy.• FRO capable of being tuned using an accuratereference clock (eg. XTAL Osc) to 0.1% accuracywith 46% duty cycle to support MIPI PHY andFlexSPI.• Internal 1 MHz low-power oscillator with 5%accuracy. Serves as the watchdog oscillator andclock for the OS/Event Timer and the Systick amongothers.Also available as the system clock to bothdomains.• 32 kHz real-time clock (RTC) oscillator that canoptionally be used as a system clock.• Main Syste m PLL:• allows CPU operation up to the maximum ratewithout the need for a high-frequency crystal.Graphics/Multimedia• 2D Vector Graphics Processing Unit, running atfrequencies of up to 200 MHz.• LCD Display Interface supporting smart LCD displaysand vi deo mode.• MIPI DSI Interface with on-chip PHY supportingtransfer rates up to 895.1 Mbps.• FlexIO can be configured to provide a parallel interfaceto an LCDI/O Peripherals• Up to 136 general purpose I/O (GPIO) pins withconfigurable pull-up/pull-down resistors. Ports can bewritten as words, half-words, bytes, or bits.• Mirrored, secure GPIO0.• Individual GPIO pins can be used as edge and levelsensitive interrupt sources, each with its own interruptvector.• All GPIO pins can contribute to one of two ganged(OR’d) interrupts from the GPIO_HS module.• A group of up to 7 GPIO pins (from Port0/1) can beselected for Boolean pattern matching which cangenerate interrupts and/or drive a “pattern-match”output.• Adjustable output driver slew rates.• JTAG bounda ry scanSecurity• Secure Isolation: Protection from software and remoteattacks using Trustzone for armV8M. Hardwareisolation of AES keys• Secure Boot: firmware in ROM providing immutableroot of trust• Secure Storage: Physically Unclonable Function(PUF) based key store, On-the-fly-AESdecryption(OTFAD) of off-chip flash for code storage• Secure Debug: Certificate based debug authenticationmechanism• Secure Loader: Supports firmware update mechanismwith authenticity (RSA signed) and confidentiality(AES-CTR encrypted) protection• Secure Identity: 128-bit Universal Unique Identifier(UUID), 256-bit Compound Device Identifier (CDI) perTCG DICE specification• Cryptographic Accelerators• Symmetric cryptography (AES) with128/192/256-bit key strength and protectionagainst Side-channel analysis (Differential PowerAnalysis and Template attacks)• Asymmetric cryptography acceleration usingCASPER co-processor• NIST SP 800-90b compliant TRNG design with512-bit output per call• Hash engine with SHA-256 and SHA1May be run from the FRO, the crystaloscillator or the CLKIN pin. • a second, independent PLL output providesalternate high-frequency clock source for theDSP CPU if the required frequency is differentfrom the main system clock. (Note: 2nd PFDoutput from Main System PLL) • two additional PLL outputs provide potentialclock sources to various peripherals.• Audio PLL for the audio subsystem.Power Control• Main external power supply: 1.8V ± 5%• Vddcore supply (from PMIC or internal PMU):adjustable from 0.6 V to 1.1 V (including retentionmode) • Analog supply: 1.71-3.6 V• Five VDDIO supplies (can be shared orindependent): 1.71 - 3.6 V• USB Supply: 3.0-3.6 V• Reduced power modes:• Sleep mode: CPU clock shut down (each CPUindependently)• Deep_sleep mode: Us er-selectableconfiguration via PDSLEEPCFG• Deep_powerdown mode: Internal powerremoved from entire chip except “always-on”domain• Each individual SRAM partition can beindependently powered-off or put into a lowpowerretain mode• DSP Domain can be powered-offindependently from the rest of the system.• Ability to operate the synchronous serialinterfaces in sleep or deep-sleep as a slave orUSART clocked by the 32 kHz RTC oscillator• Wake-up from low-power modes via interruptsfrom various peripherals including the RTCand the OS/Event timer• RBB/FBB to provide additional control over power/performance trade-offs• Power-On Reset (POR).Operating characteristics• Temperature range (ambient): -20 °C to +70 °C• VDDCORE: 0.7 V - 1.155 V• VDDIO_0/1/2/4: 1.71 V - 1.89 V• VDDIO_3: 1.71 V - 3.6 V图2.评估板i.MX RT500 EVK (MIMXRT595-EVK)外形图(正面)图3.评估板i.MX RT500 EVK (MIMXRT595-EVK)外形图(背面)图4.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(1)图5.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(2)图6.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(3)图7.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(4)图8.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(5)图9.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(6)图10.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(7)图11.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(8)图12.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(9)图13.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(10)图14.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(11)图15.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(12)图16.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(13)图17.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(14)图18.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(15)图19.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(16)图20.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(17)图21.评估板i.MX RT500 EVK (MIMXRT595-EVK)电路图(18)。

NXP mcu

置的新型开漏工作模式

LPC1100

◎ 四个通用计数器/计数器 ◎ 可编程的看门狗定时器(WDT),带锁死功能 ◎ 系统计时器 ◎ 各外设自带时钟分频器,有利于降低功耗

芯片特色:

Cortex-M0处理器性能 ● Cortex-M0微控制器可以轻松超越高端8位和16位器件的

性能水平; ● 内核额定性能为0.9DMIPS/MHz,相当于与其最接近的8位

EasyCortex M3-1300开发平台板载USB仿真器,支持USB2.0 Device,具有带电气隔离的RS-485接口等功能。EasyCortexM3-1300开发平台配套 提供多种免费商业化软件包及其详尽的开发文档,加快产品开发。

集学习、实验、开发于一体的 “三合一”高性价比开发板

● 功能特点 ◎ 标配CPU:LPC1343,全面支持LPC1313、LPC1100系列 芯片; ◎ 处理速率高达72MHz; ◎ 片上集成HID和大容量USB设备驱动; ◎ 内置嵌套向量中断控制器(NVIC); ◎ 32KB片上Flash程序存储器,支持在系统编程(ISP)和在 应用编程(IAP); ◎ 8KB SRAM可供高性能CPU通过指令总线、系统总线和 数据总线访问; ◎ 串行调试端口和串行跟踪端口; ◎ 3种低功耗模式:睡眠、深度睡眠和深度掉电; ◎ 集成PMU(电源管理单元),进一步降低功耗; ◎ 掉电检测,设有4个独立的中断和强制复位阈值; ◎ 片内集成上电复位电路; ◎ 内置系统节拍定时器(SysTick),方便操作系统移植; ◎ 3.3V单电源供电(2.0V ~3.6V); ◎ 工作温度:-40°C ~ 85°C。

Cortex-M0组件 Cortex-M0处理器

中断

嵌套向量 中断控制器

(NVIC)

什么是MCU-MCU基础知识讲解

什么是MCU?MCU基础知识讲解诸多原因显示,MCU在2018年将继续缺货。

1、汽车电子及物联网大量导入MCU架构,需求爆发2、ST、TI、瑞萨等IDM厂产能不足,导致交期拉长。

据悉,不少MCU厂商产品交期都从4个月延长至6个月,日本MCU厂商更是拉长至9个月。

3、原材料的上涨。

目前已经有晶圆厂宣布涨价,可能会对MCU造成涨价缺货。

什么是MCU?MCU,中文简称单片机。

即将CPU、存储器(RAM和ROM)、多种I/O接口等集成在一片芯片上,形成的芯片级计算机。

CPU:包括运算器、控制器和寄存器组。

是MCU内部的核心部件,由运算部件和控制部件两大部分组成。

前者能完成数据的算术逻辑运算、位变量处理和数据传送操作,后者是按一定时序协调工作,是分析和执行指令的部件。

存储器:包括ROM和RAM。

ROM程序存储器,MCU的工作是按事先编制好的程序一条条循序执行的,ROM程序存储器即用来存放已编的程序(系统程序由制造厂家编制和写入)。

存储数据掉电后不消失。

ROM又分为片内存储器和片外(扩展)存储器两种。

RAM数据存储器,在程序运行过程中可以随时写入数据,又可以随时读出数据。

存储数据在掉电后不能保持。

RAM也分为片内数据存储器和片外(扩展)存储器两种。

I/O接口:与外部输入、输出(电路)设备相连接。

PO/P1/P2/P3等数字I/O接口,内部电路含端口锁存器、输出驱动器和输入缓冲器等电路。

4位、8位、16位、32位、64位MCU的用途4位计算器、车用仪表、车用防盗装置、呼叫器、无线电话、CD播放器、LCD驱动控制。

微软全新Surface Pro拆解:SSD焊死 拆机不可取 易报废

微软全新Surface Pro拆解:SSD焊死拆机不可取易报废今年 5 月底,微软为了表示对中国客户的诚意,特别在上海召开了一场新品发布会。

在这波新品当中,最受瞩目的自然是全新 Surface Pro。

这是微软全新一代 Surface Pro 产品,不过并没有以 Surface Pro 5 命名。

不过,在该设备身上还是有诸多全新的亮点,例如 Surface 产品线中最出色的显示屏幕,还有可以变身成“创意画板”的 165 度新铰链设计等。

当然了,全新 Surface Pro 的内部已经升级到了英特尔第七代 Kaby Lake 微架构的酷睿处理器,其中内置酷睿 m3 处理器和 i5 处理器的版本可实现了“无风扇设计”,因此全新 Surface Pro 也成为了全球首款无风扇设计的内置 i5 处理器的设备。

微软还认为,得益于内部的改进,Surface Pro 5 成为了有史以来最轻便的 Surface 设备。

那么全新 Surface Pro 内部到底改进了些什么呢?唯有拆解方知!最近,知名拆解网站 iFixit 正好拆解了全新的 Surface Pro 5,我们来一探究竟。

iFixit 称,从外形表面上来看,全新 Surface Pro 看起来与去年的 Surface Pro 4 非常的相似,但内部规格和设计肯定有所不同。

在拆解之前,先来了解全新 Surface Pro 的一些公布的主要硬件,如下:- 12.3 英寸 PixelSense 显示屏,IPS 面板,分辨率为 2736 x 1824 (267 PPI)像素,3:2 屏幕比例,支持 10 点多点触控。

- 英特尔 Kaby Lake 架构处理器,最低 Core M3(4M 缓存、2.7GHz),最高 Core i7 (4M缓存、4.0GHz)- 4GB/8GB/16GB 三档容量的 1600MHz DDR3L 内存- 128GB/256GB/512GB/1TB 高速固态硬盘- 800 万像素自动对焦后置摄像头,500 万像素前置摄像头- 1 个全尺寸 USB 3.0 接口、microSDXC 读卡器、Surface Connect 接口、3.5mm 耳机插孔、。

基于ARM处理器的微控制器内存问题

基于ARM处理器的微控制器内存问题闪存现在完全主导着微控制器(MCU),但随着处理器升级到32位架构并且外设变得更加强大,存储器考虑变得更加复杂。

很容易忘记外设中的内存,这些外设使MCU更像是一个包含高级电机控制、图形用户界面(GU1)和网络的片上系统(SOC)。

尽管如此,F1ash和其他存储器类型的细节仍值得关注,以确保所选MCU具有符合系统需求的存储器。

在MCU中以更高速度快速使用ARM®Cortex w-M处理器架构也需要更仔细地检查内存支持。

供应商对其片上存储器选项采取不同的方法,这可能会影响选择哪个MCU的平衡。

如今,在更大的MCU上可以使用多达1兆字节的闪存。

随着MCU发现新应用并具有新功能,程序存储、数据表和暂存器RAM的比例发生了变化。

高端MeU可能使用高级语言(H11)进行编程,运行实时操作系统(皿),并使用现成的堆栈和软件包。

这些因素中的每一个都会影响内存需求和使用。

通常用于MCU的闪存的访问时间可以跟上25到50MHz的处理器时钟。

当高性能处理器内核的时钟频率超过200MHz时,可能会有一个巨大的差距来填补耗时耗电的等待状态。

多个片上总线和特殊的路由机制对于缓解一些繁忙的微控制器中的流量问题非常有益。

ARM处理器内核架构由于其紧凑的ThUn1b2®指令而具有非常好的代码密度,该指令仅需要16位来存储指令,而不是预期的32位。

ARMCorteχ-M0>Corteχ-M3和Corteχ-M4内核在众多供应商的微控制器中都很流行,这里将研究一些内存选择。

NXP Semiconductors1PC4000-实时辅助数据处理NXPSemiconductors自从很久以前将ARM7TDMI®内核用于MCU以来,它就在基于ARM的微控制器上取得了成功。

恩智浦在Cortex-M内核推出后迅速将其添加到其产品组合中,并且一直是将CorteX-M3、Cortex-MO和Cortex-M4集成到一端高速的MCU中的领导者之一,同时将价格推低至另一个。

常用的单片机品牌和型号介绍

常用的单片机品牌和型号介绍单片机(Microcontroller)是一种集成了微处理器核心、存储器和各种外设接口的集成电路,广泛应用于嵌入式系统中。

单片机能够完成各种控制和计算任务,因此在电子领域中使用非常广泛。

本文将介绍几个常用的单片机品牌和型号,以帮助读者选择适合自己项目的单片机。

一、STMicroelectronicsSTMicroelectronics(意法半导体)是全球领先的半导体供应商之一,提供多种单片机产品。

其中,STM32系列是STMicroelectronics最为著名的单片机系列之一,基于ARM Cortex-M内核。

STM32系列广泛应用于各种嵌入式设备,具有高性能、低功耗等特点。

常见的型号包括STM32F0、STM32F1、STM32F4等,适用于不同的应用场景。

二、AtmelAtmel是一家美国公司,也是全球最大的单片机供应商之一。

Atmel的AVR系列单片机以其高性能和易用性而闻名。

AVR系列单片机具有低功耗、快速执行速度和丰富的外设接口,非常适合于各种嵌入式应用。

其中,ATmega328P是最常用的型号之一,广泛使用于Arduino开发板等项目中。

三、Texas InstrumentsTexas Instruments(德州仪器)是一家世界领先的半导体公司,提供多种单片机产品。

MSP430系列是Texas Instruments的一系列低功耗、高集成度的单片机产品,适用于各种便携式设备和电池供电系统。

MSP430系列单片机具有强大的外设功能和丰富的存储器选项,常见的型号有MSP430G2553、MSP430F5529等。

四、MicrochipMicrochip是一家专注于微控制器和模拟半导体的供应商,其PIC 单片机系列非常知名。

PIC系列单片机具有低功耗、高稳定性和广泛的外设接口,适用于各种应用场景。

其中,PIC16F877A是最常用的型号之一,常见于工业自动化、家电控制等领域。

ARMCortex各系列处理器分类比较

Cortex-M系列M0:Cortex-M0是目前最小的ARM处理器,该处理器的芯片面积非常小,能耗极低,且编程所需的代码占用量很少,这就使得开发人员可以直接跳过16位系统,以接近8 位系统的成本开销获取 32 位系统的性能。

Cortex-M0 处理器超低的门数开销,使得它可以用在仿真和数模混合设备中。

M0+:以Cortex-M0 处理器为基础,保留了全部指令集和数据兼容性,同时进一步降低了能耗,提高了性能。

2级流水线,性能效率可达1.08 DMIPS/MHz。

M1:第一个专为 FPGA 中的实现设计的 ARM 处理器。

Cortex-M1 处理器面向所有主要 FPGA 设备并包括对领先的 FPGA 综合工具的支持,允许设计者为每个项目选择最佳实现。

M3:适用于具有较高确定性的实时应用,它经过专门开发,可使合作伙伴针对广泛的设备(包括微控制器、汽车车身系统、工业控制系统以及无线网络和传感器)开发高性能低成本平台。

此处理器具有出色的计算性能以及对事件的优异系统响应能力,同时可应实际中对低动态和静态功率需求的挑战。

M4:由 ARM 专门开发的最新嵌入式处理器,用以满足需要有效且易于使用的控制和信号处理功能混合的数字信号控制市场。

M7:在 ARM Cortex-M 处理器系列中,Cortex-M7 的性能最为出色。

它拥有六级超标量流水线、灵活的系统和存接口(包括 AXI 和 AHB)、缓存(Cache)以及高度耦合存(TCM),为MCU 提供出色的整数、浮点和 DSP 性能。

互联:64位 AMBA4 AXI, AHB外设端口 (64MB 到 512MB)指令缓存:0 到 64kB,双路组相联,带有可选 ECC数据缓存:0 到 64kB,四路组相联,带有可选 ECC指令TCM:0 到 16MB,带有可选 ECC数据TCM:0 到 16MB,带有可选 ECCCortex-M系列规格对比Cortex-A系列:ARM Cortex-A 系列是一系列用于复杂操作系统和用户应用程序的应用程序处理器。

LPC开发板简介

LPC1700特性:

EM-LPC1768开发板:

EM-LPC1768硬件资源: :

LPC1768软件资源:

LPC2400简介:

LPC2400系列ARM一款具有极高集成度并且以ARM7TDMI-S为内核的 微控制器,支持支持实时仿真和嵌入式跟踪,处理器时钟高达72MHz。

片内集成:支持STN和TFT显示的LCD控制器、10/100M以太网媒体访问 控制器(MAC)、USB 2.0全速Device/Host/OTG控制器、4个UART,2路 CAN-bus、1个SPI接口、2个SSP接口、3个I2C CAN-bus 1 SPI 2 SSP 3 I C接口和1个I2S 1 I S接口。同时还带 有1个片内4MHz内部振荡器、98KB RAM以及1个支持异步静态存储器设备 和动态存储器的外部存储器控制器(EMC)。此外,还带有多个32位定时器、 ADC、DAC、PWM。

EM-LPC2400开发板(LPC2478)

LPC2478是NXP半导体公司针对各种高级通讯、高质 量图像显示等广泛应用场合而设计的一款具有极高集 成度并且以ARM7TDMI-S为内核的微控制器。 LPC2478微控制器具有512kB片内高速Flash存储器, 该Flash存储器具有特殊的128位宽度的存储器接口和 加速器架构,可使CPU以高达72MHz的系统时钟速度 来按顺序执行Flash存储器的指令。这种特点只有 LPC2000 ARM微控制器系列的产品才能提供。 LPC2478还带有实时调试接口,包括JTAG和嵌入式 跟踪在内,可以执行32位的ARM指令和16位的 THUMB指令。

LPC2478硬件资源 硬件资源

CPU:LPC2478(NXP),ARM7TDMI-S : , 512K内部 内部Flash 内部 98K的内部 的内部SRAM 的内部 128MB外部 外部NandFlash(K9F1G08) 外部 ( ) 32M的外部 的外部SDRAM 的外部 2MB的外部 的外部NorFlash 的外部 两个RS232接口,一个三线,一个五线 接口,一个三线, 两个 接口 USB2.0规范,带联接状态指示灯 一个 规范, 一个USB HOST 规范 带联接状态指示灯,一个 接口, 一个USB OTG接口。 接口 一个 接口。 接口 支持TFT(5:6:5)LCD接口,带Buffer芯片 接口, 支持 接口 芯片 (74HC244)驱动 ) 支持两路CAN总线 支持两路 总线 一个 SD/MMC卡接口 卡接口 采用音频解码芯片HT28V31,可直接播放音乐。 ,可直接播放音乐。 采用音频解码芯片 一个复位按键,并采用专用复位芯片进行复位, 一个复位按键,并采用专用复位芯片进行复位,稳 定可靠 一个20芯 - 标准JTAG接口,支持 接口, 一个 芯Multi-ICE标准 标准 接口 支持MDK等 等 调试 5V直流电源输入,带电源指示灯 也可 直流电源输入, 也可USB直接供 直流电源输入 带电源指示灯,也可 直接供 电 四个小按键,八个高亮 四个小按键,八个高亮LED93个I/O扩展插槽 个 扩展插槽 一个蜂鸣器 外部总线扩展槽, 外部总线扩展槽,电源和地线等 一个10M/100M网络接口 网络接口 一个

ARM Cortex系列

Cortex系列ARM核心及体系结构介绍作者:杨硕,华清远见嵌入式学院讲师。

众所周知,英国的ARM公司是嵌入式微处理器世界当中的佼佼者。

ARM一直以来都是自己研发微处理器内核架构,然后将这些架构的知识产权授权给各个芯片厂商,精简的CPU架构,高效的处理能力以及成功的商业模式让ARM公司获得了巨大的成功,使他迅速占据了32位嵌入式微处理器的大部分市场份额,甚至现在,ARM芯片在上网本市场的也大有与INTEL 的ATOM处理器一较高低的实力。

目前,随着对嵌入式系统的要求越来越高,作为其核心的嵌入式微处理器的综合性能也受到日益严峻的考验,最典型的例子就是伴随3G网络的推广,对手机的本地处理能力要求很高,现在一个高端的智能手机的处理能力几乎可以和几年前的笔记本电脑相当。

为了迎合市场的需求,ARM公司也在加紧研发他们最新的ARM架构,Cortex系列就是这样的产品。

在Cortex之前,ARM核都是以ARM为前缀命名的,从ARM1一直到ARM11,之后就是Cortex系列了。

Cortex在英语中有大脑皮层的意思,而大脑皮层正是人脑最核心的部分,估计ARM公司如此命名正有此含义吧。

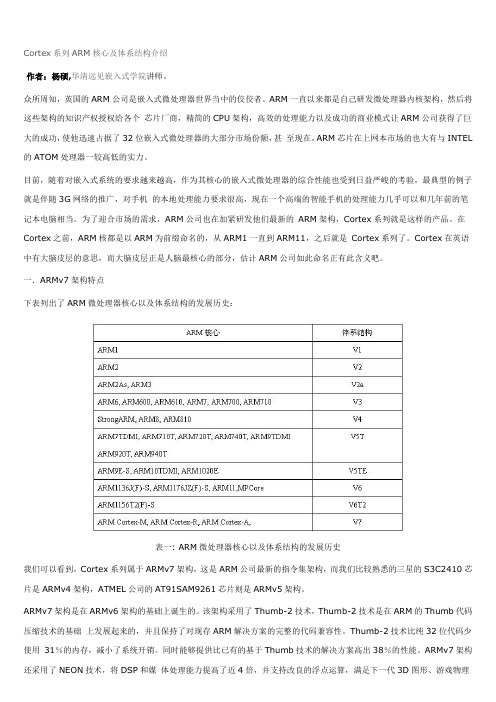

一.ARMv7架构特点下表列出了ARM微处理器核心以及体系结构的发展历史:表一: ARM微处理器核心以及体系结构的发展历史我们可以看到,Cortex系列属于ARMv7架构,这是ARM公司最新的指令集架构,而我们比较熟悉的三星的S3C2410芯片是ARMv4架构,ATMEL公司的AT91SAM9261芯片则是ARMv5架构。

ARMv7架构是在ARMv6架构的基础上诞生的。

该架构采用了Thumb-2技术,Thumb-2技术是在ARM的Thumb代码压缩技术的基础上发展起来的,并且保持了对现存ARM解决方案的完整的代码兼容性。

Thumb-2技术比纯32位代码少使用31%的内存,减小了系统开销。

同时能够提供比已有的基于Thumb技术的解决方案高出38%的性能。

关于ARM的内核架构介绍

张凌001关于ARM的内核架构很多时候我们都会对M0,M0+,M3,M4,M7,arm7,arm9,CORTEX-A系列,或者说AVR,51,PIC等,一头雾水,只知道是架构,不知道具体是什么,有哪些不同?今天查了些资料,来解解惑,不是很详细,但对此有个大体了解。

咱先来当下最火的ARM吧1.ARMARM即以英国ARM(Advanced RISC Machines)公司的内核芯片作为CPU,同时附加其他外围功能的嵌入式开发板,用以评估内核芯片的功能和研发各科技类企业的产品.ARM 微处理器目前包括下面几个系列,以及其它厂商基于 ARM 体系结构的处理器,除了具有ARM 体系结构的共同特点以外,每一个系列的 ARM 微处理器都有各自的特点和应用领域。

- ARM7 系列- ARM9 系列- ARM9E 系列- ARM10E 系列- ARM11系列- Cortex 系列- SecurCore 系列- OptimoDE Data Engines- Intel的Xscale- Intel的StrongARM ARM11系列2. Cortex 系列32位RISCCPU开发领域中不断取得突破,其设计的微处理器结构已经从v3发展到现在的v7。

Cortex 系列处理器是基于ARMv7架构的,分为Cortex-M、Cortex-R和Cortex-A三类。

由于应用领域的不同,基于v7架构的Cortex处理器系列所采用的技术也不相同。

基于v7A的称为“Cortex-A系列。

高性能的Cortex-A15、可伸缩的Cortex-A9、经过市场验证的Cortex-A8处理器以及高效的Cortex-A7和Cortex-A5处理器均共享同一体系结构,因此具有完整的应用兼容性,支持传统的ARM、Thumb指令集和新增的高性能紧凑型Thumb-2指令集。

1Cortex-M系列Cortex-M系列又可分为Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4;2Cortex-R系列Cortex-R系列分为Cortex-R4、Cortex-R5、Cortex-R7;3Cortex-A 系列Cortex-A系列分为Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A50等 ,同样也就有了对应内核的Cortex-M0开发板、Cortex-A5开发板、Cortex-A8开发板、Cortex-A9开发板、Cortex-R4开发板等等。

NXP LPC55S16 32位ARM MCU嵌入应用开发方案

NXP公司的LPC55S1x/LPC551x是基于32位ARM Cortex-M33内核的微处理器(MCU),包括CASPER加密引擎,多达256KB片上闪存,多达96KB片上SRAM,用于实时闪存加密/解密的PRINCE模块,代码看门狗,高速/全速USB主和设备接口,CANFD,五个通用计时器,一个SCTimer/PWM,一个RTC/告警计时器,一个24位多速率计时器(MRT),看门狗计时器(WWDT),九个灵活串行通信外设(可配置成USART, SPI,高速SPI, I2C或I2S接口),可编逻辑单元(PLU),一个16位2.0 MSPS ADC.ARM Cortex-M33核(r0p4)运行频率高达150MHz,集成了数字信号处理(DSP)指令,以及TrustZone®,浮点单元(FPU)和存储器保护单源(MPU),ARM Cortex M33内置了嵌套向量中断控制器(NVIC).为了支持所需的安全,LPC55S1x/LPC551x还支持安全引导, HASH, AES, RSA, UUID,动态加密和解密,调试认证和TBSA兼容.工作电压1.8V-3.6V,工作温度- 40 C 到 +105 C.主要用在工业,消费类电子和汽车市场等低功耗强功能的嵌入解决方案.本文介绍了LPC55S1x/LPC551x主要优势和特性,框图,以及开发板LPC55S16-EVK主要特性,电路图和材料清单.The LPC55S1x/LPC551xis an ARM Cortex-M33 based microcontroller for embedded applications. These devices include CASPER Crypto engine, up to 256 KB on-chip flash,up to 96 KB of on-chip SRAM, PRINCE module for on-the-fly flash encryption/decryption,Code Watchdog, high-speed/full-speed USB host and device interface with crystal-less operation for full-speed, CAN FD, five general-purpose timers, one SCTimer/PWM,one (WWDT), nine flexible serial communication peripherals (which can be configured as a USART, SPI, high speed SPI, I2C, or I2S interface)Programmable Logic Unit (PLU), one 16-bit 2.0 Msamples/sec ADCcapable of simultaneous conversions, comparator, and temperaturesensor .The ARM Cortex-M33 provides a security foundation, offering isolation to protect valuable IP and data with TrustZone® technology. It simplifies the design and software development of digital signal control systems with the integrated digital signal processing (DSP) instructions. To supportsecurity requirements, the LPC55S1x/LPC551x also offers support forsecure boot, HASH, AES, RSA, UUID, dynamic encrypt and decrypt, debug authentication, and TBSA compliance.LPC55S1x/LPC551x主要优势和特性:n ARM Cortex-M33 core (r0p4):u Running at a frequency of up to 150 MHz.u Integrated digital signal processing (DSP) instructions.u TrustZone®, Floating Point Unit (FPU) and Memory Protection Unit(MPU).u Non-maskable Interrupt (NMI) input with a selection of sources.u Serial Wire Debug with eight breakpoints and four watch points. Includes SerialWire Output for enhanced debug capabilities.u System tick timer.n CASPER Crypto co-processor is provided to enable hardware acceleration for various functions required for certain asymmetric cryptographicNXP LPC55S16 32位ARM MCU嵌入应用开发方案algorithms, such as, EllipticCurve Cryptography (ECC).n On-chip memory:u Up to 256 KB on-chip flash program memory with flash accelerator and 512 bytepage erase and write.u Up to 96 KB total SRAM consisting of 16 KB SRAM on Code Bus, 64 KBSRAM on System Bus (64 KB is contiguous), and additional 16 KB USBSRAM on SystemBus which can be used by the USB interface or for general purpose use.n PRINCE module for real-time encryption of data being written to on-chip flash and decryption of encrypted flash data during read to allow assetprotection, such assecuring application code, and enabling secure flashupdate.n On-chip ROM bootloader supports:u Booting of images from on-chip flashu Supports CRC32 image integrity checking.u Supports flash programming through In System Programming (ISP)commandsover following interfaces: USB0/1 interfaces using HID Classdevice, UARTinterface (Flexcomm 0) with auto baud, SPI slave interfaces(Flexcomm 3 or 8)using mode 3 (CPOL = 1 and CPHA = 1), and I2C slave interface (Flexcomm 1)u ROM API functions: Flash programming API, Power control API, andSecurefirmware update API using NXP Secure Boot file format, version 2.0 (SB2 files).u Supports booting of images from PRINCE encrypted flash regions.u Support NXP Debug Authentication Protocol version 1.0 (RSA-2048) and 1.1(RSA-4096).u Supports setting a sealed part to Fault Analysis mode throughDebugauthentication.n Secure Boot support:u Uses RSASSA-PKCS1-v1_5 signature of SHA256 digest ascryptographicsignature verification.u Supports RSA-2048 bit public keys (2048 bit modulus, 32-bit exponent). u Supports RSA-4096 bit public keys (4096 bit modulus, 32-bit exponent). u Uses x509 certificate format to validate image public keys.u Supports up to four revocable Root of Trust (RoT) or Certificate Authority keys,Root of Trust establishment by storing the SHA-256 hash digest of the hashes offour RoT public keys in protected flash region (PFR).u Supports anti-rollback feature using image key revocation and supports up to 16Image key certificates revocations using Serial Number field inx509 certificate.n Serial interfaces:u Flexcomm Interface contains up to nine serial peripherals (FlexcommInterface 0-7 andFlexcomm Interface 8). Each Flexcomm Interface (except flexcomm 8, whichis dedicated for high-speed SPI) can be selected bysoftware to be a USART, SPI,I2C, and I2S interface.Each Flexcomm Interface includes a FIFO that supportsUSART, SPI, and I2S.A variety of clocking options are available to each FlexcommInterface,including a shared fractional baud-rate generator, and time-outfeature.Flexcomm interfaces 0 to 5 each provide one channel pair of I2S andFlexcomm interfaces 6 to 7 each provide four channel pairs of I2S.u I2C-bus interfaces support Fast-mode and Fast-mode Plus with data rates of up to 1Mbit/s and with multiple address recognition and monitor mode. Two sets of trueI2C pads also support high-speed Mode (3.4 Mbit/s) as a slave.u USB 2.0 full speed host/device controller with on-chip PHY and dedicated DMA controller supporting crystal-less operation in device mode usingsoftware library example in technical note (TN00065).u USB 2.0 high-speed host/device controller with on-chip high-speed PHY. n Digital peripherals:u DMA0 controller with 23 channels and up to 22 programmable triggers, able toaccess all memories and DMA-capable peripherals.u DMA1 controller with 10 channels and up to 15 programmable triggers, able toaccess all memories and DMA-capable peripherals.u CAN FD module with dedicated DMA controlleru CRC engine block can calculate a CRC on supplied data using one ofthreestandard polynomials with DMA support.u Up to 64 General-Purpose Input/Output (GPIO) pins.u GPIO registers are located on the AHB for fast access. The DMA supports GPIOports.u Up to eight GPIOs can be selected as pin interrupts (PINT), triggered by rising,falling or both input edges.u Two GPIO grouped interrupts (GINT) enable an interrupt based on alogical(AND/OR) combination of input states.u I/O pin configuration with support for up to 16 function options.u Programmable Logic Unit (PLU) to create small combinatorial and/orsequentiallogic networks including state machines.n Security Features:u ARM TrustZone® enabled.u AES-256 encryption/decryption engine with keys fed directly from PUF or asoftware supplied keyu Secure Hash Algorithm (SHA2) module supports secure boot withdedicated DMA controller.u Physical Unclonable Function (PUF) using dedicated SRAM for siliconfingerprint. PUF can generate, store, and reconstruct key sizes from 64 to 4096 bits. Includeshardware for key extraction.u True Random Number Generator (TRNG).u 128 bit unique device serial number for identification (UUID).u Secure GPIO.u Code Watchdog for detecting code flow integrity.n Timers:u Five 32-bit standard general purpose asynchronous timers/counters,which support up to four capture inputs and four compare outputs, PWM mode, and externalcount input. Specific timer events can be selected to generate DMA requests.u One SCTimer/PWM with 8 input and 10 output functions (including 16 capture andmatch registers). Inputs and outputs can be routed to or from external pins andinternally to or from selected peripherals. Internally, the SCTimer/PWM supports 16captures/matches, 16 events, and 32 states.u 32-bit Real-time clock (RTC) with 1 s resolution running in the always-on powerdomain.Another timer in the RTC can be used for wake-up from all low powermodes including deep power-down, with 1 ms resolution. The RTC is clocked bythe 32 kHz FRO or 32.768 kHz external crystal.u Multiple-channel multi-rate 24-bit timer (MRT) for repetitive interrupt generation atup to four programmable, fixed rates.u Windowed Watchdog Timer (WWDT) with FRO 1 MHz as clock source. u Code Watchdog for detecting code flow integrity.u The Micro-Tick Timer running from the watchdog oscillator can be used to wake-up the device from sleep and deep-sleep modes. Includes 4capture registers with pininputs.u 42-bit free running OS Timer as continuous time-base for the system,available in any reduced power modes.It runs on 32 kHz clock source, allowing a count periodof more than 4 years. n Analog peripherals:u 16-bit ADC with five differential channel pair (or 10 single-endedchannels), andwith multiple internal and external trigger inputs and sample rates of up to 2.0MSamples/sec. The ADC support simultaneousconversions, on 2 ADC inputchannels belonging to a differential pair.u Integrated temperature sensor connected to the ADC.u Comparator with five input pins and external or internal referencevoltage.n Clock generation:u Internal Free Running Oscillator (FRO). This oscillator provides aselectable 96MHz output, and a 12 MHz output (divided down from theselected higherfrequency) that can be used as a system clock. The FRO is trimmed to +/- 2%accuracy over the entire voltage and temperature range. u 32 kHz Internal Free Running Oscillator FRO. The FRO is trimmed to +/- 2%accuracy over the entire voltage and temperature range.u Internal low power oscillator (FRO 1 MHz) trimmed to +/- 15% accuracy over theentire voltage and temperature range.u Crystal oscillator with an operating frequency of 12 MHz to 32 MHz.Option forexternal clock input (bypass mode) for clock frequencies of up to 25 MHz.u Crystal oscillator with 32.768 kHz operating frequency.u PLL0 and PLL1 allows CPU operation up to the maximum CPU rate without theneed for a high-frequency external clock. PLL0 and PLL1 can run from the internalFRO 12 MHz output, the external oscillator, internal FRO 1 MHz output, or the32.768 kHz RTC oscillator.u Clock output function with divider to monitor internal clocks.u Frequency measurement unit for measuring the frequency of any on-chip oroff-chip clock signal.u Each crystal oscillator has one embedded capacitor bank, where each canbe usedas an integrated load capacitor for the crystal oscillators. Using APIs, the capacitorbanks on each crystal pin can tune the frequency for crystals with a CapacitiveLoad (CL) leading to conserving board space and reducing costs.n Power-saving modes and wake-up:u Integrated PMU (Power Management Unit) to minimize power consumption.u Reduced power modes: Sleep, deep-sleep with RAM retention, power-down with RAM retention and CPU retention, and deep power-down with RAM retention.u Configurable wake-up options from peripherals interrupts.u The Micro-Tick Timer running from the watchdog oscillator, and the Real-TimeClock (RTC) running from the 32.768 kHz clock, can be used to wake-up thedevice from sleep and deep-sleep modes.u Power-On Reset (POR) (around 0.8 V).u Brown-Out Detectors (BOD) for VBAT_DCDC with separate thresholds for forcedreset.n Operating from internal DC-DC converter.n Single power supply 1.8 V to 3.6 V.n JTAG boundary scan supported.n Operating temperature range - 40 C to +105 C.n Available in HLQFP100, VFBGA98, and HTQFP64 packages。

NXP mcu

TinyM0核心板电路为LPC111x芯片的最小系统,硬件支持2.54mm间距的 标准排针。用户可以将TinyM0核心板配套自行设计的底板进行产品开发。 ● 支持多款芯片

和16位竞争产品的2至4倍。

Cortex-M0内核

● 32位ARM RISC处理器,16位Thumb指令集; ● 功耗与面积高度优化,设计专用于低成本、低功耗场合; ● 24位SysTick定时器; ● 32位硬件乘法器; ● 中断现场自动保存,有处理决定性、固定延迟的中断能力; ● 系统接口支持小端或字节不变的大端数据访问; ● SWD串行线调试。

LPC1300选型表:

器件型号 LPC1343 LPC1342 LPC1313 LPC1311

Flash (KB) 32 16 32 8

SRAM(KB) 8 4 8 2

USB 2.0 Device Device

-

I2C(Fast+) 1 1 1 1

ADC 8ch/10bit 8ch/10bit 8ch/10bit 8ch/10bit

置的新型开漏工作模式

LPC1100

◎ 四个通用计数器/计数器 ◎ 可编程的看门狗定时器(WDT),带锁死功能 ◎ 系统计时器 ◎ 各外设自带时钟分频器,有利于降低功耗

芯片特色:

Cortex-M0处理器性能 ● Cortex-M0微控制器可以轻松超越高端8位和16位器件的

性能水平; ● 内核额定性能为0.9DMIPS/MHz,相当于与其最接近的8位

NXP平台介绍

1. LPCXpresso-CN-LPC1114处理器内核Cortex-M0/M0+内核,运行速度高达50MHz带有SWD 调试功能、支持JTAG 调试功能(仅LPC11U00 系列)支持边界扫描(仅LPC11U00 系列)支持非屏蔽(NMI)中断(仅LPC11U00 和LPC1100XL 系列)内置嵌套向量中断控制器(NVIC)系统节拍定时器片内存储器最高配合256KB 片内Flash 程序存储器支持256 字节页擦除(仅LPC1100XL/LPC11U3X/LPC11U6X 系列)最高配置36KB 片内SRAM;最高配置4KB 片内EEPROM(仅LPC11E00 系列)(仅LPC11E00 和LPC11U00 系列)可通过片内引导装载程序软件来实现在系统编程(ISP)和在应用编程(IAP)可选择通过CAN(仅LPC11C00 系列)、USB Device(仅LPC11U00 系列)或UART 接口进行Flash ISP 编程串行接口包括:USB 2.0 全速接口,集成片上PHY(仅LPC11U00 系列)CAN 控制器(LPC11C12/C14/C22/C24 支持),内部ROM 集成供CAN 和CANOpen 标准使用的初始化和通信的API 函数,用户可直接调用;兼容CAN2.0A/B,传输速率高达1Mbit/s;支持32 个消息对象,且每个消息对象有自己的掩码标识;提供可屏蔽中断、可编程FIFO 模式集成片上高速CAN 收发器(仅LPC11C22/C24 支持)UART,可产生小数波特率,具有调制解调器、内部FIFO,支持RS-485/EIA-485 标准,支持ISO7816-3 智能卡接口及IrDA(仅LPC11U00 系列)SSP 控制器,带FIFO 和多协议功能I2C 总线接口,完全支持I2C 总线规范和快速模式,数据速率为1Mbit/s,具有多个地址识别功能和监控模式数字外设:多达80 个通用I/O(GPIO)引脚,带可配置的上拉/下拉电阻,LPC11U00 系列还可配置为中继模式和开漏模式每个GPIO 口均可配作边沿或电平中断(LPC11U00 可选择所有GPIO 中的8 个,每个GPIO中断占用独立NVIC 通道)1 个引脚(P0.7)支持20mA 的高驱动电流I2C 总线引脚在FM+模式下可支持20mA 的灌电流4 个通用定时器/计数器,共有4 路捕获输入和13 路匹配输出2 个状态可配置定时器SCT(仅LPC11U6x 系列支持)可编程的看门狗定时器(WDT)(LPC11U00 为带窗看门狗WWDT)4×40 段LCD 驱动(仅LPC11D14 支持)模拟外设:8 通道10 位ADC1 个多达12 通道输入的12 位ADC,支持多个内部和外部触发输入,支持2 个独立转换序列,最大采样率为2MBit/s(仅LPC11U6x 系列支持)内置温度传感器(仅LPC11U6x/LPC11A00 系列支持)时钟产生单元:12MHz 内部RC 振荡器可调节到+1%精度,并可将其选择为系统时钟PLL 允许CPU 在最大CPU 速率下操作,而无需高频晶振,可从主振荡器、内部RC 振荡器运行第二个专用PLL 用于USB 接口(仅LPC11U00 系列)时钟输出功能可以反映主振荡器时钟、IRC 时钟、CPU 时钟和看门狗时钟片内32KHz 的振荡器(仅LPC11U6x 系列支持)电源与功率控制:具有三种低功耗模式:睡眠模式、深度睡眠模式和深度掉电模式(LPC11E00/LPC11U00 系列为四种,增加掉电模式)集成了PMU(电源管理单元),可在睡眠、深度睡眠、掉电(仅LPC11E00/LPC11U00 系列)和深度掉电模式中极大限度地减少功耗片内固化功耗管理文件,通过简单调用就能降低功耗(仅LPC1100L、LPC1100XL、LPC11E00 和LPC11U00 系列)13 个拥有专用中断的GPIO 可将CPU 从深度睡眠模式中唤醒(LPC11E00 系列可通过复位、WDT 中断、BOD 中断唤醒,LPC11U00 系列还可通过USB 活动唤醒)上电复位(POR)掉电检测,具有4 个独立的阀值,用于中断和强制复位3.3V 单电源供电(1.8V~3.6V)封装:采用SO20、TSSOP20、TSSOP28、DIP28、HQFN33 (5 mm x 5 mm)、HQFN33 (7 mm x 7 mm)、LQFP100、LQFP64、LQFP48、PLCC44、HVQFN24、HVQFN32、HVQFN33、TFBGA 或WL-CSP(晶片级)封装参阅/products/microcontrollers/cortex_m0_m0/series/LPC1100XL.html/zh-hans/content/device/lpc11xx2. LPCXpresso-CN-LPC1227处理器内核ARM Cortex-M0 内核,运行速度高达45MHz内置嵌套向量中断控制器(NVIC)SWD 调试接口系统节拍定时器片内存储器高达8kB SRAM高达128kB 片内Flash 存储器可通过片内引导装载程序软件实现在系统编程(ISP)和在应用编程(IAP)功能数字外设21 通道Micro DMA 控制器硬件CRC 计算及校验模块两个带有小数波特率发生器和内部FIFO 的UART。

NXP推出新型120MHzARMCortex—M3微控制器

合 物 电池 、 B端 口或 其 他 2 7 ~ 5 5V 的 电流 受 限 电 US . .

源 , 两 节 串联 的 超 级 电容 器 充 电至 可 编程 的输 出 电压 。 将

L C 45具有 两 种 运 行 模 式 : 电 电 流 曲线 ( 型 ) T 42 充 典

应 用 中实 现 微控 制 器 控 制 与 信 号 处理 的集 成 已成 为 现 实 ,

Rvr o i r . 。这些 工 具 可 帮 助 包 括 汽车 电子 、 业 ie C mpl 8 e5 工 控制、 网络 通 信 等市 场 在 内 的各行 业缩 短 设 备 软 件 开 发 周

命 ;0位 A C UA T、 1 D 、 R 比较 器 与 串 行 通 信 等 集 成 型 智 能 外 设 可将 C U 解放 出来 , 面 提 高 电源 效 率 。 P 全

风 河嵌 入 式 软件 开 发 工 具套 件 全 面 升级

I tl 资 子公 司 风 河 系统 公 司 ( id Rie ) 出 其 ne全 W n v r推

的初 始 化 时 间及 运 行 时 间 。

意 法半 导 体 推 出双 接 口 E P M E RO

意 法 半 导 体 宣 布 全 新 射 频 EE ROM 芯 片 系 列 的首 P 款产 品 M2 L 4样 片 正 式 上 市 。M2 L 4是 一 款 内 置 4 R6 4 R6

标 准 Ic串 V 的 E P O 存 储 器 , 与 大 多 数 微 控 制 器 1 ER M 可 或 A I 片 通 信 ; 提 供 一 个 IO 5 9 标 准 的 R ( SC芯 还 S 163 F 射 频) 口, 接 可与 R I 阅读 器 进 行 无 线 通 信 。I0 5 9 是 FD S 163

LPC1758系统硬件说明书

动-CTS/RTS) 6. 支持 RS-485/9-bit/EIA-485 模式 7. UART3 包括 IrDA 模式,支持红外通信 8. 所有 UART 口支持 DMA 9. 4 个 UART 口 SPI 串行 I/O 控制器 1. 1 个 SPI 控制器 2. SPI 最大数据比特率 12.5Mbit/s 3. 遵行 SPI 接口规范 4. 同步、串行、全双工通信 5. 最大数据比特率的八分之一为输入时钟率 6. 每次传输 8 位至 16 位 SSP 串行 I/O 控制器 1. 2 个 SSP 控制器 2. 最大主 SSP 最大速率:50Mbit/s,从 SSP 最大速率:8Mbit/s

2

LPC1758 最小系统硬件使用说明书

7. 支持 DMA UARTs

1. 最大 UART 数据比特率 6.25Mbit/s 2. 16Byte 接受、传输 FIFO 3. 接受 FIFO 触发点 1Byte、4Byte、8Byte、14Byte 4. 内置分数波特率发生器,蕴含范围广泛的传输速率,不需要外部

26 P1[19]/MCOA0/USB_PPWR/CAP1[1]

通用 IO 口/电机 0 控制输出通道 A/USB 口使能端/时钟 1 的输入通道 1

27 P1[20]/MCI0/PWM1[2]/SCK0

通用 IO 口/电机 0 控制输入/频率脉宽调制 1,通道 2/为 SSP0 提供连续时钟

含义 JTAG 测试输出/连续线跟踪输出 JTAG 测试输入 JTAG 测试模式选择/连续线跟踪输入/出 JTAG 测试复位 JTAG 口测试时钟/连续时钟 通用 IO 口/模数转换第 3 位/数模转换输出/串口 3 接收端 通用 IO 口/模数转换第 2 位/I2S 数据接收/串口 3 发送端 模拟电源 模拟地 正参考电压 复位输出 负参考电压 实时时钟 复位

arm内核全解析_arm内核体系结构分类介绍

arm内核全解析_arm内核体系结构分类介绍ARM处理器是英国Acor n有限公司设计的低功耗成本的第一款RISC微处理器。

全称为Ad vanced RISC Machine。

ARM处理器本身是32位设计,但也配备16位指令集,一般来讲比等价32位代码节省达35%,却能保留32位系统的所有优势。

ARM内核特点ARM处理器为RISC芯片,其简单的结构使ARM内核非常小,这使得器件的功耗也非常低。

它具有经典RISC的特点:* 大的、统一的寄存器文件;* 简单的寻址模式;* 统一和固定长度的指令域,3地址指令格式,简化了指令的译码。

编译开销大,尽可能优化,采用三地址指令格式、较多寄存器和对称的指令格式便于生成优化代码;* 单周期操作,ARM指令系统中的指令只需要执行简单的和基本的操作,因此其执行过程在一个机器周期内完成;* 固定的32位长度指令,指令格式固定为32位长度,这样使指令译码结构简单,效率提高;* 采用指令流水线技术。

ARM内核体系结构ARM架构自诞生至今,已经发生了很大的演变,至今已定义了7种不同的版本:V1版架构:该架构只在原型机ARM1出现过,其基本性能包括基本的数据处理指令(无乘法)、字节、半字和字的Load/Store指令、转移指令,包括子程序调用及链接指令、软件中断指令、寻址空间64MB。

V2版架构:该版架构对V1版进行了扩展,如ARM2与ARM3(V2a版)架构,增加的功能包括乘法和乘加指令、支持协处理器操作指令、快速中断模式、SWP/SWPB的最基本存储器与寄存器交换指令、寻址空间64MB。

V3版架构:该版对ARM体系结构作了较大的改动,把寻址空间增至32位(4G B),增加了当前程序状态寄存器CPSR和程序状态保存寄存器 SPSR以便于异常处理。

增加了中止和未定义2种处理器模式。

ARM6就采用该版结构。

指令集变化包括增加了M RS/MSR指令,以访问新增的CPSR /SPSR寄存器、增加了从异常处理返回的指令功能。

典型MCU架构详解与主流MCU介绍

典型MCU架构详解与主流MCU介绍在前面的介绍中,我们已经了解到MCU就是基于一定的内核体系,集成了存储、并行或串行I/O、定时器、中断系统以及其他控制功能的微型计算机系统,如图4.1是典型的MCU组成框图。

目前,虽然很多厂商采用了ARM内核体系,但是在具体的MCU产品上,各个公司集成的功能差异非常大,形成MCU百花齐放的格局,由于本书的重点是介绍32位MCU,所以我们将重点以恩智浦公司的MCU为例来介绍,这些MCU中,LPC3000、LH7A采用ARM9内核,LPC2000和LH7采用ARM7内核,LPC1000系列采用Cortex-M3或M0内核,通过这几个系列的介绍可以了解MCU的构成和差异。

4.1 恩智浦LPC1000系列MCULPC1000系列MCU是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

LPC1000系列MCU又分为LPC1700系列和LPC1300系列,下面我们分开介绍。

4.1.1 LPC1700系列MCU介绍LPC1700系列ARM是以第二代的Cortex-M3为内核,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。

其操作频率高达100MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的高性能的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元。

LPC1700系列ARM Cortex-M3的外设组件:最高配置包括512KB片内Flash程序存储器、64KB片内SRAM、8通道GPDMA控制器、4个32位通用定时器、一个8通道12位ADC、一个10位DAC、一路电机控制PWM输出、一个正交编码器接口、6路通用PWM 输出、一个看门狗定时器以及一个独立供电的超低功耗RTC。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ISR2

POP

14

Wake-Up Interrupt Controller (WIC)

Not available prior to Revision 2 Cortex-M3 core Allows “automatic” wake-up while clocks are stopped

– Works in all power-down modes – Does not require separate enable for wake-up and interrupt

100 Throughput

8/16-bit

10

8-bit LPC900(/01) 2-Clock LPC700 6-Clock

16-bit XA

1

C51X2 6-Clock

Memory Size 2 KB 64 KB 1 MB >16 MB

2

NXP ARM-based 32-bit Microcontroller Portfolio

/products/CPUs/ARM_Cortex-M3.html

9

Cortex-M3特点

– – – – – – – – 高性能 – 1.25 DMIPS/MHz 统一的Thumb-2指令集 简单的编程模型,100% C代码 低延迟中断响应 先进的低功耗模式 全面的调试和跟踪功能 灵活的内存保护单元 (MPU) 广泛的生态系统和工具支持

Choice of ARM cores •Match performance to application Common core platform •Common tool chain •Code reuse •Common IP •Easy migration •Lower learning curve

7

What is Cortex-M3 Core?

‣ ‣ ‣ ‣ ‣ ‣ ‣ ‣ ‣

Harvard architecture with separate local instruction and data buses 3-stage pipeline with limited branch prediction Thumb-2® instructions ALU with support for H/W divide and single cycle multiply Built-in Nested Vectored Interrupt Controller (NVIC) with Wakeup interrupt controller (WIC) Automatic state save and restore for interrupts Advanced debug components Integrated low power modes Memory Protection Unit (MPU)

12

Cortex-M3 Interrupts

Nested Vector Interrupt Controller (NVIC)

Cortex Interrupts have Low Latency

– 12 cycles vs. 24-42 cycles on ARM7TDMI

Processor state automatically saved and restored

– Large subset of 32-bit ARM instructions – Backwards compatible to 16-bit Thumb® instruction set

Includes 12 new instructions:

– Bit field, Table branch, If/Then, Multiply, Divide, etc.

13

NVIC Latency Details

12-cycle interrupt latency

– 6-cycle register push (R0-R3, R12, LR, PC, xPSR) – 6-cycle interrupt address fetch

PUSH FETCH

ISR

POP

Pre-Emption

Hardware Divider

– Instruction takes from 2 - 12 cycles depending on dividend and divisor – Instruction is interruptible – The hardware divider is the main reason the Dhrystone MIPs are higher than ARM7

NXP Microcontrollers Introduction

NXP Semiconductors 2010

NXP Microcontroller Products & Cores

16/32-bit ARM ARM926EJ, ARM922T-S (LPC3000, LH7A4xx) ARM968E-S (LPC2900) ARM720T (LH795xx) ARM7TDMI-S (LPC2000, LH754xx) ARM Cortex-M3 (LPC1700) ARM Cortex-M0 (LPC1100) 51MX 6-Clock 80C51 12-Clock

4 8

ARM7TDMI vs. Cortex-M3

FEATURES Architecture ISA Support Pipeline Interrupts Inter-Interrupt Latency Sleep Modes Memory Protection Dhrystone ARM7TDMI ARMv4T (von Neumann) Thumb®/ARM 3-stage FIQ/IRQ 24 – 42 cycles None None 0.95 DMIPS/MHz (ARM) 0.74 DMIPS/MHz (Thumb®) Power Consumption Area 0.28 mW/MHz 0.62 mm2 (core only) 0.19 mW/MHz 0.86 mm2 (core + peripherals) ARM Cortex M3 ARMv7-M (Harvard) Thumb-2® 3-stage + branch speculation NMI + 1 to 240 physical interrupts 12 cycles Integrated 8 region MPU 1.25 DMIPS/MHz

– High priority ISR runs before completion of low priority ISR

PUSH ISR1 POP PUSH ISR1 ISR2 POP

Tail-Chaining

– Consecutive ISRs skip POP and PUSH

PUSH ISR1

SC100™

低成本

6

ARM Cortex-M Processors

Cortex-M family optimised for deeply embedded

– Microcontroller and low-power applications

ARM Cortex-A Series:

Applications processors for feature-rich OS and user applications

Memory footprint similar to Thumb® but with performance similar to ARM

11

Math performance of Cortex-M3

Single Cycle Multiply

Calculation 16b x 16b 32b x 16b 32b x 32b 32b x 32b Result 32b 32b 32b 64b Clock Cycles 1 1 1 3-7*

Eliminates the need to periodically wake-up the controller and poll the interrupts

– Saves power

When the CPU enters power-down, sleep, or deep sleep modes by executing the WFI (Wait For Interrupt) instruction, the NVIC sends a mask of the current interrupt situation to the WIC This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately

– Dynamic reprioritization of interrupts

Interrupts set to the same priority level have a default hardware priority level Cortex replaces the FIQ on the ARM7TDMI with an NMI interrupt

Relative DMIPS/MHz

ARM7 (ARM) Cortex-M3

Relative Code Size

8051

ARM7 (ARM) Cortex-M3

10

Thumb-2® mode

A new ARM instruction set that mixes 16 & 32-bit instructions