数电第五章

合集下载

数字电子技术基础 ppt 课件5精选全文

解:

由于在异步时序逻辑电路中,没有统一的时钟脉冲,因此,分析时必须写出时钟方程。

(1)写各时钟方程

CP0=CP(时钟脉冲源的上升沿触发) CP1=Q0(当FF0的Q0由0→1时,Q1才可能改变状态,否则Q1将保持原状态不变)

(2)写输出方程

(3)写各触发器的驱动方程

(4)写各触发器的次态方程

1、移位电路组成

(从Q3 向Q0移)

Q0端是串行输出端;

DIL是左移数据输入端;1DFra bibliotekC1FFD

Q3

1D

C1

FFC

Q2

1D

C1

FFB

Q1

1D

C1

FFA

Q0

CP

DIL

Q0Q1Q2Q3 端是并行输出端。

2、工作过程

例如:要移入D0D1D2D3

移状态表

Q0 Q1 Q2 Q3 DIL CP顺序

X X X D0

存入: 1 0 0 1

2、工作原理

存数指令

CP

Q0

Q1

Q2

Q3

D0

D1

D2

D3

1D

R

1D

R

1D

R

1D

R

RD

若输入信号 、 、 、 已被送到相应触发器的D端,当CP脉冲来到时,四个触发器的输出端 的电平分别等于端 、 、 、 的电平,这时输入信号就被寄存起来了。只要没有新的输入信号,触发器的状态就不会改变,也就是说,输入信号在寄存器中一直保持到下一个输入信号到达时为止。

K3 = Q2

=(Q3+Q2 ) Q1

Q3

Q2

Q1

Y

CP

数电第五章

E

触发器---对脉冲边沿敏感的存储电路 敏感的存储电路, 触发器 对脉冲边沿敏感的存储电路,在时钟脉冲的 上升沿或下降沿的变化瞬间改变状态。 上升沿或下降沿的变化瞬间改变状态。 CP CP

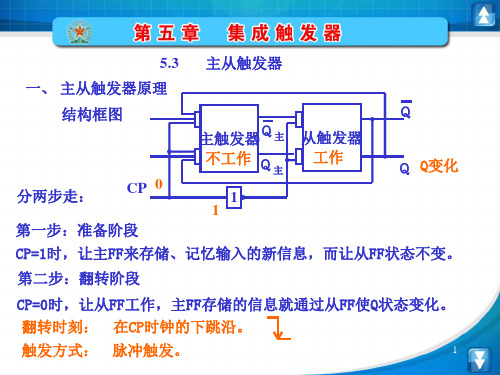

5 锁存器和触发器

5.1 双稳态存储单元电路 5.2 锁存器 5.3 触发器的电路结构和工作原理 5.4 触发器的逻辑功能

L*和H*表示门控电平 由高变低之前瞬间 和 表示门控电平 表示门控电平LE由高变低之前瞬间 Dn的逻辑电平。 的逻辑电平。

END}

5.3 触发器的电路结构和工作原理

锁存器---对脉冲电平敏感的存储电路 敏感的存储电路, 锁存器 对脉冲电平敏感的存储电路,在特定输入脉 冲电平作用下改变状态。 冲电平作用下改变状态。 E

R G4 1 & Q4 G2 ≥1

Q

0 1

E & S G3

Q3

状态发生变化。 状态发生变化。 S=0,R=0:Qn+1=Qn , : S=1,R=0:Qn+1=1 , : S=0,R=1:Qn+1=0 , : S=1,R=1:Qn+1= Ф , :

≥1

Q

1

G1

画波形

E R S Q Q

不 变

置 不 1 变

≥1

S 1 0 0 1

Q 1 0

Q 0(置位 置位) 置位 1(复位 复位)

0

Q

≥1

0

0 1 0

保持原状 不确定

1 R S

1

1

触发器的输出既不是0态,也不是1态,不 触发器的输出既不是 态 也不是 态

符合逻辑关系

R Q

≥1

S 1 0 0 1

Q 1 0

Q 0(置位 置位) 置位 1(复位 复位)

触发器---对脉冲边沿敏感的存储电路 敏感的存储电路, 触发器 对脉冲边沿敏感的存储电路,在时钟脉冲的 上升沿或下降沿的变化瞬间改变状态。 上升沿或下降沿的变化瞬间改变状态。 CP CP

5 锁存器和触发器

5.1 双稳态存储单元电路 5.2 锁存器 5.3 触发器的电路结构和工作原理 5.4 触发器的逻辑功能

L*和H*表示门控电平 由高变低之前瞬间 和 表示门控电平 表示门控电平LE由高变低之前瞬间 Dn的逻辑电平。 的逻辑电平。

END}

5.3 触发器的电路结构和工作原理

锁存器---对脉冲电平敏感的存储电路 敏感的存储电路, 锁存器 对脉冲电平敏感的存储电路,在特定输入脉 冲电平作用下改变状态。 冲电平作用下改变状态。 E

R G4 1 & Q4 G2 ≥1

Q

0 1

E & S G3

Q3

状态发生变化。 状态发生变化。 S=0,R=0:Qn+1=Qn , : S=1,R=0:Qn+1=1 , : S=0,R=1:Qn+1=0 , : S=1,R=1:Qn+1= Ф , :

≥1

Q

1

G1

画波形

E R S Q Q

不 变

置 不 1 变

≥1

S 1 0 0 1

Q 1 0

Q 0(置位 置位) 置位 1(复位 复位)

0

Q

≥1

0

0 1 0

保持原状 不确定

1 R S

1

1

触发器的输出既不是0态,也不是1态,不 触发器的输出既不是 态 也不是 态

符合逻辑关系

R Q

≥1

S 1 0 0 1

Q 1 0

Q 0(置位 置位) 置位 1(复位 复位)

数电第5章

第五章 触 发 器

图 5 – 7 由与非门构成的基本RS触发器

第五章 触 发 器

1. 功能描述 (1) 当Rd=1, Sd=0时,不管触发器原来处于什么状态, 其次态一定为“1”,即Qn+1=1,故触发器处于置位状态。 (2) 当Rd=0, Sd=1时,Qn+1=0,触发器处于复位状态。 (3) 当Rd=Sd=1 时,触发器状态不变,处于维持状态, 即Qn+1=Qn。 (4) 当Rd=Sd=0 时,Qn+1=Q n+1=1,破坏了触发器的正常 工作,使触发器失效。而且当输入条件同时消失时,触发 器是“0”态还是“1”态是不定的,这种情况在触发器工作 时是不允许出现的。因此使用这种触发器时, 禁止 Rd=Sd=0出现。

发生的。这种电路中没有统一的时钟脉冲。任何输入信

号的变化都可能立刻引起异步时序电路状态的变依从关系来分,又可分为米里 (Mealy)型和莫尔(Moore)型两类。米里型电路的输出是输 入变量及现态的函数,即

F (t ) f [ x(t ),Qn (t )]

器和JK触发器。在基本RS触发器的基础上, 加两个与非

门即可构成钟控RS触发器, 如图 5-10 所示。

第五章 触 发 器

图 5 – 10 钟控RS触发器

第五章 触 发 器

1. 功能描述 当CP=0时,触发器不工作,此时C、D门输出均为 1, 基本RS触发器处于保持态。此时无论R、S如何变化,均 不会改变C、D门的输出,故对状态无影响。 当CP=1 时,触发器工作,其逻辑功能如下: R=0, S=1, Qn+1=1,触发器置“1”; R=1, S=0, Q n+1=0,触发器置“0”; R=S=0, Qn+1=Qn,触发器状态不变; R=S=1, 触发器失效,工作时不允许。

数字电子技术基础第5章-时序逻辑电路

图5.1.4 同步时序电路与异步时序电路

5.1 时序电路的基本概念

2.米莱电路与摩尔电路

有的时序电路的输出不 仅与存储电路输出的原状态 有关,而且和电路的输入信 号有关。而另一些时序电路 仅与存储电路输出的原状态 有关。前者称为米莱型 (Mealy)电路,后者称为 摩尔型(Moore)电路。

5.1 时序电路的基本概念

(5)根据状态转换表可以绘出状态转换图或时序图。 (6)据上述分析步骤,用文字描述时序电路的逻辑功能。

5.2 基于触发器的时序电路分析

5.2.2 同步时序电路的分析举例

1.摩尔型同步时序电路的分析

例5.2.1试分析图5.2.1所示时序电路的逻辑功能,并说明 电路性质(同步或异步、摩尔或米莱、能否自启动)。

(4)每经过6个时钟脉冲信号的作用,电路状态循环一次。 当计数到101时,F作为输出进位1次。该电路是具有自启动功能 的摩尔型同步6进制计数器。

图5.2.2 例5.2.1状态转换图

图5.2.3 例5.2.1 时序波形图

5.2 基于触发器的时序电路分析

2.米莱型同步时序电路的分析 例5.2.3 图5.2.6电路是由T触发器构成的时序电路,试分析电路功能。

图5.1.1所示框图是时序电 路的基本结构,由组合电路和 存储电路两部分组成。图5.1.1 时序逻辑电路结构从图的整体 上看,组合电路部分的功能是 进行逻辑运算和算术运算,存 储电路部分是由触发器或锁存 器“组”构成,起到记忆运算 功能。

图5.1.1 时序逻辑电路

5.1 时序电路的基本概念

5.1.2 状态转换表与状态转换图

(2)根据输出方程可以确定是摩尔型电路,还是米莱型 电路。

(3)将每个触发器的激励方程代入对应触发器的特征方 程,求出各触发器的状态方程,状态方程反映各触发器输出 的现态与次态的逻辑关系。

数电第五章

D 1D E E1

E

Q

D Q

Q

Q

可见,D锁存器存在“空翻 ”现象。

3. 锁存器的动态特性

ቤተ መጻሕፍቲ ባይዱ

D

tSU

tH

C D TG TG

G1

1

Q

E

tW

tpLH

1C C

TG C

tpHL

TG

2

1

Q

Q

G2

建立时间tSU :表示D信号对E下降沿的最少时间提前量。

脉冲宽度tW :为保证D信号正确传送到Q和 Q

保持时间tH :确保数据的可靠锁存的最少时间。 延迟时间tpLH:输出从低电平到高电平的延迟时间;

1 G1

R

≥1

G2 ≥1 S

1

0

10

Q

当S、R 同时回到0时,由于两个与非

门的延迟时间无法确定,使得触发器 最终稳定状态也不能确定。

Q

0

约束条件: SR = 0

2)逻辑符号与逻辑功能

逻辑功能表

SR

Qn

Q n1

00

0

00

1

01

0

01

1

0

不变

1

0 置0

0

10

0

1

置1

10

1

1

11

0

不确定 不确定

11

1

不确定

延迟时间tpHL:高电平到低电平的延迟时间。

4. 典型集成电路

CMOS八D锁存器- 74HC/HCT373

传输门控 D 锁存器

传输门控 制D0

D1

…

D7

1

1

…1

1D

数字电子技术 第5章

锁存器电路图

(1)

E CP 1D 1

(11) 1

C1

(3)

1D Q

C1

EN

(2) 1Q

1

EN

(4) 2D

1D C1 Q

(5) 2 Q

1

EN

(6)

D

3Q

1

& ≥1 Q

(7) 3D

19) 4 Q

1D C1

Q

1

& ≥1

(12)

Q

5Q

EN

5D

(13)

1D C1 Q

1

CP

图5-13 一位D锁存器逻辑图

EN

(15)

6D

(14)

6Q

1D C1

Q

1

EN

(16)

7D

(17)

1D C1

Q

1

7Q

EN

8D

(18)

(19)

1D

Q

1

8Q

(3)移位寄存器

移位寄存器不仅可以存储代码,还可以将代码移位。 ⑴四位右移移位寄存器的原理:

并行输出

Q0 DI FF0 1D Q C1 CP FF1 1D Q1 FF2 1D Q C1 Q2 FF3 1D C1 Q Q3 DO

表5-4 74194的工作状态表

Rd

0 1 1 1 1

S1 S0 × 0 0 1 1 × 0 1 0 1

工作状态 清零 保持 右移 左移 送数

CP A

& & & & & & &

1

并行输出

FA QA Q 1 FB QB Q 1 1S C1 1R R FC Q C Q 1 FD QD Q 1S C1 1R R

74161的逻辑符号

数字电子技术第5章

(4)逻辑功能分析:当Q1Q0=11时,输出Z=1;当取 其它值时,输出Z=0;在一个循环过程中,Z=1只出现一次, 故为进位输出信号。所以,此电路是带进位输出的同步4 进制加法计数器电路。

EXIT EXIT

第5章 时序逻辑电路

分析举例

【例5.1.2】图所示电路是异步时序逻辑电路的逻辑图, 试分析它的逻辑功能。

3. 求出对应状态值

设电路初始状态为 Q3Q2Q1 Q0 =0000 当某触发器时钟 条件满足时,计算 其状态方程的值; 触发器时钟没有到 来时,则不用计算 其状态方程的值, 保持原有状态。

演 示 文 稿 Presentation

0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1

EXIT EXIT

第5章 时序逻辑电路

画状态图和时序图

演 示 文 稿 Presentation

随着CP脉冲的递 1010至1111在 增,不论从电路输 计数循环外, 出的哪一个状态开 但可以进入计 始,触发器输出的 数循环,称为 变化都会进入同一 自启动 个循环过程

(4)逻辑功能分析:由状态图和时序图 可知,该电路是十进制计数器,或10分频器。

EXIT EXIT

第5章 时序逻辑电路

5.1.2 时序逻辑电路的分析方法

演 示 文 稿 Presentation

基本步骤:

1. 根据给定的电路,写出它的输出方程和驱动方程,并求 状态方程。 时序电路的输出逻辑表达式。 2. 列状态转换真值表。 各触发器输入信号的逻辑表达式。 将驱动方程代入相应触发器的特性方程中所得到的方程 3. 分析逻辑功能。 简称状态转换表,是反映电路状态转换的规律与条件的表格。 方法:将电路现态的各种取值代入状态方程和输 出方程进行计算,求出相应的次态和输出,从而列出 4. 根据状态转换真值表来说明电路逻辑功能。 画状态转换图和时序图。 状态转换表。 如现态起始值已给定,则从给定值开始计算。如 用圆圈及其内的标注表示电路的所有稳态, 没有给定,则可设定一个现态起始值依次进行计算。 在时钟脉冲 CP作用下,各触发器状态变化的波形图。 用箭头表示状态转换的方向,箭头旁的标注表示 状态转换的条件,从而得到的状态转换示意图。 EXIT EXIT

数字电子技术基础-第五章--时序逻辑电路

(2)根据设计要求做约定,设

定状态,画出原始状态图。

5个状态至少需要3个触发器来实现,3个触发器的状态分 别用Q2Q1Q0来表示。5进制计数器应该有5个不同的状态, 至于是哪5个状态,则可由设计者自行决定。题目中要求 是“加”计数器,“加”的含义在例5-1中已经有介绍。 所以可以选择状态Q2Q1Q0为000、001、010、011、100、 000循环。可以这样约定每个状态的含义:状态000表示 计数器已经收到第1个CP脉冲,此时输出Y为0;状态001 表示计数器已经收到第2个CP脉冲,此时输出Y为0;状态 010表示计数器已经收到第3个CP脉冲,此时输出Y为0; 状态011表示计数器已经收到第4个CP脉冲,此时输出Y为 0;状态100表示计数器已经收到第5个CP脉冲,此时输出 Y为1,得到状态图如图所示。

3个周期长的输入信号(序列长度为3的输入序列)的历史有8种可能, 即输入序列可以是000、001、010、011、100、101、110、111。

从电路上电作为0时刻,依时间顺序设计电路的状 态。因此状态设计如下:0时刻时电路的状态作为 初始状态a,输入1个0(输入序列为0)用状态b 表示;输入1个1(输入序列为1)用状态c表示; 先输入1个0、再输入1个0(输入序列为00)用状 态d表示;先输入1个0、再输入1个1(输入序列 为01)用状态e表示;先输入1个1、再输入1个0 (输入序列为10)用状态f表示;先输入1个、再 输入1个1(输入序列为11)用状态g表示。因此 电路共需7个状态。通过后面的分析会看到7个状 态中有多余的。

加法运算

时序电路实现:

串行加法器:面积小,速度慢

组合电路实现:

并行加法器:面积大,速度快

组合逻辑电路实现加法运算

串行进位加法器

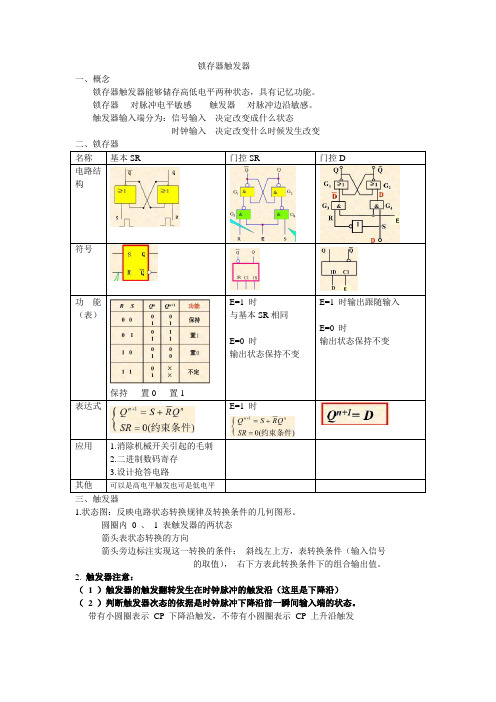

数电第五章总结

锁存器触发器

一、概念

锁存器触发器能够储存高低电平两种状态,具有记忆功能。

锁存器----对脉冲电平敏感触发器----对脉冲边沿敏感。

触发器输入端分为:信号输入---决定改变成什么状态

时钟输入---决定改变什么时候发生改变

三、触发器

1.状态图:反映电路状态转换规律及转换条件的几何图形。

圆圈内0 、 1 表触发器的两状态

箭头表状态转换的方向

箭头旁边标注实现这一转换的条件:斜线左上方,表转换条件(输入信号

的取值),右下方表此转换条件下的组合输出值。

2.触发器注意:

( 1 )触发器的触发翻转发生在时钟脉冲的触发沿(这里是下降沿)

( 2 )判断触发器次态的依据是时钟脉冲下降沿前一瞬间输入端的状态。

带有小圆圈表示CP 下降沿触发,不带有小圆圈表示CP 上升沿触发

符号

表达式

(仅在触发沿

状态图

1.上下的是直接置1置0端 低有效。

上下两端作用时其他端口无效

R D 和 S D 不受 CP 和 D 信号的影响, 具有最高的优先级。

数电课件第五章锁存器和触发器

器和主从触发器等。

不同类型的触发器具有不同的工 作特性和应用场景,可以根据实 际需求选择合适的触发器类型。

03 锁存器和触发器的应用

在时序逻辑电路中的应用

存储数据

锁存器和触发器可以用于存储数 据,在时序逻辑电路中作为寄存 器使用,保存数据以便后续处理。

控制信号

锁存器和触发器可以用于控制信号 的传递,在时序逻辑电路中作为控 制门使用,根据输入信号的变化来 控制输出信号的输出。

数电课件第五章锁存器和触发器

目录

• 锁存器概述 • 触发器概述 • 锁存器和触发器的应用 • 锁存器和触发器的实例分析 • 总结与展望

01 锁存器概述

定义与特点

01

02

定义:锁存器是一种具 特点 有存储功能的电路,能 在特定条件下保存数据, 即使在电源关闭或电路 其他部分出现故障的情 况下也能保持数据的完 整性。

分析

通过仿真验证了74HC74的触发器功能,并对其工作原理有了更深入的理解。

05 总结与展望

锁存器和触发器的重要性和应用价值

锁存器和触发器是数字电路中的基本元件,在时序逻辑电路和组合逻辑 电路中有着广泛的应用。

锁存器能够存储二进制数据,在数字系统中起到数据存储和传输的作用; 触发器则能够记忆二进制数据的状态,常用于实现时序逻辑电路如计数 器和寄存器等。

03

04

05

具有记忆功能,能够保 存前一个状态;

在时钟信号的驱动下, 通常由逻辑门电路构成, 完成数据的存储和读取; 如与门、或门和非门等。

工作原理

在时钟信号的控制下,锁存器在数据输入端接收数据,并在数据输出端输出数据。

当时钟信号处于低电平状态时,锁存器处于关闭状态,无法接收新的数据输入。

不同类型的触发器具有不同的工 作特性和应用场景,可以根据实 际需求选择合适的触发器类型。

03 锁存器和触发器的应用

在时序逻辑电路中的应用

存储数据

锁存器和触发器可以用于存储数 据,在时序逻辑电路中作为寄存 器使用,保存数据以便后续处理。

控制信号

锁存器和触发器可以用于控制信号 的传递,在时序逻辑电路中作为控 制门使用,根据输入信号的变化来 控制输出信号的输出。

数电课件第五章锁存器和触发器

目录

• 锁存器概述 • 触发器概述 • 锁存器和触发器的应用 • 锁存器和触发器的实例分析 • 总结与展望

01 锁存器概述

定义与特点

01

02

定义:锁存器是一种具 特点 有存储功能的电路,能 在特定条件下保存数据, 即使在电源关闭或电路 其他部分出现故障的情 况下也能保持数据的完 整性。

分析

通过仿真验证了74HC74的触发器功能,并对其工作原理有了更深入的理解。

05 总结与展望

锁存器和触发器的重要性和应用价值

锁存器和触发器是数字电路中的基本元件,在时序逻辑电路和组合逻辑 电路中有着广泛的应用。

锁存器能够存储二进制数据,在数字系统中起到数据存储和传输的作用; 触发器则能够记忆二进制数据的状态,常用于实现时序逻辑电路如计数 器和寄存器等。

03

04

05

具有记忆功能,能够保 存前一个状态;

在时钟信号的驱动下, 通常由逻辑门电路构成, 完成数据的存储和读取; 如与门、或门和非门等。

工作原理

在时钟信号的控制下,锁存器在数据输入端接收数据,并在数据输出端输出数据。

当时钟信号处于低电平状态时,锁存器处于关闭状态,无法接收新的数据输入。

数电 第5章 组合逻辑电路

D0 S1S0 00 S3S2 00 01 11 10 1 1 1 0

01 1 1 1 0

11 1 1 0 0

10 1 1 0 0

INT0 S1S0 00 S3S2 00 01 11 10 1 1 1 1

01 1 1 1 1

11 1 1 0 1

10 1 1 1 1

D1 S3 S2 S3 S2 D0 S3 S2 S1 INT0 S3 S2 S1S0 S3 S2 S1 S0

第5章 组合逻辑电路

5.1 引言 5.2 组合逻辑电路的分析与设计 5.3 加法器 5.4 编码器 5.5 译码器 5.6 数据选择器 5.7 数码比较器 5.8 竞争与冒险

5.1 引言

组合逻辑电路——逻辑电路任何一时刻的输入仅由该时刻的输入 所决定。 时序逻辑电路——逻辑电路某一时刻的输出不仅由该时刻的输入 所决定,而且与过去的输出有关。

(2) 列出电路的真值表。

(3) 根据真值表写出逻辑说明

“不一致电路”或“一致性判别电路

1. 判断已知逻辑电路的性质。组合逻辑电路仅由逻辑门构成, 信号从电路的输入侧向输出侧单方向传输,不存在反馈。 2. 写出电路的逻辑函数表达式。根据逻辑电路图,得到描述电 路输出与输入变量之间逻辑关系的函数式。

例4电路的真值表 A B C F

F A

BC 0 1

00 1 1

01 1 0

11 0 0

10

0

0 0 0 1 1 1 1

ห้องสมุดไป่ตู้

0

0 1 1 0 0 1 1

0

1 0 1 0 1 0 1

1

1 0 1 0 0

数字电子电路课件第五章

2

二、主从 JK 触发器 1.电路组成

K

& G

& E

&

Q主 C

& A

CP

J

&

H

& F

Q主

& D

& B

1

CP=1时,

Q

n+1

主

=

J

Q

n

+

K

Q

n

CP=0时,

2021/8/5

Q

n+1 =

Q

n+1

主

=

J

Q

n+

K

Q

n

Q Q

3

2.异步置0、置1端 RD,SD: 即无条件置0、置1端

当RD=0时,无论CP、J、K信号如何变化, 则触发器置0 当SD=0时,无论CP、J、K信号如何变化,则触发器置1

A

B

置 0

101CR‵D线塞阻1置

S‵D 10

E

置 1

维 持 线

a 01 F

10 CP

置0阻塞线

b 10 G

维 持 线

2021/8/5 D 01

a =1 RD =0 b =0 SD =1

Qn+1 =0

当D =1 时

a =0 RD =1 Qn+1 =1 b =1 SD =0

∴ Qn+1 =D

7

2.异步置0,置1端

4.对 JK , CP 信号的要求 要求:在 CP =1 期间输入

5.逻辑符号

RD

&J Q CP

激励信号 J , K 不发生变化。

&K Q

二、主从 JK 触发器 1.电路组成

K

& G

& E

&

Q主 C

& A

CP

J

&

H

& F

Q主

& D

& B

1

CP=1时,

Q

n+1

主

=

J

Q

n

+

K

Q

n

CP=0时,

2021/8/5

Q

n+1 =

Q

n+1

主

=

J

Q

n+

K

Q

n

Q Q

3

2.异步置0、置1端 RD,SD: 即无条件置0、置1端

当RD=0时,无论CP、J、K信号如何变化, 则触发器置0 当SD=0时,无论CP、J、K信号如何变化,则触发器置1

A

B

置 0

101CR‵D线塞阻1置

S‵D 10

E

置 1

维 持 线

a 01 F

10 CP

置0阻塞线

b 10 G

维 持 线

2021/8/5 D 01

a =1 RD =0 b =0 SD =1

Qn+1 =0

当D =1 时

a =0 RD =1 Qn+1 =1 b =1 SD =0

∴ Qn+1 =D

7

2.异步置0,置1端

4.对 JK , CP 信号的要求 要求:在 CP =1 期间输入

5.逻辑符号

RD

&J Q CP

激励信号 J , K 不发生变化。

&K Q

第5章,数电完整课件。

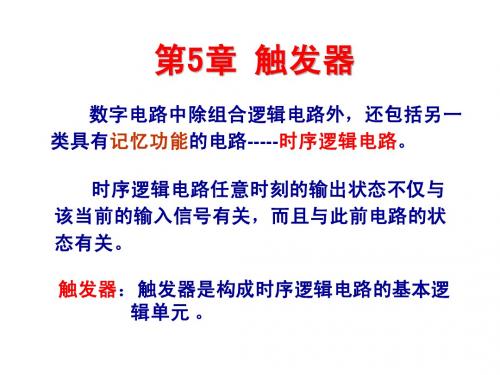

第5章 触发器

数字电路中除组合逻辑电路外, 数字电路中除组合逻辑电路外,还包括另一 类具有记忆功能的电路-----时序逻辑电路。 类具有记忆功能的电路 时序逻辑电路。 记忆功能的电路 时序逻辑电路 时序逻辑电路任意时刻的输出状态不仅与 该当前的输入信号有关, 该当前的输入信号有关,而且与此前电路的状 态有关。 态有关。 触发器: 触发器:触发器是构成时序逻辑电路的基本逻 辑单元 。

5.2 基本RS触发器 基本RS触发器

3、触发方式 、 置1 端

S

1 0

G1 &

0 1Байду номын сангаас

Q

S (Set)-置“1”端(置位 (Set)端) 置0 端

R G2 &

Q

R (Reset)-置“0”端(复位 (Reset)端)

0 1

基本触发器的触发方式属电平触发。 基本触发器的触发方式属电平触发。

5.2 基本RS触发器 基本RS触发器

双稳态触发器的特点

( 1) 触发器的次态不仅与输入信号状态有关 , ) 触发器的次态不仅与输入信号状态有关, 而且与触发器的现态有关。 而且与触发器的现态有关。 ( 2) 电路具有两个稳定状态, 在无外来触发信 ) 电路具有两个稳定状态 , 号作用时,电路将保持原状态不变。 号作用时,电路将保持原状态不变。 ( 3) 在外加触发信号有效时 , 电路可以触发翻 ) 在外加触发信号有效时, 实现置0或置 或置1。 转,实现置 或置 。 ( 4) 在稳定状态下两个输出端的状态和必须是 ) 互补关系,即有约束条件。 互补关系,即有约束条件。

以基本 RS 触发器为例 Qn+1 x x 0 0 1 1 0 1

次态: 次态: 触发器接收 输入信号之 后所处的新 的稳定状态。 的稳定状态。

数字电路中除组合逻辑电路外, 数字电路中除组合逻辑电路外,还包括另一 类具有记忆功能的电路-----时序逻辑电路。 类具有记忆功能的电路 时序逻辑电路。 记忆功能的电路 时序逻辑电路 时序逻辑电路任意时刻的输出状态不仅与 该当前的输入信号有关, 该当前的输入信号有关,而且与此前电路的状 态有关。 态有关。 触发器: 触发器:触发器是构成时序逻辑电路的基本逻 辑单元 。

5.2 基本RS触发器 基本RS触发器

3、触发方式 、 置1 端

S

1 0

G1 &

0 1Байду номын сангаас

Q

S (Set)-置“1”端(置位 (Set)端) 置0 端

R G2 &

Q

R (Reset)-置“0”端(复位 (Reset)端)

0 1

基本触发器的触发方式属电平触发。 基本触发器的触发方式属电平触发。

5.2 基本RS触发器 基本RS触发器

双稳态触发器的特点

( 1) 触发器的次态不仅与输入信号状态有关 , ) 触发器的次态不仅与输入信号状态有关, 而且与触发器的现态有关。 而且与触发器的现态有关。 ( 2) 电路具有两个稳定状态, 在无外来触发信 ) 电路具有两个稳定状态 , 号作用时,电路将保持原状态不变。 号作用时,电路将保持原状态不变。 ( 3) 在外加触发信号有效时 , 电路可以触发翻 ) 在外加触发信号有效时, 实现置0或置 或置1。 转,实现置 或置 。 ( 4) 在稳定状态下两个输出端的状态和必须是 ) 互补关系,即有约束条件。 互补关系,即有约束条件。

以基本 RS 触发器为例 Qn+1 x x 0 0 1 1 0 1

次态: 次态: 触发器接收 输入信号之 后所处的新 的稳定状态。 的稳定状态。

数电 第5章

RD = R ⋅ CP, S D = S ⋅ CP

第5章 触发器

图5.2.1 钟控RS触发器

第5章 触发器

当CP=0时,C、D门被封锁,RD=1,SD=1,由基本RS触 发器功能可知,触发器状态维持不变。 当CP=1时,RD=R, SD=S,触发器状态将发生转移。将 RD、SD代入基本RS触发器的特征方程式(5 - 1)中,可得出钟 控RS触发器的特征方程为

Q n +1 = S + RQ n RS = 0

(约束条件)

其中RS=0表示R与S不能同时为1。该方程表明当CP=1时, 钟控RS触发器的状态按上式转移,即时钟信号为1时才允 许外输入信号起作用。

第5章 触发器

同理还可得出CP=1时,钟控RS触发器的状态转移真值表、 激励表分别如表5.2.1和表5.2.2所示,状态转移图和波形图分 如图52.2(a)、 (b)所示。 钟控RS触发器是在R和S分别为1时清“0”和置“1”,称 为R、S高电平有效,所以逻辑符号的R、S输入端不加小圆圈。 表 5.2.1 钟控RS触发器状态转移真值表 R 0 0 1 1 S 0 1 0 1 Qn+1 Qn 1 0 ×

第5章 触发器

表5.2.5

J 0 0 1 1 K 0 1 0 1

钟控JK触发器的状态表 钟控 触发器的状态表

Qn+1 Qn 0 1 Q

表5.2.6 钟控JK触发器的激励表

Qn 0 0 1 1 Qn+1 0 1 0 1 J 0 1 × × K × × 1 0

第5章 触发器

图5.2.7 JK触发器的状态图

S = J Q, R = KQ

由于Q和Q互补,无论J、K输入取值如何,它不可能出现 SR=11的情况,因此这种结构也解决了R、 S之间的约束问题。 由图5.2.6(a)可见:

第五章 数电课件

5.1.1 数码寄存器

1.由D触发器构成的数码寄存器 数码寄存器具有接收、存放、输出和清除数码的 (1)电路组成 功能。

在接收指令(在计算机中称为写指令)控制下, 将数据送入寄存器存放;需要时可在输出指令(读出 输出端 指令)控制下,将数据由寄存器输出。 CP:接收脉

冲(控制信 仿真 号输入端)

图5-1 单拍工作方式的数码寄存器

重点: 1.实现任意进制异步计数器的脉冲反馈法。 2.同步计数器的分析方法。

5.3

器。

任意进制计数器

任意进制计数器是指计数器的模N不等于2n的计数

5.3.1 异步计数器

在异步二进制计数器的基础上,通过脉冲反馈或 阻塞反馈来实现。 1.脉冲反馈式 (以10进制计数器为例)

① 设计思想:通过反馈线和门电路来控制二进制 计数器中各触发器的RD 端,以消去多余状态(无效状 态)构成任意进制计数器。

数码输 入端

(2)工作原理

当CP↑时,触发器更新状态, Q3Q2Q1Q0=D3D2D1D0,即接收输入数码并保存。 单拍工作方式:不需清除原有数据,只要CP↑一 到达,新的数据就会存入。 常用4D型触发器74LS175、6D型触发器74LS174、 8D型触发器74LS374或MSI器件等实现。

2.由D型锁存器构成的数码寄存器 (1)锁存器的工作原理 送数脉冲CP为锁存 控制信号输入端, 即使能信号(电平 信号)。

5.3.2 同步计数器

下面介绍同步计数器的分析方法。 计数器的分析:根据给定的逻辑电路图,分析 计数器状态和它的输出在输入信号和时钟信号作用 下的变化规律。 分析步骤: (1)写驱动方程和输出方程。 (2)将驱动方程代入触发器的特性方程,求出电 路的状态方程(Qn+1表达式)。 (3)画出相应的Qn+1 卡诺图,然后画计数器的状 态卡诺图。 (4)列计数器的状态转换表,并画状态转换图和 时序图。 (5)说明计数器的逻辑功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例4: 分析电路功能。

0 0 1 1 0

M=10 计数器

(4)同步计数器的级联

若干片同步计数器组成同步计数链时,就要利用计数控 制端CTT、CTP传递进位信号。

高位片计数的条件是:只有等低位片输出为全1,其进位 输出CO=1时才能使高位片在输入下一个计数脉冲后接收进位 信号开始计数,否则只能为保持状态。

Q3 Q 2 Q1 Q0 & 0 Q3Q 2 Q 1Q 0 D/U RCO 74191 MAX/MIN LD D 3 D2 D1 D 0 0 0 1 1

1101 1100 1011 1010 1001 1000

EN CP

∧

0 计数脉冲

三、异步计数器74290

1 . 逻辑符号

R0(1) R0(2) R0(1) S9(1) S9(2)

1

0 0 0 1

1 0 0 0

0 0 0 0

1 0 0 0 0 0 0 0

(三)74161/ 74163功能扩展 连接成任意模M 的计数器

(1) 同步预置法

(2) 反馈清零法 (3) 多次预置法

(2)反馈清零法 例3: 分析图示电路的功能。

模12计数器

74163?

采用74161

N 0 1 2 3 4 5 6 7 8 9 10 11 12 态序表 Q3 Q2 Q1 Q0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0

第五章 常用时序集成电路及其应用

第一节 计数器

第二节 寄存器 第三节 序列码发生器

第四节 时序模块的应用

小结

第一节 计数器

•计数器的分类

用来计算输入脉冲数目

动画计数器

按进位方式,分为同步和异步计数器。

按进位制,分为模2、模10和任意模计数器。

按逻辑功能,分为加法、减法和可逆计数器。 按集成度,分为小规模与中规模集成计数器。

CTP、CTT:可作为使能端和多 内部由四个主从JK触 片级联使用。 发器和控制电路构成。

74161

R

LD CTT CTP

CP

CO CO

CO

符号中LD端为有效时,此端引 当Q3 Q2 Q1 Q0=1111 时,且 符号输入中R端有效,在 入线为低时,且时钟CP上升沿时,将 CTT等于1时, 控制输出端CO输出 此输入为低电平时,输出为0, 输入端数字送到输出端。同步预置。 有效高电平。

R0(2)

S9(1) S9(2)

74LS290

在外部将QA和CPB 在外部将QD和CPA (1) 触发器A:模2 CPA入QA出 连接构成8421BCD码计 连接构成5421BCD码计 (2) 触发器B、C、D:模5异步计 数。 数。 数器。 fCPB 入QD QB出 f 从CPA入,输出从 从CPB 入,输出从 QS9(1)、S9(2)有一个无效。 Q Q 出。 S9(1) QA 9(2) QDQ 、S出。有效。 不管

二、四位二进制可逆计数器74193

1. 逻辑符号

R

UP DN LD

LD当低电平时,数据从 D CO=0 A:数据输入,从高位 R=1时,高电平有效, 加到最大 输入到输出,且异步预置。 低位。 输出清零。 值时产生进位

QCC QCB

74LS193

R

CO

CPU CPD LD

BO

A B C D

A B C D

A B C D 加法计数

0

0

× ×× ×

× ×× ×

减法计数

保持

二、四位二进制可逆计数器74193

2. 74193功能扩展

—— 连接成任意模M 的计数器

(1) 接成M<16的计数器

(2) 接成M>16的计数器

(1)接成M<16的计数器

态序表 QD QC QB QA 0 0 1 1 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1

方法一:采用 例6:用74193设计M=9 计数器。 异步预置、 加法计数

N 0 1 2 3 4 5 6 7 8 9

0

R

74LS193

R

UP f DN 1 LD

CPU

CPD LD

QCC QCB

CO BO

0 1 1

A B C D

A B

QA QB QC QD

QA QB QC QD

C

D

CO=0

0

0 1 1 0

×

× 0 1

D3 D2 D1 D0 D3 D2 D1 D0

74161

1

R

1

× ×× ×

计数

2

3

4

5

6

7

8

CP D0 D1

D2 D3 CTT GND

4)计数:当LD = R = CPT= CTT =1时,按二进制自然 3)保持:当R=LD=1时,CTP或CTT有一个无效,各 1)异步清除:当R=0,输出“0000”状态,与CP无关。 码计数。 若初态为0000,15个CP后,输出为“1111”, 触发器均处于保持状态。 进位CO = CTTQ3Q2Q1Q0 =1。第16个CP作用后,输出 2)同步预置:当C=1,LD=0,在CP上升沿时,输出 恢复到0000状态,CO = 0。 端反映输入数据的状态。

第一节 计数器

•部分常用集成计数器

第一节 计数器

四位二进制同步计数器 四位二进制可逆计数器

中规模异步计数器

一、四位二进制同步计数器

(一) 四位二进制同步计数器74161

(二) 四位二进制同步计数器74163

(三) 74161/74163功能扩展

(一)四位二进制同步计数器74161

逻辑符号

R LD CTT CTP CP

(2) 接成M>16的计数器

(2)接成M>16的计数器

例8: 用74193设计M=147 计数器。

方法一:采用 异步清零、 加法计数。

M = (147)10

0 1 0 1 0 0 0 0 1 0 0 0 0 0 1 0

=(10010011)2

需要两片74193

(2)接成M>16的计数器

例9:用74193设计M=147 计数器

Q7 Q6 Q5 Q4 Q3Q 2 Q1Q 0 RCO 74161(2) ET EP

∧

Q3 Q2 Q1 Q0 Q3Q 2 Q1Q 0 RCO 74161(1) ET EP

∧

1 计数脉冲

RD LD D3 D2 D1 D 0 1

CP

RD LD D3 D2 D1 D 0 1

CP

清零脉冲

第一节 计数器

一、四位二进制同步计数器 二、四位二进制可逆计数器 三、中规模异步计数器

74163

CO

1

0 CO=1

Q0 Q1 Q2 Q3

f/10

0 0 1 1 1 1 0 0

D0 D1 D2 D3

0 Q0 1 Q1 1 Q2

Q3 0

例2: 同步预置法设计 M=24 计数器。

(24)10=(11000)2 初态为:0000 0001 需两片 终态:00011000 0

1 1 1 0 0 0

D3 D2 D1 D0

保持

×

1

× ×× ×

× ×× ×

保持

计数

(1)外引线排列和 74161相同。 (2)置数,计数, 保持功能与74161 相同。

(3)清零功能与 74163采用同步清零方式: 74161不同。 当R =0时,且当 CP 的上升沿

来到时,输出Q0Q1Q2Q3 才全被清零。

比较四位二进制同步计数器

0

R

74LS193

R CPU CPD LD QCC QCB

UP 1 DN f LDຫໍສະໝຸດ CO BO10 0

A B

A

QA QB QC QD

QA

QB

B

C D

C

D

QC

QD

BO=0

1

1 0 0 1

二、四位二进制可逆计数器74193

2. 74193功能扩展

—— 连接成任意模M 的计数器

(1) 接成M<16的计数器

BO=0

QCB DN Q A Q B Q C Q D

二、四位二进制可逆计数器74193

74193功能表

输 UP × × ↑ 1 1 DN × × 1 ↑ 1 R 1 0 0 入 LD × 0 1 1 1 A B C D × ×× × A B C D × ×× × 输 出 QA QB QC QD 0 0 0 0

异步预置、 例7:用74193设计M=9 计数器。 减法计数

N 0 1 2 3 4 5 6 7 8 9

(1)接成M<16的计数器 方法二:采用

态序表 QD QC QB QA

1 1 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0

方法二:采用 减法计数、 异步预置、 利用BO端。 M = (147)10 =(10010011)2

1 1 0 0 1 1 0 0 1 0 0 1

1 0 0 1

课堂练习:用集成计数器74191和与非门组成的余3码 10进制计数器。

Q Q QQ 3 2 1 0

0011

0100

0101

0110

0111

0

1

0 0 0 0