EP4CE10E22封装

EP4CE15E22C9L中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

Cyclone IV器件在商业,工业,延伸产业和汽车级版本. Cyclone IV E器件提供-6(最快 ),-7,-8,-8L和-9L速度等级的商用设备,-8L速度等级为工业设备,以及用于扩展工业和汽 车设备-7速度等级. Cyclone IV GX器件提供-6(最快),-7和-8速度等级的商用设备和 -7为工业设备的速度等级.

条件( V)

过冲持续时间为%高时间

Unit

交流输入

Vi

电压

VI = 4.20 VI = 4.25 VI = 4.30 VI = 4.35 VI = 4.40 VI = 4.45 VI = 4.50 VI = 4.55 VI = 4.60

100

%

98

%

65

%

43

%

29

%

20

%

13

%

9

%

6

%

图1-1

示出的方法来确定过冲持续时间.该

芯片中文手册,看全文,戳

1–2

第 1章: Cyclone IV器件手册

运行条件

1

Cyclone IV E工业设备I7提供具有扩展的工作温度范围.

绝对最大额定值

绝对最大额定值规定的最大工作条件Cyclone IV器件.该值是基于与所述设备和击穿和损伤 机理理论模型进行的实验.该装置的功能操作不在这些条件暗示.

从的Cyclone IV E和Cyclone IV GX器件的预期值.所有物资必须是没有高原严格单调.

表 1-3.推荐工作条件 Cyclone IV E器件

符

参数

VCCINT (3) VCCIO (3), (4) VCCA (3)

电源电压为内部逻辑, 1.2-V操作

基于EtherCAT技术的多轴运动控制系统

基于EtherCAT技术的多轴运动控制系统张从鹏;赵康康【摘要】以EtherCAT通信技术为基础,设计了一种基于ARM和FPGA双核的EtherCAT总线式多轴运动控制系统.提出了STM32作为系统管理芯片,通过SPI通信控制ET1200从站控制芯片实现Eth-erCAT总线从站通信功能的解决方案;并采用FPGA作为协处理器,完成运动控制算法的实现和执行.完成了运动控制系统的硬件电路设计和软件开发,并制作了样机.经试验测试,实现了EtherCAT总线通信功能,采用TwinCAT完成了闭环运动控制,并且可以独立工作实现运动规划,满足工业控制工程中的应用要求.%An EtherCAT bus based multi axis motion control system was designed based on ARM and FPGA , after systemat-ically study on EtherCAT technology .The solution of main control chip STM 32 controlling ET1200 through SPI was presented .A motion control algorithm based on FPGA was developed .The specific hardware circuit and software of control system was de-signed, and a prototype was produced .The experiment demonstrates that the communication function of EtherCAT bus was real -ized, and the closed-loop motion control was completed by TwinCAT .Motion control system can work independently to achieve motion planning , meetting the application of industrial control in engineering .【期刊名称】《仪表技术与传感器》【年(卷),期】2017(000)001【总页数】5页(P115-118,122)【关键词】EtherCAT;多轴;STM32;运动控制;FPGA;插补算法;TwinCAT【作者】张从鹏;赵康康【作者单位】北方工业大学机械与材料工程学院,北京 100144;北方工业大学机械与材料工程学院,北京 100144【正文语种】中文【中图分类】TP23现代制造系统正朝着柔性化、开放化、网络化方向发展,覆盖多学科、多领域相关技术。

FPGA可编程逻辑器件芯片EP4CE22F17I7中文规格书

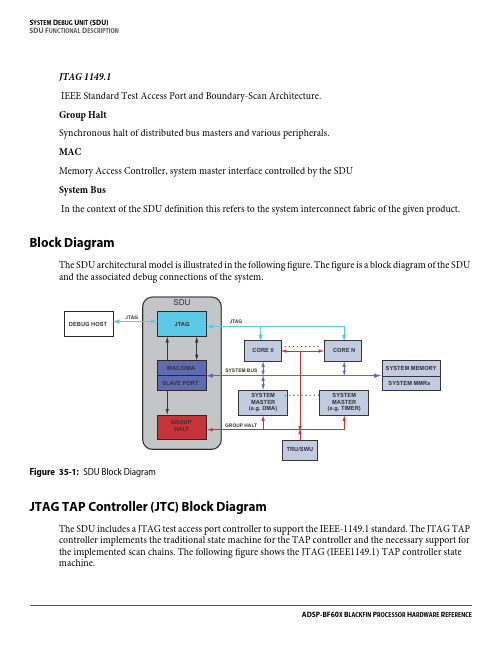

S YSTEM D EBUG U NIT (SDU)SDU F UNCTIONAL D ESCRIPTIONJTAG 1149.1IEEE Standard Test Access Port and Boundary-Scan Architecture.Group HaltSynchronous halt of distributed bus masters and various peripherals.MACMemory Access Controller, system master interface controlled by the SDUSystem BusIn the context of the SDU definition this refers to the system interconnect fabric of the given product.Block DiagramThe SDU architectural model is illustrated in the following figure. The figure is a block diagram of the SDU and the associated debug connections of the system.Figure 35-1:SDU Block DiagramJTAG TAP Controller (JTC) Block DiagramThe SDU includes a JTAG test access port controller to support the IEEE-1149.1 standard. The JTAG TAP controller implements the traditional state machine for the TAP controller and the necessary support for the implemented scan chains. The following figure shows the JTAG (IEEE1149.1) TAP controller state machine.B OOT ROM AND B OOTING THE P ROCESSORB OOTING R EGISTER R EFERENCE10NOHOOK Do not execute hook routine 9NOPREBOOT Always 08NOFAULTS Do not perform fault initialization 5NOCACHE Do not perform cache initialization 4NOMEMINIT Do not perform memory initialization 3RCU_BCODE_HBTOVW Execute wakeup functionality 2RCU_BCODE_HALT Execute no boot routine 1NOVECTINIT Do not vector to the application 0NOKERNEL Do not execute the boot kernelTable 34-29:RCU BCODE Register Fields (Continued)Bit No.Bit Name Description/EnumerationS YSTEM D EBUG U NIT (SDU)SDU F UNCTIONAL D ESCRIPTION•Block Diagram•JTAG TAP Controller (JTC) Block Diagram•Memory Access Controller (MAC)•Group HaltADSP-BF60x SDU Register ListThe system debug unit (SDU) provides IEEE-1149.1 support through its JTAG interface. The registers listed in the SDU register summary table govern SDU operations. For more information on SDU function-ality, see the SDU register descriptions.Table 35-1:ADSP-BF60x SDU Register ListName DescriptionSDU_IDCODE ID Code RegisterSDU_CTL Control RegisterSDU_STAT Status RegisterSDU_MACCTL Memory Access Control RegisterSDU_MACADDR Memory Access Address RegisterSDU_MACDATA Memory Access Data RegisterSDU_DMARD DMA Read Data RegisterSDU_DMAWD DMA Write Data RegisterSDU_MSG Message RegisterSDU_MSG_SET Message Set RegisterSDU_MSG_CLR Message Clear RegisterSDU_GHLT Group Halt Register。

基于DLIS2K的高帧频线阵成像系统设计

收稿日期:2017年10月7日,修回日期:2017年11月28日基金项目:陕西省科技厅工业攻关计划项目(编号:Z013K06-14)资助。

作者简介:陈文艺,男,博士,教授,硕士生导师,研究方向:数字图像处理及传输。

朱红雷,男,硕士研究生,研究方向:电路与系统。

杨辉,男,硕士,工程师,研究方向:数字图像处理。

∗1引言随着CMOS 性能的不断提升,CMOS 线阵成像系统可以实现CCD 线阵成像系统相同的成像质量[1~2],且系统具有低功耗、高集成度、高精度、高帧频等优势而被广泛应用到机器视觉、边沿检测、条码编码定位、非接触尺寸检测等光电检测领域[3~4]。

目前国内工业设备上使用的CMOS 线阵成像系统一般只有像机功能,不能进行实时图像处理,因此开展高帧频的CMOS 线阵工业成像系统研究,并结合FPGA 实现一体化的实时图像传感和处理系统具有较高实用价值[5~7]。

高帧频线阵成像系统的设计采用线阵CMOS 图像传感器DLIS2K 做光电转换,Altera 公司的Cy ⁃clone IV 系列中的EP4CE10E22N8型现场可编程门阵列(Field Programmable Gate Arrays ,FPGA )作为成像系统控制器和实时信号处理器,其中可编程片上系统(System on a Programmable Chip ,SOPC )与上基于DLIS2K 的高帧频线阵成像系统设计∗陈文艺1朱红雷2杨辉1(1.西安邮电大学物联网与两化融合研究院西安710061)(2.西安邮电大学电子工程学院西安710121)摘要为满足工业检测领域中对高帧频工业线阵成像系统的需求,基于线阵CMOS 图像传感器DLIS2K 设计了高帧频线阵成像系统,通过对成像系统的DAC 过程中的高、低参考电平、预加载值等的优化配置,采用行Binning 模式,对采集到的数据做中值滤波,提高了系统的成像质量和灵敏度。

通过实际场景的实验结果表明,高帧频线阵成像系统工作在像素时钟80MHz ,分辨率2048时,输出帧频可达9412fps/s ,系统信噪比约为42.3dB ,成像质量满足线阵成像系统的设计要求。

基于FPGA的双AD高精度小信号采集系统

基于F P G A的双A/D高精度小信号采集系统靳鹏飞,王振华,贺渊明,郭震(许继电气技术中心装置平台部,许昌461000)摘要:设计了一种基于F P G A的双A/D高精度小信号采集系统㊂该系统包括测试电流通道和保护电流通道㊂罗氏线圈输出的感应电动势通过共模扼流圈消除共模干扰后分别送入测试电流通道和保护电流通道,保护电流通道经过信号调理网络后直接送入A D C1中进行转换㊂为了提高测试电流通道的测量精度,调理后的信号经过P G A网络后送入A D C2中进行转换㊂F P G A负责采集数据的处理,并按照F T3报文格式进行组帧,将组帧的数字信号通过微型链路光纤组件上传至综合检测单元㊂测试结果表明,该系统测试精度达到0.2s/2级,具有很强的抗干扰能力,能够满足电力系统对电流测试精度的要求㊂关键词:双A/D;F P G A;小信号;E P4C E10E22I7N中图分类号:T N79文献标识码:AD o u b l e A/D a n d H i g h-p r e c i s i o n S m a l l S i g n a l A c q u i s i t i o n S y s t e m B a s e d o n F P G AJ i n P e n g f e i,W a n g Z h e n h u a,H e Y u a n m i n g,G u o Z h e n(X u j i E l e c t r i c T e c h n o l o g y C e n t e r D e v i c e P l a t f o r m D e p a r t m e n t,X u c h a n g461000,C h i n a)A b s t r a c t:A d o u b l e A/D a n d h i g h-p r e c i s i o n s m a l l s i g n a l a c q u i s i t i o n s y s t e m b a s e d o n F P G A i s d e s i g n e d.T h e s y s t e m i n c l u d e s t e s t c u r r e n t c h a n n e l a n d p r o t e c t i o n c u r r e n t c h a n n e l.T h e i n d u c e d e l e c t r o m o t i v e f o r c e o u t p u t b y R o g o w s k i c o i l i s s e n t t o t e s t c u r r e n t c h a n n e l a n d p r o-t e c t i o n c u r r e n t c h a n n e l r e s p e c t i v e l y a f t e r e l i m i n a t i n g c o mm o n m o d e i n t e r f e r e n c e b y c o mm o n m o d e c h o k e.T h e p r o t e c t i o n c u r r e n t c h a n n e l i s d i r e c t l y s e n t t o A D C1f o r c o n v e r s i o n a f t e r s i g n a l c o n d i t i o n i n g n e t w o r k.I n o r d e r t o i m p r o v e t h e m e a s u r e m e n t a c c u r a c y o f t h e t e s t c u r-r e n t c h a n n e l,t h e m o d u l a t e d s i g n a l i s s e n t t o A D C2f o r c o n v e r s i o n a f t e r p a s s i n g t h r o u g h P G A n e t w o r k.F P G A i s r e s p o n s i b l e f o r d a t a a c-q u i s i t i o n a n d p r o c e s s i n g,a n d f r a m e a c c o r d i n g t o F T3m e s s a g e f o r m a t.T h e d i g i t a l s i g n a l o f f r a m i n g i s u p l o a d e d t o t h e i n t e g r a t e d d e t e c t i o n u n i t t h r o u g h m i c r o l i n k o p t i c a l f i b e r c o m p o n e n t s.T h e t e s t r e s u l t s s h o w t h a t t h e t e s t a c c u r a c y o f t h e s y s t e m r e a c h e s0.2s/2l e v e l a n d h a s s t r o n g a n t i-i n t e r f e r e n c e a b i l i t y,w h i c h c a n m e e t t h e r e q u i r e m e n t s o f p o w e r s y s t e m f o r c u r r e n t t e s t a c c u r a c y.K e y w o r d s:d o u b l e A/D;F P G A;s m a l l s i g n a l;E P4C E10E22I7N0引言随着智能电网的不断发展,第三代智能变电站对继电保护装置的要求日益提高,变电站电流小信号在线监测面临严峻挑战[1]㊂传统的相位和幅值校准通过改变硬件回路中元器件参数来实现,但是随着装置运行环境越来越恶劣,温度㊁电磁场㊁高速信号的串扰都会严重影响元器件的某些参数,比如运放的零漂㊁电阻的阻值㊁电容的容值等,从而降低小信号的采样精度㊂传统控制方式是通过单片机来控制A D C的时序以及数据采集,单片机的运行速率低㊁开发不灵活,难以满足高的采样速率要求[2]㊂因此本文提出了一种基于F P G A的硬件设计方案,采用两片A/D 芯片实现对保护电流和测量电流的高速㊁高精度采集,具有很好的工程应用价值㊂1系统架构及原理1.1系统架构本文设计了一种适用于高频小信号的双A/D高精度采集系统,该系统可以直接连接罗氏线圈采集电流信号,采用双A/D设计,符合国网新规则,采样范围为0~ 100A㊂采集到的电流信号通过信号调理回路处理后,分别进入不同的A D C,单独进行转换㊂采集信号回路分为保护和测量两个回路,测量回路的小信号经过P G A处理,以提高小信号测量的精度㊂系统测试精度达到0.2s/2级,具有完备的A D C自检㊁电源自检以及精度自检㊂可编程逻辑芯片(F P G A)对数据进行处理,按照F T3报文格式进行组帧,将数字信号通过微型链路光纤组件上传至综合检测单元㊂系统采用光纤传输技术和数字信号处理技术,结合F P G A 实现了对高频小信号的精确测量㊂总体架构如图1所示㊂图1 系统总体架构1.2 工作原理本文设计的双A /D 高精度小信号采集系统是通过罗氏线圈实现电流的在线采集,A D C 采样间隔可以配置为80㊁160㊁200和256点,电流的幅值㊁相位和零漂等参数可通过光口进行调整,该系统可以灵活满足电力系统对电流测试精度的要求㊂采集系统实现了保护电流和测试电流的在线采集,罗氏线圈输出的感应电动势通过共模扼流圈消除共模干扰后分别送入测试电流通道和保护电流通道,在测试电流通道中,电流信号先后通过仪表放大器放大网络㊁运算放大器积分网络和P G A 网络,来提高系统的测量精度㊂在保护电流通道中,电流信号通过电阻分压网络转换为电压信号后,依次通过运算放大器隔离网络㊁积分网络和缓冲网络对信号进行调理,最终进入到A D C 1中进行转换㊂F P -G A 以同步串行的模式控制A D C 1和A D C 2进行数字信号的输出,同时将处理好的数字信号通过微型光纤组件发送到综合监测单元㊂综合监测单元也可以通过微型光纤组件对系统内的相关参数进行修改和配置㊂系统工作原理如图2所示㊂图2 系统工作原理2 系统设计高精度小信号采集系统可配合罗氏线圈实现小信号电流的实时在线监测[3],可结合电力系统的开入㊁开出㊁通信和管理机等单元实现对线路的保护和测量功能,主要完成小信号的高精度采集以及数据的处理和实时上传[4]㊂系统采用高可靠性硬件设计方案,测量电流通道和保护电流通道独立设计,互不干扰,可以灵活进行可视化操作,配合I E C 61850报文监视分析工具实现对幅值㊁相位和零漂等参数的调整,通过E C V T 800调试工具对采样间隔㊁波特率㊁去零漂方式㊁定时方式等参数进行设置㊂同时考虑到系统运行环境的复杂情况,本文对整个系统设置了一定的E M C 防护措施㊂该采集系统的基本功能和性能指标如表1所列㊂表1 系统功能和性能指标类 型指 标输入范围0~100A 测试精度0.2s /2级采样间隔80㊁160㊁200㊁256点可配置同步方式内部定时和外部同步脉冲可选参数配置幅值㊁相位㊁零漂等参数可调软件设计方面,系统以F P G A 作为控制芯片,分模块化进行软件设计,采用状态机的模式模拟A D C 的读写以及控制时序,用于读取各通道的转换结果,在数据处理模块中,对转换的结果进行处理和组帧,最终通过光发送模块将数据帧通过移位发送方式发送到综合监测单元,同时光模块数据接收来自综合监测单元的数据帧,用来设置系统的各个参数㊂2.1 硬件电路设计系统硬件电路采用分模块设计的方式,主要包括电源供电电路㊁测量电流采样电路㊁保护电流采样电路㊁A /D 转换电路㊁F P G A 控制电路和光纤收发电路,该设计方式能够保证系统可靠运行,兼容各种复杂的E M C 环境㊂(1)电源供电电路电源供电电路选用的是集成设计的电源模块,在抗干扰方面有很大的优势[5]㊂该电源模块的输入电压为220VA C 和220V D C ,具有过流保护㊁过压保护㊁欠压保护和过功率保护功能,能够为系统提供+5V 和ʃ12V 的供电电压㊂输入电压在80%~120%额定值范围内变化,负载在0%~100%额定值范围内变化时,输出电压纹波小于25m V ,能够保证系统可靠㊁稳定运行㊂(2)测量电流采样电路测量电流采样电路由放大电路㊁积分电路和P G A 电路组成㊂为了提高测量电流通道测试的准确性,放大电路中的运算放大器选用通用仪表放大器I N A 128,该运算放大器在增益为100倍时能够提供200k H z 的高带宽,具有非常低的偏置电流和偏置电压,能够保证测量电流通道具有很小的零漂电压㊂同时为了减小高低温环境对测量精度的影响,积分电路的运算放大器选用A D A 4077,它能够提供极低的偏置电压㊁偏置电流和漂移,使得系统尽管在苛刻的高低温环境中也能保持测量的高精度㊂P G A 电路是为了对电压小信号进一步放大,提高电流的测量精度㊂(3)保护电流采样电路保护电流采样电路由电阻分压网络㊁隔离网络㊁积分电路和缓冲网络组成㊂电阻分压网络选用高精度㊁低温漂电阻,负责将电流信号转换为适合A D C 输入量程的电压信号㊂在保护电流采样电路中加入隔离网络是为了减少分压电阻网络对积分网络的影响㊂同时,由于A D C 的模拟输入引脚存在一定的偏置电流,选用A D A 4077设计缓冲网络,能够为A D C 的模拟输入引脚提供一个低阻抗输入,减少由于偏置电流带来的直流零漂㊂(4)A /D 转换电路为了高精度采集直流小信号,本文选用了内置16位㊁双极性输入㊁同步采样的A D C 76064,其可以提供4路同步采样输入,每个通道均内置模拟输入钳位保护㊁二阶抗混叠滤波器㊁跟踪保持放大器㊁16位电荷再分配逐次逼近型转换器㊁灵活的数字滤波器㊁2.5V 基准电压缓冲以及高速串行和并行接口㊂本文将A D C 配置在串行接口模式,其中A D 1用于监视保护电流通道㊁测量电流通道和自身电源电压,A D 2用于监视保护电流通道㊁运放电源和自身的电源电压㊂(5)F P G A 控制电路系统采用A L T E R A (已被I n t e l 收购)公司的C yc l o n e I V 系列F P G A 作为主控芯片,型号为E P 4C E 10E 22I 7N [6],F P G A主控电路由主控芯片㊁时钟电路㊁复位电路㊁J A T G 电路和F L A S H 电路组成,主要完成系统初始化配置㊁A D C 初始化配置㊁A D C 采样以及数据的处理㊁存储和发送㊂F P G A通过配置A D C 芯片的A D C S ㊁A D C _C L K ㊁C O N V S T ㊁A D -F R S T D A T E 等相关引脚,采用控制C O N V S T 信号的方式来完成模拟量到数字量的转换和数字量的采集功能,对采集到的数字量进行相关处理后发送至光模块㊂(6)光纤收发电路光纤收发电路由A gi l e n t 公司生产的820n m 的微型光纤组件H F B R2412㊁H F B R1414和外围电路组成[7],系统主要对其外围电路进行设计,该电路能够为系统提供成本效益高㊁传输距离远㊁高性能㊁高可靠性的光纤通信链路㊂2.2 F P G A 程序设计系统基于模块化思想设计了F P G A 程序,主要包括N I O S _E 4㊁A D C _S AM P L E ㊁D A T A _P R O ㊁c r c _r o m ㊁s i n 240a ㊁u a r t _s e n ㊁u a r t _m a n ㊁a l t p l 10和o pt _s e l 九大模块,系统简化的R T L 级电路框图如图3所示㊂图3 系统简化的R T L 级电路框图a l t pl 10通过对外部50MH z 时钟分频为系统各个模块提供时钟信号㊂A D C _S AM P L E 模块主要实现对两片A /D 时序的控制和数据的采集,将采集到的数据按照积分公式还原出原始信号,通过数据总线传输至D A T A _P R O 模块进一步处理㊂D A T A _P R O 模块通过地址从c r c _r o m 模块中获取c r c 码来完成对原始信号C R C 校验的数据组帧,同时通过地址从s i n 240a 模块中获取相关的积分参数用于发送至A D C _S AM P L E 模块中完成原始信号的积分计算,最终将c r c 校验组帧的数据和相关参数数据按照F T 3格式组成新的数据,通过u a r t _s e n ㊁u a r t _m a n 和o p t _s e l 模块发送到综合管理单元㊂N I O S _E 4模块主要负责整个系统的调度㊁数据读写仲裁,将D A T A _P R O 模块发送的采样间隔㊁幅值㊁相位㊁零漂等参数通过S P I 总线保存至F L A S H 中㊂2.3 采集单元参数配置采集单元的参数配置主要包括采样间隔㊁幅值㊁相位㊁零漂等参数,配置界面如图4所示㊂具体配置如下:a .用信号源在v i n +和v i n -端加标准的2V 交流信号㊂设置通信口单击 打开串口 按键,打开串口,然后点击调试压板按键,将插件设置为调试模式,将拨码开关拨到E 4档㊂c .通过配合I E C 61850报文监视分析工具,可进行幅值㊁相位㊁零漂等参数调整㊂d .可通过工具对采样间隔㊁波特率㊁去零漂方式㊁定时方式等进行设置㊂e .调试完成后点击 保存参数 按钮,然后断电重新启动,可以通过 读取参数 按钮对配置参数进行校验㊂图4 配置界面3 系统测试和分析为了证明系统的工程应用价值,需要对系统的各项参数㊁功能以及电磁兼容性能指标进行验证,对双A /D 采样的小信号精度进行测试㊂测试方法如下:将电流采集单元用光纤分别连接对应的收发信号,同时通过网口㊁串口连接电脑和综合监测单元,测试中将电流信号量同时接入标准信号转换装置和互感器校验仪,标准信号转换装置出来的小电压信号接入采集单元,试验过程中分别监视采集单元的比差和相差,保护电流试验结果如表2所列,测试电流试验结果如表3所列㊂表2 保护电流试验结果通信规约通道施加量值比差/%相差/(')曼码A D 1100%I n +0.22+3A D 2100%I n +0.28+4异步A D 1100%I n +0.21+1A D 2100%I n+0.28+2同时对系统的电磁兼容性能指标进行了测试,并对测试结果进行了分析,系统电磁兼容各项性能指标满足要求㊂测试结果表明,系统保护电流采集和测试电流采集在曼码和异步的条件下,比差和相差都满足系统指标要求,装置在测试过程中通信正常,系统工作可靠㊁稳定,能够满足系统的各项参数要求[8]㊂表3 测试电流试验结果通信规约施加量值比差/%相差/(')曼码1%I n +0.02+55%I n+0.01+220%I n+0.01+2100%I n +0.01+2120%I n +0.01+2异步1%I n +0.05-15%I n+0.01+120%I n+0.01+1100%I n -0.01+1120%I n+0.01+14 结 语本文提出的基于F P G A 的双A /D 小信号采集方案能够完全满足电力系统对电流测试精度的要求,该方案电路实现简单,测试精度高,为小信号采集设计方案提供了一定的参考价值㊂文中对整个方案进行了详细的阐述,同时也对系统进行了详细的测试,实验结果表明该方案具有较高的工程应用价值㊂参考文献[1]江燕良,李莎莎,王淇森.一种避雷器在线监测装置实现方案的研究[J ].电子设计工程,2019,27(14):121125.[2]胡益诚,张晓曦,代明清,等.基于D S P 与F P G A 的信号采集系统设计[J ].信息通信,2019(4):8688.[3]张甜甜.基于A D 7862的模拟电流采集设计与F P G A 编程实现[J ].电子技术与软件工程,2018(16):8485.[4]江燕良,王振华,李莎莎.一种基于F P G A 的智能传感器采集单元的设计[J ].电子设计工程,2018,26(10):155159.[5]张岩,伍春,赵志坤.基于F P G A 的多通道数据采集卡的方案设计[J ].东北师大学报(自然科学版),2016,48(4):6367.[6]王水鱼,王伟.基于A D 7606的智能电网数据采集系统设计[J ].微型机与应用,2016,35(22):810.[7]郭震,吕玄兵,吴雪玲.基于K 60与F P G A 的电子式互感器采集单元的实现[J ].信息技术,2014(4):104106,110.[8]郭亮,卫一然,甄国涌.基于F P G A 的高速数据采集系统设计实现[J ].计算机测量与控制,2013,21(2):537539.靳鹏飞(初级工程师)㊁王振华(高级工程师)㊁贺渊明(高级工程师)㊁郭震(工程师),主要研究方向为变电站二次系统开发㊂(责任编辑:薛士然 收稿日期:2020-08-14)。

FPGA基于NIOS的串口远程升级

FPGA基于NIOS的串口远程升级--By 骏龙Ted.Gao 本文介绍一种基于串口远程升级FPGA的方法,FPGA运行NIOS,上位机通过串口连接NIOS对FLASH进行操作,上传用户的新FPGA设计,通过擦除重写FLASH,来达到更新FPGA程序的目的。

有需要请联系:QQ:765517041tedgao@;765517041@;1. 实验要求以及方案信息 (2)2. 参考例程文件 (2)3. 框图 (3)4. 例程设置 (3)4.1下载文件生成 (3)4.2下载文件合成 (4)4.3下载FPGA镜像和nios ii 软件镜像 (6)4.4生成升级RPD文件 (7)5. 运行 (8)6. 实际应用 (11)6.1 修改例程 (11)6.2 实际应用操作 (13)6.3 实际应用容易出现的问题以及避免 (14)7. 常见错误/问题 (15)7.1 新建NIOS II 软件程序 (15)7.2 Scanf函数 (16)7.3 UART指向 (17)7.4 写保护开关 (18)7.5 Remote Update IP (19)7.6 数据截取文件从RPD而非JIC (20)7.7 SOF、JIC、ELF、HEX (20)7.8 NIOS调试以及下载 (21)1.实验要求以及方案信息实现本文实验的要求:➢Cyclone IV EP4CE10E22C8 开发板➢Intel Quartus Prime 17.1➢USB转RS232 串口线➢二进制/十六进制文本编辑器方案信息:➢占用资源:LE≤3610、PLL 1个、Memory 87056bits➢Flash型号:MT25QL128ABA1ESE-0SIT 128MB SOP-82.参考例程文件参考例程包含一个原厂镜像(Factory Image),两个应用镜像(Application Image),以及各自对应的NIOS软件程序(NIOS II Software)。

QuartusII12.0使用指南2

一、建立QuartusII工程1、双击QuartusII桌面图标打开软件,如下图所示,234体命名,注意:路径中不要出现中文,命名时不要出现空格,最好使用有意义的命名,尽量不要使用123、abc、mydesign等,一般第三行命名默认和第二行一致,本例用led,读者可以类比填写,然后“Next”,如下图所示,56速度等级为8,型号为EP4CE10E22C8,然后点击“Next”,如下图所示,7891011121 /*2 * File :led3 * Description :4 * Author : XiaomaGee@5 * Copyright :6 *7 * History8 **--------------------9 * Rev : 0.0010 * Date : 05/9/201211 *12 * create.13 **--------------------14 */15 module led(clk,16 led17 );1819 input clk;2021 output led;2223 wire rst_n;24 reg led;25 reg[23 : 0] counter;2627 always@(posedge clk or negedge rst_n)28 if (!rst_n)29 counter <= 0;30 else31 counter <= counter + 1;3233 always@(posedge clk or negedge rst_n)34 if (!rst_n)35 led <= 0;36 else if (counter == 24 'hffffff)37 led<=~led;3839 assign rst_n=1;4041 endmodule4213141516、综合分析完成后出现下图,点击“OK”,如下图所示,17、选择“Assignments->pin planer“,进行分配引脚,如下图所示,18时钟线clk连接在FPGA的23脚,所以选择pin23,如下图所示,19接关闭引脚分配界面即可,如下图所示,202122tri-stated”,如下图所示,23中(双击后即可显示下拉菜单)都选择“Use as regular I/O”,点击“OK”,24直接点击“OK”,如下图所示,25二、用USB线和USB-Blaster把电脑和iCore板连接(USB供电,USB-Blaster 用于下载)。

ep ce 官方原理图

CONTENTCover Page, Placement,TOPSDRAM, EEPROMCLOCK, LED, BUTTON,SW, GPIOs, 2X13 HEADER, G-SENSOR, ADC POWER 1.2V, 2.5V, 3.3VCyclone IV EP4CE22 BANK1..BANK8 , POWER , CONFIGTitle Size Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic. All rights reserved.BTitle Size Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic. All rights reserved.BDRAM_DQ[15..0]DRAM_DQ[15..0]DRAM_ADDR[12..0]DRAM_DQM[1..0]KEY[1..0]SW[3..0]LED[7..0]DRAM_BA0DRAM_BA1DRAM_CAS_N DRAM_RAS_N DRAM_WE_N DRAM_CS_N DRAM_CKE DRAM_CLK JTAG_TMS JTAG_TCK JTAG_TDI JTAG_TDO NSTATUS CONF_DONE NCONFIG NCEI2C_SCLK I2C_SDAT G_SENSOR_CS_N G_SENSOR_INTI2C_SDATI2C_SCLK I2C_SDAT G_SENSOR_CS_N G_SENSOR_INT ADC_SDAT ADC_CS_N ADC_SADDR ADC_SCLKCLOCK_50GPIO_0_IN[1..0]GPIO_0[33..0]GPIO_1_IN[1..0]GPIO_1[33..0]GPIO_2_IN[2..0]GPIO_2[12..0]TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B PAGE 4 - 802 EP4CE22NSTATUS NCENCONFIGTDI TMS TDOTCK CONF_DONELED[7..0]SW[3..0]ADC_SCLK KEY[1..0]CLOCK_50DRAM_BA0DRAM_BA1DRAM_CKE DRAM_CLK DRAM_ADDR[12..0]DRAM_DQ[15..0]DRAM_DQM[1..0]G_SENSOR_INT DRAM_CAS_N ADC_SADDR DRAM_WE_N DRAM_CS_N ADC_CS_N G_SENSOR_CS_N ADC_SDAT DRAM_RAS_N I2C_SDATI2C_SCLK GPIO_1_IN[1..0]GPIO_0[33..0]GPIO_2_IN[2..0]GPIO_1[33..0]GPIO_0_IN[1..0]GPIO_2[12..0]DRAM_DQ[15..0]I2C_SDATPAGE 1405 POWERPAGE 9 - 1103 IN/OUT G_SENSOR_INT ADC_SADDR G_SENSOR_CS_N I2C_SDATI2C_SCLK GPIO_1_IN[1..0]GPIO_0[33..0]GPIO_2_IN[2..0]GPIO_0_IN[1..0]GPIO_1[33..0]GPIO_2[12..0]BANK 1BANK 2KEY1DRAM_DQ3DRAM_DQ6DRAM_DQ5DRAM_DQ4DRAM_DQ15DRAM_ADDR0DRAM_ADDR12DRAM_ADDR11DRAM_ADDR9DRAM_ADDR8DRAM_ADDR10LED5SW0LED7G_SENSOR_CS_N LED[7..0]G_SENSOR_INT KEY[1..0]DRAM_ADDR[12..0]DRAM_DQ[15..0]SW[3..0]DRAM_RAS_N DRAM_CAS_N Size Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.TitleDate:No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B U1AEP4CE22F17DQS2L/CQ3L,CDPCLK0DIFFIO_L3p DIFFIO_L4N IO1_0G5DIFFIO_L5p DIFFIO_L5nDIFFIO_L6p/DQS0L/CQ1L,DPCLK0DIFFIO_L6nCLK1/DIFFCLK_0nE1IO/VREFB1N0F3U1BEP4CE22F17DIFFIO_L7p/DQ1L J2DIFFIO_L7n/DQ1L J1DIFFIO_L10p K2DIFFIO_L10n/DQ1L K1DIFFIO_L11p/DQS1L/CQ1L#,DPCLK1L2DIFFIO_L11n/DQ1L L1DIFFIO_L13p/DQ1L N2DIFFIO_13n/DQ1L N1DIFFIO_L15p/DQ1LP2DIFFIO_L15n/DM1L/BWS#1L P1IO2_0/DQS3L/CQ3L#,CDPCLK1R1RUP1/DQ1L K5RDN1/DQ1L L4IO/VREFB2N0L3CLK2/DIFFCLK_1pM2CLK3/DIFFCLK_1nM1BANK 3BANK 4DRAM_DQ8DRAM_DQ9GPIO_114GPIO_112GPIO_111GPIO_16GPIO_19GPIO_18GPIO_14GPIO_13GPIO_15GPIO_12GPIO_11GPIO_17SW1CLOCK_50DRAM_CLK DRAM_DQ[15..0]DRAM_DQM[1..0]GPIO_1[33..0]GPIO_1_IN[1..0]DRAM_BA1DRAM_CKEDRAM_CS_N TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B U1CEP4CE22F17DIFFIO_B1p DIFFIO_B1n/DM3B/BWS#3B DIFFIO_B2p/DQ3B DIFFIO_B2nIO3_0/DQS1B/CQ1B#,CDPCLK2T2PLL1_CLKOUTp R4PLL1_CLKOUTn T4DIFFIO_B4p/DQ3B DIFFIO_B4n/DQ3BIO3_1/DQ3B M6IO/VREFB3N0P6DIFFIO_B5p/DQS3B/CQ3B#,DPCLK2DIFFIO_B6p/DQ3B DIFFIO_B6nDIFFIO_B7p/DQ3B DIFFIO_B7n IO3_2/DQ3B L7DIFFIO_B8p/DQ3BDIFFIO_B8n/DQS5B/CQ5B#,DPCLK3DIFFIO_B9n/DQ3BDIFFIO_B10n/DM5B/BWS#5B DIFFIO_B11p/DQ5B DIFFIO_B12n/DQ5BCLK14/DIFFCLK_6n T8CLK15/DIFFCLK_6p R8U1DEP4CE22F17DIFFIO_B14n/DQ5B N9DIFFIO_B16p/DQ5BR10DIFFIO_B16n/DQS4B/CQ5B,DPCLK4T10DIFFIO_B17p/DQ5B R11DIFFIO_B17n T11DIFFIO_B18p/DQ5B R12DIFFIO_B18n/DQ5B T12IO4_0/DQS2B/CQ3B,DPCLK5P9IO/VREFB4N0P11DIFFIO_B20pR13DIFFIO_B20n/DQ5B T13RUP2M10RDN2N11DIFFIO_B23p/DQ5BT14DIFFIO_B23n/DQS0B/CQ1B,CDPCLK3T15DIFFIO_B24p N12PLL4_CLKOUTpP14PLL4_CLKOUTnR14CLK12/DIFFCLK_7nT9CLK13/DIFFCLK_7p R9BANK 5BANK 6GPIO_2_IN2GPIO_24GPIO_23GPIO_28GPIO_29GPIO_212GPIO_211GPIO_127GPIO_120GPIO_126SW3GPIO_1[33..0]KEY[1..0]GPIO_2_IN[2..0]GPIO_2[12..0]SW[3..0]TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B EP4CE22F17RUP3/DM1R/BWS#1R N14RDN3/DQ1R P15DIFFIO_R15n/DQS3R/CQ3R#,CDPCLK4DIFFIO_R15p/DQ1R DIFFIO_R13n/DQ1R DIFFIO_R13p/DQ1R IO/VREFB5N0L14DIFFIO_R12p/DQ1R DIFFIO_R11n/DQ1R DIFFIO_R11p DIFFIO_R10n/DQ1R DIFFIO_R10p/DQS1R/CQ1R#,DRCLK6DIFFIO_R9n/DEV_OE DIFFIO_R9p/DEV_CLRn DIFFIO_R8n/DQ1R DIFFIO_R7n/DQ1RCLK6/DIFFCLK_3p M15CLK7/DIFFCLK_3nM16U1FEP4CE22F17DIFFIO_R5n/INIT_DONE G16DIFFIO_R5p/CRC_ERROR G15IO6_0DIFFIO_R4n/nCEO F16DIFFIO_R4p/CLKUSRF15IO6_1/DQS0R/CQ1R,DPCLK7IO/VREFB6N0IO6_2IO6_3/PADD23DIFFIO_R1n/PADD20/DQS2R/CQ3R,CDPCLK5C16DIFFIO_R1pC15CLK4/DIFFCLK_2p CLK5/DIFFCLK_2nBANK 7BANK 8GPIO_027GPIO_026GPIO_028GPIO_020GPIO_021GPIO_016GPIO_010GPIO_013GPIO_014GPIO_07GPIO_08GPIO_011GPIO_05GPIO_06GPIO_02GPIO_03GPIO_017GPIO_012GPIO_20SW2GPIO_2[12..0]LED[7..0]SW[3..0]ADC_SCLK ADC_SDATGPIO_0[33..0]GPIO_0_IN[1..0]TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B U1HEP4CE22F17DIFFIO_T11p/PADD17/DQS5T/CQ5T#,DPCLK10C8IO8_0/DQ3T DIFFIO_T10n/DATA2/DQ3T E8DIFFIO_T10p/DATA3F8DIFFIO_T9n/PADD18/DQ3T A7DIFFIO_T9p/DATA4/DQ3T B7IO/VREFB8N0DIFFIO_T7n/DATA14/DQS3T/CQ3T#,DPCLK11A6DIFFIO_T7p/DATA13/DQ3T B6IO8_1/DATA5/DQ3T DIFFIO_T6p/DATA6/DQ3T E6DIFFIO_T5n/DATA7/DQ3T A5DIFFIO_T5p/DATA8/DQ3T B5DIFFIO_T4n/DATA9D6DIFFIO_T3n/DATA10/DM3T/BWS#3T A4DIFFIO_T3p/DATA11B4DIFFIO_T2n A2DIFFIO_T2pA3IO8_2IO8_3/DATA12PLL3_CLKOUTp PLL3_CLKOUTn CLK11/DIFFCLK_4p CLK10/DIFFCLK_4nEP4CE22F17DIFFIO_T24n DIFFIO_T24p/DQ5T DIFFIO_T23nDIFFIO_T23p/DQS0T/CQ1T,CDPCLK6DIFFIO_T22nDIFFIO_T22p/DQ5T PLL2_CLKOUTn A14PLL2_CLKOUTp B14RUP4E11RDN4E10DIFFIO_T21n/DQ5T DIFFIO_T21p/DQ5T DIFFIO_T20n/DQ5TDIFFIO_T20p/PADD0/DQ5T IO/VREFB7N0C11DIFFIO_T19n/PADD1DIFFIO_T17p/PADD4/DQS2T/CQ3T,DPCLK8DIFFIO_T16n/PADD5/DQ5T DIFFIO_T16p/PADD6/DQ5T DIFFIO_T15n/PADD7/DQ5T DIFFIO_T15p/PADD8/DM5T/BWS#5TDIFFIO_T13p/PADD12/DQS4T/CQ5T,DPCLK9CLK9/DIFFCLK_5p B9CLK8/DIFFCLK_5nA9POWER & GNDCONFIGURATIONAS Fast POR configuration at 3.0- or 2.5-VTDOTCKDCLK ASDO NCSO DATA0NSTATUS NCENCONFIG TDI TMS TDO TCK CONF_DONEVCC1P2VCCD_PLL VCC2P5VCCA VCCD_PLLVCCA VCC3P3VCC3P3VCCAVCCAVCC3P3TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B U1JEP4CE22F17TCK H3TMS J5TDI H4TDO J4DCLK H1nSTATUS F4nCONFIG H5nCE J3ASDO C1nCSO D2DATA0H2CONF_DONEH14MSEL0H13MSEL1H12MSEL2G12R100DNIC200.1uR90C260.1uC320.1uR4TBD DNIC190.1uC240.1uC890.1uC220.1uC210.1uC3510uC280.1uL2BEADL1BEADC310.1uC300.1uEP4CE22F17G N D G N D L 9G N D L 10G N D L 11G N D K 12G N D G 11G N D B 2G N D B 15G N D C 5G N D C 12G N D D 7G N DD 10GND E4GND E13GND G4GND G13GND K4GND K13GND M4GND M13GND N7GND N10GND P5GND P12GND R2GND R15GND E2GND H16GND H15GNDA1M5GNDA2E12GNDA3E5GNDA4M12V C C I O 4V C C I O 5V C C I O 5V C C I O 6V C C I O 6V C C I O 7V C C I O 7V C C I O 7V C C I O 8V C C I O 8V C C I O 8C3610uC290.1uC37TBDDNIR71KR80DNIC230.1uC330.1uC18100uR20DNIC250.1uR10C340.1uR111KDNIC270.1uR30LED2LED1LED3LED0LED4LED7LED6LED5KEY0KEY1CLOCK_50KEY[1..0]VCC2P5VCC2P5VCC3P3VCC2P5VCC2P5TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B R132KLED3LEDGY150MHZVCC 4OUT3GND 2EN 1C401nRN212012345678U2SN74AUC171A 12A 33A 54A 95A 116A131Y 22Y 43Y 64Y 85Y 106Y 12GND7VCC 14ETP 15C410.1uLED7LEDGKEY0TACK_SW_RA4321RN112012345678C380.1uR12100KR152K KEY1TACK_SW_RA4321R14100KLED6LEDGLED5LEDG LED4LEDG C391nLED2LEDG ON1SW1SW-DIP812348765LED1LEDGGPIO - 0GPIO - 1GPIO - 2GPIO_032GPIO_031GPIO_07GPIO_012GPIO_0_IN1GPIO_0_IN0GPIO_011GPIO_016GPIO_014GPIO_020GPIO_019GPIO_010GPIO_022GPIO_026GPIO_030GPIO_017GPIO_015GPIO_06GPIO_00GPIO_024GPIO_013GPIO_09GPIO_021GPIO_033GPIO_029GPIO_025GPIO_023GPIO_02GPIO_018GPIO_028GPIO_08GPIO_05GPIO_04GPIO_027GPIO_03GPIO_132GPIO_131GPIO_17GPIO_112GPIO_1_IN1GPIO_1_IN0GPIO_111GPIO_116GPIO_114GPIO_120GPIO_119GPIO_110GPIO_122GPIO_126GPIO_130GPIO_117GPIO_115GPIO_16GPIO_10GPIO_124GPIO_113GPIO_19GPIO_121GPIO_133GPIO_129GPIO_125GPIO_123GPIO_12GPIO_118GPIO_128GPIO_18GPIO_15GPIO_14GPIO_127GPIO_13GPIO_2_IN1GPIO_20GPIO_22GPIO_24GPIO_26GPIO_28GPIO_210GPIO_212GPIO_2_IN0GPIO_2_IN2GPIO_21GPIO_23GPIO_25GPIO_27GPIO_29GPIO_211GPIO_01GPIO_11Analog_In0Analog_In4Analog_In6Analog_In3Analog_In5Analog_In7Analog_In1Analog_In2GPIO_0[33..0]GPIO_0_IN[1..0]GPIO_2[12..0]GPIO_2_IN[2..0]GPIO_1[33..0]GPIO_1_IN[1..0]VCC_SYSVCC3P3VCC_SYSVCC3P3VCC3P3Analog_In[7..0]TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B JP21122334455667788991010111112121313141415151616171718181919202021212222232324242525262627272828292930303131323233333434353536363737383839394040JP32X13 HEADER11223344556677889910101111121213131414151516161717181819192020212122222323242425252626JP11122334455667788991010111112121313141415151616171718181919202021212222232324242525262627272828292930303131323233333434353536363737383839394040Digital AccelerometerADC_IN0ADC_IN1ADC_IN2ADC_IN3ADC_IN4ADC_IN5ADC_IN6ADC_IN7ADC_IN1Analog_In1ADC_IN2Analog_In2ADC_IN3Analog_In3ADC_IN4Analog_In4ADC_IN5Analog_In5ADC_IN6Analog_In6ADC_IN7Analog_In7ADC_IN0Analog_In0G_SENSOR_INTI2C_SCLK I2C_SDATVCC_VSAGNDAGND AGNDAGNDAGNDAGNDAGNDAGNDAGNDAGNDVCC3P3Analog_In[7..0]TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B ADXL345INT18INT29NC 10RESERVED_111SDO_ALT_ADDRESS12SDA_SDI_SDIO 13SCL_SCLK 14R2622R2222C541n C421uR620DNIC530.1uC481nR212.2KDNIR2422C571nR1722R2722C551n R2022R2522C501n C511nR2822C461nC561n R1910KC524.7uDRAM_ADDR3DRAM_ADDR0DRAM_ADDR2DRAM_ADDR1DRAM_ADDR10DRAM_DQM0DRAM_DQ5DRAM_DQ0DRAM_DQ7DRAM_DQ6DRAM_DQ3DRAM_DQ2DRAM_DQ4DRAM_DQ1DRAM_ADDR12DRAM_ADDR5DRAM_ADDR7DRAM_ADDR6DRAM_ADDR8DRAM_ADDR11DRAM_ADDR4DRAM_ADDR9DRAM_DQM1DRAM_DQ8DRAM_DQ15DRAM_DQ11DRAM_DQ9DRAM_DQ10DRAM_DQ13DRAM_DQ14DRAM_DQ12DRAM_DQM[1..0]DRAM_ADDR[12..0]DRAM_CLK DRAM_CKE DRAM_BA0DRAM_BA1DRAM_WE_N DRAM_CAS_N DRAM_RAS_N DRAM_CS_N VCC3P3TitleCopyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.U5SDRAM 16Mx16A023A124A225A326A429A530A631A732A833A934nCAS 17nRAS 18LDQM 15nWE 16nCS 19CKE 37CLK 38UDQM 39D02D14D25D37D48D510D611D713D842D944D1045D1147D1248D1350D1451D1553A1236BA020V D D 1V D D27V S S 28V S S 41A1022V D D Q 3V D D Q 9V D D Q 43V D D Q49V S S Q 6V S S Q 12V S S Q 46V S S Q52A1135BA121V S S54V D D 14C620.1uC630.1uC580.1uC640.1uC590.1uC600.1uC610.1uI2C ADDRESS W/R = 0xA0/0xA1I2C_SCLK I2C_SDATVCC3P3VCC3P3VCC3P3VCC3P3TitleCopyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R351KR30R34C650.1uR332K R310DNIA1A0VSS A2VCC SDASCL WP U624LC02B456871239R361K R322KVCC_SYS Range: 3.3 ~ 5.5 V2.5V/150mA1.2V/1.5AInput Power Range: VCC2P5VCC3P3VCC3P3VCC1P2VCC_SYSVCC3P3VCC1P2TitleSize Date:Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.B 10uC7210uR450DNIFID6REG2LP5900SD-2.5VIN6G N D3VOUT 1VEN 4P A D7NC12NC25C690.47uC7310uD7PMEG2010AEBFID7R381.2KR494.99KREG3LP38500SD-ADJIN 2IN 3IN4G N D 1OUT 5OUT 6OUT 7ADJ8D A P9C740.1uC700.47uFID5J2SIP2DNI12FID8R484.99KLP38500SD-ADJG N D 1ADJD A P90.1u10uR4710K5.36KD6PMEG2010AEBSIP2DNIR46C710.1uR610D8PMEG2010AEB。

FPGA可编程逻辑器件芯片EP4CE10E22C8N中文规格书

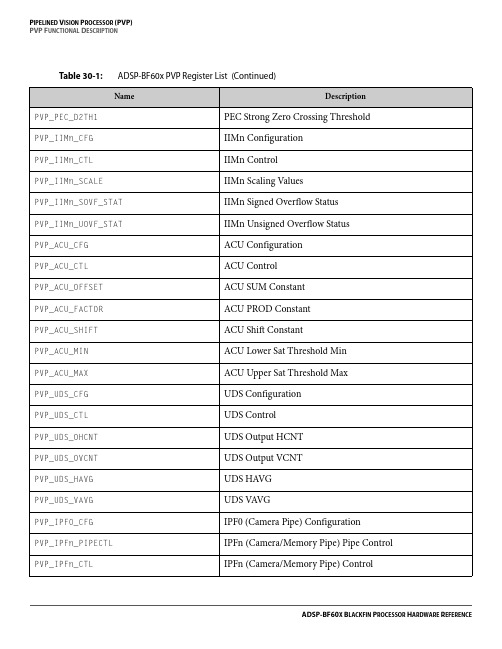

Table 30-1:ADSP-BF60x PVP Register List (Continued)Name DescriptionPVP_PEC_D2TH1PEC Strong Zero Crossing Threshold PVP_IIMn_CFG IIMn ConfigurationPVP_IIMn_CTL IIMn ControlPVP_IIMn_SCALE IIMn Scaling ValuesPVP_IIMn_SOVF_STAT IIMn Signed Overflow StatusPVP_IIMn_UOVF_STAT IIMn Unsigned Overflow StatusPVP_ACU_CFG ACU ConfigurationPVP_ACU_CTL ACU ControlPVP_ACU_OFFSET ACU SUM ConstantPVP_ACU_FACTOR ACU PROD ConstantPVP_ACU_SHIFT ACU Shift ConstantPVP_ACU_MIN ACU Lower Sat Threshold MinPVP_ACU_MAX ACU Upper Sat Threshold MaxPVP_UDS_CFG UDS ConfigurationPVP_UDS_CTL UDS ControlPVP_UDS_OHCNT UDS Output HCNTPVP_UDS_OVCNT UDS Output VCNTPVP_UDS_HAVG UDS HAVGPVP_UDS_VAVG UDS V AVGPVP_IPF0_CFG IPF0 (Camera Pipe) ConfigurationPVP_IPFn_PIPECTL IPFn (Camera/Memory Pipe) Pipe Control PVP_IPFn_CTL IPFn (Camera/Memory Pipe) ControlTable 30-1:ADSP-BF60x PVP Register List (Continued)Name Description PVP_CNVn_C40C41CNVn Coefficients 4,0 and 4,1 PVP_CNVn_C42C43CNVn Coefficients 4,2 and 4,3 PVP_CNVn_C44CNVn Coefficient 4,4PVP_CNVn_SCALE CNVn Scaling FactorPVP_THCn_CFG THCn ConfigurationPVP_THCn_CTL THCn ControlPVP_THCn_HFCNT THCn Histogram Frame Count PVP_THCn_RMAXREP THCn Max RLE ReportsPVP_THCn_CMINVAL THCn Min Clip ValuePVP_THCn_CMINTH THCn Clip Min ThresholdPVP_THCn_CMAXTH THCn Clip Max ThresholdPVP_THCn_CMAXVAL THCn Max Clip ValuePVP_THCn_TH0THCn Threshold Value 0PVP_THCn_TH1THCn Threshold Value 1PVP_THCn_TH2THCn Threshold Value 2PVP_THCn_TH3THCn Threshold Value 3PVP_THCn_TH4THCn Threshold Value 4PVP_THCn_TH5THCn Threshold Value 5PVP_THCn_TH6THCn Threshold Value 6PVP_THCn_TH7THCn Threshold Value 7PVP_THCn_TH8THCn Threshold Value 8PVP_THCn_TH9THCn Threshold Value 9P IPELINED V ISION P ROCESSOR (PVP)PVP F UNCTIONAL D ESCRIPTIONADSP-BF60x PVP Interrupt List PVP_THCn_HCNT7_STATTHCn Histogram Counter Value 7PVP_THCn_HCNT8_STATTHCn Histogram Counter Value 8PVP_THCn_HCNT9_STATTHCn Histogram Counter Value 9PVP_THCn_HCNT10_STATTHCn Histogram Counter Value 10PVP_THCn_HCNT11_STATTHCn Histogram Counter Value 11PVP_THCn_HCNT12_STATTHCn Histogram Counter Value 12PVP_THCn_HCNT13_STAT THCn Histogram Counter Value 13PVP_THCn_HCNT14_STATTHCn Histogram Counter Value 14PVP_THCn_HCNT15_STATTHCn Histogram Counter Value 15PVP_THCn_RREP_STATTHCn Number of RLE Reports PVP_PMA_CFG PMA ConfigurationTable 30-2:ADSP-BF60x PVP Interrupt List Interrupt List Description Interrupt ID DMA Channel Sensitivity PVP0 Camera Pipe DataOut B DMA Channel11138LEVEL PVP0 Camera Pipe DataOut C DMA Channel11239LEVEL PVP0 Camera Pipe StatusOut DMA Channel 11340LEVEL PVP0 Camera Pipe Control In DMA Channel 11441LEVELPVP0 Status 0115LEVEL PVP0 Memory Pipe DataOut DMA Channel 11642LEVELTable 30-1:ADSP-BF60x PVP Register List (Continued)Name Description。

基于DSP+FPGA的云台控制电路设计

基于DSP+FPGA的云台控制电路设计原东阳;洪华杰;杜卯春【摘要】根据云台系统对传感器采集量实时性和快速性要求,在传统云台单处理器控制电路的基础上,设计了以DSP芯片TMS320F28335为伺服控制核心及FPGA 芯片EP4CE10E22C8为外设管理核心的一种新型云台伺服控制电路,给出了该控制电路重要部分的芯片选型及电路设计原理,并采用模块化编程完成相应软件设计.实验中通过分析绝对式编码器信号采集等关键模块的时序信息,准确计算数据刷新频率和并行通信周期,证明该设计可以有效提高处理器获取云台位置及姿态信息的时效性,验证了控制电路的科学性和合理性,同时具有高集成度、功能可拓展等优点.【期刊名称】《测控技术》【年(卷),期】2019(038)003【总页数】6页(P126-130,134)【关键词】云台控制;FPGA;DSP;高实时性;电路设计【作者】原东阳;洪华杰;杜卯春【作者单位】国防科技大学智能科学学院,湖南长沙410073;国防科技大学智能科学学院,湖南长沙410073;国防科技大学智能科学学院,湖南长沙410073【正文语种】中文【中图分类】TP23随着计算机技术、自动控制技术和图像处理技术的快速发展,通过云台安装视觉跟踪装置、对近地目标进行捕捉辨识的无人机系统应运而生,且广泛地应用在精确制导、公路巡航、反恐防暴和抗灾救援等场合[1] 。

其中,稳定云台系统作为搭载任务挂载的平台,是无人机的一个重要组成部分[2]。

沈阳航空航天大学的冯志刚,设计基于ARM的硬件平台,运用神经网络云台控制技术,云台的姿态角度误差在±5°以内[3] ;南京理工大学的王娜,在分析无人机云台控制系统功能需求的基础上,提出了一种以STM32F407VGT6为核心的双处理器硬件设计方案,可以提高整体系统控制的实时性[4];来自北京航空精密机械研究所的聂社云等人,设计了一种基于DSP和FPGA的嵌入式运动控制平台,采用FPGA芯片Nios内核为协处理器实现良好的人机交互控制,并成功应用于一体化转台控制系统[5]。

基于嵌入式的多路肌电信号采集系统的设计

基于嵌入式的多路肌电信号采集系统的设计王梦;葛斌;朱政康;师岩琳【摘要】采用直接内存存取 (direct memory access,DMA)和双口随机存取存储器(dual-port random access memory, dual-port RAM)相结合的方式设计了基于嵌入式的多路肌电信号采集系统.该系统由现场可编程门阵列(field-programmable gate array, FPGA)控制模数转换器(ADC)器件的采样时序;ARM 作为主控器件采用DMA方式的数据采集机制,实现了上下位机的高速通信.本研究给出了数据采集接口设计方案,以及Linux操作系统下的DMA驱动程序和控制指令.实验表明该系统在采集肌电信息的同时对肌电信息进行算法处理并实时传输,明显提升了多路肌电信号采集系统的性能.%By adopting the combination of DMA and dual port RAM, we designed a multi-channel electromyographic signal acquisition system based on embedded technology.The sampling sequence of ADC device was controlled by FPGA;As the master device, ARM implementsed the high-speed communication between the up and down machine by using DMA.The paper presentsed a data acquisition interface design scheme, and the DMA driver under Linux and control instruction.Experiment shows that the system can do data acquisition, algorithm processing and real-time transmission at the same time, greatly improves the performance of the multi-channel electromyographic signal acquisition system.【期刊名称】《生物医学工程研究》【年(卷),期】2017(036)001【总页数】5页(P38-42)【关键词】直接内存存取;双口随机存取存储器;实时;肌电信号【作者】王梦;葛斌;朱政康;师岩琳【作者单位】上海理工大学医疗器械与食品学院,上海 200093;上海理工大学医疗器械与食品学院,上海 200093;上海理工大学医疗器械与食品学院,上海 200093;上海理工大学医疗器械与食品学院,上海 200093【正文语种】中文【中图分类】R3181 引言肌电信号(electromyographic signal, EMG)是产生肌肉力的电信号根源,是肌肉中许多运动单元动作电位在时间和空间上的叠加,反映了神经、肌肉的功能状态,在基础医学研究、临床诊断和康复工程中有广泛的应用[1]。

FPGA可编程逻辑器件芯片EP4CE10E22C6N中文规格书

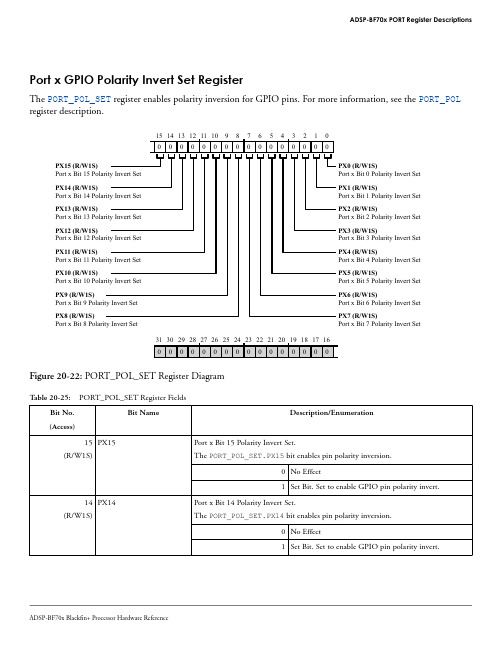

5 PX5 (R/W)

PX5 Data Toggle on Trigger. The PORT_TRIG_TGL.PX5 bit enables triggers to toggle the state of the pin.

4 PX4 (R/W)

PX4 Data Toggle on Trigger. The PORT_TRIG_TGL.PX4 bit enables triggers to toggle the state of the pin.

Bit No. (Access)

Bit Name

Description/Enumeration

10 PX10 (R/W)

PX10 Data Toggle on Trigger. The PORT_TRIG_TGL.PX10 bit enables triggers to toggle the state of the pin.

0 No Effect

1 Set Bit. Set to enable GPIO pin polarity invert.

14 PX14 (R/W1S)

Port x Bit 14 Polarity Invert Set. The PORT_POL_SET.PX14 bit enables pin polarity inversion.

30 PIQ30 (R/W1C)

Pin Interrupt 30 Level. Set the PINT_EDGE_CLR.PIQ30 bit to enable level sensitivity.

29 PIQ29 (R/W1C)

Pin Interrupt 29 Level. Set the PINT_EDGE_CLR.PIQ29 bit to enable level sensitivity.

Altera(Intel)FPGA全系列芯片选型手册

逻辑元 LAB/C 总 RAM I/O 件/单元 LB 数 位数 数 数 392 72 291 291 288 392 72 288 321 321 288 291 288 6272 276480 576 2910 2910 12288 59904 59904

291 321 6 423936 6272 276480 576 12288

4608 119808 4608 119808

Cyclone® IV E ACEX-1K® Cyclone® Cyclone® Cyclone® III Cyclone® Cyclone® II Cyclone® Cyclone®

100-TQFP 256-LBGA

100-TQFP EP1C3T100I7N (14x14) EP3C5F256C8N EP4CE6F17C7N

下载 下载 下载

查询 查询 查询 查询 查询 查询

256-FBGA (17x17) 256-FBGA 256-LBGA (17x17) 144-TQFP 144-LQFP (20x20) 208-PQFP 208-BFQFP (28x28) 208-BFQFP

下载

查询 查询 查询 查询 查询 查询 查询 查询 查询

144-TQFP EP1K30TC144-3N 下载 (20x20) 144-TQFP EP1C6T144C8N 下载 (20x20) 100-TQFP EP1C3T100I7 (14x14) 256-UBGA (14x14) 144-TQFP (20x20) 144-TQFP (20x20) 324-FBGA (19x19) 144-TQFP (20x20) EP3C5U256C8N EP1C3T144C6N EP2C8T144C8N EP1C4F324C8N EP1C6T144C8 下载 下载 下载 下载 下载 下载

基于超声多普勒原理的血压测量系统申屠蛟龙艾信友范兵兵曾研

基于超声多普勒原理的血压测量系统申屠蛟龙艾信友范兵兵曾研文章设计了基于超声多普勒原理的血压测量的系统,使用气袖控制给定频率的外部压力变化,通过FPGA接收各传感器采集的数据并处理分析,通过LCD1602显示舒张压与收缩压,从而实现超声对血压的测量。

标签:FPGA;VeriLog HDL;超声多普勒;压力传感器Abstract:In this paper, a blood pressure measurement system based on ultrasonic Doppler principle is designed. The external pressure change of given frequency is controlled by air sleeve. The data collected by various sensors are received and analyzed by FPGA. Diastolic and systolic blood pressure is displayed by LCD1602,in order to realize ultrasound blood pressure measurement.Keywords:FPGA;VeriLog HDL;ultrasonic Doppler;pressure sensor 引言随着社会经济的迅猛发展,人们的生活方式比起以前有了重大的改变,加上人口日益增多并且日趋高龄化,随之而起的健康养生意识逐渐受到大家重视,人们对医疗的追求越来越高,更加追求便捷化,家庭化的医疗设备。

有助于人们了解更多关于自身健康方面的状况。

1 系统概述本设计把FPGA作为处理芯片,压力传感器和超声多普勒传感器为数据的采集端,LCD1602为显示端。

系统结构图如图1所示。

2 硬件设计本设计的硬件主要包括FPGA处理模块、气袖压力控制模块、压力传感器模块、超声多普勒传感模块。

芯片封装 npe

芯片封装 npe(实用版)目录1.芯片封装的概念与重要性2.芯片封装的主要类型3.NPE 在芯片封装中的应用4.NPE 的优势与挑战5.我国在芯片封装领域的发展现状与前景正文一、芯片封装的概念与重要性芯片封装是指将集成电路芯片安装在载体上,并通过引线与其他电子元件连接的过程。

它对于保护芯片、提高散热性能、实现电气连接以及确保信号传输的稳定性具有至关重要的作用。

随着科技的飞速发展,芯片封装技术也在不断进步,以满足电子产品日益小型化、高性能和高可靠性的需求。

二、芯片封装的主要类型常见的芯片封装类型包括:引线框架封装(Lead Frame Package,LFP)、塑料封装(Plastic Package,PP)、陶瓷封装(Ceramic Package,CP)、金属封装(Metal Package,MP)、和覆铜载板封装(Embedded Package,EP)等。

这些封装类型各具特点,分别适用于不同的应用场景。

三、NPE 在芯片封装中的应用PE(Negative Pressure Encapsulation,负压封装)是一种先进的芯片封装技术。

其主要原理是在负压环境中进行封装,以实现更好的密封性能和更高的可靠性。

NPE 技术广泛应用于高性能、高可靠性的芯片产品中,如:微处理器、内存条、通讯芯片等。

四、NPE 的优势与挑战PE 技术具有以下优势:1.良好的密封性能,提高了芯片的防护能力;2.更高的可靠性,降低了故障率;3.更小的尺寸,满足了电子产品轻薄化的需求;4.更高的散热性能,保证了芯片的稳定运行。

然而,NPE 技术也面临一些挑战:1.设备投入成本高,生产成本相对较高;2.技术门槛较高,对生产厂商的技术实力有较高要求;3.负压环境对生产环境要求高,需要严格的无尘控制。

五、我国在芯片封装领域的发展现状与前景近年来,我国在芯片封装领域取得了显著的成果,已成为全球最大的芯片封装生产基地。

我国政府对于集成电路产业的大力支持,以及国内企业在技术创新和市场开拓上的努力,使得我国芯片封装产业不断壮大。

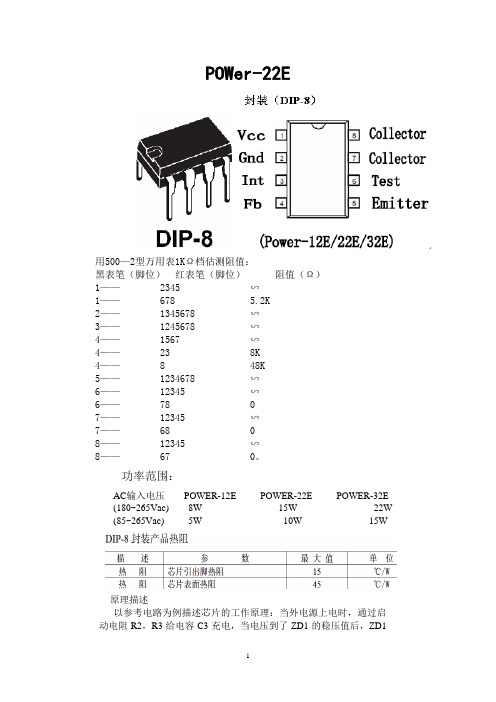

POWer22E

POWer-22E用500—2型万用表1KΩ档估测阻值:黑表笔(脚位)红表笔(脚位)阻值(Ω)1—— 2345 ∽1—— 678 5.2K2—— 1345678 ∽3—— 1245678 ∽4—— 1567 ∽4—— 23 8K4—— 8 48K5—— 1234678 ∽6—— 12345 ∽6—— 78 07—— 12345 ∽7—— 68 08—— 12345 ∽8—— 67 0。

功率范围:AC输入电压POWER-12E POWER-22E POWER-32E (180~265Vac) 8W 15W 22W (85~265Vac) 5W 10W 15W原理描述以参考电路为例描述芯片的工作原理:当外电源上电时,通过启动电阻R2,R3给电容C3充电,当电压到了ZD1的稳压值后,ZD1导通为INT提供电流,电路开启,完成电路的启动;电路开启后,电路进入正激工作状态,反馈绕组由ZD1与R8继续为INT提供电流,维持了电路的开启,由于主电路中电流Ic的增大,在限流电阻R9上的电压升高,并通过C4、R6传到Fb引脚,当电压大于0.7V时,主开关管关闭,电路进入反激工作状态,电路通过D6为C3充电,提供Vdd电压;并完成电路的振荡。

三、产品内部框图:7.5W(5V/1.5A)输出离线式开关电源启动电阻器设计:设计交流输入电压为(80V~264V),由于V DC=1.4*V AC,则对应的直流电压为(112V~370V),由表6可知POWER-22E的启动电流为0.15~1mA,则由欧姆定律R=U/I,最大电阻R max=112/0.15 =746K,最小电阻R min=370/1=370K;所以启动电阻取370K~746K之间的值,取660K电阻,由于1/4W电阻的最高耐电压只有250V,故用两只330K电阻串接以提升耐压。

6.3.2、Vdd电源限流电阻R5的计算。

由表6可知,POWER-22E的I dd电流为50mA~200mA,Vdd电压我们设计在5V,由于主开关管的V be的存在(Vbe=1.5V),由R=U/I可得,R max=(5-1.5)/0.04=70R,R min=23R,参考设计取值为47R。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Altera Device Package Information 04R-00402-2.0

144-Pin Plastic Enhanced Quad Flat Pack (EQFP) - Wire Bond - A:1.65 - D2:5.4 ▪All dimensions and tolerances conform to ASME Y14.5M – 1994.

▪Controlling dimension is in millimeters.

▪Pin 1 may be indicated by an ID dot, or a special feature, in its proximity on package surface.

Note:For more information about the exposed pad pin connection of 144-EQFP package, refer to the specific device pin-out file (https:///support/literature/lit-dp.html)

March 2015 Altera Corporation04R-00402-2.0

04R-00402-2.0 March 2015 Altera Corporation

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html . Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

101 Innovation Drive San Jose, CA 95134

March 2015 Altera Corporation 04R-00402-2.0

Document Revision History

Table 1 shows the revision history for this document.

Table 1. Document Revision History。