SOC基础教程3 组合逻辑(3学时)

数字电路基础教程

A

F ABC

B C

&F

(1-24)

或非:条件

A、B、C任一 具备,则F 不 发生。

A

F ABC B

C

异或:条件

A、B有一个具 备,另一个不 具备则F 发生。

F AB AB AB

A

B C

同或:条件

A、B相同,则 F 发生。

F AB A B A

B

A B

0010

0011 0100 0101 0110 0111 1000

1001

1010 1011 1100 1101 1110 1111

0

0

0

0

1

1

1

1

2

2

2

2

3

3

3

3

0

4

4

4

4

1

5

5

6

6

7

7

8

8

2

3

4

5

5

9

9

6

6

10

7

7

11

5

8

8

12

6

9

9

13

7

14

8

15

9

(1-17)

§1.2 基本逻辑关系

基本逻辑关系:与 ( and )、或 (or ) 非 ( not )。

• 信号放大及运算 (信号放大、功率放大) • 信号处理(采样保持、电压比较、有源滤波) • 信号发生(正弦究的问题

基本电路元件 基本数字电路

• 逻辑门电路 • 触发器

• 组合逻辑电路 • 时序电路(寄存器、计数器、脉冲发生器、

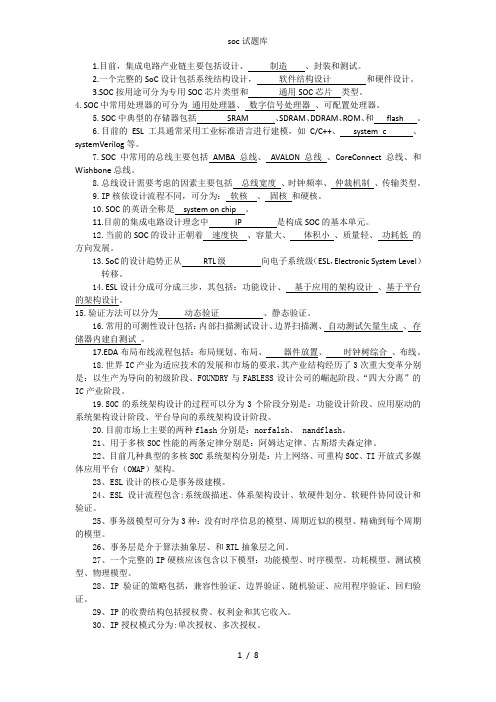

soc试题库

1.目前,集成电路产业链主要包括设计、制造、封装和测试。

2.一个完整的SoC设计包括系统结构设计,软件结构设计和硬件设计。

3.SOC按用途可分为专用SOC芯片类型和通用SOC芯片类型。

4.SOC中常用处理器的可分为通用处理器、数字信号处理器、可配置处理器。

5.SOC中典型的存储器包括SRAM 、SDRAM、DDRAM、ROM、和flash 。

6.目前的ESL工具通常采用工业标准语言进行建模,如C/C++、system c 、systemVerilog等。

7.SOC中常用的总线主要包括AMBA总线、AVALON总线、CoreConnect总线、和Wishbone总线。

8.总线设计需要考虑的因素主要包括总线宽度、时钟频率、仲裁机制、传输类型。

9.IP核依设计流程不同,可分为:软核、固核和硬核。

10.SOC的英语全称是system on chip 。

11.目前的集成电路设计理念中IP 是构成SOC的基本单元。

12.当前的SOC的设计正朝着速度快、容量大、体积小、质量轻、功耗低的方向发展。

13.SoC的设计趋势正从RTL级向电子系统级(ESL,Electronic System Level)转移。

14.ESL设计分成可分成三步,其包括:功能设计、基于应用的架构设计、基于平台的架构设计。

15.验证方法可以分为动态验证、静态验证。

16.常用的可测性设计包括:内部扫描测试设计、边界扫描测、自动测试矢量生成、存储器内建自测试。

17.EDA布局布线流程包括:布局规划、布局、器件放置、时钟树综合、布线。

18.世界IC产业为适应技术的发展和市场的要求,其产业结构经历了3次重大变革分别是:以生产为导向的初级阶段、FOUNDRY与FABLESS设计公司的崛起阶段、“四大分离”的IC产业阶段。

19.SOC的系统架构设计的过程可以分为3个阶段分别是:功能设计阶段、应用驱动的系统架构设计阶段、平台导向的系统架构设计阶段。

20.目前市场上主要的两种flash分别是:norfalsh、 nandflash。

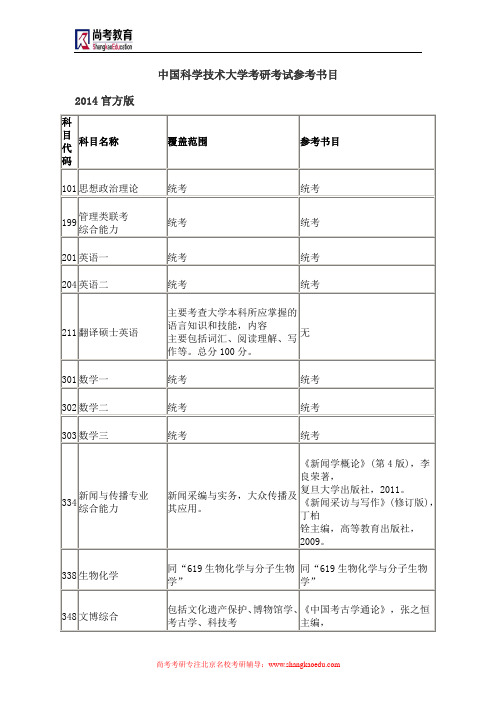

中国科学技术大学考研考试参考书目

统考

302

数学二

统考

统考

303

数学三

统考

统考

334

新闻与传播专业

综合能力

新闻采编与实务,大众传播及其应用。

《新闻学概论》(第4版),李良荣著,

复旦大学出版社,2011。

《新闻采访与写作》(修订版),丁柏

铨主编,高等教育出版社,2009。

338

生物化学

同“619生物化学与分子生物学”

同“619生物化学与分子生物学”

大学出版社2011年版。

615

马克思主义哲

学原理

唯物论、辩证论、认识论、唯物史观。

《辩证唯物主义和历史唯物主义原理》

(第五版),李秀林,人大出版社2004年版。

《马克思主义基本原理概论》,高等教育出

版社。

616

媒介文化

主要包括媒介在文化生产和再生产中的地位;一般

社会理论与一系列有关媒介和信息的传播理论之间

中国科学技术大学考研考试参考书目

2014官方版

科目

代码

科目名称

覆盖范围

参考书目

101

思想政治理论

统考

统考

199

管理类联考

综合能力

统考

统考

201

英语一

统考

统考

204

英语二

统考

统考

211

翻译硕士英语

主要考查大学本科所应掌握的语言知识和技能,内容

主要包括词汇、阅读理解、写作等。总分100分。

无

301

数学一

考查考生灵活运用这些基础知识进行现象的观察

与分析、问题的分析和解决能力,要求考生理解

高分子结构控制和聚合速率控制的基本原理

soc(系统级晶片)详细资料大全

soc(系统级晶片)详细资料大全SoC的定义多种多样,由于其内涵丰富、套用范围广,很难给出准确定义。

一般说来,SoC称为系统级晶片,也有称片上系统,意指它是一个产品,是一个有专用目标的积体电路,其中包含完整系统并有嵌入软体的全部内容。

同时它又是一种技术,用以实现从确定系统功能开始,到软/硬体划分,并完成设计的整个过程。

基本介绍•中文名:系统级晶片•外文名:System on Chip•缩写:SoC•别称:民航SOC英文解析,片上系统,综述,功能,技术发展,技术特点,优势,存在问题,核心技术,设计思想,基本结构,设计基础,设计过程,设计方法学,套用动态, 英文解析SOC,或者SoC,是一个缩写,包括的意思有:1)SoC:System on Chip的缩写,称为晶片级系统,也有称片上系统,意指它是一个产品,是一个有专用目标的积体电路,其中包含完整系统并有嵌入软体的全部内容。

2) SOC: Security Operations Center的缩写,属于信息安全领域的安全运行中心。

3)民航SOC:System Operations Center的缩写,指民航领域的指挥控制系统。

4)一个是Service-Oriented Computing,“面向服务的计算” 5)SOC(Signal Operation Control) 中文名为信号操作控制器,它不是创造概念的发明,而是针对工业自动化现状提出的一种融合性产品。

它采用的技术是正在工业现场大量使用的成熟技术,但又不是对现有技术的简单堆砌,是对众多实用技术进行封装、接口、集成,形成全新的一体化的控制器,可由一个控制器就可以完成作业,称为SOC。

6)SOC(start-of-conversion ),启动转换。

7)short-open calibration 短开路校准。

片上系统System on Chip,简称Soc,也即片上系统。

从狭义角度讲,它是信息系统核心的晶片集成,是将系统关键部件集成在一块晶片上;从广义角度讲,SoC是一个微小型系统,如果说中央处理器(CPU)是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。

SoC架构

精选ppt课件

24

处理器位宽

• 当前高性能嵌入式系统SoC的处理器多为32位处理器。所谓32位处理 器,即处理器内部的寄存器(包括地址寄存器与数据寄存器)位宽最 大为32位。低性能的嵌入式系统SoC一般多采用16位微控制器( micro-controllers),然而,随着工作负载的增加,此类系统逐渐开 始使用32位处理器。可以预见,在不久的将来,伴随高性能及超大存 储空间的需求,64位处理器将逐渐成为主流。

• 多个不同任务同时 操作,使用不同资 源

• 潜在加速比=流水 线级数

• 流水线的速率受限 于最慢的流水段

• 流水段的执行时间 如果不均衡,那么 加速比就会降低

• 开始填充流水线的 时间和最后排放流 水线的时间降低加 速比

• 相关将导致流水线

暂停

27

CPU基本概念

• CISC与RISC • 流水线技术 • 分支预测技术 • 乱序执行技术 • 标量与超标量处理器 • SIMD、MIMD和向量处理器 • VLIW处理器

DDR2 NAND

精选ppt课件

12

SEP0718结构图

LCDC

I2S

HDMI PHY

AUDIO CODEC

GPS CTRL

UART (4)

I2S

BUS5 - APB32

AUDIO

SPI

CODEC

(3)

I2C

BUS3 - AHB32

DOWN SIZER

DMAC2

GPU

PHY

USB OTG

USB DMA

精选ppt课件

28

组合逻辑电路技能训练

组合逻辑电路技能训练训练一用集成逻辑门设计组合逻辑电路一、训练目的1、学习查阅手册,根据设计要求选用集成芯片。

2、熟悉用集成逻辑门设计组合逻辑电路的方法和调试方法。

二、训练内容1、3 个阀门中必须有两个或两个以上开通时才算工作正常,否则不发生正常信号。

试设计一个能发出正常信号的逻辑电路。

2、3个工厂由甲、乙两个变电站供电。

如 1 个工厂用电,则由甲站供电;如两个工厂用电,则由乙站供电;如3 个工厂同时用电,则由甲、乙两个站供点。

试设计一个供电控制电路。

三、预习要求1、用最少的门电路实现要求的逻辑功能。

2、写出设计过程,画出逻辑图,自拟测试调整方法。

3、根据数字集成电路手册选择合适的逻辑门电路。

并画出安装接线图/四、训练要求1、测试、记录电路的逻辑功能,并列出真值表,判断设计是否正确。

2、自行分析、检测和排除训练中出现的故障。

训练二用译码器实现多种逻辑功能一、训练目的1、掌握译码器的功能测试方法。

2、熟悉显示译码器的使用。

3、熟悉译码器的应用。

二、训练内容1、测试显示译码器的逻辑功能,观察数码显示器的显示情况。

2、用4 线—10线译码器构成10 路输出的数据分配器。

3、用3线一8线译码器和与非门实现逻辑函数Y=Aeq \o\ac( O,+)+B eq \o\ac( O,+)+C。

4、用3线—8线译码器和与非门组成一个 1 位二进制全加器。

三、预习要求1、在上述4 个训练内容中,自选其中3 个进行预习。

画出安装接线图。

2、写出设计过程,根据数字集成电路手册选择集成译码器和门电路,3、自拟测试调整步骤。

四、训练要求1、测试记录电路的逻辑功能。

并列出真值表判断设计是否正确。

2、自行分析、检测和排除训练中出现的故障。

3、总结本技能训练的收获、体会。

训练三用数据选择器实现多种逻辑功能一、训练目的1、掌握数据选择器的功能测试方法。

2、熟悉数据选择器的应用。

二、训练内容1、测试8选1数据选择器的逻辑功能。

2、用8 选1 数据选择器实现三输入多数表决电路。

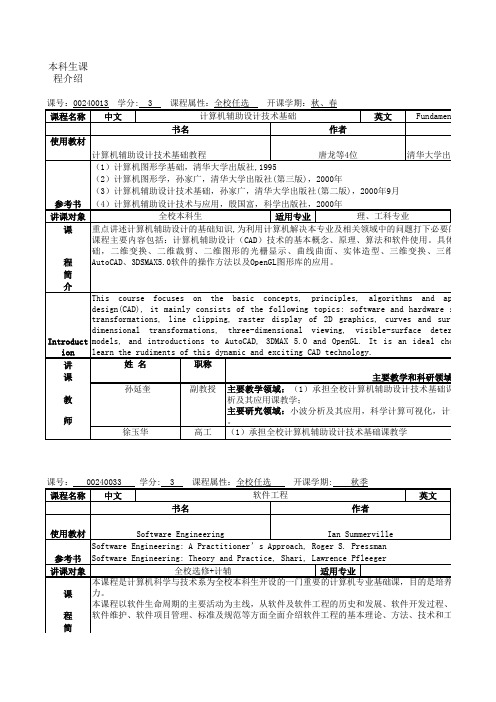

清华大学计算机系本科生全部课程详细介绍

本科生课程介绍课程名称中文英文讲课对象适用专业课程简介Introduct ion 讲课教师高工课程名称中文英文讲课对象适用专业课程简介全校选修+计辅本课程是计算机科学与技术系为全校本科生开设的一门重要的计算机专业基础课,目的是培养学生的软件力。

本课程以软件生命周期的主要活动为主线,从软件及软件工程的历史和发展、软件开发过程、需求分析、软件维护、软件项目管理、标准及规范等方面全面介绍软件工程的基本理论、方法、技术和工具。

使用教材Software Engineering Ian Summerville参考书Software Engineering: A Practitioner’s Approach, Roger S. PressmanSoftware Engineering: Theory and Practice, Shari, Lawrence Pfleeger徐玉华(1)承担全校计算机辅助设计技术基础课教学课号: 00240033 学分: 3 课程属性:全校任选 开课学期: 秋季软件工程书名作者This course focuses on the basic concepts,principles,algorithms and applicationsdesign(CAD),it mainly consists of the following topics:software and hardware system of Ctransformations,line clipping,raster display of 2D graphics,curves and surfaces,soldimensional transformations,three-dimensional viewing,visible-surface determination,models,and introductions to AutoCAD,3DMAX 5.0and OpenGL.It is an ideal choice for slearn the rudiments of this dynamic and exciting CAD technology.姓 名职称 主要教学和科研领域孙延奎副教授主要教学领域:(1)承担全校计算机辅助设计技术基础课教学;(2)析及其应用课教学;主要研究领域:小波分析及其应用,科学计算可视化,计算机图形学,。

数字逻辑与计算机组成 第3章 组合逻辑电路

硬件资源:7个4输入与门、1个7输入或门

10

1.4 组合逻辑电路设计

利用布尔代数化简, 以减少逻辑门数和输入端数 X·Y+X·Y’=X

F = SN3N2N1N0(1,2,3,5,7,11,13) =N3’N0+N3’ N2’ N1 N0’+N3 N2’ N1 N0+N3 N2 N1’ N0

非法值 • 信号值不能被有效识别为高电平或低电平,处于不确定状态。 例如:下图中的信号X

不管A是0还是1,F结点都会同时 被高电平和低电平驱动,可能导 致在F结点处之间有较大电流流动 ,使电路发热而被损坏

16

1.5 无关项、非法值和高阻态

例:设计一个检测电路,当NBCD(8421)码数值大于5时,输出为1

最简输出表达式

函数转换:独立逻辑门、中间组件、可编程器件

画出逻辑电路图 逻辑器件的标准符号,输入、输出信号、器件标识

评价电路

电路分析:功能、缺陷、电气特性等

9

1.4 组合逻辑电路设计

例1:素数检测器的设计

列出真值表

• 4-bit input, N3N2N1N0

写出最小项表达式 F = SN3N2N1N0(1,2,3,5,7,11,13)

输出变量:故障信号F 正常工作为0,发生故障为1

故障状态 真 值 表 RY G F

0 0 01 0 0 10 0 1 00 0 1 11 1 0 00 1 0 11 1 1 01 1 1 11

13

1.4 组合逻辑电路设计

逻辑抽象结果

真值表

RY G F

000 1 001 0 010 0 011 1 100 0 101 1 110 1 111 1

每个输入端和输出端只有高电平、

SOC第3章 S0C设计与EDA

• 目前的ESL工具通常采用工业标准语言进行 建模,如C/C++、System C、 SystemVerilog等,常用的软、硬件协同设 计验证工具有Mentor公司的Seamless和 ARM公司的SoC Designer. Mentor的 Catapult可实现C++到RTL级的综合。

3.2 验证的分类及相关工具

3.2.2动态验证及相关工具

• • • • 仿真流程如图3一l所示,仿真环境包括电路描述的输入、 仿真控制命令和仿真结果的显示等3部分。 仿真工具首先要把用户的描述转换为内部表示,即建立 模型。 激励波形可以同电路描述一起输入,也可以在仿真开 始之后通过控制命令输入,或者单独建立激励波形文件输 入。 控制命令包括初始值设置、仿真时间指定、仿真过程 控制、仿真中断设置、观察仿真状态、设置某些信号或变 量值,以及指定继续仿真等。在交互式仿真方式下,控制 命令交互输入;在批处理式仿真方式下,控制命令常由控 制命令文件(脚本)一次输入。 仿真结果主要为各外部输出端和其他观察点的输出波形, 以及其他一些检查结果信息。

• 3.3.2:EDA工具的综合策略 • 不同的电路描述方法将导致生成不同的电路,为 了使设计更加有效,设计者应该了解一些EDA工 具基本的综合和优化策略,这样可以选择和规划 不同的综合策略来实现高效的电路。 • 1.以速度为目标的综合策略 • 以速度为目标的综合策略是当速度问题是设计 的主要矛盾时,需要采用的综合方案。这一类算 法的核心是忽略所有的有关代价的约束,寻找出 具有最大速度特性的算子调度方案。只有当速度 满足了设计要求时才去考虑其他代价的优化。

2.静态时序分析工具

• 静态时序分析技术的许多基本概念与动态仿真不同。静 态时序分析技术通过输入一定的设计约束来静态地检查设 计的时序功能,而不需要加入相应的测试向量进行逻辑功 能仿真。它是建立在同步数字电路设计基础上的,是一种 穷尽的分析方法。静态时序分析工具通过路径计算延迟的 总和,并比较相对于预定义时钟的延迟,它仅关注时序间 的相对关系而不是评估逻辑功能。 • 静态时序分析工具可识别的时序故障数要比仿真多得 多,包括建立/保持时间、最小和最大跳变延时、时钟脉 冲宽度和时钟畸变、门级时钟的瞬时脉冲检测、总线竞争 与总线悬浮错误、不受约束的逻辑通道。 • 时序分析工具种类很多,如Synopsys公司的 Primetime是业界普遍作为Sign0ff的静态时序分析工具。

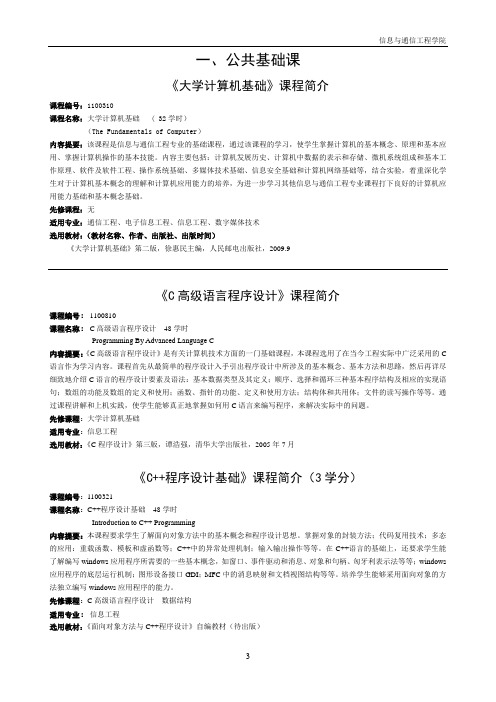

(1)北京邮电大学2009年版课程简介(信通院)

一、公共基础课《大学计算机基础》课程简介课程编号:1100310课程名称:大学计算机基础 ( 32学时)(The Fundamentals of Computer)内容提要:该课程是信息与通信工程专业的基础课程,通过该课程的学习,使学生掌握计算机的基本概念、原理和基本应用、掌握计算机操作的基本技能。

内容主要包括:计算机发展历史、计算机中数据的表示和存储、微机系统组成和基本工作原理、软件及软件工程、操作系统基础、多媒体技术基础、信息安全基础和计算机网络基础等,结合实验,着重深化学生对于计算机基本概念的理解和计算机应用能力的培养,为进一步学习其他信息与通信工程专业课程打下良好的计算机应用能力基础和基本概念基础。

先修课程:无适用专业:通信工程、电子信息工程、信息工程、数字媒体技术选用教材:(教材名称、作者、出版社、出版时间)《大学计算机基础》第二版,徐惠民主编,人民邮电出版社,2009.9《C高级语言程序设计》课程简介课程编号:1100810课程名称:C高级语言程序设计48学时Programming By Advanced Language C内容提要:《C高级语言程序设计》是有关计算机技术方面的一门基础课程,本课程选用了在当今工程实际中广泛采用的C 语言作为学习内容。

课程首先从最简单的程序设计入手引出程序设计中所涉及的基本概念、基本方法和思路,然后再详尽细致地介绍C语言的程序设计要素及语法:基本数据类型及其定义;顺序、选择和循环三种基本程序结构及相应的实现语句;数组的功能及数组的定义和使用;函数、指针的功能、定义和使用方法;结构体和共用体;文件的读写操作等等。

通过课程讲解和上机实践,使学生能够真正地掌握如何用C语言来编写程序,来解决实际中的问题。

先修课程:大学计算机基础适用专业:信息工程选用教材:《C程序设计》第三版,谭浩强,清华大学出版社,2005年7月《C++程序设计基础》课程简介(3学分)课程编号:1100321课程名称:C++程序设计基础48学时Introduction to C++ Programming内容提要:本课程要求学生了解面向对象方法中的基本概念和程序设计思想。

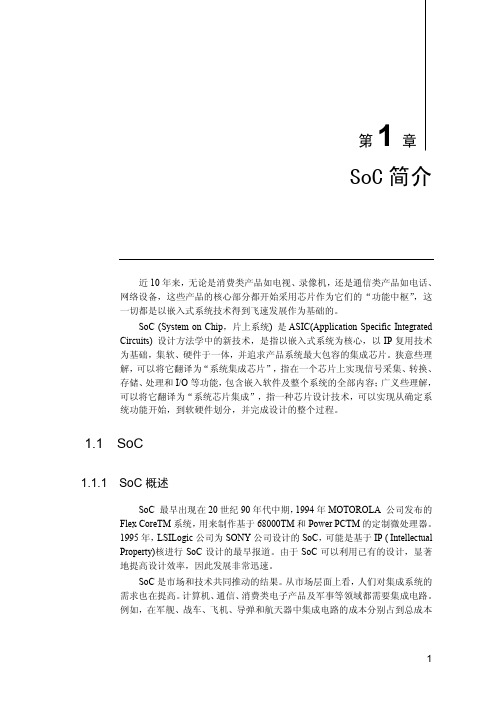

SoC片上系统初级培训资料SoC 简介SOC1

第1章SoC简介近10年来,无论是消费类产品如电视、录像机,还是通信类产品如电话、网络设备,这些产品的核心部分都开始采用芯片作为它们的“功能中枢”,这一切都是以嵌入式系统技术得到飞速发展作为基础的。

SoC (System on Chip,片上系统) 是ASIC(Application Specific Integrated Circuits) 设计方法学中的新技术,是指以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体,并追求产品系统最大包容的集成芯片。

狭意些理解,可以将它翻译为“系统集成芯片”,指在一个芯片上实现信号采集、转换、存储、处理和I/O等功能,包含嵌入软件及整个系统的全部内容;广义些理解,可以将它翻译为“系统芯片集成”,指一种芯片设计技术,可以实现从确定系统功能开始,到软硬件划分,并完成设计的整个过程。

1.1 SoC1.1.1 SoC概述SoC 最早出现在20世纪90年代中期,1994年MOTOROLA 公司发布的Flex CoreTM系统,用来制作基于68000TM和Power PCTM的定制微处理器。

1995年,LSILogic公司为SONY公司设计的SoC,可能是基于IP ( IntellectualProperty)核进行SoC设计的最早报道。

由于SoC可以利用已有的设计,显著地提高设计效率,因此发展非常迅速。

SoC是市场和技术共同推动的结果。

从市场层面上看,人们对集成系统的需求也在提高。

计算机、通信、消费类电子产品及军事等领域都需要集成电路。

例如,在军舰、战车、飞机、导弹和航天器中集成电路的成本分别占到总成本1SOC设计初级培训(Altera篇)2的22%、24%、33%、45%和66%。

随着通讯行业的迅猛发展和信息家电的迅速普及,迫使集成电路产商不断发展IC 新品种,扩大IC 规模,增强IC 性能,提高IC 的上市时间(Time to maeket) ,同时还需要实现品种的通用性和标准化,以利于批量生产,降低成本。

2024年芯片类培训教程

芯片类培训教程一、引言随着科技的飞速发展,芯片作为现代信息技术的核心,已经广泛应用于各个领域。

芯片产业在我国也得到了高度重视和快速发展。

为了满足市场对芯片人才的需求,芯片类培训教程应运而生。

本教程旨在为广大芯片行业从业者、学生及爱好者提供一个系统、全面的芯片知识学习平台,帮助学员掌握芯片设计、制造、测试和应用等方面的关键技术。

二、教程目标1.培养学员对芯片产业的认识,了解芯片在现代社会中的重要性。

2.使学员掌握芯片设计的基本原理和方法,具备一定的芯片设计能力。

3.使学员熟悉芯片制造工艺,了解芯片生产过程。

4.培养学员具备芯片测试和验证的能力,确保芯片产品的质量和性能。

5.帮助学员了解芯片在不同领域的应用,拓展职业发展空间。

三、教程内容1.芯片基础知识(1)半导体物理基础(2)半导体器件原理(3)集成电路设计方法(4)芯片制造工艺2.芯片设计(1)数字电路设计(2)模拟电路设计(3)混合信号电路设计(4)芯片封装与测试3.芯片制造(1)光刻技术(2)掺杂技术(3)薄膜沉积技术(4)刻蚀技术4.芯片测试与验证(1)芯片测试方法(2)芯片验证流程(3)故障分析与定位(4)可靠性测试5.芯片应用(1)计算机芯片(2)通信芯片(3)消费电子芯片(4)汽车电子芯片四、教学方法1.理论教学:通过讲解、案例分析等方式,使学员掌握芯片相关理论知识。

2.实践教学:结合实际工程项目,让学员动手实践,提高实际操作能力。

3.在线学习:利用网络平台,提供丰富的学习资源,方便学员随时随地进行学习。

4.企业实习:安排学员到企业实习,了解芯片产业现状,提高职业素养。

五、师资力量本教程由具有丰富教学经验和实际工程经验的专家、教授授课。

他们分别来自国内外知名高校、科研院所和企业,具备深厚的学术背景和丰富的实践经验。

六、证书与就业学员完成本教程学习并通过考试,可获得相应证书。

本教程旨在培养具备实战能力的芯片人才,为学员就业和职业发展提供有力支持。

数字电路与逻辑设计习题学生常见问题答疑[1]

![数字电路与逻辑设计习题学生常见问题答疑[1]](https://img.taocdn.com/s3/m/fe7dfaf63086bceb19e8b8f67c1cfad6195fe988.png)

数字电路与逻辑设计习题学生常见问题答疑[1]第一章绪论1、数字电路有什么优点?答:首先数字电路能产生更廉价,更可靠的数字处理系统。

其次数字处理硬件允许可编程操作,同时数字硬件和软件实现与模拟电路和模拟信号处理系统相比,通常具有更高的精度。

2、数字电路与模拟电路有什么区别?答:数字电路与模拟电路同等重要,构成数字电路与模拟电路的基本元件都是半导体器件。

但是它们工作状态不同,实现功能不同,工作信号不同,如:数字电路中三极管工作在饱和区和截止区,模拟电路中三极管工作在放大区。

数字电路实现逻辑功能,完成逻辑运算,模拟电路主要是放大电信号。

数字电路处理离散信号,模拟电路处理连续信号。

3、数字电路设计的趋势?答:当前数字电路设计的趋势是,越来越大的设计,越来越短的推向市场的时间,越来越低的价格,设计方法越来越依赖于电子设计自动化(EDA)工具。

多层次的设计表述,集成电路的设计与制造分离,芯片生产厂家提供模型或标准单元库,设计公司负责电路功能设计。

电路功能设计已进入片上系统(SOC)时代,知识产权模块(IP 核)产品化。

第二章逻辑函数及其简化1、逻辑函数为什么要化简?答:一个逻辑函数可以写成不同的表达式形式,表达式越简单,所表示的逻辑关系越明显。

化简电路的目的,就是为了降低系统的成本,提高电路的可靠性,以用最少的逻辑门实现逻辑函数。

2、公式法化简中那么多公式怎么记?它有什么优缺点?答:逻辑代数的常用公式,反映了逻辑代数运算的基本规律,是化简逻辑函数、分析和设计逻辑电路的基本公式,必须熟悉和掌握。

公式法化简没有固定的步骤。

能否以最快的速度进行化简,与经验、技巧和对公式掌握及运用的熟练程度有关。

该方法的优点是输入变量个数不受限制,缺点是结果是否为最简有时不易判断。

3、卡诺图法化简的优点?答:利用卡诺图可以直观、方便地化简逻辑函数,并且克服了公式化简法对最终化简结果难以确定等缺点。

第三章集成逻辑门1、第三章感觉和其它章节没关系,是否不重要?答:第三章介绍了常用逻辑门的内部电路结构以及外部特性,对后续学习非常重要。

计算机专业基础课程数字逻辑(必修课)

➢ 参考书

➢《数字逻辑学习与解题指南》 (第二版) 欧阳星明 主编 (华中科技大学出版社)

计算机专业基础课程数字逻辑(必修课)

5

如何学好数字逻辑?

➢ 掌握课程特点

➢ 本课程是一门既抽象又具体的课程

➢在逻辑问题的提取和描述方面是抽象的,而在逻辑 问题的实现上是具体的。因此,学习中既要务虚, 又要务实。

例如:计算机组成原理、计算机系统结构、 微型机与接口、单片机原理及其应用、 数字系统设计自动化等。

硬件是软件运行必要环境

硬件设计是协同设计(co-design)重要手段之一

计算机专业基础课程数字逻辑(必修课)

28

数字逻辑电路的种类和研究方法

➢ “数字逻辑”含义

研究数值的逻辑加工和运算的电路。

➢ 分类:

➢ 广泛阅读,拓宽知识面:通过阅读相关的参考书 籍,不仅能加深对所学知识的理解,而且能拓宽 知识面。有利于从更广度和深度加强对课程意义 的理解。

计算机专业基础课程数字逻辑(必修课)

10

如何学好数字逻辑?

➢ 注重理论联系实际

➢ 将书本知识与工程实际统一:学习中注意书本知 识与工程应用存在的差别,将理论与实际统一。

数字逻辑电路

组合逻辑 时序逻辑

研究方法

同步逻辑电路 异步逻辑电路

分析 综合或逻辑设计

计算机专业基础课程数字逻辑(必修课)

29

二、数制

1、进位计数制 进位计数制的基本因素:基数和位权。

基数是指计数制中所有到的数字符号的个数。在基数 为R的计数制中,包含0、1、…、R-1共R个数字符号,进 位规律是“逢R进一、借一当R”,称为R进位计数制。

➢换而言之,逻辑电路的分析与设计具有较大的弹性 和可塑性。

组合逻辑电路(半加器全加器及逻辑运算)ppt课件

①写出用异或门、与或非门、非门组成全加器的逻辑表达式;

②连接电路,注意与或非门不用的输入端接地;

③根据不同的输入状态,记录输出结果。

74LS86

A

B 注意:74LS54 3或4或5接地, 9或10或11接地

C

1 =1 3

2

4 =1

5

6

S

74LS54

74LS00

。 。 1

2

& ≥1

61&

3

12 &

2

CO

最新版整理ppt

13

实验二 组合逻辑电路(半加器全加器及逻辑运算)

四、实验内容 操作说明

逻辑电平

LED显示

最新版整理ppt

14

实验二 组合逻辑电路(半加器全加器及逻辑运算)

四、实验内容

2、测试用异或门和与非门组成的半加器逻辑功能

在实验箱上用异或门和与非门组成如下电路,输入接电 平开关,输出端Y、Z接电平显示发光二极管;改变输 入状态,记录输出结果。

011 100

01 10

101 110 111

01 01 11

ABC有奇数个1时S为1; ABC有偶数个1和全为0时 S为0。 -----用全加器组成三位二进制代码 奇偶校验器

最新版整理ppt

12

实验二 组合逻辑电路(半加器全加器及逻辑运算)

四、实验内容 1、组合逻辑电路功能测试

选择7400两片连接如下电路;A、B、C接电平开关,Y1、Y2接 电平显示发光管,改变A、B、C的状态填表,并写出Y1、Y2的 逻辑表达式;将运算结果与实验结果比较。

最新版整理ppt

4

实验二 组合逻辑电路(半加器全加器及逻辑运算)

组合优化课程简介.

《组合优化》课程简介组合优化 3Combinatorial Optimization 3-0预修课程:数学分析(微积分),线性代数面向对象:二、三、四年级本科生内容简介:组合优化是近二十年来运筹学最活跃的分支之一,在计算机科学、计算生物学、物流和供应链管理等新兴领域有大量的应用。

本课程主要介绍组合优化的基本理论和方法,若干重要组合优化问题的模型和算法,以及在其他学科中的应用。

通过学习,了解离散优化问题的特点和基本理论,初步掌握其建模和求解方法。

推荐教材或主要参考书:《数学规划与组合优化》姚恩瑜,何勇,陈仕平编著,浙江大学出版社,2001《组合优化》教学大纲组合优化 3Combinatorial Optimization 3-0预修课程:数学分析(微积分),线性教学大纲一、教学目的和基本要求:组合优化是近二十年来运筹学最活跃的分支之一,在计算机科学、计算生物学、物流和供应链管理等新兴领域有大量的应用。

通过本课程的学习,了解组合优化和计算复杂性的的基本概念和理论,熟悉常见组合优化问题的模型和算法,初步掌握离散优化问题的建模和求解方法。

二、主要内容及学时分配:一、组合优化初步(1)算法和计算复杂性9学时二、图和网络中的优化问题(2)匹配、着色和遍历6学时(3)网络优化6学时三、若干组合优化问题(4)排序问题6学时(5)装箱问题3学时(6)背包问题3学时(7)旅行售货商问题3学时(8)Steiner树问题3学时四、组合优化专题选讲(9)拟阵初步3学时(10)在线问题3学时(11)组合优化应用案例3学时三、教学方式:课堂讲授四、相关教学环节安排:五、考试方式及要求:笔试六、推荐教材或主要参考书:《数学规划与组合优化》姚恩瑜,何勇,陈仕平编著,浙江大学出版社,2001七、有关说明:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

延时和输入方式有关

18

仿真结果

3 2.5 2 1.5 1 0.5 0 0 -0.5 100 200 300 400

A=B=1→0 A=1 →0, B=1 A=1, B=1→0

Input Data Pattern A=B=0→1 A=1, B=0→1 A= 0→1, B=1 A=B=1→0 A=1, B=1→0 A= 1→0, B=1

如何提高静态CMOS反相器的性能 如何提高静态CMOS反相器的性能 CMOS

–降低电容 降低电容

包括寄生电容和负载电容

–降低等效导通电阻 降低等效导通电阻

增加晶体管尺寸 需小心自载效应

–一定范围内增加VDD 一定范围内增加V 一定范围内增加

3

Review(3) Review(

反相器的功耗分布

8

举例:NAND 举例:NAND

9

举例:NOR 举例:NOR

10

构建CMOS组合逻辑 构建CMOS组合逻辑 CMOS

反向输出

–out = xx & xxx | xxxx

下拉网络(NMOS)和上拉网络(PMOS) 下拉网络(NMOS)和上拉网络(PMOS) (NMOS)和上拉网络

–以输出为分界线呈对称互补关系 –晶体管数目相同,逻辑关系相反

22

延时与扇出

tpNAND2 tpINV tp (psec psec)

tpNOR2

All gates have the same drive current. Slope is a function of "driving strength"

2

4

6

8

10

12

14

16

eff. fan-out

23

快速逻辑设计方法(1) 快速逻辑设计方法(1)

逐级加大晶体管尺寸

–如果扇出为主要负载 –M1>M2>M3>….>MN –降低起主要作用的电阻 –电容的增加保持一定范围 –可提高性能20%以上

缺点:在实际的版图中不那么简 单,常常由于设计规则方面的考 虑迫使设计者不得不将晶体管距 离拉开,从而使内部电容增加. 这有可能抵消掉调整尺寸所得到 的所有收益! InN

17

Req Rp B Rp A CL Cint

Rp Rp

输入模式对延时的影响

输出由低变高

Rp A Rn B Rn A Cint B CL Rp

–一个输入变低

delay = 0.69 Rp CL

–两个输入都变低

delay = 0.69 (Rp/2) CL

输出由高变低

–两个输入都变高

delay = 0.69 (2Rn ) CL (2

13

问题

为什么用NMOS做PDN, PMOS做PUN?

VDD → 0

D

VDD → |VTp| VGS

S

VDD

S

CL

CL

D

NMOS管产生"强零"而PMOS器件产生"强1" 输出电容最初被充电至VDD.在放电时,一个NMOS器件将输出一直下拉至 GND,而一个PMOS只能把输出拉低到VTp为止,此时PMOS关断并停止提供 放电电流.因此NMOS管适于用在PDN中.

组合逻辑

1

Review(1) Review(

静态CMOS反相器 静态CMOS反相器 CMOS

–噪声容限大 噪声容限大 –无比逻辑,逻辑电平和器件尺寸无关 无比逻辑, 无比逻辑 –低输出阻抗 低输出阻抗 –输入电阻极高 输入电阻极高 –几乎没有漏电流 几乎没有漏电流

2

Review( Review(2)

均衡信号路径减少毛刺

对毛刺敏感的电路

消除毛刺的电路

使信号路径长度匹配可以减少毛刺 所标注的数字表示信号到达的时间

36

有比逻辑电路(P192) 有比逻辑电路(P192)

简单的负 载器件

伪NMOS门 门

有比逻辑试图减少一个给定逻辑功能所需要的晶体管数目. 有比逻辑试图减少一个给定逻辑功能所需要的晶体管数目. 在有比逻辑中,整个PUN被一个无条件的负载器件所替代. 被一个无条件的负载器件所替代. 在有比逻辑中,整个 被一个无条件的负载器件所替代 由于输出端的电压摆幅及门的总体功能取决于NMOS和PMOS的尺寸比,所以该电路称为有比电路. 和 的尺寸比, 由于输出端的电压摆幅及门的总体功能取决于 的尺寸比 所以该电路称为有比电路. 这不同于像互补CMOS这样的无比逻辑类型,后者的高低电平与晶体管的尺寸无关. 这样的无比逻辑类型, 这不同于像互补 这样的无比逻辑类型 后者的高低电平与晶体管的尺寸无关.

扇出表示连接到驱动门输出端的负载门的数目N. 扇出表示连接到驱动门输出端的负载门的数目 . 增加一个门的扇出会影响它的逻辑输出电平.从模拟放大器中我们知道, 增加一个门的扇出会影响它的逻辑输出电平.从模拟放大器中我们知道, 通过使负载门的输入电阻尽可能的大(也就是使输入电流最小) 通过使负载门的输入电阻尽可能的大(也就是使输入电流最小)并保持驱 动门的输出电阻较小(即减小负载电流对输出电压的影响), ),可以使这一 动门的输出电阻较小(即减小负载电流对输出电压的影响),可以使这一 影响减到最小. 影响减到最小. 当扇出较大时,所加的负载会使驱动门的动态性能变差. 当扇出较大时,所加的负载会使驱动门的动态性能变差.为此许多通用单 元和库单元都定义了一个最大扇出数来保证该单元的静态和动态性能都能 满足规定的技术要求. 满足规定的技术要求.

37

电阻负载

VDD N transistors + Load Resistive Load RL VOH = V DD VOL = F In1 In2 In3 RPN RPN + RL Assymetrical response PDN Static power consumption tpL= 0.69 RLCL

7

静态CMOS电路 静态CMOS电路 CMOS

VDD

In1 In2 VDD PMOS only F(In1,In2,…InN) PDN

PUN

Vin

Vout CL

InN In1 In2 InN

NMOS only

PMOS上拉网络,NMOS下拉网络 上拉网络, 上拉网络 下拉网络 反向输出 结构对称互补

MN

CL

In3 In2 In1

M3 M2 M1

C3 C2 C1

24

快速逻辑设计方法(2) 快速逻辑设计方法(2)

调整晶体管顺序

–关键路径上的晶体管靠近输出,假设信号in1为关键信号

关键路径 charged CL C2 charged C1 charged 关键路径 0→1 In1 M3 In2 1 M2 In3 1 M1 charged CL C2 discharged C1 discharged

27

快速逻辑设计方法(5) 快速逻辑设计方法(5)

级联优化

–插入BUFFER隔离扇入扇出

CL

CL

28

提高CMOS组合逻辑性能

– 调整输入模式 – 控制扇入扇出个数 – 逐级加大MOS管尺寸 – 降低输出电压摆幅 – 级联优化

29

CMOS逻辑功耗 CMOS逻辑功耗

电压摆幅 物理电容 翻转概率

31

信号相关性

外部信号的统计概率相对难以预知 但内部信号经常有相关性

信号相关性使电路输入信号的统计概 率的计算更加复杂

32

虚假翻转

虚假翻转产生额外功耗 虚假翻转产生额外功耗 严重的会产生毛刺 严重的会产生毛刺

33

如何降低翻转概率

逻辑重组

链形比树形具有较低的开关活动性.但是树形结构没有任何毛刺活动性. 链形比树形具有较低的开关活动性.但是树形结构没有任何毛刺活动性.

In3 1 M3 In2 1 M2 In1 M1 0→1

延时取决于CL, C1 and C2的 放电时间.

延时取决于CL的放电时间

25

快速逻辑设计方法(3) 快速逻辑设计方法(3)

优化逻辑结构

–延时和扇入呈平方关系

26

快速逻辑设计方法(4) 快速逻辑设计方法(4)

降低电压摆幅

–Tp = 0.69(3/4(CLVSwing)/IDSAT) –可线性降低延时,还可以降低功耗 –但输出电压变低,会使后级电路变慢 –可用灵敏放大器放大输出(存储器设计中常用)

20

扇入对延时的影响

A

B R4 A R3 B R2 C R1 D

C

D CL C3 C2 C1

RC分布 (Elmore delay model) tpHL = 0.69 (R1C1+(R1+R2)C2+(R1+R2+R3)C3+(R1+ R2+R3+R4)CL)

传输延时随着输入个数的增多快速上升

30

翻转的统计特性

输入并不总是均匀分布的 以2输入NOR门为例 pa为A=1的统计概率 pb为B=1的统计概率 p1 =(1- pa)(1- pb)

–输出在一个周期中为0的概率

p0 =1- p1

–在下一个周期中为1的概率

不同的信号统计概率导致不同的翻转 概率, 概率,也就决定了不同的动态功耗

–减少物理电容 减少物理电容

寄生电容和负载电容

5

什么是组合逻辑

In

Combinational Logic Circuit

In Out

Combinational Logic Circuit

Out

State

Combinational Output = f(In)

Sequential Output = f(In, Previous In)