TMS320F28335的eCAP模块

TMS320F28335核心板:Core28335软件调试指南

如果出现下图所示,则表示仿真器和开发板已连接成功。

第三步: 新建一个工程,如下图

第四步: 选择路径,输入工程项目名,并确定,则如下图所示

第五步: 添加源文件,添加 CMD 文件,如下图所示: 注意:源文件有*.c 文件,也有*.asm 文件

添加 CMD 文件跟添加源文件的方法相似,在这里不在赘述。添加完成后整个工程如下所示:

版权© 2013,株洲市索思达电子有限公司

前言

阅前必读

简介:

本 用 户指 南是 TMS320F28335 DSP 处 理 模板 硬 件使 用说 明书 ,详 细描 述 了

28335实用版 的硬件构成、原理,以及它的使用方法和编程指导。

保修:

所有由株洲市索思达电子有限公司生产制造的硬件和软件产品, 保修期为从发货 之日起一 年。 在保修期内由于产品质量原因引起的损坏, 株洲市索思达电子有限公司负责免费维修。当在 保修期内软件进行了升级, 株洲市索思达电子有限公司将免费提供。

参考资料:

TMS320F28x DSP CPU and Instruction Set Reference Guide (文献号 SPRU430) : 介 绍 TMS320F28x 系列 DSP 的 CPU 结构、指令组、流水线及中断。 TMS320C28x Floating Point Unit and Instruction Set Reference Guide (文献号 SPRUEO2)介绍浮点单元和FPU指令集。 TMS320x28xx, 28xxx Peripheral Reference Guide(文献号 绍 TMS320F28x 系列 DSP 的外设。 TMS320x2833x 献 号 System Control and Interrupts Reference Guide ( 文 SPRU566):介

DSP第5章-F28335-概述

外设总线: 用于外设互联,复用多种总线。

5.3.3 外设

1. ePWM:6个,可单独控制各个引脚,功能更强大 2.eCAP:6个 3.eQEP:2个,测速更加方便 4.ADC:12位,16路,80ns转换时间 5.Watchdog Timer:1个 6.McBSP:2个,用于连接高速外设,如音频处理模块 7.SPI:1个,连接具有SPI借口的外设

得益于F28335浮点运算单元,从而简化软件开发,缩 短开发周期,降低开发成本。

5.1 F28335的性能

高性能静态CMOS技术:主频150MHZ,指令周期6.67ns; 低功

耗设计,1.9V/1.8V内核电压,3.3VI/O引脚电压;Flash编 程电压为3.3V

高性能32位CPU:IEEE-754单精度浮点运算单元(FPU) ;

3个32位CPU定时器:定时器0、1、2。T0、T1为一般定时器 ,T0连接至PIE,T1连接至中断INT13,T2用作DSP/BIOS的

5.1 F28335的性能

串行端口外设:2个eCAN2.0B; 3个SCI(UART);2个 McBSP;1个SPI; 1个I2C总线接口。

16通道12位模数转换模块:转换时间80ns,2X8通道复用输入 接口;2个采样保持电路;单/连续通道转换;内部或外部参考电 压

▪32位定点CPU架构,支持16位和32位指令操作。前者减 少存储,提高代码密度。后者加快指令执行时间。 ▪32位IEEE-754单精度FPU,具有高效C/C++引擎,可使 用高级语言编程。 ▪32X32位MAC64位处理能力。 ▪快速中断响应。 ▪“原子指令”读写简化机制。执行更快,代码更少。

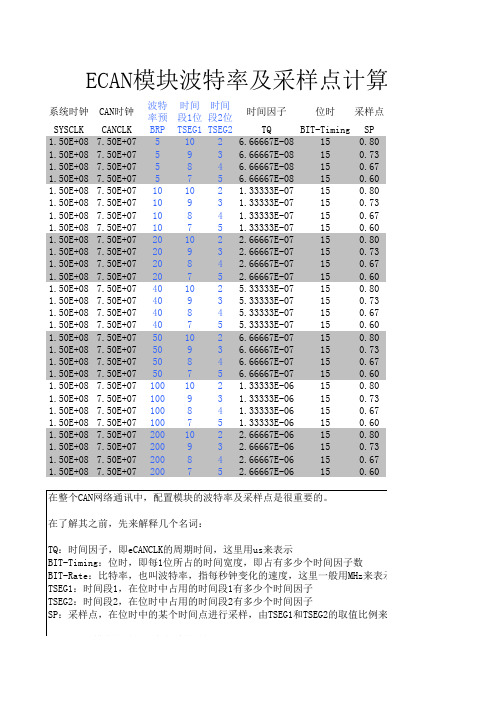

F28335的ECAN模块波特率及采样点计算

15

0.80

9

3 6.66667E-07

15

0.73

8

4 6.66667E-07

15

0.67

7

5 6.66667E-07

15

0.60

10 2 1.33333E-06

15

0.80

9

3 1.33333E-06

15

0.73

8

4 1.33333E-06

15

0.67

7

5 1.33333E-06

15

0.60

10 2 2.66667E-06

BIT-Rate 1000 1000 1000 1000 500 500 500 500 250 250 250 250 125 125 125 125 100 100 100 100 50 50 50 50 25 25 25 25

BIT-Rate 1.000 1.000 1.000 1.000 0.500 0.500 0.500 0.500 0.250 0.250 0.250 0.250 0.125 0.125 0.125 0.125 0.100 0.100 0.100 0.100 0.050 0.050 0.050 0.050 0.025 0.025 0.025 0.025

波特 率预 BRP

5 5 5 5 10 10 10 10 20 20 20 20 40 40 40 40 50 50 50 50 100 100 100 100 200 200 200 200

时间 时间 段1位 段2位

时间因子

位时 采样点

TSEG1 TSEG2

TQ

BIT-Timing SP

10 2 6.66667E-08

第九章 增强型捕获(eCAP)模块-TMS320F28335 DSP原理、开发及应用-符晓

周期

eCAP的相关寄存器

寄存器名称 TSCTR CTRPHS CAP1 CAP2 CAP3 CAP4 ECCTL1 ECCTL2 ECEINT ECFLG ECCLR ECFRC

地址单元(偏移量) 0x0000 0x0002 0x0004 0x0006 0x0008 0x000A 0x0014 0x0015 0x0016 0x0017 0x0018 0x0019

大小(×16bit)

寄存器说明

2

时间标识计数器

2

计数器相位寄存器

2

捕获寄存器1

2

捕获寄存器2

2

捕获寄存器3

2

捕获寄存器4

1

控制寄存器1

1

控制寄存器2

1

中断使能寄存器

1

中断标志寄存器

1

中断标志清除寄存器

1

中断强制寄存器

vk

xk - xk-1 t

解决方法: 在固定的位置变化量之间测量时间

vk

x tk - tk-1

还可用于额外的PWM输出

eCAP的模块连接方式

外设捕获工作模式结构框图PW Nhomakorabea 比较 逻辑

中断 控制 逻辑

极性 选择

极性 选择

极性 选择

极性 选择

连续/单次 捕获控制

APWM工作模式

开通 时间

关断时间

第九章 增强型捕获(eCAP)模块

捕获单元(eCAP)

定时器

时间戳

触发

管脚

可精确测量外部信号的时序,用于:

旋转设备的转速测量 位置传感器脉冲时间测量 脉冲信号周期及占空比测量

应用举例

精确测量脉冲的时间宽度 在低速时为增量编码器估算速度:

TMS320F28335的eCAP模块

eCAP模块1.介绍eCAP模块包括以下的资源:*可分配的输入引脚。

*32-bit时间基准(计数器)。

*4个32bit时间窗捕获控制寄存器。

*独立的边缘极性选择。

*输入信号分频(2~62)。

*4Capture event均可引起中断。

2. eCAP模块功能分析eCAP模块可以设置为event capture模式或者是APWM模式,一般而言前者比较常用,在这里我们只对第一种进行介绍。

在event capture模式下,一般可以将eCAP模块分为以下几个模块:事件分频、边沿极性选择与验证、中断控制。

2.1 事件分频输入事件信号可通过分频器分频处理(分频系数2~62),或直接跳过分频器。

这个功能通常针对输入事件信号频率很高的情况下。

2.2边沿极性选择与验证1)4个独立的边沿极性(上升沿/下降沿)选择通道。

2)Modulo4 序列发生器对Each edge(共4路)进行事件验证。

3)CAPx通过Mod4对事件边沿计数。

CAPx寄存器在下降沿时被装载。

2.3 32-bit计数器(TSCTR)此计数器为event capture提供事件基准,而时钟的计数则是基于系统时钟的。

当此计数器计数超过范围时,则会产生相应的溢出标志,若溢出中断使能,则产生中断。

此计数器在计算事件周期时非常有效。

详细的资料请参看spru807应用部分。

2.4中断控制中断能够被capture events(CEVT1-CEVT4,CTROVF)触发。

计数溢出同样会提供中断。

事件单独地被极性选择部分以及序列验证部分审核。

这些事件中的一个被选择用来作为中断源送入PIE。

设置中断的Proper过程1)Disable global interrupts.2)停止eCAP计数。

3)Disable eCAP interrupts。

4)设置外设寄存器。

5)清除eCAP中断标志位。

6)Enable eCAP中断。

7)Start ecap 计数器。

8)Enable global 中断。

关于28335各个模块的理解

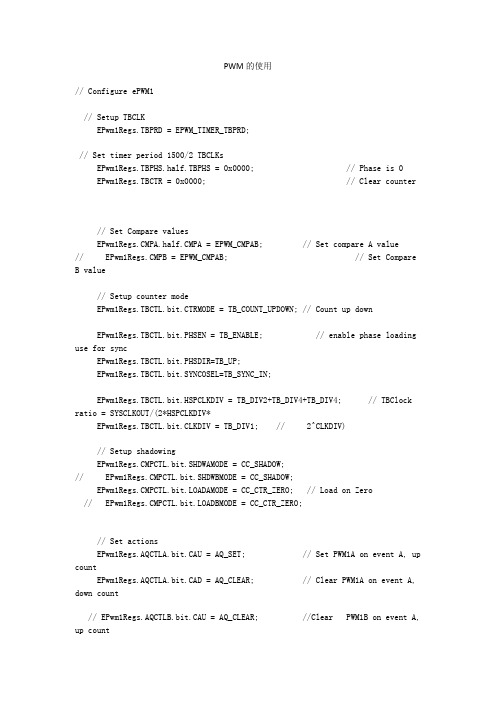

PWM的使用// Configure ePWM1// Setup TBCLKEPwm1Regs.TBPRD = EPWM_TIMER_TBPRD;// Set timer period 1500/2 TBCLKsEPwm1Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0EPwm1Regs.TBCTR = 0x0000; // Clear counter// Set Compare valuesEPwm1Regs.CMPA.half.CMPA = EPWM_CMPAB; // Set compare A value// EPwm1Regs.CMPB = EPWM_CMPAB; // Set Compare B value// Setup counter modeEPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up downEPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE; // enable phase loading use for syncEPwm1Regs.TBCTL.bit.PHSDIR=TB_UP;EPwm1Regs.TBCTL.bit.SYNCOSEL=TB_SYNC_IN;EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV2+TB_DIV4+TB_DIV4; // TBClock ratio = SYSCLKOUT/(2*HSPCLKDIV*EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // 2^CLKDIV)// Setup shadowingEPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;// EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero// EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;// Set actionsEPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on event A, up countEPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR; // Clear PWM1A on event A, down count// EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; //Clear PWM1B on event A, up count// EPwm1Regs.AQCTLB.bit.CAD = AQ_SET; // Set PWM1B on event A, down count// Set DeadBandEPwm1Regs.DBCTL.bit.IN_MODE=DBA_ALL;EPwm1Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;EPwm1Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;EPwm1Regs.DBRED=Dbred; // Dead-band rising edge delayEPwm1Regs.DBFED=Dbfed; // Dead-band falling edge delay// Set Trip ZoneEPwm1Regs.TZSEL.bit.OSHT1=TZ_ENABLE;EPwm1Regs.TZCTL.bit.TZA=TZ_FORCE_LO;EPwm1Regs.TZCTL.bit.TZB=TZ_FORCE_LO;// Interrupt where we will change the Compare ValuesEPwm1Regs.ETSEL.bit.SOCBSEL= ET_CTR_ZERO;// Select start ADC (EPWMxSOCB) on Zero eventEPwm1Regs.ETSEL.bit.SOCBEN= Enable; // EnableEPwm1Regs.ETPS.bit.SOCBPRD=ET_1ST;主要注意的就是EPWM的死区子模块。

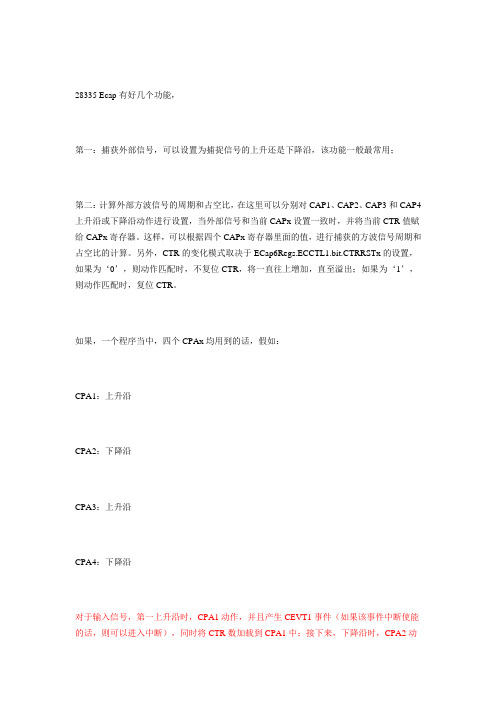

28335Ecap有好几个功能,

28335 Ecap有好几个功能,第一:捕获外部信号,可以设置为捕捉信号的上升还是下降沿,该功能一般最常用;第二:计算外部方波信号的周期和占空比,在这里可以分别对CAP1、CAP2、CAP3和CAP4上升沿或下降沿动作进行设置,当外部信号和当前CAPx设置一致时,并将当前CTR值赋给CAPx寄存器。

这样,可以根据四个CAPx寄存器里面的值,进行捕获的方波信号周期和占空比的计算。

另外,CTR的变化模式取决于ECap6Regs.ECCTL1.bit.CTRRSTx的设置,如果为‘0’,则动作匹配时,不复位CTR,将一直往上增加,直至溢出;如果为‘1’,则动作匹配时,复位CTR。

如果,一个程序当中,四个CPAx均用到的话,假如:CPA1:上升沿CPA2:下降沿CPA3:上升沿CPA4:下降沿对于输入信号,第一上升沿时,CPA1动作,并且产生CEVT1事件(如果该事件中断使能的话,则可以进入中断),同时将CTR数加载到CPA1中;接下来,下降沿时,CPA2动作,并且产生CEVT2事件(如果该事件中断使能的话,则可以进入中断),同时将CTR 数加载到CPA2中;再接下来,上升沿时,CPA3动作,并且产生CEVT3事件(如果该事件中断使能的话,则可以进入中断),同时将CTR数加载到CPA3中;再接下来,下降沿时,CPA4动作,并且产生CEVT4事件(如果该事件中断使能的话,则可以进入中断),同时将CTR数加载到CPA4中;接下来在从CPA1往返动作。

这时在一个循环里,可以利用四个CAPx里面的值进行周期和占空比的计算。

如果,程序不需要计算输入信号的周期和占空比,那么可能只要用到一个CAPx,这时就更简单了。

(如下面觉得例子),这时CTR可以不运行(ECap6Regs.ECCTL2.bit.TSCTRSTOP = EC_FREEZE),CAPx寄存器加载也可以禁止(ECap6Regs.ECCTL1.bit.CAPLDEN =EC_DISABLE;)。

TMS320F28335中文资料(难得的资料)

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.XINT2 = &ISRExint; //告诉中断入口地址

EDIS; // This is needed to disable write to EALLOW protected registers

F28335 是带浮点运算的,动态范围更大。 F2833x 的执行速度,比相同时钟频率的 F28xx 系列定点芯片,快 50%。处理数学运算性能提

升 2.45 倍,控制算法性能提升 1.57 倍,DSP 性能提升 1.38 倍。总体性能提升近 2 倍。

TMS320F28335 的 ADC

TMS320F28335 上有 16 通道、12 位的模数转换器 ADC。他可以被配置为两个独立的 8 通道输 入模式,也可以通过配置 AdcRegs.ADCTRL1.bit.SEQ_CASC=1,将其设置为一个 16 通道的级 联输入模式。输入的方式可以通过配置 AdcRegs.ADCTRL1.bit.ACQ_PS=1,将其设置为顺序

{

EALLOW; // Before setting PLLCR turn off missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1; SysCtrlRegs.PLLCR.bit.DIV = val; EDIS;

// Optional: Wait for PLL to lock. // During this time the CPU will switch to OSCCLK/2 until // the PLL is staPU will

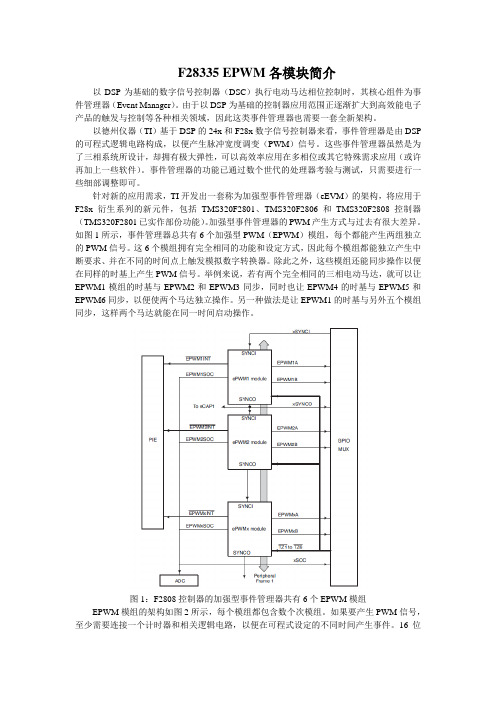

F28335 EPWM各模块简介

F28335 EPWM各模块简介以DSP为基础的数字信号控制器(DSC)执行电动马达相位控制时,其核心组件为事件管理器(Event Manager)。

由于以DSP为基础的控制器应用范围正逐渐扩大到高效能电子产品的触发与控制等各种相关领域,因此这类事件管理器也需要一套全新架构。

以德州仪器(TI)基于DSP的24x和F28x数字信号控制器来看,事件管理器是由DSP 的可程式逻辑电路构成,以便产生脉冲宽度调变(PWM)信号。

这些事件管理器虽然是为了三相系统所设计,却拥有极大弹性,可以高效率应用在多相位或其它特殊需求应用(或许再加上一些软件)。

事件管理器的功能已通过数个世代的处理器考验与测试,只需要进行一些细部调整即可。

针对新的应用需求,TI开发出一套称为加强型事件管理器(eEVM)的架构,将应用于F28x衍生系列的新元件,包括TMS320F2801、TMS320F2806和TMS320F2808控制器(TMS320F2801已实作部份功能)。

加强型事件管理器的PWM产生方式与过去有很大差异。

如图1所示,事件管理器总共有6个加强型PWM(EPWM)模组,每个都能产生两组独立的PWM信号。

这6个模组拥有完全相同的功能和设定方式,因此每个模组都能独立产生中断要求、并在不同的时间点上触发模拟数字转换器。

除此之外,这些模组还能同步操作以便在同样的时基上产生PWM信号。

举例来说,若有两个完全相同的三相电动马达,就可以让EPWM1模组的时基与EPWM2和EPWM3同步,同时也让EPWM4的时基与EPWM5和EPWM6同步,以便使两个马达独立操作。

另一种做法是让EPWM1的时基与另外五个模组同步,这样两个马达就能在同一时间启动操作。

图1:F2808控制器的加强型事件管理器共有6个EPWM模组EPWM模组的架构如图2所示,每个模组都包含数个次模组。

如果要产生PWM信号,至少需要连接一个计时器和相关逻辑电路,以便在可程式设定的不同时间产生事件。

28335的eCAP数据手册翻译

8

SWSYNC 软件强制计数器同步。它提供一个简便的软件方法使

一些或者所有 ECAP 时基同步。在 APWM 模式下也

可以通过 CTR=PRD 实现同步。

0:无影响。

1:强制同步。写 1 后,该位返回一个 0

注意:选择 CTR=PRD 意味着仅限于 APWM 模式。

7-6 SYNCO_SEL 同步输出选择

在 APWM 模式下 CAP1 与 CAP2 寄存器为有效的周期寄存器和比较寄存器; CAP3 与 CAP4 寄存器相对 CAP1 与 CAP2 寄存器为独立的影子寄存器(APRD 与 ACMP)。

4.6 中断控制

捕捉事件的发生(CEVT1-CEVT4,CTROVF)或者 APWM 事件的发生 (CTR=PRD,CTR=CMP)都将会产生一个中断请求。

7

南京研旭电气

( ECCLR ) 清 除 全 局 中 断 标 志 和 相 应 的 中 断 事 件 。 通 过 强 制 中 断 寄 存 器 (ECFRC)可以强制发生某个中断事件,这个在测试的时候比较有用。

eCAP 模块中的中断 注 意 : CEVT1 、 CEVT2 、 CEVT3 、 CEVT4 标 志 工 作 在 捕 捉 模 式 (ECCTL2[CAP/APWM]==0);CTR=PRD,CTR=CMP 标志工作在 APWM 模 式(ECCTL2[CAP/APWM]==1);CNTOVF 标志在两种模式下都可工作。

1 描述

eCAP 模块有以下关键的资源: ● 依赖一个引脚作为输入信号 ● 32 位计数器 ● 4 个 32 位时间标志寄存器(CAP1-CAP4) ● Mod4 计数器可以在 eCAP 输入引脚的上升沿/下降沿的时候将自身计数与外

部事件同步 ● 四件捕捉事件可以各自选择捕捉边沿(上升沿/下降沿) ● 对输入信号可以进行分频(分频系数为 2-62) ● 在 1-4 个捕捉事件发生后,一个 2 位的单次比较寄存器可以暂停捕捉信号 ● 使用一个四级深度的环形缓存(CAP1-CAP4)来存储连续捕捉模式下的时间

基于TMS320F28335的开关电源模块并联供电系统

摘要本系统以DSPMS320C28335作为主控,以单端反激式电路作为核心,根据AD采集两路DC模块输出电路分别控制两路PWM,做出相应调整,从而实现在4.0A以内,A、B两路DC模块电流比例在0.5~2.0之间步进为0.1的比例可调。

测试表明,本系统达到了题目的基本要求和扩展要求的全部功能。

开关电源模块并联供电系统(A题)【本科组】一、系统方案本系统主要由DC-DC主回路模块、信号采样模块、主控模块、电源模块组成,下面分别论证这几个模块的选择。

1.1 DC-DC主回路的论证与选择方案一:采用推挽拓扑。

推挽拓扑因其变压器工作在双端磁化情况下而适合应用在低压大电流的场合。

但是,推挽电路中的高频变压器如果在绕制中两臂不对称,就会使变压器因磁通不平衡而饱和,从何导致开关管烧毁;同时,由于电路中需要两个开关管,系统损耗将会很大。

方案二:采用Boost升压拓扑。

Boost电路结构简单、元件少,因此损耗较少,电路转换效率高。

但是,Boost电路只能实现升压而不能降压,而且输入/输出不隔离。

方案三:采用单端反激拓扑。

单端反激电路结构简单,适合应用在大电压小功率的场合。

由于不需要储能电感,输出电阻大等原因,电路并联使用时均流性较好。

方案论证:上述方案中,方案一系统损耗大,方案二不能实现输入输出隔离,而方案三虽然对高频变压器设计要求较高,但系统要求两个DCDC模块并联,并且对效率有一定要求。

因此,选择单端反激电路作为本系统的主回路拓扑。

1.2 控制方法及实现方案方案一:采用专用的开关电源芯片及并联开关电源均流芯片。

这种方案的优点是技艺成熟,且均流的精度高,实现成本较低。

但这种方案的缺点是控制系统的性能取决于外围电路元件参数的选择,如果参数选择不当,则输出电压难以维持稳定。

方案二:采用TI公司的DSP TMS320C28335作为主控,实现PWM输出,并控制A/D对输入输出的电压电流信号进行采样,从而进行可靠的闭环控制。

DSP28335eCAP测频

DSP28335eCAP测频F28335共有6组eCAP模块,每个eCAP不但具有捕获功能,⽽且还可⽤作PWM输出功能。

F28335捕获模块的主要特征如下: 1. 150MHz系统时钟的情况下,32位时基的时间分辨率为6.67ns; 2. 4组32位的时间标志寄存器; 3. 4级捕获事件序列,可以灵活配置捕获事件边沿极性; 4. 四级触发事件均可以产⽣中断; 5. 软件配置⼀次捕获可以最多得到4个捕获时间; 6. 可连续循环4级捕获; 7. 绝对时间捕获; 8. 不同模式的时间捕获; 9. 所有捕获都发⽣在⼀个输⼊引脚上; 10. 如果eCAP模块不作捕获使⽤,可以配置成⼀个单通道输出的PWM模式。

eCAP模块中⼀个捕获通道完成⼀次捕获任务,需要以下关键资源: 1、专⽤捕获输⼊引脚; 2、32位时基(计数器); 3、4*32位时间标签捕获寄存器; 4、4级序列器,与外部eCAP引脚的上升/下降沿同步; 5、4个事件可独⽴配置边沿极性; 6、输⼊捕获信号预定标(2-62); 7、⼀个2位的⽐较寄存器,⼀次触发后可以捕获4个时间标签事件; 8、采⽤4级深度的循环缓冲器以进⾏连续捕获; 9、4个捕获事件中任意⼀个都可以产⽣中断。

DSP2833x_SysCtrl.h// Peripheral clock control register 1 bit definitions:struct PCLKCR1_BITS { // bits descriptionUint16 EPWM1ENCLK:1; // 0 Enable SYSCLKOUT to EPWM1Uint16 EPWM2ENCLK:1; // 1 Enable SYSCLKOUT to EPWM2Uint16 EPWM3ENCLK:1; // 2 Enable SYSCLKOUT to EPWM3Uint16 EPWM4ENCLK:1; // 3 Enable SYSCLKOUT to EPWM4Uint16 EPWM5ENCLK:1; // 4 Enable SYSCLKOUT to EPWM5Uint16 EPWM6ENCLK:1; // 5 Enable SYSCLKOUT to EPWM6Uint16 rsvd1:2; // 7:6 reservedUint16 ECAP1ENCLK:1; // 8 Enable SYSCLKOUT to ECAP1 系统时钟150MHzUint16 ECAP2ENCLK:1; // 9 Enable SYSCLKOUT to ECAP2Uint16 ECAP3ENCLK:1; // 10 Enable SYSCLKOUT to ECAP3Uint16 ECAP4ENCLK:1; // 11 Enable SYSCLKOUT to ECAP4Uint16 ECAP5ENCLK:1; // 12 Enable SYSCLKOUT to ECAP5Uint16 ECAP6ENCLK:1; // 13 Enable SYSCLKOUT to ECAP6Uint16 EQEP1ENCLK:1; // 14 Enable SYSCLKOUT to EQEP1Uint16 EQEP2ENCLK:1; // 15 Enable SYSCLKOUT to EQEP2}; 由上⾯代码可知eCAP模块的时钟为系统时钟,时基是6.67ns#define EC_RISING 0 //上升沿电平值#define EC_FALLING 1 //下降沿电平值#define EC_ABS_MODE 0 //在CAPx事件中不重置计数器#define EC_ENABLE 1 //使能在捕获事件中加载CAP1-4寄存器的时间#define EC_DIV1 00000 //输⼊信号分频选择不分频#define EC_CAP_MODE 0 //ECAP⼯作于捕获⼯作模式#define EC_CONTINUOUS 0 //0为连续模式 1为单次模式#define EC_SYNCO_DIS 2 //同步输出选择: 10、11屏蔽同步信号输出#define EC_DISABLE 0 //屏蔽同步输⼊操作#define EC_RUN 1 //1计数器启动 0计数器停⽌ 以上代码为宏定义void InitECAP(){SysCtrlRegs.PCLKCR1.bit.ECAP1ENCLK = 1;//使能eCAP1SysCtrlRegs.PCLKCR1.bit.ECAP2ENCLK = 1;//使能eCAP2// SysCtrlRegs.PCLKCR1.bit.ECAP3ENCLK = 1;//使能eCAP3// SysCtrlRegs.PCLKCR1.bit.ECAP4ENCLK = 1;//使能eCAP4// SysCtrlRegs.PCLKCR1.bit.ECAP5ENCLK = 1;//使能eCAP5// SysCtrlRegs.PCLKCR1.bit.ECAP6ENCLK = 1;//使能eCAP6IER |= M_INT4;//ECap1Regs.ECEINT.all = 0x0000; // Disable all capture interruptsECap1Regs.ECCLR.all = 0xFFFF; // Clear all CAP interrupt flagsECap1Regs.ECCTL1.bit.CAPLDEN = 0; // Disable CAP1-CAP4 register loadsECap1Regs.ECCTL2.bit.TSCTRSTOP = 0; // Make sure the counter is stoppedSetCap1();SetCap2();}void SetCap1(){ECap1Regs.ECCTL1.bit.CAP1POL = EC_RISING; //⼀级事件捕捉上升沿ECap1Regs.ECCTL1.bit.CAP2POL = EC_RISING; //⼆级事件捕捉上升沿ECap1Regs.ECCTL1.bit.CAP3POL = EC_RISING; //三级事件捕捉上升沿ECap1Regs.ECCTL1.bit.CAP4POL = EC_RISING; //四级事件捕捉上升沿ECap1Regs.ECCTL1.bit.CTRRST1 = EC_ABS_MODE; //⼀级事件捕捉后不清零计数器ECap1Regs.ECCTL1.bit.CTRRST2 = EC_ABS_MODE; //⼆级事件捕捉后不清零计数器ECap1Regs.ECCTL1.bit.CTRRST3 = EC_ABS_MODE; //三级事件捕捉后不清零计数器ECap1Regs.ECCTL1.bit.CTRRST4 = EC_ABS_MODE; //四级事件捕捉后不清零计数器ECap1Regs.ECCTL1.bit.CAPLDEN = EC_ENABLE; //使能事件捕捉时捕捉寄存器装载计数器值 ECap1Regs.ECCTL1.bit.PRESCALE = EC_DIV1; //对外部信号不分频ECap1Regs.ECCTL2.bit.CAP_APWM = EC_CAP_MODE; //捕捉模式ECAPECap1Regs.ECCTL2.bit.CONT_ONESHT = EC_CONTINUOUS; //连续模式ECap1Regs.ECCTL2.bit.SYNCO_SEL = EC_SYNCO_DIS; //屏蔽同步信号输出ECap1Regs.ECCTL2.bit.SYNCI_EN = EC_DISABLE; //屏蔽同步输⼊操作ECap1Regs.ECEINT.all=0x0000; //关闭所有 CAP 中断ECap1Regs.ECCLR.all=0xFFFF; //清除所有中断标志位ECap1Regs.ECCTL2.bit.TSCTRSTOP = EC_RUN; //启动 CAP 计数器ECap1Regs.ECEINT.bit.CEVT4=1; //使能四级事件中断,即当发⽣第四次捕捉时进⼊中断} 在四级事件后进中断interrupt void ECAP1_INT_ISR(void) // ECAP-1{// Insert ISR Code hereUint32 t1,t2,t3,t4,T1,T2;t1 = ECap1Regs.CAP1;t2 = ECap1Regs.CAP2;t3 = ECap1Regs.CAP3;t4 = ECap1Regs.CAP4;T1 = t2-t1;T2 = t4-t3;// To receive more interrupts from this PIE group, acknowledge this interruptPieCtrlRegs.PIEACK.all = PIEACK_GROUP4;ECap1Regs.ECCLR.all=0xFFFF; //clare all flag}。

TMS320F28335中文资料

TMS320F28335中文资料TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM 和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断.GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序.OTP ROM区(0×38 0000~0×38 03FF)为只读空间,存储A/D转换器的校准程序,用户不能对此空间写入程序。

tms320f28335原理及其在电气工程中的应用

tms320f28335原理及其在电气工程中的应用TMS320F28335是一款基于32位定点数字信号处理器(DSP)的芯片,由德州仪器公司(Texas Instruments)生产。

它具有高速、高效、低功耗等优点,广泛应用于各种电气工程领域。

TMS320F28335基于C28x内核架构,拥有高达150MHz的最高工作频率,可以实现复杂的数字信号处理和控制算法,如矢量控制、PID调节、滤波、FFT等。

此外,它还拥有多种外设接口,如GPIO、CAN、SPI、I2C等,可以实现各种外部设备的连接和数据通信。

在电气工程领域中,TMS320F28335主要应用于电力电子、电机控制、光伏发电、电网无功补偿、智能电网等方面。

具体应用包括:

1. 电机控制:TMS320F28335内置了多种PWM输出模块和编码器接口,可以实现高性能的电机控制,如直接矢量控制、间接矢量控制等。

2. 电力电子:TMS320F28335可以实现各种电力电子开关器件的PWM控制,如IGBT、MOSFET、整流器等,实现电力变换、能量转换和电子调节等功能。

3. 光伏发电:TMS320F28335可以与光伏逆变器的控制器相结合,通过MPPT 算法实现对光伏电池板的最大功率追踪,提高光伏发电效率。

4. 智能电网:TMS320F28335可以与智能电网控制器相结合,实现对电网的无功补偿、电网状态监测、分布式发电控制等功能。

总之,TMS320F28335作为一款高性能的DSP芯片,具有广泛的应用前景,在电气工程领域中将有着越来越广泛的应用。

TMS320F28335在电网频率测量中的

TMS320F28335在电网频率测量中的

本文提出了一种基于TMS320F28335 的频率测量方法,用于监测电力系统的电能质量。

该方法采用DSP 的eCAP 模块和通用定时器对输入信号的上升沿进行捕捉,通过记录两个上升沿的触发时间得到输入信号的频率。

与软件测频方法相比,其硬件电路简单,可靠性高、实时性好。

理论分析和实验测试表明,该方法测频精度高,很好的满足了电能质量监测装置的要求。

引言:

频率是衡量电能质量的重要指标,也是判断电力系统故障的重要依据。

一般情况下,电力系统的频率会随着负荷的波动而有所变化。

在正常情况下电网频率变化缓慢,即使发生系统事故,在很短的时间内( 如一个工频周期) 电网频率的变化量也是较小的。

频率测量若能不断实时地测量电网频率,所测量的频率误差可减小到很小的程度。

数字频率的测量方法主要有:( 1) 测量电压波形某一整数周波的时间,从而计算频率; ( 2) 利用波形识别或曲线拟合技术来估算频率。

后一种方法不能很好的抑制谐波分量,计算量偏大,要对每一周波都进行一次计。

tms320f28335的gpioa组控制原理

tms320f28335的gpioa组控制原理TMS320F28335的GPIOA组控制简介TMS320F28335是德州仪器(Texas Instruments)推出的一款高性能数字信号处理器(DSP)。

作为一名资深的创作者,学习如何利用TMS320F28335的GPIOA组进行控制是十分重要的。

GPIO(General Purpose Input Output)是通用输入输出口,可以连接外部设备和传感器,用于数据的输入和输出。

本文将深入浅出地介绍TMS320F28335的GPIOA组控制的相关原理,帮助读者了解如何使用这个强大的功能。

GPIOA组GPIOA组是TMS320F28335芯片的一部分,它提供了32个独立的GPIO引脚,可以通过编程将其配置为输入或输出。

这些引脚可以连接到外部设备,例如LED灯、开关、传感器等。

引脚配置在开始控制GPIOA组之前,首先需要将引脚配置为输入或输出模式。

可以通过设置特定的寄存器来实现。

输入模式将引脚配置为输入模式时,可以读取外部设备或传感器的信号。

下面是配置引脚为输入模式的示例代码:= 0; // 设置GPIO0为普通IO口= 0; // 设置GPIO0为输入上述代码将将GPIO0配置为输入模式。

通过修改GPIO0的GPAMUX1和GPADIR寄存器的特定位,可以实现配置其他引脚为输入模式的操作。

输出模式将引脚配置为输出模式时,可以向外部设备发送信号。

下面是配置引脚为输出模式的示例代码:= 0; // 设置GPIO1为普通IO口= 1; // 设置GPIO1为输出上述代码将将GPIO1配置为输出模式。

通过修改GPIO1的GPAMUX1和GPADIR寄存器的特定位,可以实现配置其他引脚为输出模式的操作。

读取输入一旦将引脚配置为输入模式,就可以读取与之连接的外部设备或传感器的信号。

下面是读取输入信号的示例代码:Uint16 input = ; // 读取GPIO0的输入信号上述代码将GPIO0的输入信号读取到变量input中。

TMS320F28335在电网频率测量中的应用

TMS320F28335在电网频率测量中的应用本文提出了一种基于TMS320F28335 的频率测量方法,用于监测电力系统的电能质量。

该方法采用DSP 的eCAP 模块和通用定时器对输入信号的上升沿进行捕捉,通过记录两个上升沿的触发时间得到输入信号的频率。

与软件测频方法相比,其硬件电路简单,可靠性高、实时性好。

理论分析和实验测试表明,该方法测频精度高,很好的满足了电能质量监测装置的要求。

引言:频率是衡量电能质量的重要指标,也是判断电力系统故障的重要依据。

一般情况下,电力系统的频率会随着负荷的波动而有所变化。

在正常情况下电网频率变化缓慢,即使发生系统事故,在很短的时间内( 如一个工频周期) 电网频率的变化量也是较小的。

频率测量若能不断实时地测量电网频率,所测量的频率误差可减小到很小的程度。

数字频率的测量方法主要有: ( 1) 测量电压波形某一整数周波的时间,从而计算频率; ( 2) 利用波形识别或曲线拟合技术来估算频率。

后一种方法不能很好的抑制谐波分量,计算量偏大,要对每一周波都进行一次计算,将会占用过多的处理器时间,其不能兼顾计算精度与实时性。

而前者的测量精度受电压过零点的影响较大。

本文提出通过过零检测电路将电网基波整型成方波,用TMS320F28335( DSP) 的捕捉模块对方波上升沿进行捕捉的频率测量方法,在一定程度上抑制了电压过零点的影响,有很好的测量精度和实时性。

1 通用定时器与捕捉模块TMS320F28335 是指令周期为6. 67 ns。

主频达150 MHz; 高性能的32 位CPU , 单精度浮点运算单元( FPU ) , 采用哈佛流水线结构,能够快速执行中断响应。

并具有统一的内存管理模式。

本文提出的测频方法主要应用TMS320F28335 中的捕获单元( eCAP) 和通用定时器( GPT ) 单元。

1. 1 通用定时器通用定时器是TMS320F28335 常用的PIE 接口,其核心是计数器, 32 位计数。

TMS320F28335的EPWM参考手册中文-很有用.

DSP原理与应用The Technology & Applications of DSP北京交通大学电气工程学院郝瑞祥haorx@本页已使用福昕阅读器进行编辑。

福昕软件(C)2005-2009,版权所有,仅供试用。

§7.1F28335的PWM控制●每个ePWM模块都支持下列特性:●精确的16位时间定时器,可以进行周期和频率控制。

●两个PWM输出(EPWMxA and EPWMxB) 可以用于下面的控制●–两个独立的PWM输出进行单边控制●–两个独立的PWM输出进行双边对称控制●–一个独立的PWM输出进行双边非对称控制●与其它ePWM模块有关的可编程超前和滞后相控。

●在一个循环基础上的硬件锁定(同步)相位关系。

●独立的上升沿和下降沿死区延时控制●可编程控制故障区(trip zone)用于故障时的周期循环控制(trip)和单次(one-shot)控制.●一个控制条件可以使PWM输出强制为高,低,或高阻逻辑电平.●所有事件都可以触发CPU中断,启动ADC开始转换。

●可编程事件有效降低了在中断时CPU的负担。

●PWM高频载波信号对于脉冲变压器门极驱动非常有用。

本页已使用福昕阅读器进行编辑。

福昕软件(C)2005-2009,版权所有,仅供试用。

多个ePWM模块结构框图ePWM模块的子模块和信号连接模块相关信号说明如下:●PWM 输出信号(EPWMxA and EPWMxB) (x=1…6)●通过IO引脚输出PWM信号.●Trip-zone 信号(TZ1 to TZ6).这些输入信号警告ePWM模块有外部故障发生。

设备的每个模块都可以配置成使用或者忽略任何故障区信号(Trip-zone)。

这些信号可以设置为通用IO外设的异步输入。

●基于时间的同步输入信号(EPWMxSYNCI)和输出(EPWMxSYNCO)信号.同步信号雏菊花形将ePWM模块连接在一起。

每个模块可以配置成使用或忽略其同步输入信号。

DSP28335eCAP模块使用总结

DSP28335eCAP模块使⽤总结28335DSP的捕获模块(ECAP)的⼀些使⽤总结(转帖)留着⽇后⽤个⼈理解的捕获模块就是在捕捉到跳变时(上升沿或下降沿)将定时器的值存⼊寄存器,通过时间来计算周期和频率。

因为本⼈也是初学,讲不清楚,还请⼤家看下⾯的讲解吧。

有使⽤OMAPL138的亲的话可以⼀起交流⼀下啊~~第⼀:捕获外部信号,可以设置为捕捉信号的上升还是下降沿,该功能⼀般最常⽤;第⼆:计算外部⽅波信号的周期和占空⽐,在这⾥可以分别对CAP1、CAP2、CAP3和CAP4上升沿或下降沿动作进⾏设置,当外部信号和当前CAPx设置⼀致时,并将当前CTR值赋给CAPx寄存器。

这样,可以根据四个CAPx寄存器⾥⾯的值,进⾏捕获的⽅波信号周期和占空⽐的计算。

另外,CTR的变化模式取决于ECap6Regs.ECCTL1.bit.CTRRSTx的设置,如果为‘0’,则动作匹配时,不复位CTR,将⼀直往上增加,直⾄溢出;如果为‘1’,则动作匹配时,复位CTR。

如果,⼀个程序当中,四个CPAx均⽤到的话,假如:CPA1:上升沿CPA2:下降沿CPA3:上升沿CPA4:下降沿对于输⼊信号,第⼀上升沿时,CPA1动作,并且产⽣CEVT1事件(如果该事件中断使能的话,则可以进⼊中断),同时将CTR数加载到CPA1中;接下来,下降沿时,CPA2动作,并且产⽣CEVT2事件(如果该事件中断使能的话,则可以进⼊中断),同时将CTR数加载到CPA2中;再接下来,上升沿时,CPA3动作,并且产⽣CEVT3事件(如果该事件中断使能的话,则可以进⼊中断),同时将CTR数加载到CPA3中;再接下来,下降沿时,CPA4动作,并且产⽣CEVT4事件(如果该事件中断使能的话,则可以进⼊中断),同时将CTR数加载到CPA4中;接下来在从CPA1往返动作。

这时在⼀个循环⾥,可以利⽤四个CAPx⾥⾯的值进⾏周期和占空⽐的计算。

如果,程序不需要计算输⼊信号的周期和占空⽐,那么可能只要⽤到⼀个CAPx,这时就更简单了。

以TMS320F28335为主处理器的车载智能电源控制器的设计

以TMS320F28335为主处理器的车载智能电源控制器的设计1.系统需求分析:车载智能电源控制器的设计要满足以下基本需求:-能够监测车辆电池的电压和电流,并实时反馈给主处理器。

-根据实时检测到的电池情况,控制发电机的输出电压和电流,以保证电池的正常充电。

-实现智能管理和优化电池的使用,延长电池的寿命。

-对电池的充电状态进行监测和保护,避免过充和过放。

2.硬件设计:-包括电压和电流传感器、电池电压分压器、发电机控制电路等在内的外围电路的设计。

电压和电流传感器用于检测电池的电压和电流,将数据传输给主处理器。

电池电压分压器用于将电池电压降低到适合主处理器的输入电压范围。

发电机控制电路负责对发电机的输出电压和电流进行调节和控制。

3.软件设计:-主处理器的软件设计主要包括以下几个方面:1)电池电压和电流的实时监测和反馈:主处理器通过读取电压和电流传感器的数据,实时监测车辆电池的状态,并将数据反馈给其他相关模块进行处理。

2)发电机控制:根据电池的状态和需要,主处理器通过发电机控制电路对发电机的输出电压和电流进行调节和控制,以实现电池的正常充电。

3)电池管理:主处理器通过智能算法对电池的使用情况进行分析,并根据实时需求对电池进行优化管理,延长电池的使用寿命。

4)充电状态监测和保护:主处理器通过读取电池的电压和电流数据,实时监测电池的充电状态,并对电池进行保护措施,避免过充和过放。

4.系统性能:-车载智能电源控制器的设计需要满足以下性能指标:1)准确性:电池电压和电流的实时监测需要具备高准确性,以确保充电系统的稳定性和安全性。

2)响应速度:主处理器需要具备快速的响应能力,及时调节发电机的输出电压和电流,以满足车辆电池的需要。

3)功耗控制:主处理器的功耗应尽量低,以减少对车辆电池的能源消耗,延长整个系统的使用寿命。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

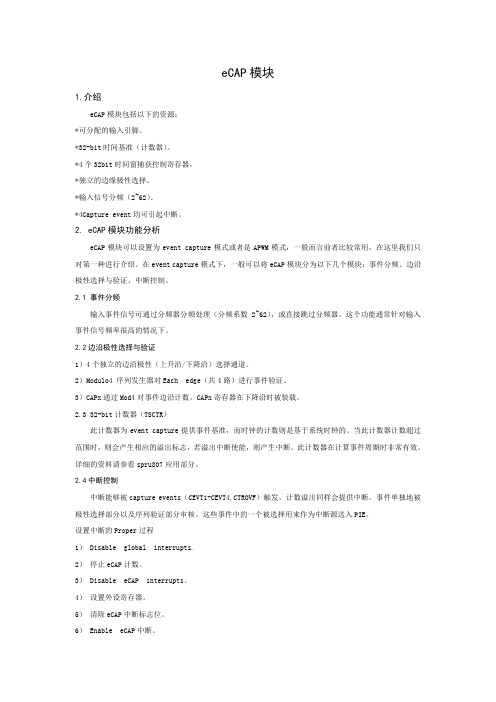

eCAP模块

1.介绍

eCAP模块包括以下的资源:

*可分配的输入引脚。

*32-bit时间基准(计数器)。

*4个32bit时间窗捕获控制寄存器。

*独立的边缘极性选择。

*输入信号分频(2~62)。

*4Capture event均可引起中断。

2. eCAP模块功能分析

eCAP模块可以设置为event capture模式或者是APWM模式,一般而言前者比较常用,在这里我们只对第一种进行介绍。

在event capture模式下,一般可以将eCAP模块分为以下几个模块:事件分频、边沿极性选择与验证、中断控制。

2.1 事件分频

输入事件信号可通过分频器分频处理(分频系数2~62),或直接跳过分频器。

这个功能通常针对输入事件信号频率很高的情况下。

2.2边沿极性选择与验证

1)4个独立的边沿极性(上升沿/下降沿)选择通道。

2)Modulo4 序列发生器对Each edge(共4路)进行事件验证。

3)CAPx通过Mod4对事件边沿计数。

CAPx寄存器在下降沿时被装载。

2.3 32-bit计数器(TSCTR)

此计数器为event capture提供事件基准,而时钟的计数则是基于系统时钟的。

当此计数器计数超过范围时,则会产生相应的溢出标志,若溢出中断使能,则产生中断。

此计数器在计算事件周期时非常有效。

详细的资料请参看spru807应用部分。

2.4中断控制

中断能够被capture events(CEVT1-CEVT4,CTROVF)触发。

计数溢出同样会提供中断。

事件单独地被极性选择部分以及序列验证部分审核。

这些事件中的一个被选择用来作为中断源送入PIE。

设置中断的Proper过程

1)Disable global interrupts.

2)停止eCAP计数。

3)Disable eCAP interrupts。

4)设置外设寄存器。

5)清除eCAP中断标志位。

6)Enable eCAP中断。

7)Start ecap 计数器。

8)Enable global 中断。

3. eCAP模块的理解

配置好eCAP模块的引脚后,外部事件由引脚输入,首先通过模块的分频部分,分频系数为2~62,也可以选择跳过分频部分。

经过分频部分后的信号(通常频率会降低),送至边沿及序列审核部分,边沿审核即设置为上升沿或下降沿有效,序列审核则是分配当前对哪个寄存器(CAP1~CAP4)作用的问题,之后就是中断部分了。

引起中断的中断源有7个,event capture模式下有五个,分别是审核后各路的事件以及溢出中断。