Quartus II 调用ModelSim 仿真

Quartus-II调用modelsim仿真方法

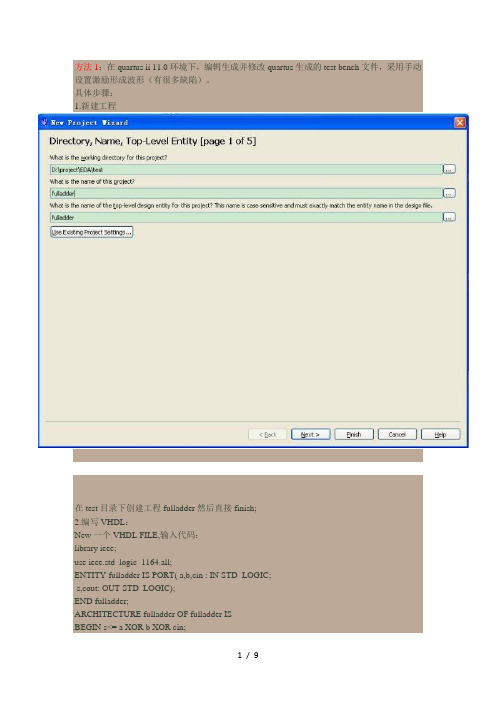

方法1:在quartus ii 11.0环境下,编辑生成并修改quartus生成的test bench文件,采用手动设置激励形成波形(有很多缺陷)。

具体步骤:1.新建工程在test目录下创建工程fulladder然后直接finish;2.编写VHDL:New一个VHDL FILE,输入代码:library ieee;use ieee.std_logic_1164.all;ENTITY fulladder IS PORT( a,b,cin : IN STD_LOGIC;s,cout: OUT STD_LOGIC);END fulladder;ARCHITECTURE fulladder OF fulladder ISBEGIN s<= a XOR b XOR cin;cout <=(a AND b) OR (a AND cin) OR (b AND cin);END fulladder;保存在test目录下,文件名为默认fulladder。

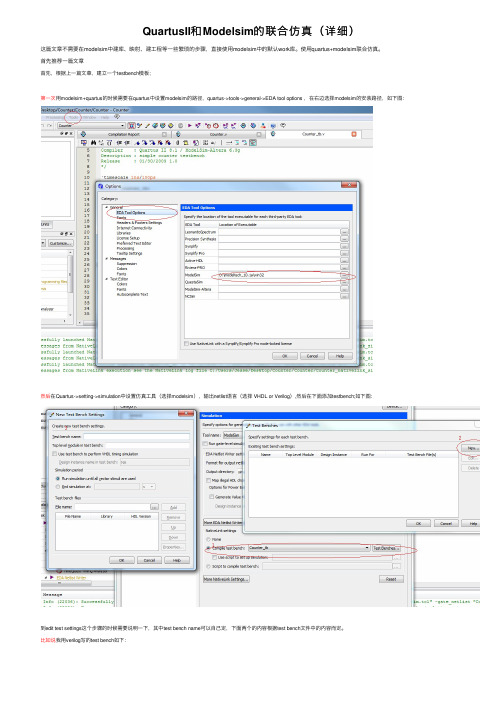

3. 在Quartes II 11.0界面菜单栏中选择 Tools-->options选项卡中选中EDA tool options,在该选项卡中下面的ModelSim-Altera一项指定安装路径为(如d:/Altera/11.0/modelsim_ae/win32aloem)4.在Quartes II 11.0界面菜单栏中选择Assignments->Settings。

选中该界面下EDA Tool settings中的Simulation一项;Tool name中选择ModelSim-Altera;Format for output netlist中选择开发语言的类型VHDL或其它,如图:然后点击APPLY应用和OK。

5.设置完成后,编译工程:在Quartus II 11.0界面菜单栏中选择菜单栏选择Processing-->start Compilation,等待编译,无错后会在test目录下生成simulation目录,执行下一步。

如何能从Quartus II中调用Modelsim进行仿真

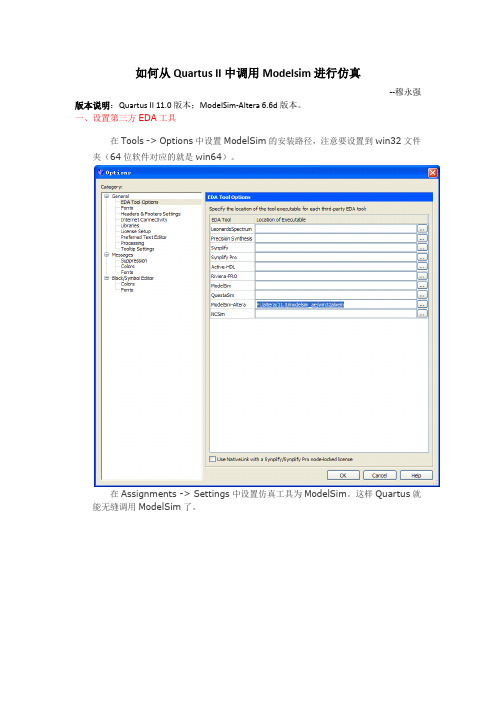

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

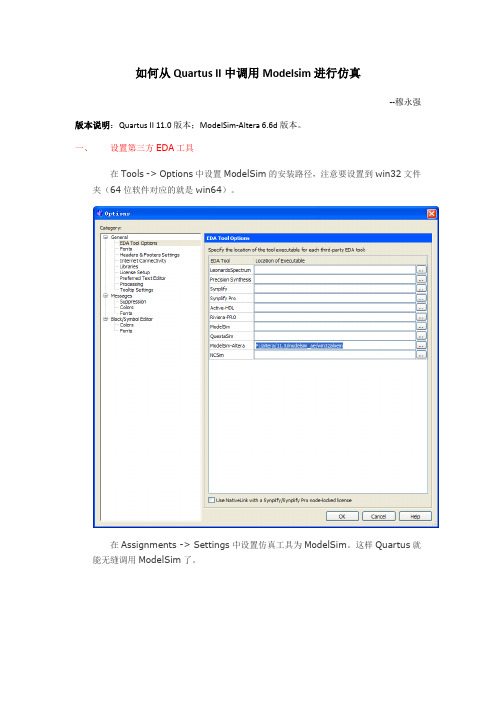

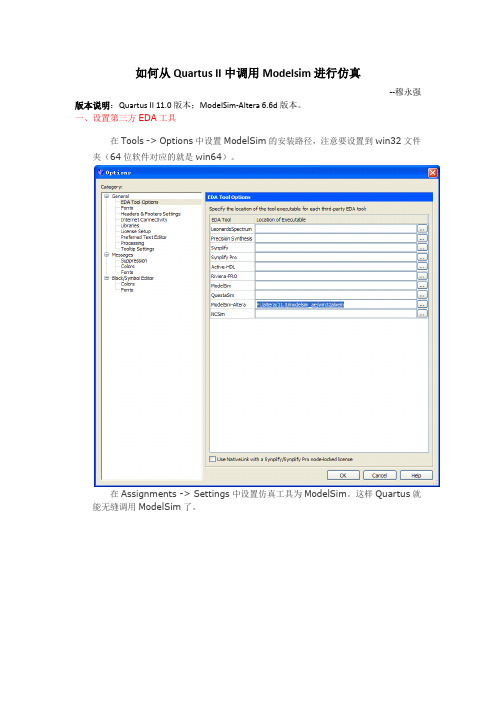

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

Quartus II调用ModelsimSE进行功能仿真

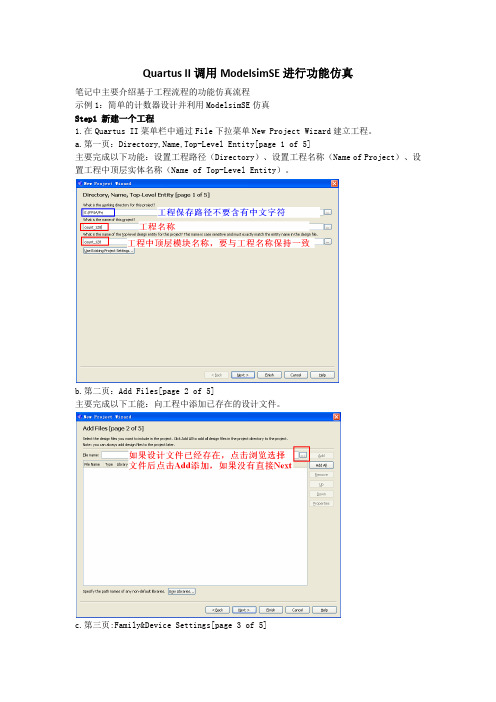

Quartus II调用ModelsimSE进行功能仿真笔记中主要介绍基于工程流程的功能仿真流程示例1:简单的计数器设计并利用ModelsimSE仿真Step1 新建一个工程1.在Quartus II菜单栏中通过File下拉菜单New Project Wizard建立工程。

a.第一页:Directory,Name,Top-Level Entity[page 1 of 5]主要完成以下功能:设置工程路径(Directory)、设置工程名称(Name of Project)、设置工程中顶层实体名称(Name of Top-Level Entity)。

b.第二页:Add Files[page 2 of 5]主要完成以下工能:向工程中添加已存在的设计文件。

c.第三页:Family&Device Settings[page 3 of 5]主要实现完成功能:选择自己所使用的FPGA芯片。

d.第四页:EDA Tool Settings[page 4 of 5]主要完成功能:根据需要选择使用哪种EDA工具Design Entry/Synthesis:设计输入/综合工具Simulation:仿真工具Timing Analysis:时序分析工具Format Verification:格式验证工具Board –Level:板级工具e.第五页:Summary[page 5 of 5]主要完成功能:生成建立工程的总结报告,包含了前面设置的内容。

根据报告查看新建工程是否与自己要建立的工程要求一致,如果不一致返回(<Back)上一层或多层进行修改,直到满足要求为止。

f.Finish:通过工程向导完成新建工程。

2.向新建工程中添加设计文件。

根据自己使用的HDL语言添加设计文件,Finish完成。

本示例中设计文件代码如下所示:完成一个简单的计数器,使计数器计数满128后重新计数。

module count_128(clk,rst_n,count);//工程模块及端口声明input clk,rst_n;//输入信号:时钟信号和复位output reg[7:0] count;//定义count位宽和数据类型always@(posedge clk or negedge rst_n)if(!rst_n)count<=8'd0;//复位置零else if(count[7])//当count最高位为1,也就是计数到128时,count置0count<=1'd0;else //否则继续计数count<=count+1'd1;endmodule/*计数模块实现128计数,当coun计数满128重新计数*/3.将设计文件保存在工程目录下并对设计文件进行语法分析。

QUARTUS II 与 MODELSIM联合仿真设置方法_经验总结

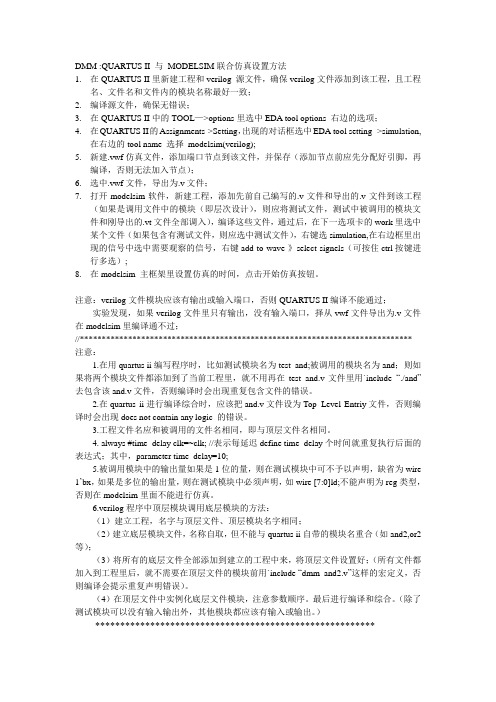

DMM :QUARTUS II 与MODELSIM联合仿真设置方法1.在QUARTUS II里新建工程和verilog 源文件,确保verilog文件添加到该工程,且工程名、文件名和文件内的模块名称最好一致;2.编译源文件,确保无错误;3.在QUARTUS II中的TOOL—>options里选中EDA tool options 右边的选项;4.在QUARTUS II的Assignments->Setting,出现的对话框选中EDA tool setting ->simulation,在右边的tool name 选择modelsim(verilog);5.新建.vwf仿真文件,添加端口节点到该文件,并保存(添加节点前应先分配好引脚,再编译,否则无法加入节点);6.选中.vwf文件,导出为.v文件;7.打开modelsim软件,新建工程,添加先前自己编写的.v文件和导出的.v文件到该工程(如果是调用文件中的模块(即层次设计),则应将测试文件,测试中被调用的模块文件和刚导出的.vt文件全部调入),编译这些文件,通过后,在下一选项卡的work里选中某个文件(如果包含有测试文件,则应选中测试文件),右键选simulation,在右边框里出现的信号中选中需要观察的信号,右键add to wave-》select signels(可按住ctrl按键进行多选);8.在modelsim 主框架里设置仿真的时间,点击开始仿真按钮。

注意:verilog文件模块应该有输出或输入端口,否则QUARTUS II编译不能通过;实验发现,如果verilog文件里只有输出,没有输入端口,择从vwf文件导出为.v文件在modelsim里编译通不过;//****************************************************************************注意:1.在用quartus ii编写程序时,比如测试模块名为test_and;被调用的模块名为and;则如果将两个模块文件都添加到了当前工程里,就不用再在test_and.v文件里用`include “./and”去包含该and.v文件,否则编译时会出现重复包含文件的错误。

Quartus II 直接调用 modelsim se 进行前仿真和后仿真

Quartus II 直接调用modelsim se 进行前仿真和后仿真Modelsim的独立版本仿真速度比Quartus自带的Modelsim-Altera快,且Modelsim的独立版本支持Verilog和VHDL语言的混合仿真,因此Modelsim-Altera尽管可以直接从Quartus 官方下载,但不少人仍然会选用独立版本的Modelsim进行设计仿真。

使用Modelsim-Altera非常方便,安装后Quartus已经做好了与Modelsim-Altera的链接。

如果使用独立版本的Modelsim,则需要自己手动配置才能将独立版本Modelsim与Quartus 链接使用。

以下以使用Quartus II 11.1sp2和modelsim se 10.0a进行工程的前仿真后后仿真为例进行介绍。

即在Quartus进行设置,直接通过Quartus II的菜单调用modelsim se运行前仿真和后仿真。

当然也可参照网上的介绍,编译modelsim的Altera库,在modelsim se中直接建立工程并运行仿真。

本文介绍通过在Quartus中进行设置,通过Quartus菜单直接调用运行modelsim se的仿真,配置好后就如同Altera官方的Modelsim-Altera版本一样使用简便。

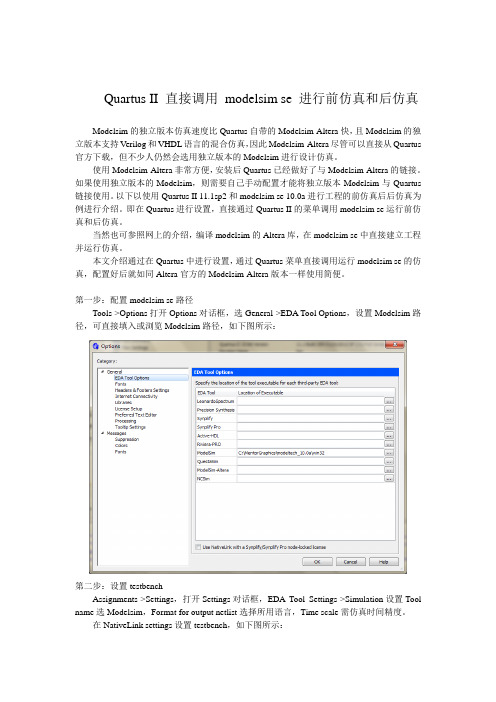

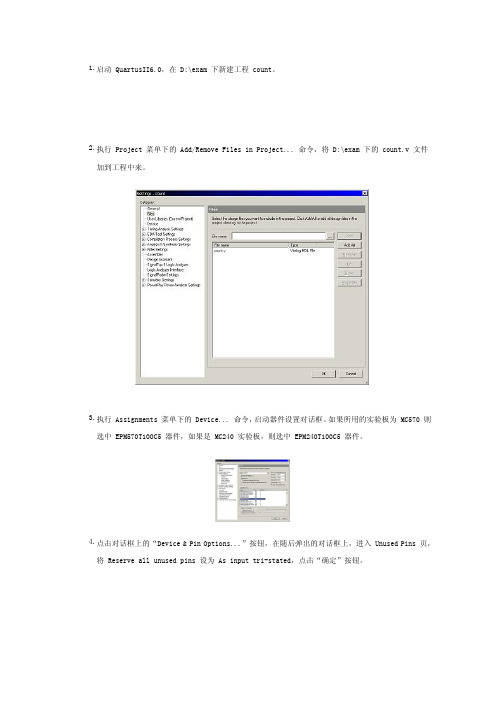

第一步:配置modelsim se路径Tools->Options打开Options对话框,选General->EDA Tool Options,设置Modelsim路径,可直接填入或浏览Modelsim路径,如下图所示:第二步:设置testbenchAssignments->Settings,打开Settings对话框,EDA Tool Settings->Simulation设置Tool name选Modelsim,Format for output netlist选择所用语言,Time scale需仿真时间精度。

VHDLQuartusII调用Modelsim进行仿真

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

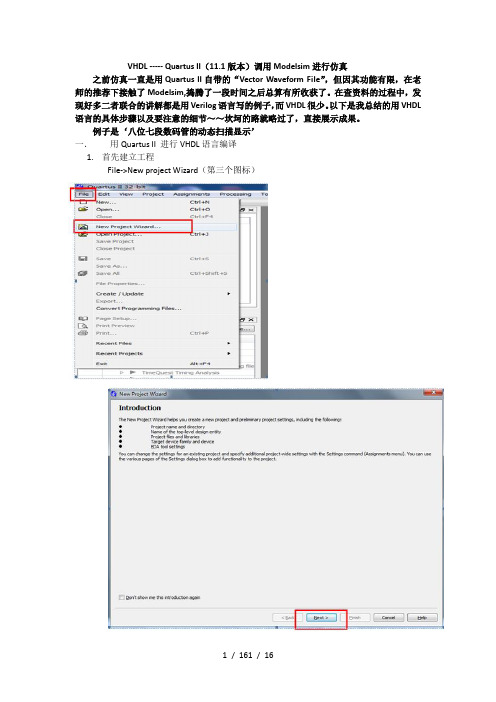

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

3.编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

QUARTUS II10.1调用modelsim仿真

QUARTUS II 10.1调用ModelSim-Altera仿真的过程(以上软件在六维空间上面都有,只有QUARTUS需要破解,破解方法在另外一篇文章中详述)。

我是个菜鸟,刚接触这个QUARTUS仿真,以前的版本都是直接利用自带的仿真软件,建立一个波形文件vector wavefile(后来发现这个文件可以在QUARTUS里面直接转化成TESTBENCH文件),现在10.0以后不支持直接这么仿真了,而是建议用外部的仿真器仿真(不知道我理解的对不对)。

害的我费了老大的劲,关键是我是初级的水平,能不能整点容易的。

废话少说,主要是发泄一下我的积怨。

(本文参考“Quartus II 调用ModelSim 仿真”一文)1.建立工程文件,这个我就不多说了。

网上有很多,不过在这里,我想提示一下就是工程文件名称要跟顶层实体名称一致(如果只有一个文件的话,那么工程名要跟MODUEL(Verilog HDL),ENTITY(VHDL)后面的名称一致,还有一个就是这里要跟文件名一致,这个文件是顶层文件),这个名称一致的问题至关重要,在后面还有很多地方要一致,就是大家记住一句话,所有的MODUEL和ENTITY的名称要和文件名一致,我就是后面TESTBENCH 中的MODUEL名称和文件名称不一致导致我出错好久。

2.建立Verilog文件(此处为顶层文件),文件名要和项目名一致,且和MODUEL名一致。

文件如下:在保存之前:保存之后,是自动添加到项目中的,只要文件名一致:3.设置仿真器:Assignments---settings---这里tool name:Format for output netlist:用哪个选哪个,后面的不用改(这个是综合的时候用的,用于生成网表文件),还有个东西就是TESTBENCH 在后面讲。

这里设置完了之后编译源文件就能在那个目录下面生成simulation\modelsim文件夹。

Quartus II调用ModelSim仿真方法

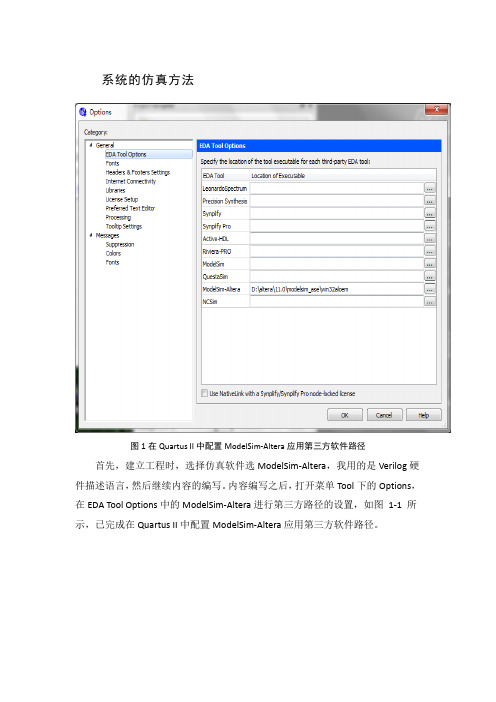

系统的仿真方法图1在Quartus II中配置ModelSim-Altera应用第三方软件路径首先,建立工程时,选择仿真软件选ModelSim-Altera,我用的是Verilog硬件描述语言,然后继续内容的编写。

内容编写之后,打开菜单Tool下的Options,在EDA Tool Options中的ModelSim-Altera进行第三方路径的设置,如图1-1 所示,已完成在Quartus II中配置ModelSim-Altera应用第三方软件路径。

如图2 NativeLink settings然后,选择Assignments下的EDA Tool Settings下的Simulation中的NativeLink settings,选择Compile test bench,设置其中的Test Benches,New,然后编辑里头内容,然后具体内容如图 2 所示,然后,Test bench name填入的是设计的顶层文件、Top level module in test bench和Design instance name in test bench是填入仿真的文件的名字,Test bench files填入仿真的文件路径。

最后生成测试文件,选择在Quartus II开发界面菜单栏下Processing下的Start 下面的Start Test Bench Template Writer,提示生成成功。

生成测试仿真文件的大框,里头一些内容还需自己添加。

以下告诉你如何添加内容,在仿真目录下找到为“.vt”的文件,然后打开这个文件,根据需要给以激励和时钟进行编辑。

具体的Test Bench的编写正在附录四中,写完Test Bench之后就可以进行在菜单栏Tools 下的Run EDA Simulation下的EDA RTL Simulation仿真。

QuartusII 调用ModelSim仿真

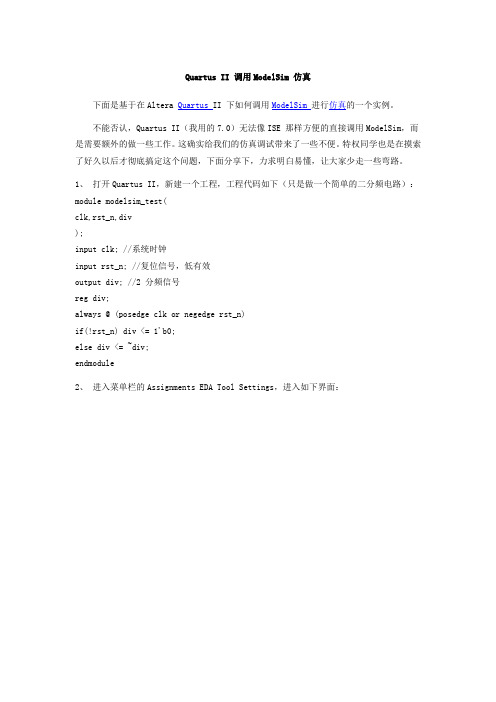

Quartus II 调用ModelSim 仿真下面是基于在Altera Quartus II 下如何调用ModelSim 进行仿真的一个实例。

不能否认,Quartus II(我用的7.0)无法像ISE 那样方便的直接调用ModelSim,而是需要额外的做一些工作。

这确实给我们的仿真调试带来了一些不便。

特权同学也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让大家少走一些弯路。

1、打开Quartus II,新建一个工程,工程代码如下(只是做一个简单的二分频电路):module modelsim_test(clk,rst_n,div);input clk; //系统时钟input rst_n; //复位信号,低有效output div; //2 分频信号reg div;always @ (posedge clk or negedge rst_n)if(!rst_n) div <= 1'b0;else div <= ~div;endmodule2、进入菜单栏的Assignments EDA Tool Settings,进入如下界面:双击“EDA tools”下的“Simulation”选项,弹出如下界面:点击Tool name 最右侧的下拉条,选择“ModelSim”,在弹出的界面做如下设置:3、以上设置完成,重新编译工程。

打开工程目录,看到多了一个“simulation”文件夹,再打开该文件夹下的“modelsim”文件夹。

看到有三个文件,其中.vo 文件就是我们的代码布局布线信息。

仿真还需要几个文件,我们把它们都拷贝到该目录下。

4、打开“C:altera70quartusedasim_lib”(具体quartus 软件安装文件的根目录视您的实际情况而定,大体路径都一样),因为我们用的是MAX II器件,所以把“maxii_atoms.v”拷贝到3 中提到的目录下,这个文件是仿真元件库。

Quartus II 与ModelSim联合仿真

Quartus II 与ModelSim联合仿真1.仿真工具ModelSim使用在option的EDA Tool中定位ModelSim的路径。

2.在ModelSim仿真中出现Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand,the result will be 'X'(es).这个解决方法是给程序里的信号赋初值。

3.Quartus II 5.1和ModelSim的联合仿真方法一:①设定仿真EDA工具为ModelSim②在Quartus II 5.1中,用自带工具建立仿真文件*.vmf,File->Export…,将导出文件保存在simulation/modelsim文件夹下。

③在Settings窗口中,点击Gate Level Simulation Settings …,如图1所示。

图1 Gate Level Simulation Settings …选择Test bench mode,Test bench file为刚刚导出的*.vht文件,Test bench name为*.vht 中的* _vhd_vec_tst,Design instance name in test bench为导出文件*.vht中的i1。

④上述步骤设置完成后,单击ok,回到Settings对话界面,单击ok完成设定。

设置TestBench完成之后,在Quartus II中执行菜单命令:Tools->EDA Simulation Tool->Run EDA Gate Level Simulation,即可启动ModelSim开始仿真。

但要使用testbench作仿真,单独Qaurtus II并无法做到,就得使用ModelSim了,这又牵涉到『前仿真』与『后仿真』。

QuartusII和Modelsim的联合仿真(详细)

QuartusII和Modelsim的联合仿真(详细)这篇⽂章不需要在modelsim中建库、映射、建⼯程等⼀些繁琐的步骤,直接使⽤modelsim中的默认work库。

使⽤quartus+modelsim联合仿真。

⾸先推荐⼀篇⽂章⾸先,根据上⼀篇⽂章,建⽴⼀个testbench模板;第⼀次⽤modelsim+quartus的时候需要在quartus中设置modelsim的路径,quartus->tools->general->EDA tool options ,在右边选择modelsim的安装路径,如下图:然后在Quartus->setting->simulation中设置仿真⼯具(选择modelsim),输出netlist语⾔(选择 VHDL or Verilog),然后在下⾯添加testbench;如下图:到edit test settings这个步骤的时候需要说明⼀下,其中test bench name可以⾃⼰定,下⾯两个的内容根据test bench⽂件中的内容⽽定。

⽐如说我⽤verilog写的test bench如下:那么我下⾯两个的名字就为分别为 Counter_tb和counter 如下图:如果是⽤VHDL写的test bench,如下图那么我们下⾯两个的内容就是ADC_vhd_tst和i1,如同下图这样设置了之后,就可以从quartus中直接进⾏RTL仿真和门极(时序)仿真了,(上图打勾就代表使⽤时序仿真);具体为什么要这么设置请看如果不这么设置的话,可以进⾏RTL仿真,但是不能进⾏门级(时序)仿真,门级(时序)仿真的时候会报 Failed to find INSTANCE 错误。

做到上⼀部可以编写程序,然后编译,接着运⾏RTL simulation,这个时候modelsim会⾃⼰启动,然后⾃⼰编译,接着在work library中会有两个单元,其中⼀个是testbench⽣成的,我们仿真的话是⽤这个。

Quartus系列:QuartusII原理图调用ModelSim进行仿真

Quartus系列:QuartusII原理图调⽤ModelSim进⾏仿真1.新建⼀个⼯程,创建⼀个原理图⽂件,并在其中进⾏原理图电路绘制,本例以⼀个2输⼊与门为例,如下图所⽰:绘制好电路图后,保存绘制好的电路⾄新建的⼯程,如下图所⽰:因为原理图⽂件ModelSim等第三⽅仿真器并不识别,所以需要将其输出为Veilog或者VHDL⽂件,操作如下:点击当前选项后弹出如下对话框,选择要⽣成的对应的硬件描述语⾔⽂件,点击OK按钮完成对应⽂件的⽣成(⽣成⽂件的路径为当前项⽬⽂件夹下),本⽂中以Verilog为例:确认⽂件⽣成后,在⼯程中单击原理图⽂件,将其从当前⼯程中移除后,右击"Files"如下图所⽰:点击选项后,在弹出的对话框中增加⽣成的源⽂件,如下图所⽰:通过上述步骤,即可将源⽂件加⼊到⼯程中.2 选择"Processing"中的"Start Compilation"完成对项⽬的编译。

3 参考“Quartus II 调⽤ModelSim仿真调试”中的步骤,即可完成对应的ModelSim调⽤仿真。

4 如果想使⽤Quartus中的波形⽂件作为调⽤ModelSim的仿真激励,那么只需要注意以下事项:使⽤波形⽂件完成仿真后,⽣成的波形⽂件本⾝是不能为第三⽅仿真⼯具识别,同样需要将其输出为Verilog或者VHDL等格式,如下图所⽰:单击“Export...”在弹出的对话框中保存⽣成的testbench,此时的testbench中即包含了波形仿真时的激励,但是这个testbench的⽂件后缀为“*.vt”。

选择菜单栏下的Assignments->Settings,在弹出的界⾯中选择EDA Tool Settings->Simulation,设置如下图所⽰:其中“3”指定到⽣成的testbench即可。

最后,如果确实不想将原理图转换为Verilog或者VHDL进⾏仿真,即不想将原理图⽂件从项⽬中移除,那么可以只⽣成功能仿真⽹表进⾏仿真,在指定好testbench后,选择"Tools"->"EDASimulation Tool"->"Run EDA Gate Level Simulation"进⾏仿真。

Quartus II接合ModelSim做仿真

1.启动 QuartusII6.0,在 D:\exam 下新建工程 count。

2.执行 Project 菜单下的 Add/Remove Files in Project... 命令,将 D:\exam 下的 count.v 文件加到工程中来。

3.执行 Assignments 菜单下的 Device... 命令,启动器件设置对话框。

如果所用的实验板为 MC570 则选中 EPM570T100C5 器件,如果是 MC240 实验板,则选中 EPM240T100C5 器件。

4.点击对话框上的“Device & Pin Options...”按钮,在随后弹出的对话框上,进入 Unused Pins 页,将 Reserve all unused pins 设为 As input tri-stated,点击“确定”按钮。

5.在左侧的 Category 窗口里,展开 EDA Tool Setings 组,选中 Simulation 项,对话框的左侧将弹出有关于 Simulation 的设置项。

在 Tool name 一栏,选择 ModelSim;Format for output netlist 一栏,选择 Verilog;Time scale 一栏,选择 1ns。

点击“OK”按钮。

6.在 Assignments 菜单下,点击 Pins 命令。

在 Pin Planner 中,按下图所示,分配管脚。

7.在 Project Navigator 窗口中,将页面切换到文件管理页(中间的),选中 Device Design Files 组中的 count.v 文件,点击右键,在弹出菜单中点击 Set as Top-level Entity 命令,将该文件设为顶层设计文件。

在 Processing 菜单下,点击 Start Compilation 命令,待编译完成后,退出 QuartusII6.0。

将 D:\exam\simulation\modelsim 下的 count_v.sdo 文件复制到 D:\exam 下。

QuartusII与modelsim联调仿真

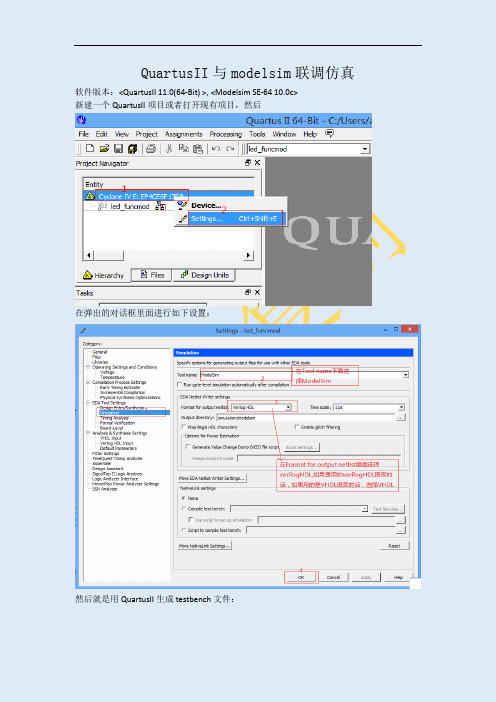

QuartusII与modelsim联调仿真软件版本:<QuartusII 11.0(64-Bit) >,<Modelsim SE-64 10.0c>

新建一个QuartusII项目或者打开现有项目,然后

在弹出的对话框里面进行如下设置:

然后就是用QuartusII生成testbench文件:

如果生成testbench成功的话,会在这个工程文件夹下面产生simulation/modelsim文件夹,里面有用于仿真的testbench文件,***.vt,可以对它进行修改,用于必要的参数初始化等,例如时钟的初始化,复位信号的初始化等等。

然后再次单击Settings,弹出对话框,进行如下设置:

在单击TestBenches后弹出对话框,如下所示:

然后单击new,弹出对话框如下所示:

单击确定后,有如下图示:

特别说明:如果testbench要修改就在联合调用之前进行修改,一般,简单的修改就是添加时钟和复位信号,参考下图:

修改好了则执行如下图所示的内容:

此时,QuartusII会调用Modelsim进行仿真,如果之前的时钟和复位是设置了的,即初始化是成功的,则仿真会在Modelsim启动过后立即执行。

执行结果如下图所示:

至此,即完成了QuartusII与Modelsim的联调仿真。

如何从Quartus II中调用Modelsim进行仿真

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\models im文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

如何从Quartus II中调用Modelsim进行仿真

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\models im文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

QuartusII调用modelsim无缝仿真

QuartusII调⽤modelsim⽆缝仿真本篇⽂章为转载,写的不错,最近在学modelsim仿真,⽹上的教程很乱,把⾃⼰认为不错的整理贴出来,后⾯有机会会写个详细点的。

Quartus 中调⽤modelsim的流程1. 设定仿真⼯具assignmentèsettingèEDA tool settingèsimulation选择你需要的⼯具。

2. ⾃动产⽣测试激励⽂件模板:processingèstartèStart test bench template writer我们点击之后系统会⾃动在⽬录:当前⽂件夹è simulation è modelsim (这个⽂件夹名字跟你选的仿真⼯具有关) 中产⽣⼀个测试激励⽂件xxx.vt(Verilog test bench) 或者 xxx.vht(VHDL test bench), ⽂件名跟你⼯程中的Top module 的名字⼀样,后缀为.vt或者.vht。

3. 编辑⾛动⽣成的test bench⽂件我们加⼊⾃⼰需要的激励以及初始化语句,这⾥我们还要修改test bench的模块名字为tb(我们会看到这个名字和后⾯的设定有联系)。

4. 连接test bench,我们需要从Quartus中⾃动调⽤仿真⼯具,所以需要设定Native Link选项。

a) 还是在simulation的设置页⾯⾥,设定 Native Link对话框中的设定。

我们这⾥因为需要⼯具⾃动调⽤激励所以选中b) 点击右边的Test Benches, 我们需要在这⾥设定⼀个相关联的test bench.这⾥会弹出⼀个让你指定test bench的对话框,因为我们之前没有指定任何的test bench,所以这⾥是空⽩的。

c) 指定test bench因为我们是第⼀次产⽣test bench,点击new.点击New之后会产⽣⼀个New Test bench setting的对话框,在这⾥你将test bench和你的相应的test bench file进⾏绑定。

在Quartus中调用Modelsim进行仿真

在QuartusⅡ中调用ModelSim进行仿真Quartus Ⅱ版本:Quartus Ⅱ10.0 (32-bit);安装路径为D:\Myfiles\QUARTUS_10.0 ModelSim版本:ModelSim SE 6.5;安装路径为D:\Myfiles\ModelsimSE一、Quartus设置(1)在QuartusⅡ中指明仿真工具及其路径(2)在QuartusⅡ中编译所需的元器件库二、建立工程及仿真(1)在QuartusⅡ中建立工程counter,并指明仿真工具(2)顶层文件代码(3)激励文件代码(4)在Quartus中添加testbench文件(5)在Quartus中全编译工程(6)前仿真(7)后仿真一、QuartusⅡ的相关设置(1)在QuartusⅡ中指明仿真工具及其路径在QuartusⅡ中执行Tools\Options,打开EDA Tool Options选项卡。

我们使用ModelSim 进行仿真,所以在ModelSim对应的Location of Executable中选择ModelSim的安装路径D:\Myfiles\ModelsimSE\win32,如图1所示:图1(2)在QuartusⅡ中编译所需的元器件库1)在ModelSim安装路径D:\Myfiles\ModelsimSE中新建文件夹modelsimSE_lib,用于存放编译的文件2)在QuartusⅡ10.0中执行Tools\Launch EAD Simiulation Library Compiler,在打开的界面中Executable location一项选择ModelSim的安装路径D:\Myfiles\ModelsimSE\Win32在Avaliable families中根据自己需要选择可能用的到器件系列,如cyclone、stratix等;在这里可以多选择一些,以备能用到,并且一次编译后,以后就不用再编译了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Quartus II 调用ModelSim 仿真

技术分类:EDA工具与服务可编程器件 | 2009-03-30

下面是基于在Altera Quartus II 下如何调用ModelSim 进行仿真的一个实例。

不能否认,Quartus II(我用的7.0)无法像ISE 那样方便的直接调用ModelSim,而是需要额外的做一些工作。

这确实给我们的仿真调试带来了一些不便。

特权同学也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让大家少走一些弯路。

1、打开Quartus II,新建一个工程,工程代码如下(只是做一个简单的二分频电路):

module modelsim_test(

clk,rst_n,div

);

input clk; //系统时钟

input rst_n; //复位信号,低有效

output div; //2 分频信号

reg div;

always @ (posedge clk or negedge rst_n)

if(!rst_n) div <= 1'b0;

else div <= ~div;

endmodule

2、进入菜单栏的Assignments EDA Tool Settings,进入如下界面:

双击“EDA tools”下的“Simulation”选项,弹出如下界面:

点击Tool name 最右侧的下拉条,选择“ModelSim”,在弹出的界面做如下设置:

3、以上设置完成,重新编译工程。

打开工程目录,看到多了一个“simulation”文件夹,再打开该文件夹下的“modelsim”文件夹。

看到有三个文件,其中.vo 文件就是我们的代码布局布线信息。

仿真还需要几个文件,我们把它们都拷贝到该目录下。

4、打开“C:altera70quartusedasim_lib”(具体quartus 软件安装文件的根目录视您的实际情况而定,大体路径都一样),因为我们用的是MAX II器件,所以把“maxii_atoms.v”拷贝到3 中提到的目录下,这个文件是仿真元件库。

5、编写一个工程RTL 源码的Testbench 文件,用于作为仿真激励(具体如何编写清参考相关数据文档资料)。

这个实例的testbench 如下:

module vtf_test;

// Inputs

reg clk;

reg rst_n;

// Output

wire div;

modelsim_test u1(

.clk(clk),

.rst_n(rst_n),

.div(div)

);

initial begin

clk = 0;

forever

#10 clk = ~clk; //产生50MHz 的时钟

end

initial begin

rst_n = 0;

#1000 rst_n = 1; //上电后1us 复位信号

#1000;

$stop;

end

endmodule

将该文件命名为tb_test.v,保存到3 提到的文件夹下。

6、在wokspace 的library 面板的空白处单击右键,选择“new”→“library”

在新弹出界面中做如下设置,然后点击“OK”。

7、启动ModelSim 软件,点击菜单栏的Compile compile 命令,弹出如下界面:

Library 选择刚才新建的“work_test”,查找范围定位到我们3 提到的文件夹下。

全选在该目录下可以看到的文件,点击Compile(注意该文件夹必须在全英文/数字路径下,否则会出错无法编译)。

8、我们回到wokspace 的library 面板,work_test 多处了下拉框,点击后如下:

我们右键单击vtf_test 文件,在弹出的菜单中选择Simulation

9、执行上面的操作后,软件自动弹出wokspace 的sim 面板如下:

在vtf_test 栏单击右键,在弹出菜单中选择Add Add to Wave。

然后软件将弹出波形窗口。

10、波形窗口如下:

这时我们点击全速编译(一次不行,多点一次,工具栏倒数第三个按钮),然后点击观看全部波形(放大缩小按钮后面一个蓝色按钮)。

11、仿真结果如下:

可以看到div 信号确实是clk 的二分频。

呵呵,基本的操作就到此结束了。