MCZ33993EW中文资料

MC33035DWG资料

MC33035, NCV33035 Brushless DCMotor ControllerThe MC33035 is a high performance second generation monolithic brushless DC motor controller containing all of the active functions required to implement a full featured open loop, three or four phase motor control system. This device consists of a rotor position decoder for proper commutation sequencing, temperature compensated reference capable of supplying sensor power, frequency programmable sawtooth oscillator, three open collector top drivers, and three high current totem pole bottom drivers ideally suited for driving power MOSFETs.Also included are protective features consisting of undervoltage lockout, cycle−by−cycle current limiting with a selectable time delayed latched shutdown mode, internal thermal shutdown, and a unique fault output that can be interfaced into microprocessor controlled systems.Typical motor control functions include open loop speed, forward or reverse direction, run enable, and dynamic braking. The MC33035 is designed to operate with electrical sensor phasings of 60°/300° or 120°/240°, and can also efficiently control brush DC motors. Features•10 to 30 V Operation•Undervoltage Lockout•6.25 V Reference Capable of Supplying Sensor Power •Fully Accessible Error Amplifier for Closed Loop Servo Applications•High Current Drivers Can Control External 3−Phase MOSFET Bridge•Cycle−By−Cycle Current Limiting•Pinned−Out Current Sense Reference•Internal Thermal Shutdown•Selectable 60°/300° or 120°/240° Sensor Phasings•Can Efficiently Control Brush DC Motors with External MOSFET H−Bridge•NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes•Pb−Free Packages are Available241P SUFFIXPLASTIC PACKAGECASE 724DW SUFFIXPLASTIC PACKAGECASE 751E(SO−24L)See detailed ordering and shipping information in the package dimensions section on page 27 of this data sheet.ORDERING INFORMATIONSee general marking information in the device marking section on page 27 of this data sheet.DEVICE MARKING INFORMATIONRepresentative Schematic DiagramThis device contains 285 active transistors.MAXIMUM RATINGSRating Symbol Value Unit Power Supply Voltage V CC40V Digital Inputs (Pins 3, 4, 5, 6, 22, 23)−V ref V Oscillator Input Current (Source or Sink)I OSC30mA Error Amp Input Voltage Range (Pins 11, 12, Note 1)V IR−0.3 to V ref V Error Amp Output Current (Source or Sink, Note 2)I Out10mA Current Sense Input Voltage Range (Pins 9, 15)V Sense−0.3 to 5.0V Fault Output Voltage V CE(Fault)20V Fault Output Sink Current I Sink(Fault)20mA Top Drive Voltage (Pins 1, 2, 24)V CE(top)40V Top Drive Sink Current (Pins 1, 2, 24)I Sink(top)50mA Bottom Drive Supply Voltage (Pin 18)V C30V Bottom Drive Output Current (Source or Sink, Pins 19, 20, 21)I DRV100mA Power Dissipation and Thermal CharacteristicsP Suffix, Dual In Line, Case 724Maximum Power Dissipation @ T A = 85°C Thermal Resistance, Junction−to−AirDW Suffix, Surface Mount, Case 751E Maximum Power Dissipation @ T A = 85°C Thermal Resistance, Junction−to−AirP DRθJAP DRθJA86775650100mW°C/WmW°C/WOperating Junction Temperature T J150°COperating Ambient Temperature Range (Note 3)MC33035NCV33035T A−40 to +85−40 to +125°CStorage Temperature Range T stg−65 to +150°C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.ELECTRICAL CHARACTERISTICS(V CC = V C = 20 V, R T = 4.7 k, C T = 10 nF, T A = 25°C, unless otherwise noted.)Characteristic Symbol Min Typ Max Unit REFERENCE SECTIONReference Output Voltage (I ref = 1.0 mA) T A = 25°C(Note 4)V ref5.95.826.24−6.56.57VLine Regulation (V CC = 10 to 30 V, I ref = 1.0 mA)Reg line− 1.530mV Load Regulation (I ref = 1.0 to 20 mA)Reg load−1630mV Output Short Circuit Current (Note 5)I SC4075−mA Reference Under Voltage Lockout Threshold V th 4.0 4.5 5.0V ERROR AMPLIFIERInput Offset Voltage (Note 4)V IO−0.410mV Input Offset Current (Note 4)I IO−8.0500nA Input Bias Current (Note 4)I IB−−46−1000nA Input Common Mode Voltage Range V ICR(0 V to V ref)V Open Loop Voltage Gain (V O = 3.0 V, R L = 15 k)A VOL7080−dB Input Common Mode Rejection Ratio CMRR5586−dB Power Supply Rejection Ratio (V CC = V C = 10 to 30 V)PSRR65105−dB1.The input common mode voltage or input signal voltage should not be allowed to go negative by more than 0.3 V.2.The compliance voltage must not exceed the range of −0.3 to V ref.3.NCV33035: T low = −40°C, T high = 125°C. Guaranteed by design. NCV prefix is for automotive and other applications requiring site and changecontrol.4.MC33035: T A = −40°C to +85°C; NCV33035: T A = −40°C to +125°C.5.Maximum package power dissipation limits must be observed.ELECTRICAL CHARACTERISTICS (continued) (V CC = V C = 20 V, R T = 4.7 k, C T = 10 nF, T A = 25°C, unless otherwise noted.) Characteristic Symbol Min Typ Max Unit ERROR AMPLIFIEROutput Voltage SwingHigh State (R L = 15 k to Gnd) Low State (R L = 15 k to V ref)V OHV OL4.6−5.30.5−1.0VOSCILLATOR SECTIONOscillator Frequency f OSC222528kHz Frequency Change with Voltage (V CC = 10 to 30 V)Δf OSC/ΔV−0.01 5.0% Sawtooth Peak Voltage V OSC(P)− 4.1 4.5V Sawtooth Valley Voltage V OSC(V) 1.2 1.5−V LOGIC INPUTSInput Threshold Voltage (Pins 3, 4, 5, 6, 7, 22, 23)High State Low State V IHV IL3.0−2.21.7−0.8VSensor Inputs (Pins 4, 5, 6)High State Input Current (V IH = 5.0 V) Low State Input Current (V IL = 0 V)I IHI IL−150−600−70−337−20−150μAForward/Reverse, 60°/120° Select (Pins 3, 22, 23)High State Input Current (V IH = 5.0 V) Low State Input Current (V IL = 0 V)I IHI IL−75−300−36−175−10−75μAOutput EnableHigh State Input Current (V IH = 5.0 V) Low State Input Current (V IL = 0 V)I IHI IL−60−60−29−29−10−10μACURRENT−LIMIT COMPARATORThreshold Voltage V th85101115mV Input Common Mode Voltage Range V ICR− 3.0−V Input Bias Current I IB−−0.9−5.0μA OUTPUTS AND POWER SECTIONSTop Drive Output Sink Saturation (I sink = 25 mA)V CE(sat)−0.5 1.5V Top Drive Output Off−State Leakage (V CE = 30 V)I DRV(leak)−0.06100μA Top Drive Output Switching Time (C L = 47 pF, R L = 1.0 k)ns Rise Time t r−107300Fall Time t f−26300Bottom Drive Output VoltageHigh State (V CC = 20 V, V C = 30 V, I source = 50 mA) Low State (V CC = 20 V, V C = 30 V, I sink = 50 mA)V OHV OL(V CC−2.0)−(V CC−1.1)1.5−2.0VBottom Drive Output Switching Time (C L = 1000 pF)ns Rise Time t r−38200Fall Time t f−30200Fault Output Sink Saturation (I sink = 16 mA)V CE(sat)−225500mV Fault Output Off−State Leakage (V CE = 20 V)I FLT(leak)− 1.0100μA Under Voltage Lockout V Drive Output Enabled (V CC or V C Increasing)V th(on)8.28.910Hysteresis V H0.10.20.3Power Supply CurrentPin 17 (V CC = V C = 20 V)Pin 17 (V CC = 20 V, V C = 30 V) Pin 18 (V CC = V C = 20 V)Pin 18 (V CC = 20 V, V C = 30 V)I CCI C−−−−12143.55.016206.010mAV s a t , O U T P U T S A T U R A T I O N V O L T A G E (V )5.0 μs/DIVA V = +1.0No Load T A = 25°C, O U T P U T V O L T A G E (V )O 4.53.01.51.0 μs/DIV A V = +1.0No Load T A = 25°C3.053.02.95I O , OUTPUT LOAD CURRENT (mA)f, FREQUENCY (Hz)562202001801601401201008060−−16−08.0162432404840240A V O L , O P E N L O O P V O L T A G E G A I N (d B )E X C E S S P H A S E (D E G R E E S ),φT A , AMBIENT TEMPERATURE (°C)−55−4.0−2.02.01254.01007550250−25f O S C O S C I L L A T O R F R E Q U E N C Y C H A N G E (%),Δ1001.0R T , TIMING RESISTOR (k Ω)100010010010f O S C O S C I L L A T O R F R E Q U E N C Y (k H z ),Figure 1. Oscillator Frequency versusTiming Resistor Figure 2. Oscillator Frequency Changeversus TemperatureFigure 3. Error Amp Open Loop Gain andPhase versus Frequency Figure 4. Error Amp Output SaturationVoltage versus Load CurrentFigure 5. Error Amp Small−SignalTransient Response Figure 6. Error Amp Large−SignalTransient Response1.02.00− 0.8−1.61.60.8 5.04.03.00V , O U T P U T V O L T A G E (V )O VI Sink , SINK CURRENT (mA)0−40−20−4020, N O R M A L I Z E D R E F E R E N C E V O L T A G E C H A N G E (m V )ΔV r e f 0−−−−− 12− 16V r e f , R E F E R E N C E O U T P U T V O L T A G E C H A N G E (m V )ΔFigure 11. Bottom Drive Response Time versusCurrent Sense Input Voltage Figure 12. Fault Output Saturationversus Sink Current0CURRENT SENSE INPUT VOLTAGE (NORMALIZED TO V th )50100150200250t H L , B O T T O M D R I V E R E S P O N S E T I M E (n s )1.0O U T P U T V O L T A G E (%)−40I O , OUTPUT LOAD CURRENT (mA)02.0806020, O U T P U T S A T U R A T I O N V O L T A G E (V )s a t V 50 ns/DIV V CC = 20 V V C = 20 V C L = 1.0 nF T A = 25°C100 ns/DIVV CC = 20 V V C = 20 V R L = 1.0 k C L = 15 pF T A = 25°CFigure 13. Top Drive Output SaturationVoltage versus Sink CurrentFigure 14. Top Drive Output WaveformFigure 15. Bottom Drive Output Waveform Figure 16. Bottom Drive Output WaveformI Sink , SINK CURRENT (mA)0.40.81.2V s a t , O U T P U T S A T U R A T I O N V O L T A G E (V )Figure 17. Bottom Drive Output SaturationVoltage versus Load Current 50 ns/DIVV CC = 20 V V C = 20 V C L = 15 pF T A= 25°CFigure 18. Power and Bottom Drive SupplyCurrent versus Supply Voltage, P O W E R S U P P L Y C U R R E N T (m A )C C , I C I V CC , SUPPLY VOLTAGE (V)1000100100O U T P U T V O L T A G E (%)O U T P U T V O L T A G E (%)PIN FUNCTION DESCRIPTIONPin Symbol Description1, 2, 24B T, A T, C T These three open collector Top Drive outputs are designed to drive the externalupper power switch transistors.3Fwd/Rev The Forward/Reverse Input is used to change the direction of motor rotation. 4, 5, 6S A, S B, S C These three Sensor Inputs control the commutation sequence.7Output Enable A logic high at this input causes the motor to run, while a low causes it to coast.8Reference Output This output provides charging current for the oscillator timing capacitor C T and areference for the error amplifier. It may also serve to furnish sensor power.9Current Sense Noninverting Input A 100 mV signal, with respect to Pin 15, at this input terminates output switchconduction during a given oscillator cycle. This pin normally connects to the topside of the current sense resistor.10Oscillator The Oscillator frequency is programmed by the values selected for the timingcomponents, R T and C T.11Error Amp Noninverting Input This input is normally connected to the speed set potentiometer.12Error Amp Inverting Input This input is normally connected to the Error Amp Output in open loopapplications.13Error Amp Out/PWM Input This pin is available for compensation in closed loop applications.14Fault Output This open collector output is active low during one or more of the followingconditions: Invalid Sensor Input code, Enable Input at logic 0, Current SenseInput greater than 100 mV (Pin 9 with respect to Pin 15), Undervoltage Lockoutactivation, and Thermal Shutdown.15Current Sense Inverting Input Reference pin for internal 100 mV threshold. This pin is normally connected tothe bottom side of the current sense resistor.16Gnd This pin supplies a ground for the control circuit and should be referenced backto the power source ground.17V CC This pin is the positive supply of the control IC. The controller is functional over aminimum V CC range of 10 to 30 V.18V C The high state (V OH) of the Bottom Drive Outputs is set by the voltage applied tothis pin. The controller is operational over a minimum V C range of 10 to 30 V. 19, 20, 21C B, B B, A B These three totem pole Bottom Drive Outputs are designed for direct drive of theexternal bottom power switch transistors.2260°/120° Select The electrical state of this pin configures the control circuit operation for either60° (high state) or 120°(low state) sensor electrical phasing inputs.23Brake A logic low state at this input allows the motor to run, while a high state does notallow motor operation and if operating causes rapid deceleration.INTRODUCTIONThe MC33035 is one of a series of high performance monolithic DC brushless motor controllers produced by Motorola. It contains all of the functions required to implement a full−featured, open loop, three or four phase motor control system. In addition, the controller can be made to operate DC brush motors. Constructed with Bipolar Analog technology, it offers a high degree of performance and ruggedness in hostile industrial environments. The MC33035 contains a rotor position decoder for proper commutation sequencing, a temperature compensated reference capable of supplying a sensor power, a frequency programmable sawtooth oscillator, a fully accessible error amplifier, a pulse width modulator comparator, three open collector top drive outputs, and three high current totem pole bottom driver outputs ideally suited for driving power MOSFETs. Included in the MC33035 are protective features consisting of undervoltage lockout, cycle−by−cycle current limiting with a selectable time delayed latched shutdown mode, internal thermal shutdown, and a unique fault output that can easily be interfaced to a microprocessor controller. Typical motor control functions include open loop speed control, forward or reverse rotation, run enable, and dynamic braking. In addition, the MC33035 has a 60°/120°select pin which configures the rotor position decoder for either 60° or 120° sensor electrical phasing inputs. FUNCTIONAL DESCRIPTIONA representative internal block diagram is shown in Figure 19 with various applications shown in Figures 36, 38, 39, 43, 45, and 46. A discussion of the features and function of each of the internal blocks given below is referenced to Figures 19 and 36.Rotor Position DecoderAn internal rotor position decoder monitors the three sensor inputs (Pins 4, 5, 6) to provide the proper sequencing of the top and bottom drive outputs. The sensor inputs are designed to interface directly with open collector type Hall Effect switches or opto slotted couplers. Internal pull−up resistors are included to minimize the required number of external components. The inputs are TTL compatible, with their thresholds typically at 2.2 V. The MC33035 series is designed to control three phase motors and operate with four of the most common conventions of sensor phasing. A 60°/120°Select (Pin 22) is conveniently provided and affords the MC33035 to configure itself to control motors having either 60°, 120°, 240° or 300° electrical sensor phasing. With three sensor inputs there are eight possible input code combinations, six of which are valid rotor positions. The remaining two codes are invalid and are usually caused by an open or shorted sensor line. With six valid input codes, the decoder can resolve the motor rotor position to within a window of 60 electrical degrees.The Forward/Reverse input (Pin 3) is used to change the direction of motor rotation by reversing the voltage across the stator winding. When the input changes state, from high to low with a given sensor input code (for example 100), the enabled top and bottom drive outputs with the same alpha designation are exchanged (A T to A B, B T to B B, C T to C B). In effect, the commutation sequence is reversed and the motor changes directional rotation.Motor on/off control is accomplished by the Output Enable (Pin 7). When left disconnected, an internal 25 μA current source enables sequencing of the top and bottom drive outputs. When grounded, the top drive outputs turn off and the bottom drives are forced low, causing the motor to coast and the Fault output to activate.Dynamic motor braking allows an additional margin of safety to be designed into the final product. Braking is accomplished by placing the Brake Input (Pin 23) in a high state. This causes the top drive outputs to turn off and the bottom drives to turn on, shorting the motor−generated back EMF. The brake input has unconditional priority over all other inputs. The internal 40 kΩ pull−up resistor simplifies interfacing with the system safety−switch by insuring brake activation if opened or disconnected. The commutation logic truth table is shown in Figure 20. A four input NOR gate is used to monitor the brake input and the inputs to the three top drive output transistors. Its purpose is to disable braking until the top drive outputs attain a high state. This helps to prevent simultaneous conduction of the the top and bottom power switches. In half wave motor drive applications, the top drive outputs are not required and are normally left disconnected. Under these conditions braking will still be accomplished since the NOR gate senses the base voltage to the top drive output transistors.Error AmplifierA high performance, fully compensated error amplifier with access to both inputs and output (Pins 11, 12, 13) is provided to facilitate the implementation of closed loop motor speed control. The amplifier features a typical DC voltage gain of 80 dB, 0.6 MHz gain bandwidth, and a wide input common mode voltage range that extends from ground to V ref. In most open loop speed control applications, the amplifier is configured as a unity gain voltage follower with the noninverting input connected to the speed set voltage source. Additional configurations are shown in Figures 31 through 35.OscillatorThe frequency of the internal ramp oscillator is programmed by the values selected for timing components R T and C T. Capacitor C T is charged from the Reference Output (Pin 8) through resistor R T and discharged by an internal discharge transistor. The ramp peak and valley voltages are typically 4.1 V and 1.5 V respectively. To provide a good compromise between audible noise and output switching efficiency, an oscillator frequency in the range of 20 to 30 kHz is recommended. Refer to Figure 1 for component selection.Figure 19. Representative Block DiagramInputs (Note 2)Outputs(Note 3) Sensor Electrical Phasing (Note 4)Top Drives Bottom DrivesS A 60°S B S C S A120°S B S C F/R Enable BrakeCurrentSense A T B T C T A B B B C B Fault1 1 1 0 0 00111111111111111111111111111111111111111111111111111(Note 5)F/R = 11 1 1 0 0 00111111111111111111111111111111111111111111111(Note 5)F/R = 01 0011111XXXXXX111111(Note 6)Brake = 01 0011111XXXX11XX111111111111(Note 7)Brake = 1V V V V V V X11X1111111(Note 8) V V V V V V X01X1111110(Note 9) V V V V V V X00X1110000(Note 10)V V V V V V X1011110000(Note 11) NOTES:1.V = Any one of six valid sensor or drive combinations X = Don’t care.2.The digital inputs (Pins 3, 4, 5, 6, 7, 22, 23) are all TTL compatible. The current sense input (Pin 9) has a 100 mV threshold with respect to Pin 15.A logic 0 for this input is defined as < 85 mV, and a logic 1 is > 115 mV.3.The fault and top drive outputs are open collector design and active in the low (0) state.4.With 60°/120°select (Pin 22) in the high (1) state, configuration is for 60°sensor electrical phasing inputs. With Pin 22 in low (0) state, configurationis for 120° sensor electrical phasing inputs.5.Valid 60° or 120° sensor combinations for corresponding valid top and bottom drive outputs.6.Invalid sensor inputs with brake = 0; All top and bottom drives off, Fault low.7.Invalid sensor inputs with brake = 1; All top drives off, all bottom drives on, Fault low.8.Valid 60° or 120°sensor inputs with brake = 1; All top drives off, all bottom drives on, Fault high.9.Valid sensor inputs with brake = 1 and enable = 0; All top drives off, all bottom drives on, Fault low.10.Valid sensor inputs with brake = 0 and enable = 0; All top and bottom drives off, Fault low.11.All bottom drives off, Fault low.Figure 20. Three Phase, Six Step Commutation Truth Table (Note 1)Pulse Width ModulatorThe use of pulse width modulation provides an energy efficient method of controlling the motor speed by varying the average voltage applied to each stator winding during the commutation sequence. As C T discharges, the oscillator sets both latches, allowing conduction of the top and bottom drive outputs. The PWM comparator resets the upper latch, terminating the bottom drive output conduction when the positive−going ramp of C T becomes greater than the error amplifier output. The pulse width modulator timing diagram is shown in Figure 21. Pulse width modulation for speed control appears only at the bottom drive outputs.Current LimitContinuous operation of a motor that is severely over−loaded results in overheating and eventual failure. This destructive condition can best be prevented with the use of cycle−by−cycle current limiting. That is, each on−cycle is treated as a separate event. Cycle−by−cycle current limiting is accomplished by monitoring the stator current build−up each time an output switch conducts, and upon sensing an over current condition, immediately turning off the switch and holding it off for the remaining duration of oscillator ramp−up period. The stator current is converted to a voltage by inserting a ground−referenced sense resistor R S (Figure 36) in series with the three bottom switch transistors (Q4, Q5, Q6). The voltage developed across the sense resistor is monitored by the Current Sense Input (Pins 9 and 15), and compared to the internal 100 mV reference. The current sense comparator inputs have an input common mode range of approximately 3.0 V. If the 100 mV current sense threshold is exceeded, the comparator resets the lower sense latch and terminates output switch conduction. The value for the current sense resistor is:R S+0.1I stator(max)The Fault output activates during an over current condition. The dual−latch PWM configuration ensures that only one single output conduction pulse occurs during any given oscillator cycle, whether terminated by the output of the error amp or the current limit comparator.Figure 21. Pulse Width Modulator Timing Diagram Current Sense Input Capacitor C T Error Amp Out/PWMInput Latch Set"Inputs Top Drive Outputs Bottom DriveOutputsFault OutputReferenceThe on−chip 6.25 V regulator (Pin 8) provides charging current for the oscillator timing capacitor, a reference for the error amplifier, and can supply 20 mA of current suitable for directly powering sensors in low voltage applications. In higher voltage applications, it may become necessary to transfer the power dissipated by the regulator off the IC. This is easily accomplished with the addition of an external pass transistor as shown in Figure 22. A 6.25 V reference level was chosen to allow implementation of the simpler NPN circuit, where V ref − V BE exceeds the minimum voltage required by Hall Effect sensors over temperature. With proper transistor selection and adequate heatsinking, up to one amp of load current can be obtained.Figure 22. Reference Output BuffersThe NPN circuit is recommended for powering Hall or opto sensors, where the output voltage temperature coefficient is not critical. The PNP circuit is slightly more complex, but is also more accurate over temperature. Neither circuit has current limiting.V V and Sensor Power6.25 VUndervoltage LockoutA triple Undervoltage Lockout has been incorporated to prevent damage to the IC and the external power switch transistors. Under low power supply conditions, it guarantees that the IC and sensors are fully functional, and that there is sufficient bottom drive output voltage. The positive power supplies to the IC (V CC ) and the bottom drives (V C ) are each monitored by separate comparators that have their thresholds at 9.1 V . This level ensures sufficient gate drive necessary to attain low R DS(on) when driving standard power MOSFET devices. When directly powering the Hall sensors from the reference, improper sensor operation can result if the reference output voltage falls below 4.5 V . A third comparator is used to detect this condition. If one or more of the comparators detects an undervoltage condition, the Fault Output is activated, the top drives are turned off and the bottom drive outputs are held in a low state. Each of the comparators contain hysteresis to prevent oscillations when crossing their respective thresholds.Fault OutputThe open collector Fault Output (Pin 14) was designed to provide diagnostic information in the event of a system malfunction. It has a sink current capability of 16 mA and can directly drive a light emitting diode for visual indication.Additionally, it is easily interfaced with TTL/CMOS logic for use in a microprocessor controlled system. The Fault Output is active low when one or more of the following conditions occur:1)Invalid Sensor Input code 2)Output Enable at logic [0]3)Current Sense Input greater than 100 mV4)Undervoltage Lockout, activation of one or more of the comparators5)Thermal Shutdown, maximum junction temperature being exceededThis unique output can also be used to distinguish between motor start−up or sustained operation in an overloaded condition. With the addition of an RC network between the Fault Output and the enable input, it is possible to create a time−delayed latched shutdown for overcurrent. The added circuitry shown in Figure 23 makes easy starting of motor systems which have high inertial loads by providing additional starting torque, while still preserving overcurrent protection. This task is accomplished by setting the current limit to a higher than nominal value for a predetermined time.During an excessively long overcurrent condition, capacitor C DLY will charge, causing the enable input to cross its threshold to a low state. A latch is then formed by the positive feedback loop from the Fault Output to the Output Enable.Once set, by the Current Sense Input, it can only be reset by shorting C DLY or cycling the power supplies.Drive OutputsThe three top drive outputs (Pins 1, 2, 24) are open collector NPN transistors capable of sinking 50 mA with a minimum breakdown of 30 V. Interfacing into higher voltage applications is easily accomplished with the circuits shown in Figures 24 and 25.The three totem pole bottom drive outputs (Pins 19, 20, 21) are particularly suited for direct drive of N−Channel MOSFETs or NPN bipolar transistors (Figures 26, 27, 28 and 29). Each output is capable of sourcing and sinking up to 100 mA. Power for the bottom drives is supplied from V C (Pin 18). This separate supply input allows the designer added flexibility in tailoring the drive voltage, independent of V CC. A zener clamp should be connected to this input when driving power MOSFETs in systems where V CC is greater than 20 V so as to prevent rupture of the MOSFET gates.The control circuitry ground (Pin 16) and current sense inverting input (Pin 15) must return on separate paths to the central input source ground.Thermal ShutdownInternal thermal shutdown circuitry is provided to protect the IC in the event the maximum junction temperature is exceeded. When activated, typically at 170°C, the IC acts as though the Output Enable was grounded.Figure 23. Timed Delayed Latched Over Current ShutdownFigure 24. High Voltage Interface withNPN Power TransistorsTransistor Q1 is a common base stage used to level shift from V CC to the high motor voltage, V M. The collector diode is required if V CC is present while V M is low.[R DLY C DLY Inǒ6.25–(20x10–6R DLY)1.4–(20x10R DLY)Ǔ。

MC33991中文资料

摘要:MC33991是Motorola公司生产的两相步进电机驱动器,可以准确地控制步进电机的运动并及时反馈步时电机的工作状态。

该电路有良好的抗干扰能力,可以灵活地控制驱动步时电机,是汽车电子设备特别是汽车仪表中的理想驱动器。

关键词:步时电动机驱动器SPIMC33991汽车仪表1MC33991的主要特点MC33991是单独封装、通过SPI(同步串行外设接口)进行通信、可同时控制二个步进电机的驱动电路。

该电路由4个可驱动线圈的功率H桥和辅助逻辑控制器组成。

每组H桥的驱动可用来控制步时电机的速度、旋转方向及每相线圈中电流的大小。

MC33991有良好的抗干扰能力,可以十分灵活地驱动步进电机,因此是汽车电子设备特别是汽车仪表的理想驱动器。

只要做一些外围设备的改进,该电路也可以仿照气隙磁通的运行,把普通电机转化为步进电机来控制。

MC33991的特性如下:•最小的上层处理器(不需其他外设即可直接驱动电机);•仿效普通电机的运动进行控制,使电机有完美的动态和静态性能;•有4096个静态指示位置;•最大指针扫过范围为340°;•最大指针速度为400deg/s;•最大指针加速度为4500deg/s2;•应用微步距控制技术(每步细分为12个微步);•指针回零校准;•有16位SPI;•内部时钟校准;•睡眠模式下的耗电量较小。

内韶晶撮GADMC33991的内部结构框图2结构原理与引脚功能2.1内部结构MC33991的内部结构框图如图1所示,它由PI 、逻辑电路、电压/温度检测及功率H 桥等模块组成。

MC33991主控电路先将驱动命令通过SPI 以串行数据的方式输出,再通过逻辑电路将命令转化成驱动信号以驱动功率H 桥,H 桥输出电流直接驱动步进电机,同时MC33991中的电压/温度等检测模块可以随时检测电机的动转状态,并将检测结果通过SPI 以串行输出方式将数据反馈给主控电路。

2.2引脚功能VnuC5SCL K 5051SP1RST-18T ICOSOt SINOj C0S1匚・»»■>中国事揃 遵理_!«样|z 章TRTZ压低检过及压测H 桥及-COSO+ -COSO- -SSNO+ SINO COS1+c osi-RTZ SINH SiKl-L24WideBodySOICThermaltyEnhancedleadFramehttpffj^^gstgUdqxomCOS+、COS-、SIN+与SIN-:H 桥输出端。

mc中文资料

低成本开关电源芯片M C34063A (M C33063)中文资料该器件本身包含了DC/DC变换器所需要的主要功能的单片控制电路且价格便宜。

它由具有温度自动补偿功能的基准电压发生器、比较器、占空比可控的振荡器,R—S触发器和大电流输出开关电路等组成。

该器件可用于升压变换器、降压变换器、反向器的控制核心,由它构成的DC/DC变换器仅用少量的外部元器件。

在各类电子产品中均非常广泛的应用.MC34063主要特性:输入电压范围:2、5~40V输出电压可调范围:1.25~40V最大输出电流:1.5A最大开关频率:100kHz低静态电流短路电流限制可实现升压或降压电源变换器MC34063的内部结构,引脚图及引脚功能:图1MC34063内部结构及引脚图1脚:开关管T1集电极引出端;2脚:开关管T1发射极引出端;3脚:定时电容ct接线端;调节ct可使工作频率在100—100kHz范围内变化;4脚:电源地;5脚:电压比较器反相输入端,同时也是输出电压取样端;使用时应外接两个精度不低于1%的精密电阻;6脚:电源端;7脚:负载峰值电流(Ipk)取样端;6,7脚之间电压超过300mV时,芯片将启动内部过流保护功能;8脚:驱动管T2集电极引出端。

MC34063A在线电源计算器-OnlinePowercalculationMC34063主要参数:项目条件参数单位PowerSupplyVoltage电源电压VCC40VdcComparatorInputVoltageRange比较器输入电压范围VIR0.3-+40VdcSwitchCollectorVoltage集电极电压开关VC(switch)40VdcSwitchEmitterVoltage(VPin1=40V)发射极电压开关VE(switch)40VdcSwitchCollectortoEmitterVoltage开关电压集电极到发射极VCE(switch)40VdcDriverCollectorVoltage驱动集电极电压VC(driver)40VdcDriverCollectorCurrent(Note1)驱动集电极电流IC(driver)100mASwitchCurrent开关电流ISW1.5AOperatingJunctionTemperature工作结温TJ+150℃OperatingAmbientTemperatureRange操作环境温度范围TAMC34063A0-70℃MC33063AV40-125MC33063A40-85StorageTemperatureRange储存温度范围Tstg65-150℃MC34063应用电路图图2MC34063电压逆变器图3MC34063降压电路图4NPN三极管扩流升压转换器图5NPN三极管扩流降压转换器图6 升压转换器MC34063的工作原理MC34063组成的降压电路MC34063组成的降压电路原理如图7。

丹东华奥电子 LD33035 无刷直流电机控制器说明书

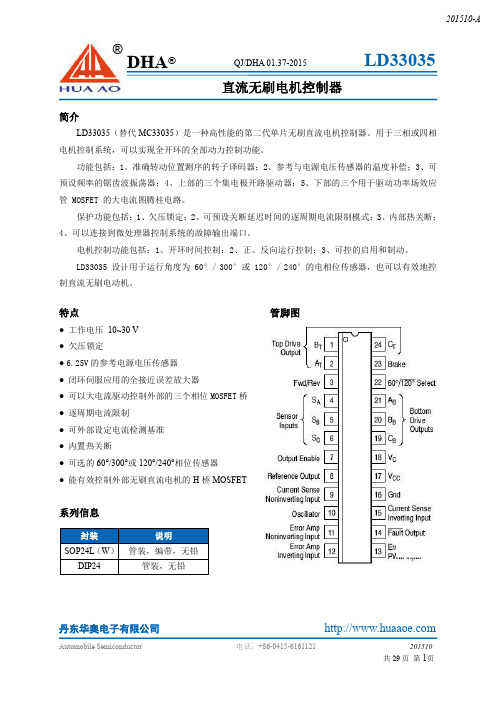

丹东华奥电子有限公司简介LD33035(替代MC33035)是一种高性能的第二代单片无刷直流电机控制器。

用于三相或四相电机控制系统,可以实现全开环的全部动力控制功能。

功能包括:1、准确转动位置测序的转子译码器;2、参考与电源电压传感器的温度补偿;3、可预设频率的锯齿波振荡器;4、上部的三个集电极开路驱动器;5、下部的三个用于驱动功率场效应管MOSFET 的大电流图腾柱电路。

保护功能包括:1、欠压锁定;2、可预设关断延迟时间的逐周期电流限制模式;3、内部热关断;4、可以连接到微处理器控制系统的故障输出端口。

电机控制功能包括:1、开环时间控制;2、正、反向运行控制;3、可控的启用和制动。

LD33035设计用于运行角度为60°/300°或120°/240°的电相位传感器,也可以有效地控制直流无刷电动机。

特点管脚图●工作电压10~30V ●欠压锁定●6.25V 的参考电源电压传感器●闭环伺服应用的全接近误差放大器●可以大电流驱动控制外部的三个相位MOSFET 桥●逐周期电流限制●可外部设定电流检测基准●内置热关断●可选的60°/300°或120°/240°相位传感器●能有效控制外部无刷直流电机的H 桥MOSFET系列信息封装说明SOP24L (W )管装,编带,无铅DIP24管装,无铅直流无刷电机控制器管脚功能描述丹东华奥电子有限公司功能示意图丹东华奥电子有限公司极限参数丹东华奥电子有限公司电参数(V CC=V C=20V,R T=4.7k,C T=10nF,T A=25℃,除非另外说明)丹东华奥电子有限公司CC C T T A注:1、输入共模电压或输入信号电压不应超过-0.3V。

2、调节电压不得超过−0.3至V REF范围。

丹东华奥电子有限公司介绍LD33035(替代MC33035)是一种单片的直流无刷电机控制器,它包含了开环控制的三、四相电机控制系统所需的全部功能。

RK3399W_V1.0 硬件规格书V_.0712

RK3399W V1.0智能工控主板之阿布丰王创作规格书文档修改历史目录第一章产品概述31.1适用范围31.2产品概述31.3产品特点31.4外观及接口示意图4第二章基本功能列表6第三章 PCB尺寸和接口规划83.1PCB尺寸图83.2接口参数说明9第四章电气性能20第五章组装使用注意事项21第一章产品概述1.1 RK3399W适用范围RK3399W属于商显智能自助终端主板,普遍适用于:互动广告机、互动数字标牌、智能自助终端、智能零售终端、O2O智能设备、工控主机、机器人设备等。

1.2 产品概述RK3399W采取瑞芯微RK3399 (双CortexA72大核+四 CortexA53小核)六核64位超强CPU,搭载Android7.1系统,主频高达2 GHz。

采取MaliT860MP4 GPU,支持4K、H.265硬解码。

多路视频输出和输入,性能更强,速度更快,接口更丰富,是您在人机交互、智能终端、工控项目上的最佳选择。

1.3 产品特点◆RK3399超强CPU搭载Android 7.1系统,速度更快,性能更强。

◆支持5G和2.4GWIFI,独立双天线。

◆双网口设计,支持1000M网口+100M网口。

◆内置PCIE 3G/4G模块接口.支持华为、中兴、龙尚等多种PCIE3G/4G模块,支持上网和通话.◆丰富的扩展接口.6个USB接口(1路USB3.0 OTG,1路USB Host 1路+3路HUB,1路TYPE C),1路485接口,4路可扩展串口(2路TTL,2路RS232),GPIO及ADC接口,可以满足市场上各种外设的要求。

◆高清晰度。

最大支持3840x2160的4K解码,支持LVDS/eDP/HDMIOUT/HDMI IN等接口的LCD显示屏、裁剪屏,支持双屏异显.◆支持Android系统定制,提供系统调用接口API 参考代码,完美支持客户上层应用APP开发。

◆完美支持红外、光学、电容、电阻、触摸膜等多种主流触摸屏,支持免驱触摸屏的HID配置,无需调试。

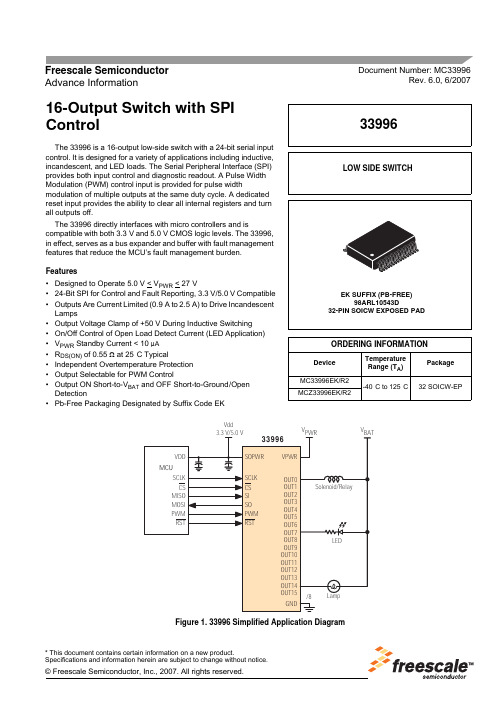

MCZ33996EK资料

VPWR SOPWR

VIN VD

fSPI

ECLAMP

VESD1 VESD2

TA TJ TC TSTG PD TPPRT

RθJA RθJL RθJC

-1.5 to 50 -0.3 to 7.0 -0.3 to 7.0 -0.3 to 45

6.0 50

±2000 ±200

-40 to 125 -40 to 150 -40 to 125 -55 to 150

MC33996EK/R2 MCZ33996EK/R2

Temperature Range (TA)

Package

-40°C to 125°C 32 SOICW-EP

Vdd

3.3 V/5.0 V

VPWR

VBAT

33996

VDD

MCU

SCLK CS

MISO MOSI PWM

RST

SOPWR

VPWR

SCLK CS SI SO PWM RST

Output 0 – Output 15

SOPWR Supply Battery Input

Ground System Clock

Chip Select Serial Input Serial Output

Reset PWM Control

Open drain output pin.

Power supply pin to the SO output driver. Battery supply input pin. Ground for logic, analog, and power output devices. System Clock for internal shift registers of the 33996. SPI control chip select input pin from the MCU to the 33996. Serial data input pin to the 33996. Serial data output pin. Active low reset input pin. PWM control input pin. Supports PWM on any combination of outputs.

莫萨 MC-3201 系列迷你计算机用户指南说明书

MC-3201SeriesCompact computers with 11th Gen Intel®Core™processor,designed for IIoT,AI,and marine applications,-20to 55°C operating temperatureFeatures and Benefits•11th Gen Intel®Core™processor (Tiger Lake U)•2built-in DDR4memory slots;total capacity up to 32GB•M.2B key socket for 5G,GPS,and M.2SATA SSD expansion modules •M.2E key socket for Wi-Fi and BT expansion modules•Variety of interfaces:2serial ports,4Giga LAN ports,2USB 3.1(type A)ports,and 4USB 2.0(type A)ports•Built-in TPM 2.0module•Complies with IEC-60945and IACS E10standardsCertificationsIntroductionThe MC-3201Series computers are built around a 11th Gen Intel®Celeron®or Intel®Core™i3,i5,or i7processor and come with 2DisplayPort interfaces,2USB 3.1ports,4GbE ports,and 23-in-1RS-232/422/485serial ports.The computers are also equipped with a 2.5-inch SSD/HDD slot and a built-in TPM 2.0module.Additional value and convenience are provided through a modular design with two independent slots for flexible system integration and ers have the option to add a variety of different communications modules,including Wi-Fi,5G,LTE,GPS,and M.2SATA SSD expansion modules.Compliance with the IEC-60945and IACS E10standards ensures the MC-3201delivers stable and reliable system operations for marine and IIoT applications.These certifications are issued to indicate the suitability of product for use in marine applications.Proactive Monitoring FunctionMoxa Proactive Monitoring is a small-footprint,resource-friendly,easy-to-use utility available with some Moxa computers to track a number of system parameters.You can view the current values for key parts by simply clicking on the icons corresponding to the parameters in a Windows-based user er-defined key part indicators (KPIs)are used to monitor the computer’s key parts.Visible and/or audio alerts are triggered automatically via relays and SNMP traps when these KPIs exceed their preset threshold values,making it extremely convenient for operators to avoid system downtime by setting up predictive maintenance tasks well in advance.The Proactive Monitoring tool is currently available with DA-720Series,DA-820C Series,MC-1200Series,MC-3201Series,and MC-7400Series.AppearanceFront Panel(S-S models)Front Panel(M-S models)SpecificationsComputerCPU MC-3201-TGL7-M-S/S-S Models:Intel®Core™i7-1185G7E processor(12M Cache,upto1.8GHz)MC-3201-TGL5-M-S/S-S Models:Intel®Core™i5-1145G7E processor(8M Cache,upto1.5GHz)MC-3201-TGL3-M-S/S-S Models:Intel®Core™i3-1115G4E processor(6M Cache,upto2.2GHz)MC-3201-TGL1-M-S/S-S Models:Intel®Celeron®6305E processor(4M Cache,up to1.8GHz)Graphics Controller Intel®Iris®Xe GraphicsSystem Memory Pre-installed8GB DDR4System Memory Slot SODIMM DDR42133slot x2,up to32GB max.Supported OS Linux Debian11,64-bit,kernel5.10Windows10Embedded IoT Ent2019LTSC64-bit(Both optional,available via CTOS)Storage Slot External:2.5-inch HDD/SSD slots x1Internal:M.2B key socket x1mPCIe socket x1Computer InterfaceEthernet Ports Auto-sensing10/100/1000Mbps ports(RJ45connector)x4Serial Ports RS-232/422/485ports x2,software selectable(DB9male)Digital Input M-S Models:DIs x4Digital Output M-S Models:DOs x4USB3.0USB3.0hosts x2,type-A connectorsUSB2.0USB2.0hosts x4,type-A connectors Video Output DisplayPort x2up to3840x2160resolution at60Hz Audio Input/Output Line in x1,Line out x1,3.5mm phone jack Buttons Reset buttonPower buttonTPM TPM v2.0Ethernet InterfaceMagnetic Isolation Protection 1.5kV(built-in)10/100/1000BaseT(X)Ports(RJ45connector)4Serial InterfaceBaudrate50bps to115.2kbpsConnector DB9maleData Bits5,6,7,8Flow Control RTS/CTS,XON/XOFFParity None,Even,Odd,Space,MarkStop Bits1,1.5,2ESD Protection4kV contact,8kV airSerial SignalsRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDRS-422Tx+,Tx-,Rx+,Rx-,GNDRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GND RS-485-2w Data+,Data-,GNDLED IndicatorsSystem Power x1Storage x1Serial2per port(Tx,Rx)LAN2per port(10/100/1000Mbps)Physical CharacteristicsDimensions220x80x170mm(8.66x3.15x6.69in) Weight3,000g(6.61lb)Housing MetalInstallation Wall mountingPower ParametersInput Voltage M-S Models:24VDCS-S Models:9to36VDCEnvironmental LimitsOperating Temperature-20to55°C(-4to131°F)Storage Temperature-30to60°C(-22to140°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMC EN55032/35EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:4kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:3V/mIEC61000-4-4EFT:Power:0.5kV;Signal:0.5kVIEC61000-4-5Surge:Power:0.5kV,Signal:1kVIEC61000-4-6CS:3VIEC61000-4-8PFMF:1A/m at50to60Hz Safety UL62368-1EN62368-1IEC62368-1IEC60950-1Shock IEC60068-2-27Vibration IEC60068-2-64Maritime M-S Models:IEC60945,IACS E10Green Product RoHS,CRoHS,WEEEMTBFTime323,270hrsStandards Telcordia(Bellcore)Standard TR/SR WarrantyWarranty Period3yearsDetails See /warrantyPackage ContentsDevice1x MC-3201Series computerInstallation Kit1x wall-mounting kitCable1x Power-jack-to-terminal-block cable Documentation1x quick installation guide1x warranty cardDimensionsOrdering InformationModel Name CPU RAMOptional OSStorage(SSD/HDD)LAN/Serial PortsUSB3.0/2.0PortsVideo OuputsInterfaceExpansionMC-3201-TGL7-S-S Intel®Core™i7-1185G7E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL5-S-S Intel®Core™i5-1145G7E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL3-S-S Intel®Core™i3-1115G4E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL1-S-S Intel®Celeron®6305E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL7-M-S Intel®Core™i7-1185G7E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL5-M-S Intel®Core™i5-1145G7E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL3-M-S Intel®Core™i3-1115G4E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E keyMC-3201-TGL1-M-S Intel®Celeron®6305E8GB512GB(max)4/22/42x Display1x mPCIe1x M.2B key1x M.2E key©Moxa Inc.All rights reserved.Updated Jul18,2023.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

MC33035中文

0.1

0.2

0.3

电源电流

ICC

--

12

16

mA

管脚 17 (VCC = VC = 20 V)

IC

--

14

20 0

管脚 17 ( VCC = 20 V, VC = 30 V)

--

3.5

6.0

管脚 18 ( VCC = VC = 20 V)

--

5.0

10

管脚 18 (VCC = 20 V, VC = 30 V)

ISC

40

75

–

mA

基准欠电压锁定阈值

Vth

4.0

4.5

5.0

V

误差放大器

输入偏移电压 (TA = –40° ~ +85°C)

VIO

--

0.4

10

mV

输入偏移电流 (TA = –40°∼+85°C)

IIO

--

8.0

500

nA

输入偏置电流 (TA = –40° ~ +85°C)

IIB

--

-46

-1000 nA

tHl ,低速驱 动响应 时间

图11,低速驱动响应时间 VS电流感应输入电压

250

VCC=20V

VC=20V

200

RL=∞

CT=10nF

150

TA=25℃

100

50

0 1.0

2.0 3.0 4.0 5.0 6.07.0 10 电流感应输入电压(标称为 Vth)

V sa t,输出饱 和电压 (V)

图12,fault输出饱和电压 VS陷电流

Vsat,输出饱和电压(V)

MC3399中文资料

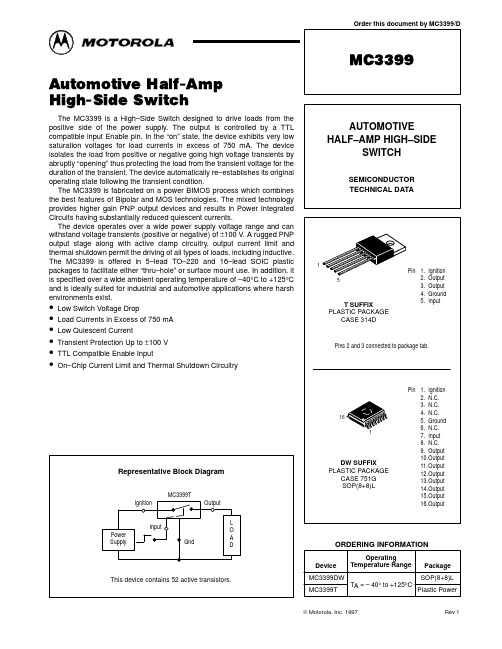

AUTOMOTIVE HALF–AMP HIGH–SIDE SWITCH

SEMICONDUCTOR TECHNICAL DATA

1 5

• • • • •

Load Currents in Excess of 750 mA Low Quiescent Current Transient Protection Up to ±100 V TTL Compatible Enable Input On–Chip Current Limit and Thermal Shutdown Circuitry

Ignition Output* IL 35 V Transient Generator + – 12 V Input Control Circuit Thermal Sense Current Limit 35 V RL 50 Ω

Ground

NOTE: * Depending on load current and transient duration, an output capacitor (CO) of sufficient value may be used to hold up output voltage during the transient, and absorb turn–off delay voltage overshoot.

MC3399T Ignition Output L O A D

DW SUFFIX PLASTIC PACKAGE CASE 751G SOP(8+8)L

Pin 1. Ignition 2. N.C. 3. N.C. 4. N.C. 5. Ground 6. N.C. 7. Input 8. N.C. 9. Output 10.Output 11. Output 12.Output 13.Output 14.Output 15.Output 16.Output

mc33035

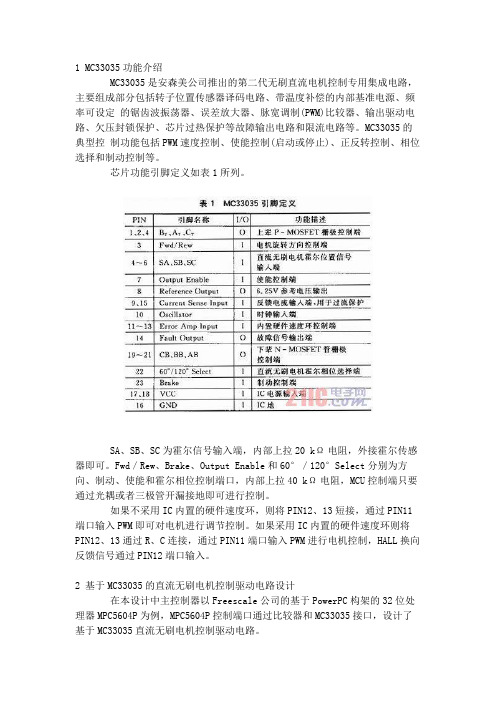

1 MC33035功能介绍MC33035是安森美公司推出的第二代无刷直流电机控制专用集成电路,主要组成部分包括转子位置传感器译码电路、带温度补偿的内部基准电源、频率可设定的锯齿波振荡器、误差放大器、脉宽调制(PWM)比较器、输出驱动电路、欠压封锁保护、芯片过热保护等故障输出电路和限流电路等。

MC33035的典型控制功能包括PWM速度控制、使能控制(启动或停止)、正反转控制、相位选择和制动控制等。

芯片功能引脚定义如表1所列。

SA、SB、SC为霍尔信号输入端,内部上拉20 kΩ电阻,外接霍尔传感器即可。

Fwd/Rew、Brake、Output Enable和60°/120°Select分别为方向、制动、使能和霍尔相位控制端口,内部上拉40 kΩ电阻,MCU控制端只要通过光耦或者三极管开漏接地即可进行控制。

如果不采用IC内置的硬件速度环,则将PIN12、13短接,通过PIN11端口输入PWM即可对电机进行调节控制。

如果采用IC内置的硬件速度环则将PIN12、13通过R、C连接,通过PIN11端口输入PWM进行电机控制,HALL换向反馈信号通过PIN12端口输入。

2 基于MC33035的直流无刷电机控制驱动电路设计在本设计中主控制器以Freescale公司的基于PowerPC构架的32位处理器MPC5604P为例,MPC5604P控制端口通过比较器和MC33035接口,设计了基于MC33035直流无刷电机控制驱动电路。

传统的直流无刷电机控制驱动电路采用MPC5604P、预驱动IC和MOSFET 实现,其中包括电压泵即自举电路。

本设计是基于直流无刷电机控制芯片MC33035实现的,MC33035实现预驱动和电子自动换向功能,采用MC33035实现直流无刷电机的控制驱动电路,既简化了电路设计,同时也减轻了MPC5604P 的运算量。

MPC5604P和MC33035之间通过光耦或者比较器实现电平转换。

Microsoft鼠标产品说明书

H3S-00003D5D-00001PN7-00001RJN-00001U7Z-00001GMF-001764FD-00025P58-00061 Sculpt Comfort Mouse Mobile Mouse 4000Mobile Mouse 3600Mobile Mouse 1850Mobile Mouse 3500Comfort Mouse 4500Basic Optic Mouse MSRP $39.95MSRP $34.95MSRP $29.95MSRP $14.95MSRP $29.95MSRP $22.45MSRP $14.95 Bluetooth Wireless USB Bluetooth Wireless USB Wireless USB Wired USB Wired USBBasicKTF-00013L6V-00001RVF-00052HDQ-00001 Modern Mobile Mouse Sculpt Ergonomic Mouse ARC Touch Mouse Classic IntelliMouse MSRP $34.99MSRP $59.95MSRP $59.95MSRP $39.99 Bluetooth Wireless USB Wireless USB Wired USB Premium Core CoreD e s k t o pPart Code L5V-000017N9-00001L3V-00001PP4-00001PP3-00001M7J-00001PT3-00001PY9-00001APB-00001Description Sculpt Ergonomic DesktopDesigner Desktop Sculpt Comfort DesktopComfort Desktop 5050Desktop 3050Desktop 2000Desktop 900Desktop 850Desktop 600Price MSRP $129.95MSRP $99.95MSRP $79.95MSRP $69.95MSRP $69.95MSRP $49.95MSRP $49.95MSRP $39.95MSRP $29.95Connection Wireless USB Bluetooth Wireless USB Wireless USB Wireless USBWireless USBWireless USBWireless USBWired USB Quality Premium Premium Premium Premium Core Core Core Core Basic Ergonomic Yes No Yes Yes No No No No No Battery Life36 months 9 months KB 18 months, MS 10 monthsKB 15 months, MS 8 monthsKB 15 months, MS 8 monthsKB 18 months, MS 8 months24 months 15 months N/A Box RetailRetailRetailRetailRetailRetailRetailRetailRetailWhy buy?Built on advanced ergonomic design principlesSlim with built-in trackpadMaximized for comfort andcustomized for youErgonomist approved and AES 128-Bit encryptionCompact, modern with AES 128-Bit encryptionQuality build and AES 128-Bit encryptionComfort with AES 128-Bit encryptionQuality build and AES 128-Bit encryption Quality design and AES 128-Bit encryption CommentAlso availablefor business (PN9-00005)Also availablefor business (3J2-00002)W e b c a mPart Code Q2F-00013H5D-00013T3H-00011Description LifeCam Studio LifeCam Cinema LifeCam 3000Price MSRP $99.95MSRP $69.95MSRP $39.95Connection Wired USB Wired USB Wired USB Quality Premium Premium Core Ergonomic N/A N/A N/A Battery LifeN/A N/A N/A BoxRetail Retail RetailWhy buy?1080p HD sensor, 720p HD video, Skype certifiedTrue 720p HD video plus auto focusTrue 720p HD VideoCommentAlso available for business (5WH-00002)Also available for business (6CH-00002)Also available for business (T4H-0002)H e a d s e t sPart Code 7XF-00001JUG-00013Description LifeChat LX-6000LifeChat LX-3000Price MSRP $80.95MSRP $39.95Connection Wired USB Wired USB Quality Premium Basic Ergonomic N/A N/A Battery LifeN/A N/A BoxRetailRetail Why buy?High-fidelity sound,7 foot cable, inline volume, Skype / Lync certified6 foot cable, Skype certifiedCommentAlso available for business (7XF-00001)K e y b o a r dPart Code 5KV-00001LXM-00001QSZ-00001N9Z-00001PZ3-00001ANB-00001Description Sculpt Ergo KeyboardMicrosoft Ergonomic KeyboardMicrosoft Bluetooth ® KeyboardAll-in-One Media KeyboardKeyboard 850Keyboard 600Price MSRP $85.95MSRP $59.99MSRP $49.99MSRP $39.95MSRP $29.95MSRP $16.95Connection Wireless USB Wired USB Wireless USBWireless USBWireless USBWired USB Quality Premium Core Core Core Basic Basic Ergonomic Yes Yes No No No No Battery Life36 months N/A 36 months 9 months 15 months N/A BoxBusiness RetailRetail RetailRetailRetailWhy buy?Ergonomist approvedAll-day typing comfortA sleek, wireless typing experienceSlim with built-in trackpadQuality design and AES 128-Bit encryptionQuality design and AES 128-Bit encryptionCommentAlso availablen White (ANB-00026)A d a p t e r sPart Code P3Q-00001HFR-00001Description Wireless DisplayAdapter USB-C to VGA Adapter Price MSRP $49.95MSRP $39.99Connection USB/HDMI Wired USB Quality Premium Core Ergonomic N/A N/A Battery LifeN/A N/A BoxRetail RetailWhy buy?See it all on your big screenShare photos, video, and presentations in a way that’s larger than lifeCommentErgonomics Modern Productivity Gaming Classic。

奥 местLCD电视AT3201W用户手册说明书

ContentsImportant safety instructions 5Taking care of your remote control 6Cleaning and servicing 6First things first 7Basic features and benefits 7Packing checklist 7Your LCD TV overview 8Front panel view 8Rear panel view 9Basic connection 11Connecting the power cord 11Connecting an antenna 11Connecting DVD/VCR/AV equipment 12Connecting a camera, camcorder or video game 12Connecting headphones 13Connecting a PC or Notebook 13Remote control overview 14Getting started 18Power On 18Setup Wizard 18Changing channels 18Adjusting the volume 18OSD Navigation 19Navigating the OSD using the remote control: 19Advanced Features 20Empowering Key: Scenario Mode and Favourite Channels 20PIP/PBP/POP 22Parental Control 22Troubleshooting 23Product specifications 24English5Important safety instructionsRead these instructions carefully. Save them for fu-ture reference.1 Follow all warnings and instructions marked onthe product.2 Unplug this product from the power outlet be-fore cleaning. Use a soft, moist cloth for clean-ing. Do not use liquid or aerosol cleaners.3 Do not use this product near water. Do not spillwater or any other liquid on the product.4 Do not place this product on an unstable cart,stand, or table. The product may fall, causing serious damage to the product.5 Slots and openings are provided for ventila-tion; to ensure reliable operation of the prod-uct and to protect it from overheating. These openings must not be blocked or covered. The openings should never be blocked by placing the product on a bed, sofa, rug, or other simi-lar surface. This product should never be placed near or over a radiator or heat register, or in a built-in installation unless proper ventilation is provided.6 This product should be operated from the typeof power source indicated on the label. If you are unsure of the type of power source avail-able, consult your dealer or local power com-pany before use.7 Do not step on or place heavy objects on thepower cord. Carefully route the power cord and any cables away from foot traffic. Do not locate this product where persons will step on the cord.8 If an extension cord is used with this product,make sure that the total ampere rating of the equipment plugged into the extension cord does not exceed the extension cord ampere rating. Also, make sure that the total rating of all products plugged into the wall outlet does not exceed the fuse rating.9 Never push objects of any kind into this prod-uct through cabinet slots as they may touch dangerous voltage points or short out parts that could result in a fire or electric shock. 10 Do not attempt to service this product yourself,as opening or removing covers may expose you to dangerous voltage points or other risks. Re-fer all servicing to qualified service personnel.11 Unplug this product from the wall outlet andrefer servicing to qualified service personnel under the following conditions:a. When the power cord or plug is damaged or frayed.b. If liquid has been spilled into the product.c. If the product has been exposed to rain or water.d. If the product does not operate normally when the operating instructions are fol-lowed. Adjust only those controls that are covered by the operating instructions since improper adjustment of other controls may result in damage and will often require extensive work by a qualified technician to restore the product to normal condition.e. If the product has been dropped or the case has been damaged.f. If the product exhibits a distinct change in performance, indicating a need for service.12 Only use the correct power cord (provided inyour accessories box) for this product. Always disconnect the power cord from the wall outlet before servicing or disassembling this equip-ment.E n g l i s h6Taking care of your remote controlFollow these steps to ensure proper care of your remote control:• Handle the remote control with care. Dropping it, placing it in direct sunlight, or allowing it to getwet may cause damage.• Do not tamper with the batteries, and keep them away from children.• When you anticipate that the remote control will not be used for an extended period, remove thebatteries to prevent possible damage from battery leakage.• Dispose of batteries according to local regulations. Recycle if possible.Cleaning and servicingWhen cleaning your LCD TV, follow these steps:1 Power off the TV.2 Disconnect the power cord.3 Use a soft, moist cloth. Do not use liquid or aerosol cleaners.E n g l i s h8Your LCD TV overviewFront panel viewNo. Item DescriptionHeadphone Connects to headphones.Input Select source.When the OSD is on, press this button to confirm selection Vol Down Volume down.When the OSD is on, functions the same as the Left arrow Vol Up Volume up.When OSD is on, functions the same as the Right arrow Channel Down Channel down.When the OSD is on, functions the same as the Down arrow Channel Up Channel up.When the OSD is on, functions the same as the Up arrow Menu Turns the OSD menu ON and OFFPowerTurns the Power ON and OFFEnglishNo. Item DescriptionTuner Connects to the outdoor antenna cableAV1 / SCART 1 In Supports an external device with a SCART cable(for RGB, CVBS, S-Video,Audio left/right input)Out In TV mode, connects to your VCR In or PVR In with SCART cable to re-cord TV programsAV2 / SCART 2 In Supports external device with a SCART cable(for RGB, CVBS, S-Video,YPbPr/YCbCr, Audio left/right input)Out In TV mode, connect to your VCR In or PVR In with a SCART cable to re-cord TV programsAudio Out Connects to the audio jack input of your external device.AV3Audio-R Connects to the Audio-R output of your DVD, VCR player using the redcomposite cableAudio-L Connects to the Audio-L output of your DVD, VCR player using the whitecomposite cablePr/Cr Connects to the Component- Pr/Cr output of your DVD, VCR player usingthe red component cablePb/Cb Connects to the Component- Pb/Cb output of your DVD, VCR player us-ing the blue component cableY Connects to the Component-Y output of your DVD, VCR player using thegreen component cable9E n g l i s hDISPLAY MUTETV RECALL MENUMPXSWAP ACTIVE POSITIONSIZE/MODEINDEX SUBTITLE TELETEXT REVEALSIZE MIX SUBPAGE HOLDVOL PIP/PBP/POPCHOKENTERAV SCART PCSLEEP ZOOM WIDE SRS1234567809Teletext keysSUBPA G E H O L D Remote control overviewEnglishTeletext keysItem DescriptionINDEX Go to the index page SUBTITLE Show subtitlesTELETEXT Press to switch from TV/AV to Teletext mode. REVEAL Press to reveal hidden teletext information.SIZE Press once to zoom teletext page to 2X; press again to resume. MIX Press to overlay teletext page on the TV image, i.e. subtitles.HOLDPress to pause the current teletext page in multi-page viewing mode. Color buttons (R/G/Y/B)Operates corresponding button on the teletext page.There are five main OSD menus. These are: Picture, Audio. Use the following method to easily navigate these menus.OKUse the OSD to define your “e” Empowering Key setting: Scenario mode or Favourite channel. The default for the “e” key is the Scenario mode. Follow these steps: Menu > Empowering > e Key Setting. Choose between “Favourite channel” or “Scenario mode.” Now, when you press the “e” key, your chosen selec-Scenario ModePress the“e”Empowering key and use the Scenario mode to select pre-defined audio and video settings for optimal enjoyment of the following scenarios: Standard, Movie, Sport, Concert, Game, User; and smoothly presents moving images.Scenario Mode Design DirectionStandard mode allows you to watch your favourite channels with sharp, brilliantimagery via adaptive brightness and contrast adjustments. Clear-sounding audio isprovided by SRS performance.For comfortably enjoying movies at home, Movie mode displays dim scenes inclear detail; compensates for colour; and smoothly presents moving images. Thisis accomplished through optimal Gamma correction plus saturation, brightnessand contrast adjustments. Movie mode makes the most of high-definition movieViewing your favourite channelsOn the remote control, if you press the “e” Empowering key for less than 1 second, the favourite channel table will pop up. Your currently selected favourite channel will be highlighted. To view your other favourite channels, press the “e” Empowering key again to toggle the TV channels sequentially according to your favourite list.In TV, AV, SCART and PC mode, press PIP/PBP/POP button once to display using picture- in- picture (PIP). Press twice to display using picture- by- pic-In SCART and PC mode, press PIP/PBP/POP button three times to display picture-on-picture (POP). Then, the POP screens will display the subsequent TV channels one-by-one.PBP (Picture by Picture)PIP (Picture in Picture)EnglishTroubleshootingBefore you call the Acer service center, please check the following items:The following is a list of possible situations that may arise during the use of your LCD TV. Easy answers and solutions are provided for each one.There is no picture or sound.• Make sure the power cord is properly inserted in the power outlet.• Make sure the input mode selector is set to the correct source.• Make sure the antenna at the rear of the TV is properly connected.• Make sure the main power switch is turned on.• Make sure the volume is not set to minimum or the sound is not set to mute.• Make sure the headphones are not connected.• Reception other than those of broadcasting stations can be considered.Picture is not clear.• Make sure the antenna cable is properly connected.• Consider whether TV signals are being properly received.• Poor picture quality can occur due to a VHS camera, camcorder, or other peripheral being connectedat the same time. Switch off one of the other peripherals.• The ‘ghost’ or double image may be caused by obstruction to the antenna due to high rise buildingsor hills. Using a highly directional antenna may improve the picture quality.• The horizontal dotted lines shown on the pictures may be caused by electrical interference, e.g. hairdryer, nearby neon lights and etc. Turn off or remove these equipment.Picture is too dark, too light or tinted.• Check the color adjustment.• Check the brightness setting.• Check the sharpness function.• Fluorescent lamp may have reached the end of service life.Remote control does not work.• Check the batteries of the remote control.• Make sure the remote sensor window is not blocked or under strong fluorescent lighting.• Try to clean the remote control sensor lens on the TV with a soft cloth.• Use the buttons (hot keys) on the TV before the remote control works.If the above items do not solve your technical issue, please refer to the warranty card for service information.E n g l i s hProduct specificationsItem SpecificationPanel specifications Resolution1366 x 768 pixels Brightness (typical.) 500 nits Contrast Ratio (typical.) 800:1 Display colors16.7 M Viewing Angle (typical.) H:170 ; V:170Response Time (typical.)12 ms (gray to gray)Power supply Input100V to 240 V-AC. Max. power consumption 210 WPower Saving5 WMechanical Dimensions (W x H x D mm) 1018 x 616 x 210 mm Swivel angle 40 degrees(R20 & L20) Weight (kg) / (lbs.) 20.7kg / 45.6lbs.Wall MountingYesTerminal AV1/ SCART1 SCART(RGB,CVBS,S-Vidoe,Audio R/L )AV2/ SCART2 SCART(RGB,CVBS,S-Video,YPbPr/CbCr,Audio R/L ) AV3 RCA for YPbPr/CbCr,Audio R/L AV4 RCA for CVBS, Audio R/L AV5 S-Video, Audio R/L PC D-sub Yes DVI-D(HDCP) Yes PC audio-in Yes Audio-out YesHeadphonesYesAudio system 3D surround YesSpeakers 10 W + 10 WSRSWOW。

MY9373技术文档

(Iout0 Iout1 ... Iout15) −(Ideal Output Current)

% (

16

(Ideal Output Current)

*100%

*3 输出电流对输出电压变化的偏移量公式定义如下:

%/V

Ioutn (@Voutn 3V) − Ioutn (@Voutn 1V) 100%

MY-SEMI

输入及输出等效电路

1. DCK, DI, LAT, GCK 输入端

Preliminary

2. DO 输出端

MY9373

最大限定范围(Ta=25C, Tj(max) = 150C)

特性 电源电压 输入端电压 输出端电流 输出端耐受电压 资料时钟频率 灰阶时钟频率 接地端电流

热阻值(On 4-Layers PCB)

输入信号固定 Rrext = 14KΩ 所有输出关闭 输入信号固定 Rrext = 14KΩ 所有输出打开 输入信号固定 Rrext = 1.4KΩ 所有输出关闭 输入信号固定 Rrext = 1.4KΩ 所有输出打开

MY9373

最小值 0.7VDD

GND

一般值

VDD-0.4 1

最大值 单位

VDD V

MY-Semi Inc. 0

MY9373

功能方块图

Preliminary

MY-SEMI

管脚说明

编号.

SS

QF

1

10

2

23

3

24

4

1

5~20 2~9,11~18

21

20

22

19

23

21

24

22

名称 功能说明

威斯丹利智能家庭中控网关说明书

扫扫码码关关注注公公众众号号

广州市威士丹利智能科技有限公司

GGuanggzzhhoouuVAePnsOi LInLtOelliSgmenatrtTeTcehcnhonloogloy gCyoC., oL.t,dLtd 广广州州市市⻩⻩埔埔区区科科学学大大道道181号8号广广州芯州大芯厦大8厦楼8楼 全全国国服服务务热热线线::4040-06-868-84-2432838

Q3:网关无法添加 a. 指示灯是否亮的。若不亮,请确认线路是否联通的,是否停电。 b. 指示灯亮的,复位后,指示灯是否有相应改变。若指示灯没有相应反应,

尝试重启。

3. 包装成箱的产品,应放在通⻛、干燥、无腐蚀性气体的地方 贮存,堆放高度不能超过十层,仓库温度-10℃~+40℃,湿 度≤75%。

4. 避免雨、雪、猛力撞击等。

Zigbee指示灯

WAN网口 LAN网口 CLR复位孔 电源插孔

电源指示灯 网络指示灯

USB插口 POWER按键 C-3B401-10

Zigbee指示灯

WAN网口 CLR复位孔

电源插孔

USB插口 POWER按键

Zigbee入网孔: 短按,网关打开设备搜索入网。 CLR 复 位 孔: ⻓按5秒,设备恢复出厂默认状态 POWER 按键: ⻓按5秒,清除用户信息,用户可重新绑定

最大发射功率:20dbm 无线信道:2.4GHz 材质:PC+ABS 工作温度:0-40℃ 工作湿度:10%-90%RH

三.孔位标示

C-3B501-10

C-3B502-10

指示灯

Zigbee入网孔 CLR复位孔

POWER按键 LAN/WAN

LAN/WAN POWER按键

-2-

WOC产品介绍

有线电视无线网络产品介绍

北 京 志 扬 创 新 科 技 有 限 公 司

Beijing Cytech Systems Ltd – WLAN Over CATV System

产品资质

• 国家专利技术申请 200410086857.6 • 通过国家广电系统产品认证 CATVA7-2007-0830/31

WOC产品的特性

• 不需电源:安装过程中无需另外设置外接电源 • 不需布线:可利用原有的有线电视线路直接加载无线讯号 • 容易安装:仅需更换有线电视面板和分频器,安装简单,改 装周期短。

• 不易损坏:所以无线宽带都属于内置天线,安装完成后不易 损坏。

• 降低成本:相对于有线综合布线而言,安装数量越多,则综 合安装成本越低。

WOC系列: 分配器

• 型号…WD-02 • 二分配器

– 1个输入至2个输出

• 宽广的使用频率范围

– 5MHz~2.6GHz

• 低损耗

– 低于 6dB

• 连结头造型

– F头母头

WD-02

Beijing Cytech Systems Ltd – WLAN Over CATV System

WOC系列:合路分配器

Beijing Cytech Systems Ltd – WLAN Over CATV System

WOC产品的应用

• 酒店客房的无线覆盖 • 酒店会议室、咖啡厅、大堂的无线覆盖 • 医院病房的无线覆盖

• 学生公寓的无线覆盖

• 别墅公寓的无线覆盖 • 办公场所的无线覆盖

Beijing Cytech Systems Ltd – WLAN Over CATV System

30cm连结头造型smabeijingcytechsystemsltdwlanovercatvsystem串接方式5c2v同轴电缆有线电视电缆网络有线电视电缆网线射频连接缆线5c2v同轴电缆无线局域网wl030ts33bts33bts33bts33bts33ms01beijingcytechsystemsltdwlanovercatvsystem串并接混合方式5c2v同轴电缆有线电视电缆wl030ts33bts33bts33bts33ms02ts33bts33bts33bts33网络beijingcytechsystemsltdwlanovercatvsystemts33b串并接混合方式5c2v同轴电缆ts33bts33bts33ms04ts33bts33bts33ts33bts33bts33ts33ts33b有线电视电缆网络beijingcytechsystemsltdwlanovercatvsystem并接方式5c2v同轴电缆ts33ms08ts33ts33ts33ts33ts33ts33ts33有线电视电缆网络beijingcytechsystemsltdwlanovercatvsystem并接方式5c2v同轴电缆ts33ms08ts33ts33ts33ts33ts33ts33ts33ts33bts33有线电视电缆网络wd02beijingcytechsystemsltdwlanovercatvsystem系统架构示意accesspoint80211catv信号将catv信息和wifi混频送至cableout同轴线缆分配器分支器带天线面板终端分离器1分支终端分离器wlan天线面板beijingcytechsystemsltdwlanovercatvsystem损耗值5c电视缆线损耗为每米05db空气介质损耗

AK4399EQ中文资料