纵向横向晶体管区别[1]

横向pnp晶体管的工作原理

横向pnp晶体管的工作原理英文回答:Lateral pnp Transistor Operation.A lateral pnp transistor is a type of bipolar junction transistor (BJT) in which the emitter, base, and collector regions are formed in a single semiconductor layer. The emitter and collector regions are heavily doped, while the base region is lightly doped. The emitter-base junction is forward-biased, while the base-collector junction is reverse-biased.When the emitter-base junction is forward-biased, electrons from the emitter region diffuse into the base region, where they recombine with holes. This creates a depletion region around the emitter-base junction. The depletion region prevents electrons from the emitter region from reaching the collector region.When the base-collector junction is reverse-biased, holes from the collector region diffuse into the base region, where they recombine with electrons. This creates a depletion region around the base-collector junction. The depletion region prevents holes from the collector region from reaching the emitter region.The width of the depletion regions around the emitter-base and base-collector junctions depends on the applied bias voltages. When the emitter-base junction is forward-biased, the depletion region around the emitter-base junction is narrow, and the depletion region around the base-collector junction is wide. This allows electrons from the emitter region to diffuse into the base region, but prevents holes from the collector region from reaching the emitter region.When the emitter-base junction is reverse-biased, the depletion region around the emitter-base junction is wide, and the depletion region around the base-collector junction is narrow. This prevents electrons from the emitter region from reaching the base region, and allows holes from thecollector region to reach the emitter region.The width of the depletion regions around the emitter-base and base-collector junctions also depends on thedoping concentrations of the emitter, base, and collector regions. When the emitter region is heavily doped, the depletion region around the emitter-base junction is narrow. When the base region is lightly doped, the depletion region around the emitter-base junction is wide. When thecollector region is heavily doped, the depletion region around the base-collector junction is narrow.The lateral pnp transistor is a versatile device that can be used in a variety of applications. It is often usedin power amplifiers, switching circuits, and logic circuits.中文回答:横向pnp晶体管的工作原理。

NPN型三极管和PNP型的区别

1.PNP型晶体管PNP晶体管是另一种类型晶体管。

它的工作原理和NPN晶体管相似,只是在基区运动并放大信号的多数载流子是空穴而不是电子。

PNP晶体管的发射结要正偏,基区的电压要比发射区的电压要高,而集电极要是多数载流子空穴通过,集电区的电压要比基区的要低。

这一点和NPN晶体管的极间电位正好相反。

在双极模拟集成电路中要应用NPN-PNP互补设计以及某些偏置电路极性的要求,需要引入PNP结构的晶体管。

如横向PNP管广泛应用于有源负载、电平位移等电路中。

它的制作可与普通的NPN管同时进行,不需附加工序。

在横向PNP管中,发射区注入的少子(空穴)在基区中流动的方向与衬底平行,故称为横向PNP 管。

纵向PNP管其结构以P型衬底作集电区,集电极从浓硼隔离槽引出。

N型外延层作基区,用硼扩散作发射区。

由于其集电极与衬底相通,在电路中总是接在最低电位处,这使它的使用场合受到了限制,在运放中通常只能作为输出级或输出缓冲级使用。

2.Plug and Play在PnP技术出现之前,中断和I/O端口的分配是由人手工进行的,您想要这块声卡占用中断5,就找一个小跳线在卡上标着中断5的针脚上一插。

这样的操作需要用户了解中断和I/O端口的知识,并且能够自己分配中断地址而不发生冲突,对普通用户提出这样的要求是不切实际的。

PnP技术就是用来解决这个问题的,PnP技术将自动找到一个不冲突的中断和I/O地址分配给外部设备,而完全不需要人工干预。

但是如果您读懂了上面关于中断冲突的那一部分,您就应该了解,在中断资源非常紧张的今天,即使是PnP技术,也不一定能找到一个合适的中断分配给您刚刚插入的设备,所以尽量释放那些没有必要的中断,对PnP正常工作也是很有帮助的。

有些PnP冲突来源于主板的设计。

许多主板上有一个AGP插槽、五个PCI插槽和两个ISA插槽,而其中的AGP插槽一般是和一个PCI插槽共用一个中断的,也就是这两个槽的中断可以是合理的任何值,但必须是相同的,当您在AGP槽上插了显示卡,如果您还在同中断的PCI槽上插了一块声卡的话,就一定会产生中断冲突。

计算机一级考试内容核心知识点总结

计算机一级考试内容核心知识点总结计算机一级考试核心知识点总结。

一、计算机基础知识。

1. 计算机发展历程。

- 第一代计算机(1946 - 1957):电子管计算机,如ENIAC,体积大、功耗高、速度慢,主要用于科学计算。

- 第二代计算机(1958 - 1964):晶体管计算机,体积减小、功耗降低、速度提高,开始应用于数据处理和事务管理。

- 第三代计算机(1965 - 1970):中小规模集成电路计算机,可靠性和速度进一步提高,应用范围更广。

- 第四代计算机(1971年至今):大规模和超大规模集成电路计算机,微型计算机得到广泛应用,计算机网络迅速发展。

2. 计算机系统组成。

- 硬件系统。

- 中央处理器(CPU):包括运算器和控制器。

运算器进行算术和逻辑运算;控制器负责控制计算机各部件协调工作。

CPU的性能指标主要有主频、字长、核心数等。

- 存储器。

- 内存储器(内存):随机存取存储器(RAM),断电后数据丢失;只读存储器(ROM),断电后数据不丢失,如BIOS。

内存的容量和读写速度影响计算机性能。

- 外存储器:如硬盘、光盘、U盘等。

硬盘容量大、读写速度较快,是计算机主要的外存设备;光盘有CD、DVD等类型;U盘便于携带、使用方便。

- 输入设备:如键盘、鼠标、扫描仪等。

键盘用于输入字符信息;鼠标用于操作图形界面;扫描仪用于将纸质文档转换为电子文档。

- 输出设备:如显示器、打印机、音箱等。

显示器用于显示计算机处理结果;打印机有喷墨、激光等类型,用于打印文档;音箱用于输出声音。

- 软件系统。

- 系统软件:操作系统(如Windows、Linux、macOS等),管理计算机硬件资源和软件资源,提供用户与计算机交互的界面;语言处理程序,将高级语言编写的程序转换为机器语言;数据库管理系统,用于管理数据库中的数据。

- 应用软件:如办公软件(Microsoft Office、WPS等)、图像处理软件(Photoshop等)、视频播放软件(PotPlayer等)等,用于满足用户特定的需求。

LDMOS简介

什么是RF LDMOS晶体管DMOS主要有两种类型,垂直双扩散金属氧化物半导体场效应管VDMOSFET(vertical double-diffused MOSFET)和横向双扩散金属氧化物半导体场效应管LDMOSFET (lateral double-dif fused MOSFET)。

LDMOS由于更容易与CMOS工艺兼容而被广泛采用。

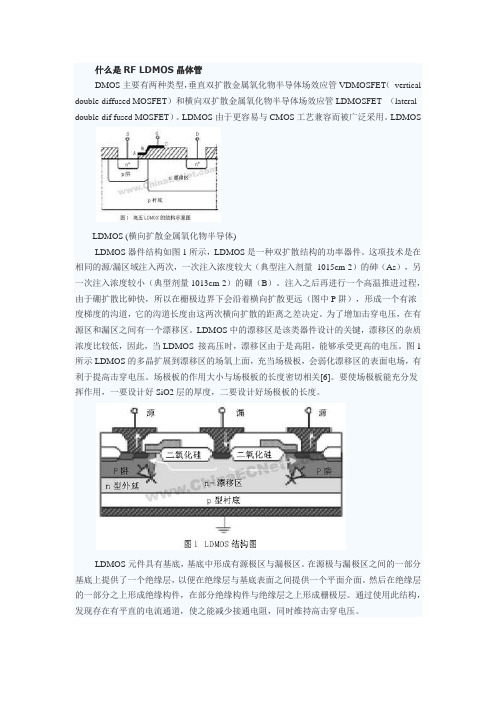

LDMOSLDMOS (横向扩散金属氧化物半导体)LDMOS器件结构如图1所示,LDMOS是一种双扩散结构的功率器件。

这项技术是在相同的源/漏区域注入两次,一次注入浓度较大(典型注入剂量1015cm-2)的砷(As),另一次注入浓度较小(典型剂量1013cm-2)的硼(B)。

注入之后再进行一个高温推进过程,由于硼扩散比砷快,所以在栅极边界下会沿着横向扩散更远(图中P阱),形成一个有浓度梯度的沟道,它的沟道长度由这两次横向扩散的距离之差决定。

为了增加击穿电压,在有源区和漏区之间有一个漂移区。

LDMOS中的漂移区是该类器件设计的关键,漂移区的杂质浓度比较低,因此,当LDMOS 接高压时,漂移区由于是高阻,能够承受更高的电压。

图1所示LDMOS的多晶扩展到漂移区的场氧上面,充当场极板,会弱化漂移区的表面电场,有利于提高击穿电压。

场极板的作用大小与场极板的长度密切相关[6]。

要使场极板能充分发挥作用,一要设计好SiO2层的厚度,二要设计好场极板的长度。

LDMOS元件具有基底,基底中形成有源极区与漏极区。

在源极与漏极区之间的一部分基底上提供了一个绝缘层,以便在绝缘层与基底表面之间提供一个平面介面。

然后在绝缘层的一部分之上形成绝缘构件,在部分绝缘构件与绝缘层之上形成栅极层。

通过使用此结构,发现存在有平直的电流通道,使之能减少接通电阻,同时维持高击穿电压。

LDMOS与普通MOS管主要有两点区别:1,采用LDD结构(或称之为漂移区);2,沟道由两次扩散的横向结深控制。

LDMOS 的优势• 卓越的效率,可降低功率消耗与冷却成本• 卓越的线性度,可将信号预校正需求降到最低• 优化超低热阻抗,可缩减放大器尺寸与冷却需求并改善可靠度• 卓越的尖峰功率能力,可带来最少数据错误率的高3G 数据率• 高功率密度,使用较少的晶体管封装• 超低感抗、回授电容与串流闸阻抗,目前可让LDMOS 晶体管在双载子器件上提供7 bB 的增益改善• 直接源极接地,提升功率增益并免除BeO 或AIN 隔离物质的需求• 在GHz 频率下拥有高功率增益,带来更少设计步骤、更简易更具成本效益的设计(采用低成本、低功率驱动晶体管)• 绝佳的稳定性,由于负漏极电流温度常数,所以不受热散失的影响• 比双载子更能忍受较高的负载未匹配现象(VSWR),提高现场实际应用的可靠度• 卓越的射频稳定度,在栅极与漏极间内置隔离层,可以降低回授电容• 在平均无故障时间(MTTF) 上有相当好的可靠度LDMOS主要的缺点1.功率密度低;2.容易受到静电的破坏。

集成运算放大电路全篇

Y0 Y1 Y2 Y3 B

注:式中Aod为差模开环放大倍数。

二、 集成运放中的电流源电 路

4.2.1 基本电流源电路

一、镜像电流源

+VCC

IR

B IC0

T0

R 2IB

A

IB0

IB1

IC1 T1

UBE0= UBE1, β0=β1=β, IC0=IC1=IC= βIB , IC1为输出电流, IR为基准电流。

基准电流表达式:

IR

用

uP

集成运放组成方框图:

输入级

uN

中间级

输出级 uO

偏置电路

1) 输入级 又称前置级,常为双输入高性能差分放大电路(高Ri 、大Ad、 大KCMR、静态电流小)。输入级的好坏直接影响着集成运放的大多数性能 参数。

2) 中间级 主放大器,使集成运放具有较强的放大能力,多采用共射 (或共源)放大电路。放大管经常采用复合管,以恒流源做集电极负载。

R`3

C`1 R`3

2.1k

2.1k

R`5 240k

C`1

R`4 25k

R`5 240k

- +

R7 100k

-∞ A3

(以下电路同上,仅C1、C2 值不同,电路从略)

图5.6 十五段优质均衡器

(2) 当R4的滑动触头移到最左边时,其电路如图8.7(a)所示。

C1

R3

R3

C2 R5

R4 R5

-∞

R6

B点的电流方程为:

IR

IB2

IC

IC2

1 2

IC2

2

2

2 2

2

I

C

2

IC2

(1

数控车床纵向进给系统和横向进给系统的设计

1绪论1.1数控系统的发展简史1952年第一代数控系统一一电子管数控系统的诞生。

20世纪50年代末,完全由固定布线的晶休管元器件电路所组成的第二代数控系统一一晶体管数控系统被研制成功,取代了昂贵的、易坏的、难以推广的电子管控制装置。

随着集成电路技术的发展,1965年出现了第三代数控系统一一集成电路数控系统。

1970年,在美国芝加哥国际机床展览会上,首次展出了第四代数控系统一一小型计算机数控系统,然后,随着微型计算机以其无法比拟的性能价格比渗透各个行业,1974年,第五代数控系统一一微型计算机数控系统也出现了。

应用一个或多个计算机作为数控系统的核心组件的数控系统统称为计算机数控系统(CNC)。

综上所述,由于微电子技术和计算机技术的不断发展,数控机床的数控系统也随着不断更新,发展非常迅速,几乎5年左右时间就更新换代一次⑴。

数控机床是先进制造业的基础机械,是最典型的多品种、小批量、高科技含量的机电一体化产品。

欧、美、日等工业化国家已先后完成了数控机床产品进程,1990年日本机床产值数控化率达75%,美国达70. 1%,德国达57%。

目前世界数控机床年产量超过15万台,品种超过1500多种[2]。

1.2我国数控系统的发展现状及趋势1.2.1数控技术状况目前,我国数控系统正处在由研究开发阶段向推广应用阶段过渡的关键时期,也是由封闭型向开放型过渡的时期。

我国数控系统在技术上已趋于成熟,在重大关键技术(包括核心技术),已达到国际先进水平。

自“七五”以来,国家一直把数控系统的发展作为重中之重来支持,现已开发出具有中国版权的数控系统,掌握了国外一直对我国封锁的一些关键技术。

例如,曾长期困扰我国、并受到西方国家封锁的多坐标联动技术对我们已不再是难题,0.1 J m当量的超精密数控系统、数控仿型系统、非圆齿轮加工系统、高速进给数控系统、实时多任务操作系统都已研制成功。

尤其是基于PC机的开放式智能化数控系统,可实施多轴控制,具备联网进线等功能既可作为独立产品,又是一代开放式的开发平台,为机床厂及软件开发商二次开发创造了条件。

横向晶体管和纵向晶体管

横向晶体管和纵向晶体管晶体管是现代电子技术的基石,无论是计算机、手机还是电视等电子设备都离不开晶体管的参与。

在众多类型的晶体管中,横向晶体管和纵向晶体管是最为常见和重要的两种。

本文将详细介绍横向晶体管和纵向晶体管的定义、特点以及在电子技术中的应用,以期给读者一个全面而又生动的了解,并为相关领域的研究和开发提供一定的指导。

首先,我们来了解一下横向晶体管。

横向晶体管又称为MOSFET (金属-氧化物-半导体场效应晶体管),它是一种基于场效应原理工作的晶体管,用途广泛。

横向晶体管的主要特点是通过改变栅极电压来控制导电的沟道。

对于晶体管中的栅极,我们可以将其看作是晶体管的“控制开关”,通过改变栅极电压的大小和极性,我们可以调整晶体管的开关状态,从而实现信号的控制和放大。

横向晶体管有着多种应用,其中最为重要的莫过于在集成电路中的应用。

在集成电路中,横向晶体管扮演着信号切换、放大和传输的关键角色。

通过在集成电路上布置多个横向晶体管,我们可以实现复杂的逻辑运算和信号处理功能。

此外,横向晶体管还广泛应用于电源管理、放大器设计、通信系统、传感器等领域。

横向晶体管具有功耗低、速度快、噪声小、制造工艺成熟等优点,因此备受电子工程师和科学家的青睐。

接下来,让我们了解一下纵向晶体管。

纵向晶体管又称为BJT(双极型接面型晶体管),它是一种基于电流控制原理工作的晶体管。

纵向晶体管的主要特点是通过控制输入电流来控制晶体管的工作状态。

与横向晶体管不同,纵向晶体管的输入信号是电流而不是电压。

纵向晶体管具有放大和开关控制的功能,被广泛应用于模拟和数字电路中。

纵向晶体管也有着广泛的应用领域。

在数字电路中,纵向晶体管常用于逻辑门、触发器和存储器等电路的设计。

在模拟电路中,纵向晶体管被用于放大信号、构建滤波器和振荡器等电路。

此外,纵向晶体管还在功率放大器、调制解调器、音频放大器和无线通信系统等领域得到广泛应用。

纵向晶体管具有饱和状态响应快、输入输出电阻高等特点,在电路设计和信号处理中有着独特的优势。

模拟版图中的典型器件--青软

实现了BIPOLAR的快速、MOS的高密集度。

BIPOLAR

我们之前学习过PN结中,N型区域存在大量电子,P型区域存在大

量空穴。在PN结上加一正向电压,PN结导通。 如果我们在这个PN结的顶端再加一个N层,并在两个N层之间加 一个更高的电压,结果会是什么样子的呢?

BIPOLAR

三极管的三极

我们可以根据右图的电路来学习一 下,如果想让下面的PN结导通, 需要一个偏置电压(0.8V),电子 通过P区向左运动(从E到B)。

:利用两层金属和其之间CTM来实现 :利用两层甚至更多层金属层来实现,有时会利用Poly跟

metal来实现

Netlist中的调用: CC1 A B 2.4p $[MP]

LVS Commandfile 中的定义:

DEVICE C(MP) pmcapdev pgate psd

电容

电容的形状一般是方形最好,但有时根据需要, 在保证有效面积不变的情况下,形状可以随意调整 (主要是根据block的形状与摆放做相应调整,保证 block为矩形)。

电容与其相关的电路不易离太 远,在layout电容时,其面积要计 算清楚(有些是定义W/L)。 电容的摆放也要注意,尽量均

匀、对称。(如右图,如果c1与c2

电容的个数是1:8,摆放就按右 图)。

电容上面严禁走线,尤其是

信号线。

电容注意事项

在要求不是很 高的时候电容 的形状可以根 据block的摆 放调整。(注 意cap上面有 跑线)。

POLY电容

二、poly电容

画法:由poly1 和poly2组成, 需要用metal连 接出去,一般 poly2为正极。

POLY电容

二、poly电容

右图为poly电 容的剖面图

第七章双极型晶体管教材

3

7.2发射极电流集边效应

C B

E

E 电流集边

B

N 型隔离岛

发射极电流集边效应所造成的直接后果就是使得 发射极电流集中到边缘,从而减小了发射结的有 效面积。

4

发射极电流集边效应

18

圆型横向PNP管的版图

B

E

C N型隔离岛

圆形版图中所设计圆形都是采用多边形近似 产生的,多边形的边数越多,就越趋于圆形, 自然性能也就越好 。

19

圆型横向PNP管的版图

B

B

C

E E

C

C

N型隔离岛

N型隔离岛

与圆形发射区设计相比较,虽然基区宽度会稍微

增加,但是其版图更容易设计。与圆形发射区相

比,方形发射区的面积—周长比更低,因此,基

5

发射极电流集边效应

在设计NPN晶体管版图时,增加发射区面 积并不等效于发射极电流同比增长,应该 从增加发射极周长角度,也就是增大发射 区周长与面积的比值。

采用梳状版图结构,其每个齿条应又细又 长,考虑到发射极上的金属存在电阻,因 此齿条形的发射极也不能过长过细。

6

7.3 双极型晶体管的分类与版图

然可以做的很高,因此梳形版图能够很好的兼

顾大电流和高频率特性。

15

7.3.2 标准双极型工艺衬底PNP

C

管 E

B

N型外延层

P型衬底

集电区由P型衬底构成,基区为N型外延层,发射区 对应NPN管的基区扩散,其制作工艺与NPN管完全 兼容,且不需要多余掩膜层。衬底PNP管的电流放 大倍数与特征频率虽然没有NPN管大,但都高于横 向PNP管,且其耐压高,比较适合做电路的输出级。

问题总结-BJT

BJT知识总结问题1: 纵向横向晶体管区别1.集成NPN晶体管在双极型线性集成电路中NPN晶体管的用量最多,所以它的质量对电路性能的影响最大。

集成NPN晶体管的结构示意图如图2—69所示。

它是在P型衬底上扩散高掺杂的N+型掩埋层,生长N型外延层,扩散P型基区、N+型发射区和集电区而制成的。

其中N+型掩埋层的作用是为了减小集电区的体电阻。

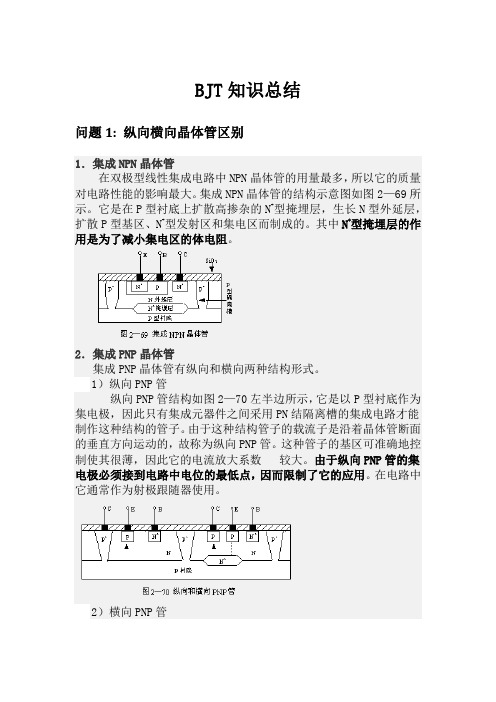

2.集成PNP晶体管集成PNP晶体管有纵向和横向两种结构形式。

1)纵向PNP管纵向PNP管结构如图2—70左半边所示,它是以P型衬底作为集电极,因此只有集成元器件之间采用PN结隔离槽的集成电路才能制作这种结构的管子。

由于这种结构管子的载流子是沿着晶体管断面的垂直方向运动的,故称为纵向PNP管。

这种管子的基区可准确地控制使其很薄,因此它的电流放大系数 较大。

由于纵向PNP管的集电极必须接到电路中电位的最低点,因而限制了它的应用。

在电路中它通常作为射极跟随器使用。

2)横向PNP管横向PNP管结构如图2—70右半边所示,这种结构管子的载流子是沿着晶体管断面的水平方向运动的,故称为横向PNP管。

由于受工艺限制,基区宽度不可能很小,所以它的 值相对较低,一般为十几倍到二、三十倍。

横向PNP管的优点是:发射结和集电结都有较高的反向击穿电压,所以它的发射结允许施加较高的反压;另外它在电路中的连接方式不受任何限制,所以比纵向PNP管有更多的用途。

它的缺点是结电容较大,特征频率f T较低,一般为几~几十兆赫。

问题2: 相近的尺寸下,为什么BJT的工作工作频率比CMOS 的高,噪声低,从器件的角度分析.BJT工作频率比CMOS高是因为fT更大:BJT的fT=2uVt/2piWB*WB,CMOS的fT=1.5u(Vgs-Vth)/2piL*L,在相同工艺条件下,WB可以远小于L,所以BJT的fT比CMOS大.BJT噪声特性比CMOS更好是因为:BJT电流流动主要在体内(基区在体内),而CMOS 的导电沟道在表面,所受散射更多,所以噪声更大.但是现在L可以做的越来越小了,工作频率达到或者超过BJT没有问题了。

亚10_nm工艺节点的晶体管器件结构gaa_解释说明以及概述

亚10 nm工艺节点的晶体管器件结构gaa 解释说明以及概述1. 引言:1.1 概述:亚10 nm工艺节点的晶体管器件结构GAA是当前半导体行业中的研究热点之一。

随着集成电路技术的不断发展和市场需求的增长,小型化、高性能和低功耗已成为下一代芯片设计的主要目标。

GAA结构作为一种新型晶体管器件结构,在实现这些目标方面具有巨大潜力。

本文将深入探讨亚10 nm工艺节点中GAA晶体管器件结构的原理、制备方法与流程,并详细分析关键要素的设计与优化。

同时,我们也会对亚10 nm工艺节点GAA技术的进展和挑战进行论述,并提出解决方案和未来发展方向。

1.2 文章结构:本文按以下方式组织并呈现对亚10 nm工艺节点GAA晶体管器件结构的分析和探讨:第二部分将介绍亚10 nm工艺节点以及GAA(Gate-All-Around)结构。

我们将对亚10 nm工艺节点进行概述,并详细介绍GAA结构的特点与应用前景。

第三部分将重点阐述GAA晶体管器件结构的工作原理,并介绍其制备方法与流程。

同时,我们还将深入探讨GAA结构中关键要素的设计与优化。

第四部分将分析亚10 nm工艺节点GAA技术的现状、趋势及面临的挑战和难题。

我们将进一步探讨解决方案,并展望未来发展方向。

最后,第五部分将对本文进行总结,强调亚10 nm工艺节点GAA的重要性和优势。

我们还会展望并分析GAA技术的发展前景,并以简洁明了的结束语结束全文。

1.3 目的:本文旨在全面解释和概述亚10 nm工艺节点下晶体管器件结构GAA。

通过对相关理论、制备方法和优化策略等方面的详细阐述,读者能够全面了解并掌握该领域的最新研究成果和应用前景。

同时,本文也将对出现的问题和挑战进行探讨与解决方案提供参考。

这篇文章为学者、研究人员和工程师们提供了一个充分了解亚10 nm工艺节点GAA晶体管器件结构相关知识的平台,并为他们在芯片设计领域取得更好成果提供了重要参考。

2. 亚10nm工艺节点的晶体管器件结构gaa2.1 亚10nm工艺节点介绍亚10纳米(nm)工艺节点代表着半导体行业在微缩技术领域取得的重要突破。

BCD工艺综述

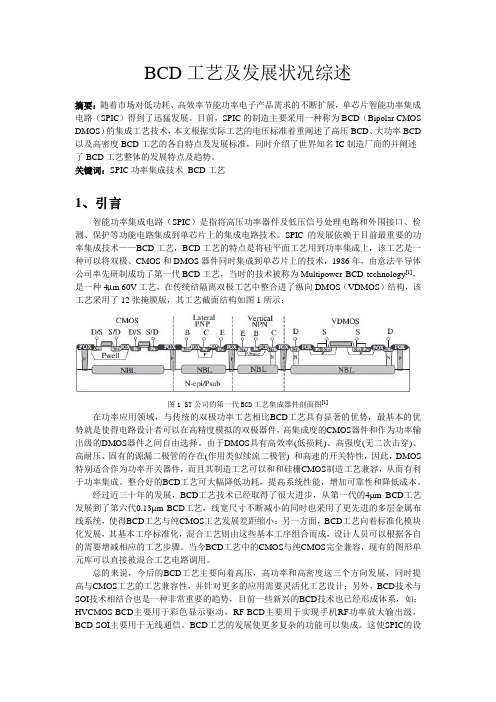

BCD工艺及发展状况综述摘要:随着市场对低功耗、高效率节能功率电子产品需求的不断扩展,单芯片智能功率集成电路(SPIC)得到了迅猛发展。

目前,SPIC的制造主要采用一种称为BCD(Bipolar CMOS DMOS)的集成工艺技术,本文根据实际工艺的电压标准着重阐述了高压BCD、大功率BCD 以及高密度BCD工艺的各自特点及发展标准,同时介绍了世界知名IC制造厂商的并阐述了BCD工艺整体的发展特点及趋势。

关键词:SPIC功率集成技术BCD工艺1、引言智能功率集成电路(SPIC)是指将高压功率器件及低压信号处理电路和外围接口、检测、保护等功能电路集成到单芯片上的集成电路技术。

SPIC的发展依赖于目前最重要的功率集成技术——BCD工艺,BCD工艺的特点是将硅平面工艺用到功率集成上,该工艺是一种可以将双极、CMOS和DMOS器件同时集成到单芯片上的技术,1986年,由意法半导体公司率先研制成功了第一代BCD工艺,当时的技术被称为Multipower BCD technology[1],是一种4μm 60V工艺,在传统结隔离双极工艺中整合进了纵向DMOS(VDMOS)结构,该工艺采用了12张掩膜版,其工艺截面结构如图1所示:图1 ST公司的第一代BCD工艺集成器件剖面图[1]在功率应用领域,与传统的双极功率工艺相比BCD工艺具有显著的优势,最基本的优势就是使得电路设计者可以在高精度模拟的双极器件,高集成度的CMOS器件和作为功率输出级的DMOS器件之间自由选择。

由于DMOS具有高效率(低损耗)、高强度(无二次击穿)、高耐压、固有的源漏二极管的存在(作用类似续流二极管) 和高速的开关特性,因此,DMOS 特别适合作为功率开关器件,而且其制造工艺可以和和硅栅CMOS制造工艺兼容,从而有利于功率集成。

整合好的BCD工艺可大幅降低功耗,提高系统性能,增加可靠性和降低成本。

经过近三十年的发展,BCD工艺技术已经取得了很大进步,从第一代的4μm BCD工艺发展到了第六代0.13μm BCD工艺,线宽尺寸不断减小的同时也采用了更先进的多层金属布线系统,使得BCD工艺与纯CMOS工艺发展差距缩小;另一方面,BCD工艺向着标准化模块化发展,其基本工序标准化,混合工艺则由这些基本工序组合而成,设计人员可以根据各自的需要增减相应的工艺步骤。

IC课件第八章3

VOH=VCC - IOHR2 =VCC-NOHIIHR2

NOH= (VCC -VOH)/IIHR2

IIH较小, NOH一般可以

达几十。

20

I I N I 在式I开中C 2态的S:2为是2SI保T2B2证的2 V饱O和L=深VC度ES2,即T2处于饱和态,则

因为 C2R2OL IL

双极型逻辑门电{路 TTL (Transistor-Transistor Logic) ECL(Emitter Coupled Logic)

I2L (Integred-Injection Logic) 15

8-5 TTL门电路的工作原理和基本参数

一、简易TTL门的工作原理

1、“关态”: 2、“开态”:

减小乃至消除的方法: NPN集电区掺金:少子寿命 ,βpnp 埋层:基区宽度 ,基区N+掺杂 ,注入效率 , βpnp

10

② 横向寄生效应 如一个n型岛内有两个P区,会形成横向PNP结构。 I. 可以借此制作PNP管 II. 如果不希望出现PNP效应,可拉大间距,或者n区接

高电位。 在多发射结NPN管中,会形成横向NPN结构,当 一个发射结接高电平,其余接地时,该输入端电 流会过大。

14

双极型逻辑门电路

双极型门电路依照其内部晶体管的工作状态,可分为饱 和型和非饱和型。 饱和型门电路其中的晶体管工作在截至状态,或工作在 饱和状态。由于饱和时的集电极电流基本不受晶体管参 数制造容差的影响,特别是值容差的影响,因此最先得 以实现,缺点主要是由于饱和引起的少子存储效应,使 电路的延迟时间较长。 TTL们及I2L门系列,都是饱和门电路的电表。 非饱和门电路的主要代表是ECL门电路,它内部的晶体 管则是工作在放大和截止状态,因而速度较快,但功耗 较大,多用于高速大型计算机中。

集成电路中的晶体管及寄生效应

25

六种集成二极管的特性比较

BC短接二极管,没有寄生PN P效应, 。

26

集成齐纳二极管和次表面齐纳管

IC中,齐纳二极管一般是反向工作BC短接二极管。 次表面齐纳二极管设 法把击穿由表面引入 体内。 扩散法: 在N+发射区 内加一道P+扩散. 离子注入: P型基区扩 散N+发射区扩散后,增 加一次硼离子注入.

30

2.7 MOS集成电路中的有源寄生效应

1 场区寄生M当互连铝线跨过场氧区B、C两个扩散区时,如 果互连铝线电位足够高,可能使场区表面反型,形成寄生 沟道,使本不应连通的有源区导通,造成工作电流泄漏, 使器件电路性能变差,乃至失效。

31

场区寄生MOSFET

图2.26

10

NPN管工作于截止区 VBC(npn)<0 VEB(pnp)<0 VBE(npn)<0,VCS (npn)>0 VBC(pnp)>0

寄生PNP管截止

NPN管工作于放大区

VBE(npn)>0

VBC(npn)<0 VEB(pnp)<0 VCS (npn)>0 VBC(pnp)>0

15

2.3 集成双极晶体管的无源寄生效应

CCS1 CBE

CCS2

CCS2

2-3

由图2-3可归纳出集成NPN管的无源寄生效应包括: 寄生电阻 res(1~3Ω),rcs (加埋层,磷穿透工艺),rb 寄生电容: CD 扩散电容, CJ 势垒电容(CBE,CBC, CCS), Cpad 焊盘电容。

集成电路中的无源寄生将影响集成电路的瞬态特性。

8

IE

IB

I1 I2 I3 I S’

集成电路中晶体管及其寄生效应

rE ,c

Rc SE

2.3.1 集成NPN晶体管中的寄生电阻

2. 集电极串联电阻rCS rC SrC1rC2rC3

2.3.1 集成NPN晶体管中的寄生电阻

2. 集电极串联电阻rCS

R1= epi*lch*cwc

R5=

epi*

hb le*we

增加n+埋 层、穿透 磷扩散、

EC B

2.4.1 横向PNP管

二. 横向PNP管的电学特性

3. 击穿电压低,由c-e穿通电压 决定,突变结近似: VPT=qNBWbL2/2osi

4. 特征频率低 (受WbL和寄生PNP影响)

5.临界电流ICr小。

EC B

2.4.1 横向PNP管

三. 横向PNP管常用图形

1.单个横向PNP管

结构简单,面积小

BC P N+

P+ N–-epi

P+

P-Sub

2.5.1 一般集成二极管

7.单独SC结

VF=VSCF BV=BVSC Cj = Cs Cp= 0 无寄生PNP管

C N+ P+ N–-epi P+

P-Sub

从表2.2中可以看到:

(1)BC短接二极管,因为没有寄生PNP效应,且 存储时间最短,正向压降低,故一般DTL电路的 输入端的门二极管都采用这种接法;

△V=VBE-VBC

B(P)

PNP

S(P)

EB

P+

P N+

N–-epi

P-Sub

NPN

C(N)

C

N+

P+

2.3 集成双极晶体管的无源寄生效应

MOSFET结构介绍

图10:体二极管正向特性

9.体二极管反向恢复

当二极管从导通状态切换为关断状态时, MOSFET的寄生体二极管产生反向恢复,因 为存储的少子电荷必须被清除,在器件内部, 或者通过负电流主动的清除,或者通过复合 被动的清除。

在数据表中,有三个参数列出来表示二极管 的反向恢复。

trr: 体二极管反向恢复时间。 IRM: 体二极管反向峰值电流。 Qrr: 体二极管反向恢复电荷,就是二极管电

图6: MOSFET寄生电容

MOSFET的电容是非线性的,是直流偏置电压的函数。图7示出了电容如何随 VDS电压增加而变化。所有的MOSFET的寄生电容来源于不依赖于偏置的氧化 物电容和依赖于偏置的硅耗尽层电容的组合。当电压增加时,和VDS相关电容 的减小来源于耗尽层电容减小,耗尽层区域扩大。

图7b示出了当VGS电压增加大于阈值电压,VDS电压值低,MOSFET栅极电容 也增加,因为MOS沟道电子反形层形成,在沟漕底部形成电子聚集层。这也 是为什么一旦电压超过QGD阶级,栅极电荷特性曲线的斜率增加的原因。

图4 Rds on对栅极偏置和温度

阈值电压

阈值电压VGS(TH)定义为最小的栅极偏置电压,此时,在源极和漏极间形成导 通的沟道。对于功率MOSFET,通道在250uA的漏源极电流时测量。栅极氧 化层厚度和沟道掺杂集中度用来控制阈值电压。10-15V的驱动电压,其典型 值设计为2-4V。使用CMOS技术缩减,功率MOSFET的栅极驱动电压可以降 到的2.5-4.5V。因此,这些应用需要更低的阈值电压1-2V。阈值电压具有负 的温度系数,温度增加,阈值电压降低。

下一步,测试器件的栅极继续充电到最终的值,漏源极电压变为RDSON x ID。 栅源极电压自由的上升,上升的斜率由栅极的充电电流和CISS决定,在VGS>VTH 时,CISS更高,图7b所示,导致在栅极电荷曲线上,更低的斜率,直到栅源 极电压达到最大值。这个栅极的电荷是所有栅极电荷QG。

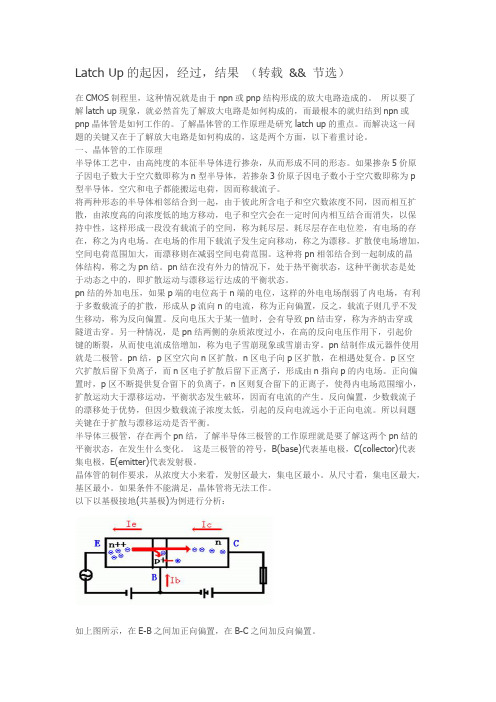

LatchUp的起因,经过,结果(转载节选)

Latch Up的起因,经过,结果(转载&& 节选)在CMOS制程里,这种情况就是由于npn或pnp结构形成的放大电路造成的。

所以要了解latch up现象,就必然首先了解放大电路是如何构成的,而最根本的就归结到npn或pnp晶体管是如何工作的。

了解晶体管的工作原理是研究latch up的重点。

而解决这一问题的关键又在于了解放大电路是如何构成的,这是两个方面,以下着重讨论。

一、晶体管的工作原理半导体工艺中,由高纯度的本征半导体进行掺杂,从而形成不同的形态。

如果掺杂5价原子因电子数大于空穴数即称为n型半导体,若掺杂3价原子因电子数小于空穴数即称为p 型半导体。

空穴和电子都能搬运电荷,因而称载流子。

将两种形态的半导体相邻结合到一起,由于彼此所含电子和空穴数浓度不同,因而相互扩散,由浓度高的向浓度低的地方移动,电子和空穴会在一定时间内相互结合而消失,以保持中性,这样形成一段没有载流子的空间,称为耗尽层。

耗尽层存在电位差,有电场的存在,称之为内电场。

在电场的作用下载流子发生定向移动,称之为漂移。

扩散使电场增加,空间电荷范围加大,而漂移则在减弱空间电荷范围。

这种将pn相邻结合到一起制成的晶体结构,称之为pn结。

pn结在没有外力的情况下,处于热平衡状态,这种平衡状态是处于动态之中的,即扩散运动与漂移运行达成的平衡状态。

pn结的外加电压,如果p端的电位高于n端的电位,这样的外电电场削弱了内电场,有利于多数载流子的扩散,形成从p流向n的电流,称为正向偏置,反之,载流子则几乎不发生移动,称为反向偏置。

反向电压大于某一值时,会有导致pn结击穿,称为齐纳击穿或隧道击穿。

另一种情况,是pn结两侧的杂质浓度过小,在高的反向电压作用下,引起价键的断裂,从而使电流成倍增加,称为电子雪崩现象或雪崩击穿。

pn结制作成元器件使用就是二极管。

pn结,p区空穴向n区扩散,n区电子向p区扩散,在相遇处复合。

p区空穴扩散后留下负离子,而n区电子扩散后留下正离子,形成由n指向p的内电场。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.集成NPN晶体管

在双极型线性集成电路中NPN晶体管的用量最多,所以它的质量对电路性能的影响最大。

集成NPN晶体管的结构示意图如图2—69所示。

它是在P 型衬底上扩散高掺杂的N+型掩埋层,生长N型外延层,扩散P型基区、N+型发射区和集电区而制成的。

其中N+型掩埋层的作用是为了减小集电区的体电阻。

2.集成PNP晶体管

集成PNP晶体管有纵向和横向两种结构形式。

1)纵向PNP管

纵向PNP管结构如图2—70左半边所示,它是以P型衬底作为集电极,因此只有集成元器件之间采用PN结隔离槽的集成电路才能制作这种结构的管子。

由于这种结构管子的载流子是沿着晶体管断面的垂直方向运动的,故称为纵向PNP管。

这种管子的基区可准确地控制使其很薄,因此它的电流放大系数β较大。

由于纵向PNP管的集电极必须接到电路中电位的最低点,因而限制了它的应用。

在电路中它通常作为射极跟随器使用。

2)横向PNP管

横向PNP管结构如图2—70右半边所示,这种结构管子的载流子是沿着晶体管断面的水平方向运动的,故称为横向PNP管。

由于受工艺限制,基区宽度不可能很小,所以它的β值相对较低,一般为十几倍到二、三十倍。

横向PNP管的优点是:发射结和集电结都有较高的反向击穿电压,所以它的发射结允许施加较高的反压;另外它在电路中的连接方式不受任何限制,所以比纵向PNP管有更多的用途。

它的缺点是结电容较大,特征频率f T较低,一般为几~几十兆赫。