FPGA可编程逻辑器件芯片XCZU28DR-2FFVG1517E中文规格书

FPGA可编程逻辑器件芯片XCZU27DR-L2FFVG1517E中文规格书

SSTLSSTL18_I is defined by the JEDEC standard JESD8-15, and is used for DDR2 SDRAM interfaces.For some topologies (such as short, point-to-point interfaces), the class-I driver can result in reduced overshoot and better signal integrity.HSTLThe high-speed transceiver logic (HSTL) HSTL_I_18 (1.8V) standard is a general-purpose high-speed bus standard as defined by the JEDEC standard JESD8-6.Table 109: Allowed Attributes for SSTL18_I and HSTL_I_18 I/O PrimitivesAttributesIBUF/IBUFE3OBUF/OBUFT IOBUF/IOBUFE3Allowed Values Default Allowed Value Default Allowed Values Default IOSTANDARDSSTL18_I, HSTL_I_18SSTL18_I, HSTL_I_18SSTL18_I, HSTL_I_18SLEWN/A FAST, SLOW SLOW FAST, SLOW SLOW ODT RTT_48,RTT_NONE RTT_NONE N/A RTT_48,RTT_NONERTT_NONE UNDEFINED Default IOSTANDARDWhen an IOSTANDARD is not defined by the user, the default assignment for the IOSTANDARD defaults to UNDEFINED. For a Versal ACAP design to complete implementation, a non-default IOSTANDARD must be defined with one of the valid I/O standards described in this section. The UNDEFINED standard acts as a placeholder to allow a design to complete the early stages or implementation.Single-Ended Input Buffer PrimitivesFigure 64: Single-Ended Input Buffer PrimitivesI OIBUFInput fromDevice Pad IBUF_INTERMDISABLEINTERMDISABLEOI Input fromDevice Pad IBUFDISABLEX21628-100720Chapter 7: HD IOB ResourcesAM010 (v1.2) April 2, 2021Versal ACAP SelectIO Resources Architecture ManualTable 110: IBUF and IBUF_INTERMDISABLE AttributesAttributeValues Description IOSTANDARDSee HD IOB Supported Standards Assigns an I/O standard to the E_IBUFDISABLE FALSE IBUFDISABLE is not supported in HD IOB and must be set to FALSE.(IBUF_INTERMDISABLE only)Table 111: IBUF and IBUF_INTERMDISABLE PortsPortI/O Description OOutput Buffer output representing the input path to the device.IInput Input port connection. Connect directly to top-level port in the design.IBUFDISABLE Input The IBUFDISABLE pin can disable the input buffer and force the O output to the internal logic to a logic High when the IBUFDISABLE signal is asserted High. (IBUF_INTERMDISABLE only)INTERMDISABLE InputIBUFDISABLE is not supported in HD IOB. (IBUF_INTERMDISABLE only)Single-Ended Bidirectional Buffer PrimitivesFigure 65: Single-Ended Bidirectional Buffer PrimitivesIOBUF_INTERMDISABLE IOIOBUFT I O IO X21629-092318Table 112: IOBUF, IOBUF_INTERMDISABLE AttributesAttributeValues Description DRIVE4, 8, 12Specifies the drive strength of the output.SLEWSLOW, FAST Specifies the slew rate of the output.IOSTANDARDSee HD IOB Supported Standards Assigns an I/O standard to the E_IBUFDISABLE FALSE IBUFDISABLE is not supported in HD IOB and must be set to FALSE.(IOBUF_INTERMDISABLE only)Chapter 7: HD IOB ResourcesAM010 (v1.2) April 2, 2021Versal ACAP SelectIO Resources Architecture Manual。

FPGA可编程逻辑器件芯片XC2V500-4FF1517C中文规格书

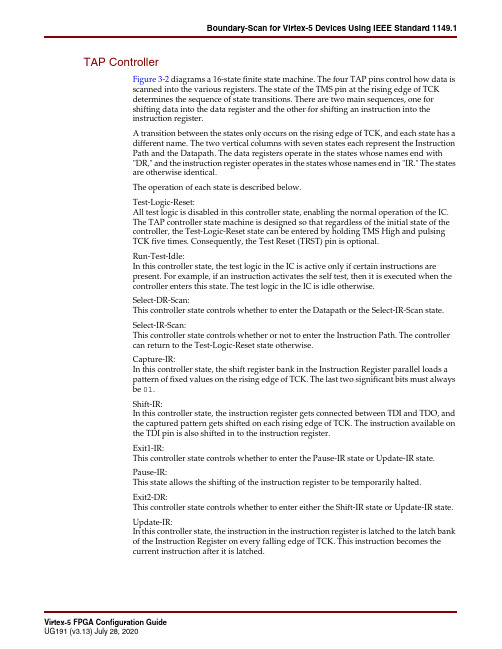

Boundary-Scan for Virtex-5 Devices Using IEEE Standard 1149.1TAP ControllerFigure3-2 diagrams a 16-state finite state machine. The four TAP pins control how data isscanned into the various registers. The state of the TMS pin at the rising edge of TCKdetermines the sequence of state transitions. There are two main sequences, one forshifting data into the data register and the other for shifting an instruction into theinstruction register.A transition between the states only occurs on the rising edge of TCK, and each state has adifferent name. The two vertical columns with seven states each represent the InstructionPath and the Datapath. The data registers operate in the states whose names end with"DR," and the instruction register operates in the states whose names end in "IR." The statesare otherwise identical.The operation of each state is described below.Test-Logic-Reset:All test logic is disabled in this controller state, enabling the normal operation of the IC.The TAP controller state machine is designed so that regardless of the initial state of thecontroller, the Test-Logic-Reset state can be entered by holding TMS High and pulsingTCK five times. Consequently, the Test Reset (TRST) pin is optional.Run-Test-Idle:In this controller state, the test logic in the IC is active only if certain instructions arepresent. For example, if an instruction activates the self test, then it is executed when thecontroller enters this state. The test logic in the IC is idle otherwise.Select-DR-Scan:This controller state controls whether to enter the Datapath or the Select-IR-Scan state.Select-IR-Scan:This controller state controls whether or not to enter the Instruction Path. The controllercan return to the Test-Logic-Reset state otherwise.Capture-IR:In this controller state, the shift register bank in the Instruction Register parallel loads apattern of fixed values on the rising edge of TCK. The last two significant bits must alwaysbe 01.Shift-IR:In this controller state, the instruction register gets connected between TDI and TDO, andthe captured pattern gets shifted on each rising edge of TCK. The instruction available onthe TDI pin is also shifted in to the instruction register.Exit1-IR:This controller state controls whether to enter the Pause-IR state or Update-IR state.Pause-IR:This state allows the shifting of the instruction register to be temporarily halted.Exit2-DR:This controller state controls whether to enter either the Shift-IR state or Update-IR state.Update-IR:In this controller state, the instruction in the instruction register is latched to the latch bankof the Instruction Register on every falling edge of TCK. This instruction becomes thecurrent instruction after it is latched.Capture-DR:In this controller state, the data is parallel-loaded into the data registers selected by the current instruction on the rising edge of TCK.Shift-Dr, Exit1-DR, Pause-DR, Exit2-DR, and Update-DR:These controller states are similar to the Shift-IR, Exit1-IR, Pause-IR, Exit2-IR, and Update-IR states in the Instruction path.Virtex-5 devices support the mandatory IEEE 1149.1 commands, as well as several Xilinx vendor-specific commands. The EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS,IDCODE, USERCODE, and HIGHZ instructions are all included. The TAP also supports internal user-defined registers (USER1, USER2, USER3, and USER4) and configuration/readback of the device.The Virtex-5 Boundary-Scan operations are independent of mode selection. TheBoundary-Scan mode in Virtex-5 devices overrides other mode selections. For this reason, Boundary-Scan instructions using the Boundary-Scan register (SAMPLE/PRELOAD, INTEST, and EXTEST) must not be performed during configuration. All instructions except the user-defined instructions are available before a Virtex-5 device is configured. After configuration, all instructions are available.JSTART and JSHUTDOWN are instructions specific to the Virtex-5 architecture andconfiguration flow. In Virtex-5 devices, the TAP controller is not reset by the PROGRAM_B pin and can only be reset by bringing the controller to the TLR state. The TAP controller is reset on power up.For details on the standard Boundary-Scan instructions EXTEST, INTEST, and BYPASS, refer to the IEEE Standard.Figure 3-2:Boundary-Scan TAP Controller1UG191_c3_02_050406NOTE: The value shown adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.Chapter 5:Dynamic Reconfiguration Port (DRP)Configuration RegistersWarm Boot Start Address Register (WBSTAR)The name of each bit position in the WBSTAR is given in Figure 6-6 and described in Table 6-12.DescriptionReservedPERSIST_DEASSERT_AT_DESYNCHReserved ReservedRBCRC_NO_PINRBCRC_EN ReservedBPI_1ST_READ_CYCLESBPI_PAGE_SIZEBit Index 313029282726252423222120191817161514131211109876543210ValueFigure 6-5:Configuration Options Register 1Table 6-11:Configuration Options Register 1 Description NameBit IndexDescriptionPERSIST_DEASSERT_AT_DESYNCH 17Enables deassertion of PERSIST with the DESYNCH commandRBCRC_NO_PIN 9Disables INIT_B as read back CRC error status output pinRBCRC_EN8Continuous readback CRC enable BPI_1ST_READ_CYCLES[3:2]First byte read timing:00: 1 C C LK 01: 2 C C LKs 10: 3 C C LKs 11: 4 C C LKs BPI_PAGE_SIZE [1:0]Flash memory page size:00: 1byte/word 01: 4 bytes/words 10: 8 bytes/words 11: Reserved。

FPGA可编程逻辑器件芯片XCZU7EV-2FFVF1517I中文规格书

CoolRunner-II Serial Peripheral Interface MasterThe receive full flag (RCV_FULL) is set whenever data is loaded from the SPI receive shiftregister to the SPIRR. This signal is clocked from the system clock and is reset whenever theμC reads data from the SPIRR.SCK Clock LogicThis process generates the SCK output based on the CLKDIV, CPHA, and CPOL settings inthe SPI control register. The clock frequency of the SCK signal is determined by dividing downthe input clock based on the entries in the control register. The signal, SCK_INT is the internalSCK used to clock serial data out of the device and is continually generated. The SPI Controlstate machine is synchronized to this internal signal. The signal SCK_1 represents SCK whenCPHA = 1 and the signal SCK_0 represents SCK when CPHA = 0. The SPI control statemachine generates the masks for these clocks (CLK0_MASK, CLK1_MASK) so that the outputSCK has the correct phase relationship with the data and is held in its inactive state when thereis no data to be transferred. A representation of the logic required to generate the SCK signaloutput to the SPI bus is shown in Figure8.Figure 8: SCK Clock Generation LogicSPI Shift RegistersSPI Transmit Shift RegisterThe SPI transmit shift register is an 8-bit loadable shift register containing SPI data. This shiftregister is loaded from the SPI Transmit Register (SPITR) via a load signal generated by theSPI Control state machine and is clocked by the rising edge of SCK_INT. The data shifting outis the MOSI data. Note that in Figure8, SCK_OUT is one SYS_CLK delay from SCK_INT.Therefore, it is necessary to delay the data being shifted out from the SPI transmit shift registerby one SYS_CLK as well so that the relationship between MOSI and SCK_OUT is maintained. XAPP386 (v1.0) December 12, 2002White Paper: CoolRunner-II CPLDs in Cell Phone Handsets/Terminals But what about new applications that are not in this group? There are applications yet to come that we can envision, but whose exact specifications we cannot wholly anticipate. Designing for their arrival is sometimes called “future proofing.”It is true that some applications are better served by microprocessor code dropped into on board EPROM, but that can only happen as long as the processor bandwidth is available for the application. If this cannot be done, either more processors or additional silicon needs to be added. Either way, the application will need to interface into the phone bus network, and that will require programmable logic, very low power programmable logic.MediPhone—A Speculative Example To drive home some of these ideas, consider an idea for a product that probably does not exist today, but easily could in the near future. It will be marketed under the name “MediPhone” and will target segments of the population that require quick medical support. This would include the growing population of elderly citizens (frequently with enough money to buy these) as well as handicapped people needing close monitoring. See Figure4 for an “artist” conception of this futuristic phone.MediPhone works like this:1. A heart attack (or other medical emergency occurs)2.The victim or friend dials Emergency (911 in the U.S.)3.Personnel receiving the call at a medical facility recognize the phone is“MediPhone” equipped and extract the geographic location of the emergency using GPS4.The medic directs the friend to place the cell phone on the victim’s face5. A video camera scans the Iris for dilation to determine shock level6.The friend is directed to attach small electrodes to the forehead/ear and chest ofthe victim, where pulse is taken and EEG/EKG measurements are driven into the Internet. Everything is attached to the phone.Figure 4:MediPhone Block DiagramWP198 (v1.1) July 4, 2005。

FPGA可编程逻辑器件芯片XCZU11EG-2FFVF1517E中文规格书

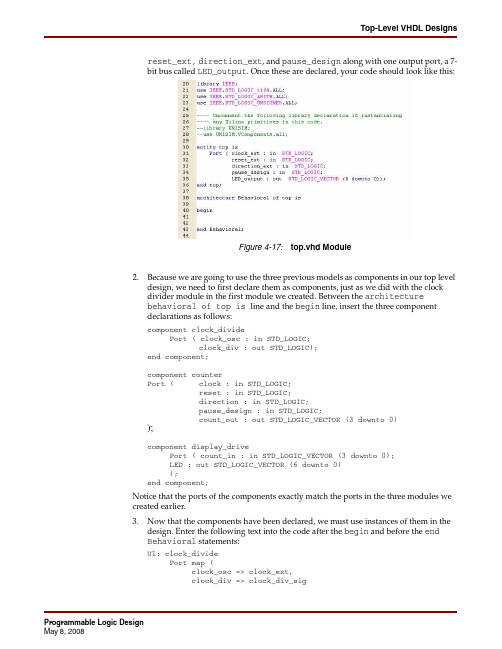

Programmable Logic Design May 8, 2008Top-Level VHDL Designs reset_ext,direction_ext, and pause_design along with one output port, a 7-bit bus calledLED_output. Once these are declared, your code should look like this:Figure 4-17:top.vhd Module2.Because we are going to use the three previous models as components in our top leveldesign, we need to first declare them as components, just as we did with the clock divider module in the first module we created. Between the architecturebehavioral of top is line and the begin line, insert the three componentdeclarations as follows:component clock_dividePort ( clock_osc : in STD_LOGIC;clock_div : out STD_LOGIC);end component;component counterPort ( clock : in STD_LOGIC;reset : in STD_LOGIC;direction : in STD_LOGIC;pause_design : in STD_LOGIC;count_out : out STD_LOGIC_VECTOR (3 downto 0) );component display_drivePort ( count_in : in STD_LOGIC_VECTOR (3 downto 0);LED : out STD_LOGIC_VECTOR (6 downto 0));end component;Notice that the ports of the components exactly match the ports in the three modules we created earlier.3.Now that the components have been declared, we must use instances of them in thedesign. Enter the following text into the code after the begin and before the end Behavioral statements:U1: clock_dividePort map (clock_osc => clock_ext,clock_div => clock_div_sigProgrammable Logic Design May 8, 2008Complex Programmable Logic Devices (CPLDs)provide the ability to program the devices time and time again, electrically programmingand erasing the device. Gone are the days of erasing for more than 20 minutes under an UVeraser.Complex Programmable Logic Devices (CPLDs)Complex programmable logic devices (CPLDs) extend the density of SPLDs. The conceptis to have a few PLD blocks or macrocells on a single device with a general-purposeinterconnect in-between. Simple logic paths can be implemented within a single block.More sophisticated logic requires multiple blocks and uses the general-purposeinterconnect in-between to make these connections. CPLDs feature:•Central global interconnect•Simple, deterministic timing•Easily routed•PLD tools add only interconnect•Wide, fast complex gatingFigure 1-3:CPLD ArchitectureCPLDs are great at handling wide and complex gating at blistering speeds – 5nanoseconds, for example, which is equivalent to 200 MHz. The timing model for CPLDsis easy to calculate so before starting your design you can calculate your input-to-outputspeeds.Why Use a CPLD?CPLDs enable ease of design, lower development costs, more product revenue for yourmoney, and the opportunity to speed your products to market.•Ease of Design: CPLDs offer the simplest way to implement a design. Once a designhas been described, by schematic and/or HDL entry, you simply use CPLDdevelopment tools to optimize, fit, and simulate the design. The development toolscreate a file that is used to customize (that is, program) a standard off-the-shelf CPLDwith the desired functionality. This provides an instant hardware prototype andallows the debugging process to begin. If modifications are needed, you can enter。

FPGA可编程逻辑器件芯片XCVU095-2FFVC1517E中文规格书

Power-On and ResetPrior to displaying the main menu, the system controller initializes the adjustable voltage (VADJ) on the FPGA FMC expansion port interface within the available choices of 1.8V, 1.5V, 1.2V, and 0.0V.•If no cards are attached to the FMC ports, the VADJ voltage is set to 1.8V.•When one FMC card is attached, its I2C EEPROM is read to find a VADJ voltage supported by both the VCU108 board and the FMC module within the available choices of 1.8V, 1.5V, 1.2V, and 0.0V.•When two FMC cards are attached with differing VADJ requirements, VADJ is set to the lowest value compatible with the VCU108 board and the FMC modules, within the available choices of 1.8V, 1.5V, 1.2V, and 0.0V.The VADJ voltage is set and then the main menu is displayed. The VADJ settings can be viewed by scrolling back through the terminal window output.The VADJ voltage can be set manually with the FMC menu.VCU108 On-board ClocksThe VCU108 board hosts two programmable clocks. One is the user programmable system clock (Silicon Labs Si570) that operates in the frequency range between 10MHz and810MHz. The second VCU108 programmable clock source is the Silicon Labs Si5328B, which is typically used as a jitter attenuator for a recovered clock from a serial transceiver. However, the Si5328B can also be used as an independent clock source with a frequency range of 8kHz to 808MHz. In addition to the programmable clock sources, the UltraScale FPGA evaluation boards provide a 300MHz fixed frequency system clock.Clock MenuThe clock menu is used to set the frequency of the onboard programmable clock sources. At VCU108 board power-up, the onboard programmable clock sources generate their factory default frequencies until the system controller has booted and checked the onboard EEPROM to determine if a frequency value has previously been saved for either onboard clock source. Previously saved values are restored to the onboard clock sources, which then output these frequencies until they are reprogrammed to a different value, or the VCU108 board is turned off.PMBus MenuThe PMBus is an I2C bus that is used to read the voltage settings of the nine VCU108 power rails controlled by the Maxim power system. Through the PMBus menu these power rails can be read once or scanned continuously until stopped by a key press. Table C-1 lists the voltage rails accessible through the system controller's interface to the Maxim PMBus.PMBus Menu OptionsVCU108 System Controller -PMBus Menu-1.Get PMBus Voltages2.Continuous Scan PMBUS Voltages3.Get VCCINT Voltage4.Get VCC1V8 Voltage5.Get VADJ1V8 Voltage6.Get VCC1V2 Voltage7.Get MGTAVCC Voltage8.Get MGTAVTT Voltage9.Get UTIL3V3 Voltage A.Get UTIL1V35 Voltage 0.Return to Main Menu Select an optionOption 1: Get PMBus VoltagesVCCINT, VCCBRAM = 0.950V VCCAUX, VCC1V8= 1.800V VCCBRAM, VCCINT = 0.950V VCC1V8, VCCAUX = 1.800VVADJ1V8= 1.800VTable C-1:Maxim Power Supply RailMaxim Power Supply Rail I2C AddressNominal VoltageVCCINT 0x0A 0.95V VCC1V80x11 1.80V VADJ_1V80x12 1.80V VCC1V20x14 1.20V MGTAVCC 0x72 1.00V MGTAVTT 0x73 1.20V UTIL_3V30x1B 3.30V UTIL_1V350x1A1.35VSYSMON MenuThe Virtex® UltraScale™ FPGA on the VCU108 contains a 200KSPS analog-to-digital converter known as the system monitor (SYSMON), which is described in UltraScale Architecture System Monitor User Guide (UG580) [Ref31]. Measurements made internal to the UltraScale FPGA are accomplished by the SYSMON block for VCCINT, VCCBRAM, and VCCAUX. In conjunction with an onboard analog multiplexer (Analog Devices ADG707) and inline Kelvin sense resistors, the UltraScale SYSMON ADC measures the current on the eight rails listed in Table C-2.Table C-2:SYSMON Monitored Power RailSYSMON Monitored Power Rail Nominal Voltage Maximum Rail CurrentVCCINT/VCCBRAM0.95V60AVCC1V8/VCCAUX 1.80V10AVADJ_1V8 1.80V10AVCC1V2 1.20V10AMGTAVCC 1.00V17AMGTAVTT 1.20V17A。

FPGA可编程逻辑器件芯片XC2V80-5FF1517I中文规格书

Configuration Data File FormatsXilinx design tools can generate configuration data files in a number of different formats, as described in Table 1-3. BitGen converts the post-PAR NCD file into a configuration file or a bitstream. PROMGen, the PROM file generator, converts one or more bitstream files into a PROM file. PROM files can be generated in a number of different file formats and does not need to be used with a PROM. They can be stored anywhere and delivered by any means.Bitstream OverviewThe Virtex-5 bitstream contains commands to the FPGA configuration logic as well as configuration data. Table 1-4 gives a typical bitstream length for each of the Virtex-5 devices.Table 1-3:Xilinx Configuration File FormatsFileExtension Bit Swapping (1)Xilinx SoftwareTool (2)DescriptionBITNot Bit Swapped BitGen (generated bydefault)Binary configuration data file containing header informationthat does not need to be downloaded to the FPGA. Used toprogram devices from iMPACT with a programming cable. RBTNot Bit Swapped BitGen (generated if -b option is set)ASCII equivalent of the BIT file containing a text header and ASCII 1s and 0s. (Eight bits per configuration bit.)BIN∙BitGen: Not Bit Swapped ∙PROMGen:Bit Swapped BitGen (generated if -g binary:yes option is set) or PROMGen Binary configuration data file with no header information. Similar to BIT file. Can be used for custom configuration solutions (for example, microprocessors), or in some cases to program third-party PROMs.MCS EXO TEK Bit Swapped PROMGen or iMPACT ASCII PROM file formats containing address and checksum information in addition to configuration data. Used mainly for device programmers and iMPACT.HEXDetermined by UserPROMGen or iMPACTASCII PROM file format containing only configuration data. Used mainly in custom configuration solutions.Notes:1.Bit swapping is discussed in the “Bit Swapping” section.2.For complete BitGen and PROMGen syntax, refer to the Development System Reference Guide .Table 1-4:Virtex-5 FPGA Bitstream LengthDevice Total Number of Configuration Bits (1)XC5VLX308,374,016XC5VLX5012,556,672XC5VLX8521,845,632XC5VLX11029,124,608XC5VLX15541,048,064XC5VLX22053,139,456XC5VLX33079,704,8324.The PROM in this diagram represents one or more Xilinx PROMs. Multiple PROMscan be cascaded to increase the overall configuration storage capacity.5.The BIT file must be reformatted into a PROM file before it can be stored on thePROM. Refer to the “Generating PROM Files” section.6.On some Xilinx PROMs, the reset polarity is programmable. RESET should beconfigured as active Low when using this setup.7.For ganged serial configuration, all devices must be identical (same IDCODE) andmust be configured with the same bitstream.8.The CCLK net requires Thevenin parallel termination. See “Board Layout forConfiguration Clock (CCLK),” page73.9.Ganged serial configuration is specific to the Platform Flash XCFS and XCFP PROMonly.10.Fallback and Multiboot are not supported in ganged serial configuration.There are a number of important considerations for ganged serial configuration:∙Startup Sequencing (GTS)GTS should be released before DONE or during the same cycle as DONE to ensure all devices are operational when all DONE pins have been released.∙Disable the Active DONE Driver for All DevicesFor ganged serial configuration, the active DONE driver must be disabled for all devices if the DONE pins are tied together, because there can be variations in the startup sequencing of each device. A pull-up resistor is therefore required on the common DONE signal.-g DriveDone:no (BitGen option, all devices)∙Connect all DONE pins if using a Master DeviceIt is important to connect the DONE pins for all devices in ganged serial configuration if one FPGA is used as the Master device. Failing to connect the DONE pins can cause configuration to fail for individual devices in this case. If all devices are set for Slave serial mode, the DONE pins can be disconnected (if the external CCLK sourcecontinues toggling until all DONE pins go High).For debugging purposes, it is often helpful to have a way of disconnecting individual DONE pins from the common DONE signal.∙DONE Pin Rise TimeAfter all DONE pins are released, the DONE pin should rise from logic 0 to logic 1 in one CCLK cycle. If additional time is required for the DONE signal to rise, the BitGen donepipe option can be set for all devices in the serial daisy chain.∙Configuration Clock (CCLK) as Clock Signal for Board LayoutThe CCLK signal is relatively slow, but the edge rates on the Virtex-5 input buffers are very fast. Even minor signal integrity problems on the CCLK signal can cause the configuration to fail. (Typical failure mode: DONE Low and INIT_B High.) Therefore, design practices that focus on signal integrity, including signal integrity simulation with IBIS, are recommended.∙Signal FanoutDesigners must focus on good signal integrity when using ganged serialconfiguration. Signal integrity simulation is recommended.∙PROM Files for Ganged Serial ConfigurationSelectMAP Configuration Interface PROM files for ganged serial configuration are identical to the PROM files used toconfigure single devices. There are no special PROM file considerations.SelectMAP Configuration InterfaceThe SelectMAP configuration interface (Figure2-6) provides an 8-bit, 16-bit, or 32-bitbidirectional data bus interface to the Virtex-5 configuration logic that can be used for bothconfiguration and readback. (For details, refer to Chapter7, “Readback and ConfigurationVerification.”) The bus width of SelectMAP is automatically detected (see “Bus Width AutoDetection”).CCLK is an output in Master SelectMAP mode; in Slave SelectMAP, CCLK is an input. Oneor more Virtex-5 devices can be configured through the SelectMAP bus.There are four methods of configuring an FPGA in SelectMAP mode:∙Single device Master SelectMAP∙Single device Slave SelectMAP∙Multiple device SelectMAP bus∙Multiple device ganged SelectMAPTable2-4 describes the SelectMAP configuration interface.Figure 2-6:Virtex-5 Device SelectMAP Configuration InterfaceTable 2-4:Virtex-5 Device SelectMAP Configuration Interface PinsPin Name Type Dedicatedor Dual-PurposeDescriptionM[2:0]Input Dedicated Mode pins - determine configuration modeCCLK Input andOutputDedicatedConfiguration clock source for all configurationmodes except JTAGD[31:0]Three-StateBidirectionalDual-PurposeConfiguration and readback data bus, clockedon the rising edge of CCLK. See “Parallel BusBit Order” and Table1-2.BU S YDONECCLKPROGRAM_BINIT_BD[31:0]M[2:0]C S_BRDWR_BC S O_BUG191_c2_10_072407Chapter 2:Configuration Interfaces。

FPGA可编程逻辑器件芯片XC2V80-6FF1517C中文规格书

Chapter4 User PrimitivesThe configuration primitives described in this chapter are provided for users to accessFPGA configuration resources during or after FPGA configuration. For additionalinformation and instantiation templates, refer to UG615, Spartan-6 Libraries Guide for HDLDesigns.BSCAN_SPARTAN6JTAG is a standard four-pin interface: TCK, TMS, TDI, and TDO. Many applications arebuilt around this interface. The JTAG TAP controller is a dedicated state machine inside theconfiguration logic. BSCAN_SPARTAN6 provides access between the JTAG TAP controllerand user logic in fabric. There are up to four instances of BSCAN_SPARTAN6 for eachdevice. Each instance of this design element can handle one JTAG USER instruction(USER1 through USER4) as set with the JTAG_CHAIN attribute. To handle all four USERinstructions, four of these elements can be instantiated, and the JTAG_CHAIN attributemust be set appropriately. Table4-1 lists the BSCAN_SPARTAN6 port descriptions.Table 4-1:BSCAN_SPARTAN6 Port DescriptionsSignal Name Type FunctionSEL Output Active-High interface selection output. SEL=1 when the JTAGinstruction register holds the corresponding (USER1, USER2,USER3, or USER4) instruction. Change in Update_IR state. SELchanges on the falling edge of TCK in the UPDATE_IR state ofthe TAP controller.RESET Output Active-High reset output. RESET=1 during theTEST-LOGIC-RESET state, PROGRAM_B, or duringpower-up. This signal is deasserted on the falling edge of TCK.TDI Output Fed through directly from the FPGA TDI pin.DRCK Output DRCK is the same as TCK in the Capture_DR and Shift_DRstates. If the interface is not selected by the instruction register,DRCK remains High.CAPTURE Output Active-High pulse indicating the Capture_DR state. This signalis asserted on the falling edge of TCK.UPDATE Output Active-High pulse indicating the Update_DR state. This signalis asserted on the falling edge of TCK.SHIFT Output Active-High pulse indicating the Shift_DR state. This signal isasserted on the falling edge of TCK.RUNTEST Output Indicates JTAG is in Run Test/Idle state.Configuration PinsFloating signal levels are problematic in CMOS logic systems. Other logic components in the system can require a valid input level from the FPGA. The internal pull-up resistors generate a logic High level on each pin. Generally, a device driving signals into the FPGA can overcome the pull-up resistor. Similarly, an individual pin can be pulled down using an appropriately sized external pull-down resistor.In hot-swap or hot-insertion applications, the pull-up resistors provide a potential current path to the I/O power rail. Turning off the pull-up resistors disables this potential path. However, then external pull-up or pull-down resistors can be required on each individual I/O pin.During power-up or at reconfiguration following PROG_B assertion, the I/O pull-ups may be enabled until the device begins configuration.FWE_B Pull-up to VCCO_1No termination User I/O MOSI/CSI_B Pull-up to VCCO_2No termination User I/O RDWR_B Pull-up to VCCO_2No termination User I/OAWAKE Pull-up to VCCO_1No termination User I/O if Suspend feature is not used (4)SUSPEND No termination No termination SUSPEND pin (3)(4)HDC Pull-up to VCCO_1No termination User I/O LDC Pull-up to VCCO_1No termination User I/O USERCCLK Pull-up to VCCO_2No termination User I/O Other I/O(not used during configuration)Pull-up to VCCONo terminationUser I/ONotes:1.A24/A25 are in bank 5 in the 6SLX75/T devices and larger densities and in FG676 and larger packages. Then the pull-up is to VCCO_5.2.Setting the BitGen options configures the termination on the respective pin. Not setting an option defaults to Pull-up. Refer to the BitGen section of UG628, Command Line Tools User Guide , for software settings.3.The SUSPEND pin must be Low during power-up. Connection of an external pull-down resistor ensures this condition.4.For more details on the Suspend feature, refer to UG394, Spartan-6 FPGA Power Management User Guide .Table 5-2:Spartan-6 FPGA Configuration Pin Termination (Cont’d)PinPre-ConfigurationPost-ConfigurationHSWAPEN = 0(enabled)HSWAPEN = 1(disabled)Chapter 5:Configuration DetailsReserving Dual-Purpose Configuration Pins (Persist)Dual-purpose pins serve as configuration pins and user I/Os after configuration. TheBitGen option -g Persist is used to reserve these pins as configuration pins (seeTable5-3 for the settings).Table 5-3:Dual-Purpose Configuration Pin SettingsPin Name Bank SelectMAP BPI SPI/Serial DIN/D0/MISO/MISO[1]2Persist No PersistD1/MISO22Persist No NoD2/MISO32Persist No NoD[15:3]2Persist(1)No NoDOUT1Persist No PersistINIT_B(2)2Persist(2)No(2)Persist(2)RDWR_B2Persist No NoM02No No NoM12No No NoHSWAPEN0No No NoCCLK2Persist No PersistGCLK0/USERCCLK2No No NoCSO_B2No No NoMOSI/MISO0/CSI_B2Persist No NoAWAKE(3)1No No NoA[25:0](4)1No No NoSCP[7:0](3)0No No NoFCS_B1No No NoFOE_B1No No NoFWE_B1No No NoHDC1No No NoLDC1No No NoNotes:1.All 16 data pins are persisted regardless of whether the SelectMAP data width is x8 or x16.2.INIT_B is persisted if readback CRC is enabled, regardless of the POST_CRC_INIT_FLAG setting.3.AWAKE and SCP[7:0] are activated based on the suspend setting.4.A24 and A25 are in bank 5 in larger devices with 6 or more I/O banks.Chapter 6:Readback and Configuration VerificationChapter 7:Reconfiguration and MultiBoot。

FPGA可编程逻辑器件芯片XC2V8000-4FF1517I中文规格书

The procedures for configuring and using each of the seven major blocks in theGTX_DUAL tile shown in Figure1-3 are discussed in detail in the following sections:1.“Shared PMA PLL,” page 86 (Chapter5)2.“Reset,” page 101 (Chapter5)3.“Clocking,” page 96 (Chapter5)4.“Power Control,” page 110 (Chapter5)5.“Dynamic Reconfiguration Port,” page 117 (Chapter5)6.“GTX Transmitter (TX),” page 119 (Chapter6)7.“GTX Receiver (RX),” page 161 (Chapter7)Ports and AttributesThis section contains alphabetical tables of pins (Table1-2), ports (Table1-3 and Table1-4),and attributes (Table1-5 and Table1-6). In all Port and Attribute tables in this guide, namesthat end with 0 are for the GTX0 transceiver on the tile, and names that end with 1 are forthe GTX1 transceiver. Names that do not end with 0 or 1 are shared.Table1-2 lists alphabetically the signal names, directions, and descriptions of theGTX_DUAL analog pins, and provides links to their detailed descriptions.Table 1-2:GTX_DUAL Analog Pin SummaryPin Dir Description Section (Page)MGTAVCC In (Pad)Analog supply for the internal analogcircuits of the GTX_DUAL tile.Analog DesignGuidelines (page253)MGTAVCCPLL In (Pad)Analog supply for the shared PMAPLL of the GTX_DUAL tile.Analog DesignGuidelines (page253)MGTAVTTRX In (Pad)Analog supply for the receivercircuits and the termination of theGTX_DUAL tile.Analog DesignGuidelines (page253)MGTAVTTRXC In (Pad)FXT only: Analog supply for theresistor calibration and the standbycircuit of the entire device.Analog DesignGuidelines (page253)MGTAVTTRXC_R In (Pad)TXT only: Analog supply for theresistor calibration and standbycircuits of the X1 column.Analog DesignGuidelines (page254)MGTAVTTRXC_L In (Pad)TXT only: Analog supply for theresistor calibration and standbycircuits of the X0 column.Analog DesignGuidelines (page254)MGTAVTTTX In (Pad)Analog supply for the transmittertermination and driver circuits andthe clock routing and muxingnetwork of the GTX_DUAL tile.Analog DesignGuidelines (page254)MGTREFCLKP MGTREFCLKN In (Pad)Differential clock input pin pair forthe reference clock of the GTX_DUALtile.Analog DesignGuidelines (page254)MGTRREF In (Pad)FXT only: Reference resistor input forthe entire device.Analog DesignGuidelines (page254)RXUSRCLK20 RXUSRCLK21In N/AInput clock used for the interfacebetween the FPGA and the GTXtransceiver.FPGA RX Interface(page237)RXVALID0 RXVALID1Out RXUSRCLK2Indicates symbol lock and validdata on RXDATA andRXCHARISK[3:0] for PCIExpress operations.RX OOB/Beacon Signaling(page174)TXBUFDIFFCTRL0[2:0] TXBUFDIFFCTRL1[2:0] In AsyncControls the strength of the TXpre-drivers.Configurable TX Driver(page151)TXBUFSTATUS0[1:0] TXBUFSTATUS1[1:0]Out TXUSRCLK2TX buffer status. Indicates TXbuffer overflow or underflow.TX Buffering, PhaseAlignment, and TX SkewReduction (page143)TXBYPASS8B10B0[3:0] TXBYPASS8B10B1[3:0]In TXUSRCLK2Controls the operation of the TX8B/10B encoder on a per-bytebasis.Configurable 8B/10BEncoder (page130)TXCHARDISPMODE0[3:0] TXCHARDISPMODE1[3:0]In TXUSRCLK2TXCHARDISPMODE andTXCHARDISPVAL allow the8B/10B disparity of outgoingdata to be controlled when8B/10B encoding is enabled.When 8B/10B encoding isdisabled, TXCHARDISPMODEis used to extend the data bus forTX interfaces whose width is amultiple of 10.FPGA TX Interface(page120), Configurable8B/10B Encoder (page130)TXCHARDISPVAL0[3:0] TXCHARDISPVAL1[3:0]In TXUSRCLK2TXCHARDISPVAL andTXCHARDISPMODE allow thedisparity of outgoing data to becontrolled when 8B/10Bencoding is enabled. When8B/10B encoding is disabled,TXCHARDISPVAL is used toextend the data bus for 10-bit,20-bit, or 40-bit TX interfaces.FPGA TX Interface(page121), Configurable8B/10B Encoder (page130)TXCHARISK0[3:0] TXCHARISK1[3:0]In TXUSRCLK2Set High to send TXDATA as an8B/10B K character.Configurable 8B/10BEncoder (page131)TXCOMSTART0 TXCOMSTART1In TXUSRCLK2Initiates the transmission of theCOM sequence selected byTXCOMTYPE (SATA only).TX Out-of-Band/BeaconSignaling (page157)TXCOMTYPE0 TXCOMTYPE1In TXUSRCLK2Selects the type of COM signal tosend (SATA only).TX Out-of-Band/BeaconSignaling (page157)TXDATA0[31:0] TXDATA1[31:0]In TXUSRCLK2Transmitting data bus.FPGA TX Interface(page121)TXDATAWIDTH0[1:0] TXDATAWIDTH1[1:0]In TXUSRCLK2Selects the width of thetransmitting data bus port.FPGA TX Interface(page121)Table 1-3:GTX_DUAL Port Summary (Cont’d)Port Dir Domain Description Section (Page)Chapter 1:Introduction to the RocketIO GTX TransceiverCLK_COR_KEEP_IDLE_0 CLK_COR_KEEP_IDLE_1BooleanControls whether the elastic buffermust retain at least one clock correctionsequence in the byte stream.Configurable ClockCorrection (page213)CLK_COR_MAX_LAT_0 CLK_COR_MAX_LAT_1IntegerSpecifies the maximum elastic bufferlatency.Configurable ClockCorrection (page213)CLK_COR_MIN_LAT_0 CLK_COR_MIN_LAT_1IntegerSpecifies the minimum elastic bufferlatency.Configurable ClockCorrection (page214)CLK_COR_PRECEDENCE_0 CLK_COR_PRECEDENCE_1BooleanDetermines whether clock correctionor channel bonding takes precedencewhen both operations are triggered atthe same time. Set to TRUE to giveclock correction precedence.Configurable ClockCorrection (page214)CLK_COR_REPEAT_WAIT_0 CLK_COR_REPEAT_WAIT_1IntegerSpecifies the minimum number ofRXUSRCLK cycles without clockcorrection that must occur betweensuccessive clock corrections.Configurable ClockCorrection (page214)CLK_COR_SEQ_1_1_0 CLK_COR_SEQ_1_1_1CLK_COR_SEQ_1_2_0 CLK_COR_SEQ_1_2_1 CLK_COR_SEQ_1_3_0 CLK_COR_SEQ_1_3_1 CLK_COR_SEQ_1_4_110-bitBinaryThe CLK_COR_SEQ_1 attributes areused in conjunction withCLK_COR_SEQ_1_ENABLE to defineclock correction sequence 1.Configurable ClockCorrection (page214)CLK_COR_SEQ_1_ENABLE_0 CLK_COR_SEQ_1_ENABLE_14-bitBinarySets which parts of clock correctionsequence1 are don't cares.Configurable ClockCorrection (page214)CLK_COR_SEQ_2_1_0 CLK_COR_SEQ_2_1_1 CLK_COR_SEQ_2_2_0CLK_COR_SEQ_2_2_1 CLK_COR_SEQ_2_3_0 CLK_COR_SEQ_2_3_1 CLK_COR_SEQ_2_4_0 CLK_COR_SEQ_2_4_110-bitBinaryUsed in conjunction withCLK_COR_SEQ_2_ENABLE to definethe second clock correction sequence.Configurable ClockCorrection (page215)CLK_COR_SEQ_2_ENABLE_0 CLK_COR_SEQ_2_ENABLE_14-bitBinarySets which parts of clock correctionsequence2 are don't cares.Configurable ClockCorrection (page215)CLK_COR_SEQ_2_USE_0 CLK_COR_SEQ_2_USE_1BooleanDetermines if the second clockcorrection sequence is to be used.Configurable ClockCorrection (page215)CLK_CORRECT_USE_0 CLK_CORRECT_USE_1Boolean Set to TRUE to enable clock correction.Configurable ClockCorrection (page213)Table 1-5:GTX_DUAL Attribute Summary (Cont’d)Attribute Type Description Section (Page)Chapter 2:RocketIO GTX Transceiver WizardPackage Placement Information。

FPGA可编程逻辑器件芯片XC2V80-5FF1517C中文规格书

Chapter 1:Configuration OverviewCheck Device ID (Step 5)After the device is synchronized, a device ID check must pass before the configuration data frames can be loaded. This prevents a configuration with a bitstream that is formatted for a different device. For example, the device ID check should prevent an XC5VLX30 from being configured with an XC5VLX50 bitstream.If an ID error occurs during configuration, the device attempts to do a fallback reconfiguration (see “Fallback MultiBoot,” page 153).The device ID check is built into the bitstream, making this step transparent to mostdesigners. Table 1-13 shows the Virtex-5 device ID codes, and Table 1-14 shows the signals relating to the device ID check. The device ID check is performed through commands in the bitstream to the configuration logic, not through the JTAG IDCODE register in this case.The Virtex-5 JTAG ID Code register has the following format:vvvv:fffffff:aaaaaaaaa:cccccccccc11wherev =revisionf =7-bit family code (0010101=XC5VLXT, 0010100=XC5VLX, 0010111=XC 5VSXT,and 0011001=XC5VFXT)a =number of array rows plus array columns c =company codeTable 1-12:Signals Relating to SynchronizationSignal Name Type AccessDescriptionDALIGNStatusOnly available through the SelectMAP interface during an ABORT sequence. (See “Configuration Abort Sequence Description,” page 58.)Indicates whether the device is synchronized.IWIDTH Status Internal signal. Accessed only through the Virtex-5Status register.(1)Indicates the detected bus width:00=x101=x810=x1611=x32If ICAP is enabled, this signal reflects the ICAP width after configuration is done.Notes:rmation on the Virtex-5 status register is available in Table 6-9. Information on accessing the device status register via JTAG is available in Table 7-5. Information on accessing the device status register via SelectMAP is available in Table 7-1.Figure 1-8:Check Device ID (Step 5)UG191_c1_07_050406StepsConfiguration Sequence Table 1-13:Virtex-5 Device ID CodesDeviceID Code (Hex)Revision CodeFamily, Array, and CompanyCodeXC5VLX30See Note 1286E093XC5VLX50See Note 12896093XC5VLX85See Note 128AE093XC5VLX110See Note 128D6093XC5VLX155See Note 128EC093XC5VLX220See Note 1290C093XC5VLX330See Note 1295C093XC5VLX20T See Note 12A56093XC5VLX30T See Note 12A6E093XC5VLX50T See Note 12A96093XC5VLX85T See Note 12AAE093XC5VLX110T SeeNote12AD6093 XC5VLX155T SeeNote12AEC093 XC5VLX220T See Note 12B0C093XC5VLX330T SeeNote12B5C093 XC5VSX35T See Note 12E72093XC5VSX50T See Note 12E9A093XC5VSX95T See Note 12ECE093XC5VSX240T See Note 12F3E093XC5VFX30T See Note 13276093XC5VFX70T See Note 132C6093XC5VFX100T See Note 132D8093XC5VFX130T See Note 13300093XC5VFX200T See Note 13334093XC5VTX150T See Note 14502093XC5VTX240T See Note 1453E093 Notes:1.The value of the Version code can be 0x0 to 0xF.∙Sending a bitstream to the data pin follows the same bit-swapping rule as in SelectMAP mode. See “Parallel Bus Bit Order.”∙If Flash programming is not required, FCS_B, FOE_B, and FWE_B can be tied off; that is, DONE is connected to FCS_B, FOE_B is tied Low, and FWE_B is tied High.∙The CCLK outputs are not used to connect to Flash but are used to sample Flash read data during configuration. All timings are referenced to CCLK. The CCLK pin must not be driven or tied High or Low.∙The RS[1:0] pins are not connected as shown in Figure 2-22. These output pins are only required for MultiBoot configuration. See Chapter 8, “Reconfiguration and MultiBoot.”∙HSWAPEN must be connected to either disable or enable the pull-up resistors.∙If HSWAPEN is left unconnected or tied High, a pull-up resistor is required for FCS_B.∙If HSWAPEN is tied Low, the FCB_B, FOE_B, FWE_B, and the address pins have internal weak pull-up resistors during configuration. After configuration, FCS_B can be either controlled by I/O in user mode or by enabling a weak pull-up resistor through constraints.∙To enable the active driver on DONE, the DriveDONE option in BitGen must be enabled.∙“MultiBoot Bitstream Spacing,” page 155 provides information on when DCI or DCM lock wait is turned on.∙For daisy chaining FPGAs in BPI mode, see Figure 2-12, page 52.∙The BPI Flash vendor data sheet should be referred to for details on the specific Flash signal connectivity. To prevent address misalignment, close attention should be paid to the Flash family address LSB for the byte/word mode used. Not all Flash families use the A0 as the address LSB.Table 2-9 defines the BPI configuration interface pins.If the FPGA is subject to reprogramming or fallback during configuration from the BPI flash, then the INIT pin can be connected to the BPI reset to set the BPI into a known state.Table 2-9:Virtex-5 Device BPI Configuration Interface PinsPin Name Type Dedicated or Dual-PurposeDescriptionM[2:0]InputDedicated The Mode pins determine the BPI mode:010 = BPI-Up mode 011 = BPI-Down modeHSWAPENInputDedicatedControls I/O (except Bank 0 dedicated I/Os) pull-up resistors during configuration. This pin has a built-in weak pull-up resistor.0 = Pull-up during configuration 1 = 3-state during configurationDONEBidirectional, Open-Drain, or ActiveDedicated Active-High signal indicating configuration is complete: 0 = FPGA not configured 1 = FPGA configured。

FPGA可编程逻辑器件芯片XC2V1000-4FF1517I中文规格书

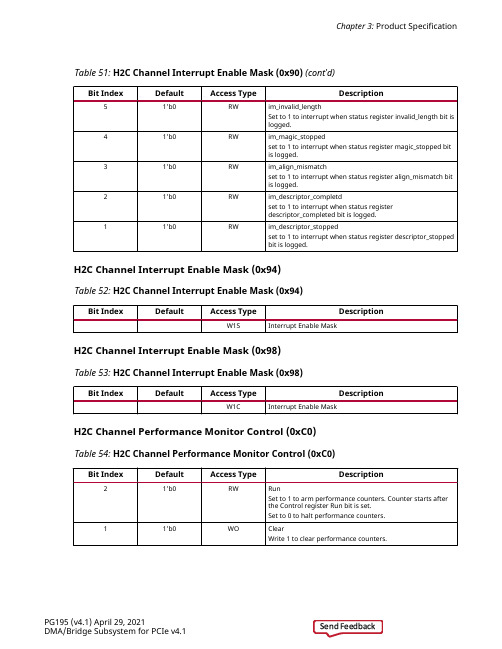

Chapter 3: Product SpecificationTable 51: H2C Channel Interrupt Enable Mask (0x90) (cont'd)Bit Index Default Access Type Description51’b0RW im_invalid_lengthSet to 1 to interrupt when status register invalid_length bit islogged.41’b0RW im_magic_stoppedset to 1 to interrupt when status register magic_stopped bitis logged.31’b0RW im_align_mismatchset to 1 to interrupt when status register align_mismatch bitis logged.21’b0RW im_descriptor_completdset to 1 to interrupt when status registerdescriptor_completed bit is logged.11’b0RW im_descriptor_stoppedset to 1 to interrupt when status register descriptor_stoppedbit is logged.H2C Channel Interrupt Enable Mask (0x94)Table 52: H2C Channel Interrupt Enable Mask (0x94)Bit Index Default Access Type DescriptionW1S Interrupt Enable MaskH2C Channel Interrupt Enable Mask (0x98)Table 53: H2C Channel Interrupt Enable Mask (0x98)Bit Index Default Access Type DescriptionW1C Interrupt Enable MaskH2C Channel Performance Monitor Control (0xC0)Table 54: H2C Channel Performance Monitor Control (0xC0)Bit Index Default Access Type Description21’b0RW RunSet to 1 to arm performance counters. Counter starts afterthe Control register Run bit is set.Set to 0 to halt performance counters.11’b0WO ClearWrite 1 to clear performance counters.Spartan-3 FPGA Family: Introduction and Ordering InformationSpartan-3 FPGA Family: Introduction and Ordering InformationTable 54: H2C Channel Performance Monitor Control (0xC0) (cont'd)Bit Index Default Access Type Description01’b0RW AutoAutomatically stop performance counters when a descriptorwith the stop bit is completed. Automatically clearperformance counters when the Control register Run bit isset. Writing 1 to the Performance Monitor Control registerRun bit is still required to start the counters.H2C Channel Performance Cycle Count (0xC4)Table 55: H2C Channel Performance Cycle Count (0xC4)Bit Index Default Access Type Description31:032’h0RO pmon_cyc_count[31:0]Increments once per clock while running. See thePerformance Monitor Control register (0xC0) bits Clear andAuto for clearing.H2C Channel Performance Cycle Count (0xC8)Table 56: H2C Channel Performance Cycle Count (0xC8)Bit Index Default Access Type Description161’b0RO pmon_cyc_count_maxedCycle count maximum was hit.9:010’h0RO pmon_cyc_count [41:32]Increments once per clock while running. See thePerformance Monitor Control register (0xC0) bits Clear andAuto for clearing.H2C Channel Performance Data Count (0xCC)Table 57: H2C Channel Performance Data Count (0xCC)Bit Index Default Access Type Description31:032’h0RO pmon_dat_count[31:0]Increments for each valid read data beat while running. Seethe Performance Monitor Control register (0xC0) bits Clearand Auto for clearing.H2C Channel Performance Data Count (0xD0)Table 58: H2C Channel Performance Data Count (0xD0)Bit Index Default Access Type Description161’b0RO pmon_dat_count_maxedData count maximum was hitTable 58: H2C Channel Performance Data Count (0xD0) (cont'd)Bit Index Default Access Type Description 15:10Reserved9:010’h0RO pmon_dat_count [41:32]Increments for each valid read data beat while running. Seethe Performance Monitor Control register (0xC0) bits Clearand Auto for clearing.C2H Channel Registers (0x1)The C2H channel register space is described in this section.Table 59: C2H Channel Register SpaceAddress (hex)Register Name0x00C2H Channel Identifier (0x00)0x04C2H Channel Control (0x04)0x08C2H Channel Control (0x08)0x0C C2H Channel Control (0x0C)0x40C2H Channel Status (0x40)0x44C2H Channel Status (0x44)0x48C2H Channel Completed Descriptor Count (0x48)0x4C C2H Channel Alignments (0x4C)0x88C2H Poll Mode Low Write Back Address (0x88)0x8C C2H Poll Mode High Write Back Address (0x8C)0x90C2H Channel Interrupt Enable Mask (0x90)0x94C2H Channel Interrupt Enable Mask (0x94)0x98C2H Channel Interrupt Enable Mask (0x98)0xC0C2H Channel Performance Monitor Control (0xC0)0xC4C2H Channel Performance Cycle Count (0xC4)0xC8C2H Channel Performance Cycle Count (0xC8)0xCC C2H Channel Performance Data Count (0xCC)0xD0C2H Channel Performance Data Count (0xD0)C2H Channel Identifier (0x00)Table 60: C2H Channel Identifier (0x00)Bit Index Default Access Type Description 31:2012’h1fc RO Subsystem identifier19:164’h1RO C2H Channel Target。

FPGA可编程逻辑器件芯片XCKU060-2FFVA1517I中文规格书

FPGA可编程逻辑器件芯⽚XCKU060-2FFVA1517I中⽂规格书Introduction to the UltraScale ArchitectureThe Xilinx? UltraScale? architecture is the first ASIC-class architecture to enablemulti-hundred gigabit-per-second levels of system performance with smart processing, while efficiently routing and processing data on-chip. UltraScale architecture-based devices address a vast spectrum of high-bandwidth, high-utilization system requirements by using industry-leading technical innovations, including next-generation routing, ASIC-like clocking, 3D-on-3D ICs, multiprocessor SoC (MPSoC) technologies, and new powerreduction features. The devices share many building blocks, providing scalability across process nodes and product families to leverage system-level investment across platforms.Virtex? UltraScale+? devices provide the highest performance and integration capabilities in a FinFET node, including both the highest serial I/O and signal processing bandwidth, as well as the highest on-chip memory density. As the industry's most capable FPGA family, the Virtex UltraScale+ devices are ideal for applications including 1+Tb/s networking and data center and fully integrated radar/early-warning systems.Virtex UltraScale devices provide the greatest performance and integration at 20nm,including serial I/O bandwidth and logic capacity. As the industry's only high-end FPGA at the 20nm process node, this family is ideal for applications including 400G networking, large scale ASIC prototyping, and emulation.Kintex? UltraScale+ devices provide the best price/performance/watt balance in a FinFET node, delivering the most cost-effective solution for high-end capabilities, includingtransceiver and memory interface line rates as well as 100G connectivity cores. Our newest mid-range family is ideal for both packet processing and DSP-intensive functions and is well suited for applications including wireless MIMO technology,Nx100G networking, and data center.Kintex UltraScale devices provide the best price/performance/watt at 20nm and include the highest signal processing bandwidth in a mid-range device, next-generation transceivers, and low-cost packaging for an optimum blend of capability andcost-effectiveness. The family is ideal for packet processing in 100G networking and data centers applications as well as DSP-intensive processing needed in next-generation medicalimaging, 8k4k video, and heterogeneous wireless infrastructure.找FPGA 和CPLD 可编程逻辑器件,上深圳宇航军⼯半导体有限公司Gigabit Transceiver Channels by Device/PackageTable 1-2 lists the quantity of gigabit transceiver channels for the UltraScale andUltraScale+ devices. In all devices, a gigabit transceiver channel is one set of MGTRXP, MGTRXN, MGTTXP, and MGTTXN pins. For transceiver data rate limitations on specific device/package combinations, see the specific UltraScale and UltraScale+ device data sheets [Ref 4].FSVA3824SSI, flip-chip, fine-pitch, lidless with stiffener ring BGA 1.065x 65FSVB3824 SSI, flip-chip, fine-pitch, lidless with stiffener ringBGA1.065x 65Notes:1.FFV, FLV, and FLG packages are footprint compatible when the package code letter designator and pin count are identical.See UltraScale Architecture and Product Overview (DS890) [Ref 1] for specific letter codes and ordering code information.2.These 52.5x 52.5 packages have the same PCB ball footprint as the 47.5x 47.5 packages and are footprint compatible.Table 1-1:Package Specifications (Cont’d)Packages (1)DescriptionPackage SpecificationsPackage Type Pitch (mm)Size (mm)Table 1-2:Serial Transceiver Channels (GTH/GTY) by Device/PackageDevicePackageGTH ChannelsGTY ChannelsKintex UltraScale DevicesXCKU035FBVA676160XCKU040160XCKU035SFVA78480XCKU04080XCKU035FBVA900160XCKU040160XCKU025FFVA1156120XCKU035160XCKU040200XCKU060280XCKU095208XCKU060FFVA1517320XCKU085FLVA1517480XCKU115480XCKU095FFVC15172020XCKU115FLVD1517640XCKU095 FFVB17603216Pin DefinitionsTable1-5 lists the pin definitions used in UltraScale and UltraScale+ device packages.DBC QBC Multi-functionInputByte lane clock (DBC and QBC) input pin pairs are clock inputs directly driving source synchronous clocks to the bit slices in the I/O banks. In memory applications, these are also known as DQS. For more information, consult the UltraScale Architecture SelectIO Resources User Guide (UG571) [Ref 5].PERSTN[0 to 1]Multi-functionInputDefault reset pin locations for the integrated block for PCI Express.User I/O Multi-Function Configuration PinsFor further descriptions, including configuration modes and recommended external pull-up/pull-down resistors, see the UltraScale Architecture Configuration User Guide (UG570) [Ref 7].EMCCLK Multi-function Input External master configuration clock.DOUT_CSO_B Multi-function Output Data output for serial daisy-chaining or active-Low chip-select output for SelectMAP daisy-chaining.D[04 to 31]Multi-function Bidirectional Configuration data pins.A[00 to 28]Multi-function Output Address output.CSI_ADV_B Multi-function Input or Output Active-Low chip-select input or address valid output.FOE_B Multi-function Output Active-Low flash output enable.FWE_FCS2_B Multi-function Output Active-Low flash write-enable for BPI flash or flash chip-select for second SPI (x8) flash.RS[0 to 1]Multi-functionOutputRevision select outputs.Dedicated (Bank 0) Configuration Pins (2)For more information see the UltraScale Architecture Configuration User Guide (UG570) [Ref 7].M[0 to 2]_0Dedicated Input Configuration mode selection.INIT_B_0DedicatedBidirectional (open-drain)Active-Low initializationTable 1-5:Pin Definitions (Cont’d)Pin NameTypeDirectionDescription。

FPGA可编程逻辑器件芯片XC2VP50-5FFG1517C中文规格书

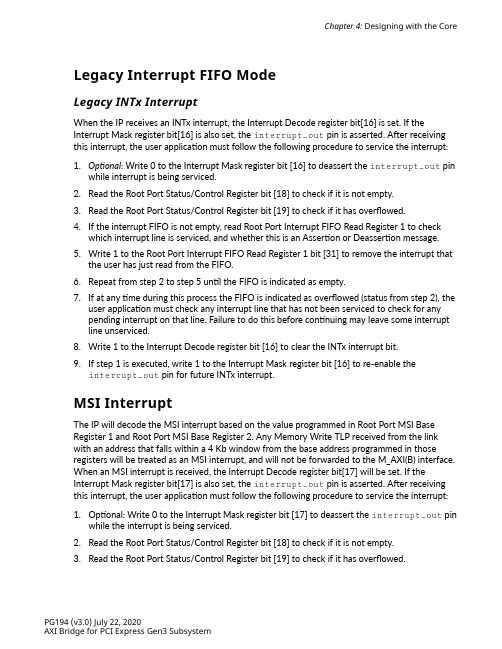

Chapter 4: Designing with the CoreLegacy Interrupt FIFO ModeLegacy INTx InterruptWhen the IP receives an INTx interrupt, the Interrupt Decode register bit[16] is set. If theInterrupt Mask register bit[16] is also set, the interrupt_out pin is asserted. After receiving this interrupt, the user application must follow the following procedure to service the interrupt:1.Optional: Write 0 to the Interrupt Mask register bit [16] to deassert the interrupt_out pinwhile interrupt is being serviced.2.Read the Root Port Status/Control Register bit [18] to check if it is not empty.3.Read the Root Port Status/Control Register bit [19] to check if it has overflowed.4.If the interrupt FIFO is not empty, read Root Port Interrupt FIFO Read Register 1 to checkwhich interrupt line is serviced, and whether this is an Assertion or Deassertion message.5.Write 1 to the Root Port Interrupt FIFO Read Register 1 bit [31] to remove the interrupt thatthe user has just read from the FIFO.6.Repeat from step 2 to step 5 until the FIFO is indicated as empty.7.If at any time during this process the FIFO is indicated as overflowed (status from step 2), theuser application must check any interrupt line that has not been serviced to check for anypending interrupt on that line. Failure to do this before continuing may leave some interruptline unserviced.8.Write 1 to the Interrupt Decode register bit [16] to clear the INTx interrupt bit.9.If step 1 is executed, write 1 to the Interrupt Mask register bit [16] to re-enable theinterrupt_out pin for future INTx interrupt.MSI InterruptThe IP will decode the MSI interrupt based on the value programmed in Root Port MSI BaseRegister 1 and Root Port MSI Base Register 2. Any Memory Write TLP received from the linkwith an address that falls within a 4 Kb window from the base address programmed in thoseregisters will be treated as an MSI interrupt, and will not be forwarded to the M_AXI(B) interface.When an MSI interrupt is received, the Interrupt Decode register bit[17] will be set. If theInterrupt Mask register bit[17] is also set, the interrupt_out pin is asserted. After receiving this interrupt, the user application must follow the following procedure to service the interrupt:1.Optional: Write 0 to the Interrupt Mask register bit [17] to deassert the interrupt_out pinwhile the interrupt is being serviced.2.Read the Root Port Status/Control Register bit [18] to check if it is not empty.3.Read the Root Port Status/Control Register bit [19] to check if it has overflowed.PG194 (v3.0) July 22, 2020AXI Bridge for PCI Express Gen3 SubsystemChapter 4: Designing with the Core4.If the interrupt FIFO is not empty, read the Root Port Interrupt FIFO Read Register 2 to checkMSI Message Data from the received MSI interrupt. This is used by the user application todetermine the interrupt vector number and can also be used to determine the source of theinterrupt.5.Write 1 to the Root Port Interrupt FIFO Read Register 1 bit [31] to remove the interrupt userhas just read from the FIFO.6.Repeat from step 2 until the FIFO is indicated as empty.7.If at any time during this process, the FIFO was indicated as overflowed (status from step 2),the user application must check any unserviced interrupt vectors to check for any pendinginterrupts on that line. Failure to do this before continuing can leave some interrupt vectorunserviced.8.Write 1 to the Interrupt Decode Register bit [17] to clear the MSI interrupt bit.9.If step 1 was executed, write 1 to the Interrupt Mask Register bit [17] to re-enable theinterrupt_out pin for future MSI interrupts.MSI-X InterruptAll MSI-X interrupts must be decoded by the user application externally to the IP. T o do this, set all of their Endpoints to use an MSI-X address that falls outside of the range of the 4Kb window from the base address programmed in the Root Port MSI Base Register 1 and Root Port MSI Base Register 2. All MSI-X interrupts will be forwarded to the M_AXI(B) interface.All TLPs forwarded to M_AXI(B) interface are subject to the PCIe-to-AXI Address translation.Interrupt Decode ModeLegacy INTx InterruptWhen the IP has received an INTx interrupt, the Root Port Interrupt Decode 2 register is set. Ifthe Root Port Interrupt Decode 2 Mask register is also set, the interrupt_out pin is asserted.After receiving this interrupt, the user application must follow this procedure to service theinterrupt:1.Optional: Write 0 to the Interrupt Decode 2 Mask register to deassert an interrupt line whilethe interrupt is being serviced.2.Read the Root Port Interrupt Decode 2 register to check which interrupt line is currentlyasserted.3.Repeat step 2 until all interrupt lines are deasserted. The interrupt line is automaticallycleared when the IP receives the INTx Deassert Message corresponding to that interrupt line.4.If step 1 was executed, write 1 to the Interrupt Decode 2 Mask register to re-enable aninterrupt line for future INTx interrupt.PG194 (v3.0) July 22, 2020AXI Bridge for PCI Express Gen3 SubsystemChapter 4: Designing with the CoreMSI InterruptThe IP decodes the MSI interrupt based on the value programmed in Root Port MSI BaseRegister 1 and Root Port MSI Base Register 2. Any Memory Write TLPs received from the linkwith an address that falls within the 4 Kb window from the base address programmed in thoseregisters will be treated as MSI interrupt, and will not be forwarded to the M_AXI(B) interface.Note: MSI Message Data [5:0] will always be decoded as MSI Message vector regardless of how manyvectors are enabled at your Endpoint.When an MSI interrupt is received, the Root Port MSI Interrupt Decode 1 or Root Port MSIInterrupt Decode 2 register is set. If the Root Port MSI Interrupt Decode 1 or Root Port MSIInterrupt Decode 2 register is also set, the interrupt_out_msi_vec* pins are asserted.interrupt_out_msi_vec0to31 corresponds to MSI vector 0 - 31, andinterrupt_out_msi_vec32to63 corresponds to MSI vector 32 - 63. After receiving thisinterrupt, the user application must follow this procedure to service the interrupt:1.Optional: Write 0 to the Root Port MSI Interrupt Decode 1 or 2 Mask register to deassert theinterrupt_out_msi_vec* pins while the interrupt is being serviced.2.Read the Root Port MSI Interrupt Decode 1 or 2 register to check which interrupt vector isasserted.3.Write 1 to the Root Port MSI Interrupt Decode 1 or 2 register to clear the MSI interrupt bit.4.If step 1 was executed, write 1 to the Root Port MSI Interrupt Decode 1 or 2 Mask registerbit to re-enable the interrupt_out_msi_vec* pins for future MSI interrupts.MSI-X InterruptAll MSI-X interrupts must be decoded by the user application externally to the IP. T o do this, the user application must set all Endpoints to use an MSI-X address that falls outside of the range of the 4Kb window from the base address programmed in the Root Port MSI Base Register 1 andthe Root Port MSI Base Register 2. All MSI-X interrupts are forwarded to the M_AXI(B) interface.All TLPs forwarded to M_AXI(B) interface are subject to PCIe-to-AXI Address translation.Tandem ConfigurationTandem Configuration features are available for the Bridge core for all UltraScale devices.Tandem Configuration is not currently supported for Bridge mode in UltraScale+ devices.Tandem Configuration utilizes a two-stage methodology that enables the IP to meet theconfiguration time requirements indicated in the PCI Express Specification.Multiple use casesare supported with this technology:PG194 (v3.0) July 22, 2020AXI Bridge for PCI Express Gen3 Subsystem。

FPGA可编程逻辑器件芯片XCKU060FFVA1517中文规格书

DS022-2 (v3.0) March 21, 2014Production Product SpecificationDLL PropertiesProperties provide access to some of the Virtex-E seriesDLL features, (for example, clock division and duty cyclecorrection).Duty Cycle Correction Property The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270,use the duty-cycle corrected default, exhibiting a 50/50 duty cycle. The DUTY_CYCLE_CORRECTION property (by default TRUE) controls this feature. To deactivate the DLL duty-cycle correction for the 1x clock outputs, attach the DUTY_CYCLE_CORRECTION=FALSE property to the DLL symbol. Clock Divide Property The CLKDV_DIVIDE property specifies how the signal on the CLKDV pin is frequency divided with respect to the CLK0 pin. The values allowed for this property are 1.5, 2,2.5, 3, 4, 5, 8, or 16; the default value is 2.Startup Delay PropertyThis property, STARTUP_WAIT, takes on a value of TRUEor FALSE (the default value). When TRUE the device con-figuration DONE signal waits until the DLL locks beforegoing to High.Virtex-E DLL Location Constraints As shown in Figure 26, there are four additional DLLs in the Virtex-E devices, for a total of eight per Virtex-E device.These DLLs are located in silicon, at the top and bottom of the two innermost block SelectRAM columns. The location constraint LOC, attached to the DLL symbol with the identi-fier DLL0S, DLL0P , DLL1S, DLL1P , DLL2S, DLL2P , DLL3S,or DLL3P , controls the DLL location.The LOC property uses the following form:LOC = DLL0P Design FactorsUse the following design considerations to avoid pitfalls andimprove success designing with Xilinx devices.Input Clock The output clock signal of a DLL, essentially a delayed ver-sion of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the qual-ity of the DLL input clock relates directly to the quality of theoutput clock waveforms generated by the DLL. The DLLinput clock requirements are specified in the data sheet.In most systems a crystal oscillator generates the systemclock. The DLL can be used with any commercially availablequartz crystal oscillator. For example, most crystal oscilla-tors produce an output waveform with a frequency toleranceof 100 PPM, meaning 0.01 percent change in the clockperiod. The DLL operates reliably on an input waveform witha frequency drift of up to 1 ns — orders of magnitude inexcess of that needed to support any crystal oscillator in theindustry. However, the cycle-to-cycle jitter must be kept toless than 300 ps in the low frequencies and 150 ps for thehigh frequencies.Input Clock Changes Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL produces an unreliable lock signal and out-put clock.It is possible to stop the input clock with little impact to theDLL.Stopping the clock should be limited to less than100 μs to keep device cooling to a minimum. The clockshould be stopped during a Low phase, and when restoredthe full High period should be seen. During this time,LOCKED stays High and remains High when the clock isrestored.When the clock is stopped, one to four more clocks are stillobserved as the delay line is flushed. When the clock isrestarted, the output clocks are not observed for one to fourclocks as the delay line is filled. The most common case istwo or three clocks.In a similar manner, a phase shift of the input clock is alsopossible. The phase shift propagates to the output one tofour clocks after the original shift, with no disruption to theCLKDLL control.Output ClocksAs mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF , a global clock buffer BUFG, or they can route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bot-tom). In addition, the CLK2X output of the secondary DLL can connect directly to the CLKIN of the primary DLL in the same quadrant.Do not use the DLL output clock signals until after activationof the LOCKED signal. Prior to the activation of theLOCKED signal, the DLL output clocks are not valid andcan exhibit glitches, spikes, or other spurious movement.Figure 26: Virtex Series DLLsDS022-4 (v3.0) March 21, 2014Production Product Specification 6IO_VREF_L299N_YY W56IO_L299P_YY V16IO_L300N_YY V76IO_L300P_YY U26IO_VREF_L301N_Y V616IO_L301P_Y U17IO F57IO G637IO H17IO H737IO K237IO K437IO L637IO M537IO M1037IO N537IO N107IO R747IO T27IO T737IO U87IO V437IO_L302N_YY U97IO_L302P_YY U47IO_L303N_Y U77IO_VREF_L303P_Y U517IO_L304N_YY U37IO_L304P_YY U67IO_L305N_YY T37IO_VREF_L305P_YY T67IO_L306N_Y T97IO_L306P_Y T4 7IO_L307N_Y T55Table 28: FG1156 — XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200EBankPin Description Pin #7IO_L307P_Y R147IO_L308N_Y R67IO_L308P_Y T107IO_L309N_YY R27IO_L309P_YY R57IO_L310N_YY P17IO_VREF_L310P_YYP57IO_L311N_YR87IO_L311P_YP27IO_L312N_YR957IO_L312P_YN147IO_L313N_YP47IO_L313P_YR107IO_L314N_YYP87IO_L314P_YYN27IO_L315N_YYP657IO_L315P_YYP747IO_L316N_YM17IO_VREF_L316P_YN47IO_L317N_YN67IO_L317P_YN37IO_L318NP97IO_L318PM27IO_L319N_YN77IO_L319P_YM37IO_L320N_YP107IO_L320P_YM47IO_L321N_YL17IO_L321P_YN87IO_L322N_YYL27IO_L322P_YYN97IO_L323N_YYM77IO_VREF_L323P_YYK17IO_L324N_Y M8Table 28: FG1156 — XCV1000E, XCV1600E, XCV2000E, XCV2600E, XCV3200E Bank Pin Description Pin #。

FPGA可编程逻辑器件芯片XCVU095-2FFVD1517E中文规格书

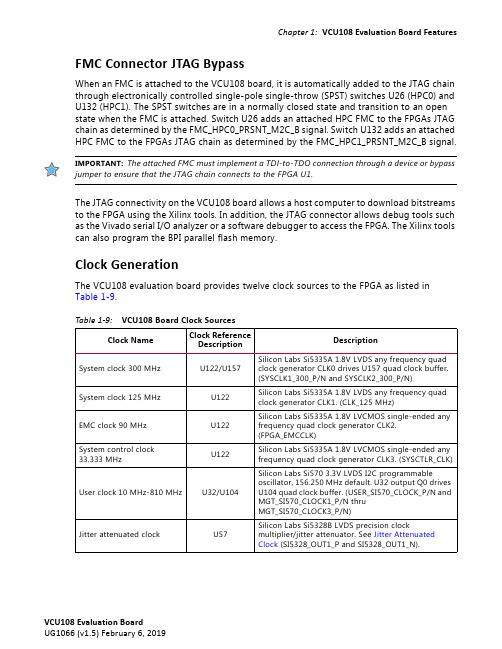

FMC Connector JTAG BypassWhen an FMC is attached to the VCU108 board, it is automatically added to the JTAG chain through electronically controlled single-pole single-throw (SPST) switches U26 (HPC0) and U132 (HPC1). The SPST switches are in a normally closed state and transition to an open state when the FMC is attached. Switch U26 adds an attached HPC FMC to the FPGAs JTAG chain as determined by the FMC_HPC0_PRSNT_M2C_B signal. Switch U132 adds an attachedHPC FMC to the FPGAs JTAG chain as determined by the FMC_HPC1_PRSNT_M2C_B signal.The JTAG connectivity on the VCU108 board allows a host computer to download bitstreams to the FPGA using the Xilinx tools. In addition, the JTAG connector allows debug tools such as the Vivado serial I/O analyzer or a software debugger to access the FPGA. The Xilinx tools can also program the BPI parallel flash memory.Clock GenerationThe VCU108 evaluation board provides twelve clock sources to the FPGA as listed in Table1-9.Table 1-9:VCU108 Board Clock SourcesClock Name Clock ReferenceDescription DescriptionSystem clock 300 MHz U122/U157Silicon Labs Si5335A 1.8V LVDS any frequency quad clock generator CLK0 drives U157 quad clock buffer. (SYSCLK1_300_P/N and SYSCLK2_300_P/N)System clock 125 MHz U122Silicon Labs Si5335A 1.8V LVDS any frequency quadclock generator CLK1. (CLK_125 MHz)EMC clock 90 MHz U122Silicon Labs Si5335A 1.8V LVCMOS single-ended any frequency quad clock generator CLK2.(FPGA_EMCCLK)System control clock33.333MHz U122Silicon Labs Si5335A 1.8V LVCMOS single-ended any frequency quad clock generator CLK3. (SYSCTLR_CLK)User clock 10MHz-810MHz U32/U104Silicon Labs Si570 3.3V LVDS I2C programmable oscillator, 156.250 MHz default. U32 output Q0 drives U104 quad clock buffer. (USER_SI570_CLOCK_P/N and MGT_SI570_CLOCK1_P/N thruMGT_SI570_CLOCK3_P/N)Jitter attenuated clock U57Silicon Labs Si5328B LVDS precision clock multiplier/jitter attenuator. See Jitter Attenuated Clock (SI5328_OUT1_P and SI5328_OUT1_N).Table 1-25:VCU108 Board FPGA U1 to CFP2 Module ConnectionsFPGA (U1) Pin Schematic NetName FPGA (U1)Direction CFP2 Pin Number CFP2 Pin NameAC40CFP2_TX9_X_P Output3TX9_P AC41CFP2_TX9_X_N Output2TX9_N AA40CFP2_TX8_X_P Output6TX8_P AA41CFP2_TX8_X_N Output5TX8_N W40CFP2_TX7_X_P Output102TX7_P W41CFP2_TX7_X_N Output103TX7_N T42CFP2_TX6_3_P Output99TX6_P T43CFP2_TX6_3_N Output100TX6_N P42CFP2_TX5_2_P Output96TX5_P P43CFP2_TX5_2_N Output97TX5_N U40CFP2_TX4_X_P Output93TX4_P U41CFP2_TX4_X_N Output94TX4_NTable 1-29 lists the HDMI Codec U52 to the XCVU095 device U1 connections. All HDMI nets in this table are series resistor coupled.For more information about the Analog Devices ADV7511KSTZ-P, see the Analog Devices website [Ref 21]. For additional information about HDMI IP options, see the DisplayPort LogiCORE IP Product Guide (PG064) [Ref 22].Table 1-29:HDMI Codec U52 to XCVU095 Device U1 ConnectionsFPGA (U1)PinSchematic NetNameFPGA (U1) DirectionI/O StandardADV7511 U52Pin NumberNameR36HDMI_D0Output LVCMOS1888D8R34HDMI_D1Output LVCMOS1887D9P34HDMI_D2Output LVCMOS1886D10V30HDMI_D3Output LVCMOS1885D11V33HDMI_D4Output LVCMOS1884D12V34HDMI_D5Output LVCMOS1883D13U35HDMI_D6Output LVCMOS1882D14T36HDMI_D7Output LVCMOS1881D15Y34HDMI_D8Output LVCMOS1880D16W34HDMI_D9Output LVCMOS1878D17V32HDMI_D10Output LVCMOS1874D18U33HDMI_D11Output LVCMOS1873D19AH33HDMI_D12Output LVCMOS1872D20AH30HDMI_D13Output LVCMOS1871D21AM33HDMI_D14Output LVCMOS1870D22AM31HDMI_D15Output LVCMOS1869D23AH34HDMI_DE Output LVCMOS1897DE AJ35HDMI_SPDIF Output LVCMOS1810SPDIF AK33HDMI_CLK Output LVCMOS1879CLK AK30HDMI_VSYNC Output LVCMOS182VSYNC AK29HDMI_HSYNC Output LVCMOS1898HSYNC AJ33HDMI_INT Input LVCMOS1845INT AJ36HDMI_SPDIF_OUTInputLVCMOS1846SPDIF_OUT。

FPGA可编程逻辑器件芯片XC2V250-4FF1517I中文规格书

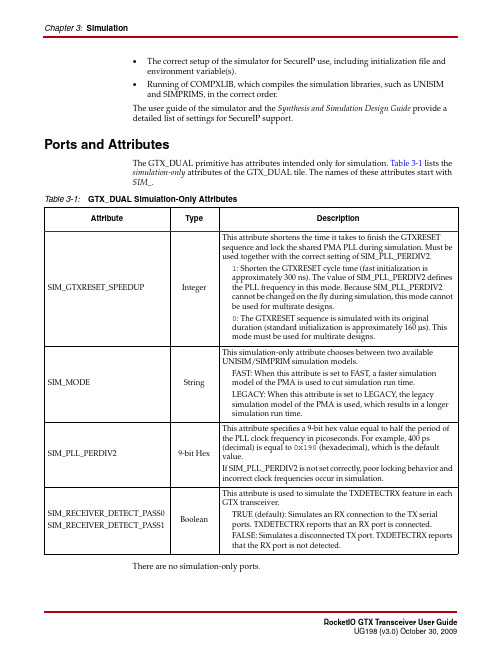

Chapter 3:Simulation•The correct setup of the simulator for SecureIP use, including initialization file and environment variable(s).•Running of COMPXLIB, which compiles the simulation libraries, such as UNISIM and SIMPRIMS, in the correct order.The user guide of the simulator and the Synthesis and Simulation Design Guide provide a detailed list of settings for SecureIP support.Ports and AttributesThe GTX_DUAL primitive has attributes intended only for simulation. Table 3-1 lists the simulation-only attributes of the GTX_DUAL tile. The names of these attributes start with SIM_.There are no simulation-only ports.Table 3-1:GTX_DUAL Simulation-Only Attributes AttributeTypeDescriptionSIM_GTXRESET_SPEEDUP IntegerThis attribute shortens the time it takes to finish the GTXRESET sequence and lock the shared PMA PLL during simulation. Must be used together with the correct setting of SIM_PLL_PERDIV2.1: Shorten the GTXRESET cycle time (fast initialization isapproximately 300ns). The value of SIM_PLL_PERDIV2 defines the PLL frequency in this mode. Because SIM_PLL_PERDIV2 cannot be changed on the fly during simulation, this mode cannot be used for multirate designs.0: The GTXRESET sequence is simulated with its originalduration (standard initialization is approximately 160µs). This mode must be used for multirate designs.SIM_MODEStringThis simulation-only attribute chooses between two available UNISIM/SIMPRIM simulation models.FAST: When this attribute is set to FAST, a faster simulation model of the PMA is used to cut simulation run time.LEGACY: When this attribute is set to LEGACY, the legacy simulation model of the PMA is used, which results in a longer simulation run time.SIM_PLL_PER D IV29-bit HexThis attribute specifies a 9-bit hex value equal to half the period of the PLL clock frequency in picoseconds. For example, 400ps (decimal) is equal to 0x190 (hexadecimal), which is the default value.If SIM_PLL_PERDIV2 is not set correctly, poor locking behavior and incorrect clock frequencies occur in simulation.SIM_RECEIVER_DETECT_PASS0SIM_RECEIVER_DETECT_PASS1BooleanThis attribute is used to simulate the TXDETECTRX feature in each GTX transceiver.TRUE (default): Simulates an RX connection to the TX serial ports. TXDETECTRX reports that an RX port is connected.FALSE: Simulates a disconnected TX port. TXDETECTRX reports that the RX port is not detected.DescriptionDescriptionThe behavior of the GTX_DUAL tile is modeled using a SmartModel. The SmartModel allows the design containing GTX_DUAL tiles to be simulated in the following design phases:•Register Transfer Level (RTL)/Pre-Synthesis Simulation •Post-Synthesis Simulation/Pre-NGDBuild Simulation •Post-NGDBuild/Pre-Map Simulation •Post-Map/Partial Timing Simulation •Post-Place and Route/Timing SimulationLimitationsThe analog nature of some blocks inside the GTX_DUAL tile generates some restrictions when simulated using an HDL simulator. Receiver detection and OOB/beacon signaling are analog features of the GTX_DUAL tile that can only be modeled in a limited way with an HDL simulator. The shared PMA PLL is another analog block in the GTX_DUAL tile that is difficult to model precisely. The simulation-only attributesSIM_GTXRESET_SPEEDUP and SIM_PLL_PERDIV2 speed up the simulation by shortening the locking time of the shared PMA PLL.SmartModel AttributesSIM_GTXRESET_SPEEDUPThe SIM_GTXRESET_SPEEDUP attribute can be used to shorten the simulated lock time of the shared PMA PLL.If TXOUTCLK or RXRECCLK is used to generate clocks in the design, these clocks occasionally flatline while the GTX_DUAL tile is locking. If a PLL or a digital clockmanager (DCM) is used to divide TXOUTCLK or RXRECCLK, the final output clock is not ready until both the GTX_DUAL tile and the PLL or DCM have locked. Equation 3-1 provides an estimate of the time required before a stable source from TXOUTCLK orRXRECCLK is available in simulation, including the time required for any PLLs or DCMs used.Equation 3-1If either the PLL or the DCM is not used, the respective term can be removed from the lock time equation. When simulating multirate designs where the shared PMA PLL frequency or REFCLK frequency changes, SIM_GTXRESET_SPEEDUP must be set to FALSE. Appendix F, “Advanced Clocking” illustrates multirate design examples.SIM_MODEThis simulation-only attribute chooses between two available UNISIM/SIMPRIMsimulation models. The LEGACY setting selects the legacy simulation model of the PMA of the GTX transceiver. The FAST setting selects a faster simulation model of the PMA of the GTX transceiver to cut simulation run time.The Legacy model is available for existing users who have been using simulation models with ISE® 11.1 and older software for their designs; however, this legacy model will bet USRCLKstable t GTXRESETsequence t locktimePLL t locktimeDCM ++≅Figure 4-4:XC5VFX70T-FF1136, XC5VFX100T-FF1136 GTX Placement (2 of 2)Shared PMA PLL。

FPGA可编程逻辑器件芯片XCKU095FFVC1517中文规格书