北信科大DSP实验报告

dsp原理与应用实验报告总结

dsp原理与应用实验报告总结DSP(Digital Signal Processing)数字信号处理是利用数字技术对信号进行处理和分析的一种方法。

在本次实验中,我们探索了DSP的原理和应用,并进行了一系列实验以验证其在实际应用中的效果。

以下是对实验结果的总结与分析。

实验一:数字滤波器设计与性能测试在本实验中,我们设计了数字滤波器,并通过性能测试来评估其滤波效果。

通过对不同类型的滤波器进行设计和实现,我们了解到数字滤波器在信号处理中的重要性和应用。

实验二:数字信号调制与解调本实验旨在通过数字信号调制与解调的过程,了解数字信号的传输原理与方法。

通过模拟调制与解调过程,我们成功实现了数字信号的传输与还原,验证了调制与解调的可行性。

实验三:数字信号的傅里叶变换与频谱分析傅里叶变换是一种重要的信号分析方法,可以将信号从时域转换到频域,揭示信号的频谱特性。

本实验中,我们学习了傅里叶变换的原理,并通过实验掌握了频谱分析的方法与技巧。

实验四:数字信号的陷波滤波与去噪处理陷波滤波是一种常用的去除特定频率噪声的方法,本实验中我们学习了数字信号的陷波滤波原理,并通过实验验证了其在去噪处理中的有效性。

实验五:DSP在音频处理中的应用音频处理是DSP的一个重要应用领域,本实验中我们探索了DSP在音频处理中的应用。

通过实验,我们成功实现了音频信号的降噪、均衡和混响处理,并对其效果进行了评估。

实验六:DSP在图像处理中的应用图像处理是另一个重要的DSP应用领域,本实验中我们了解了DSP在图像处理中的一些基本原理和方法。

通过实验,我们实现了图像的滤波、边缘检测和图像增强等处理,并观察到了不同算法对图像质量的影响。

通过以上一系列实验,我们深入了解了DSP的原理与应用,并对不同领域下的信号处理方法有了更深刻的认识。

本次实验不仅加深了我们对数字信号处理的理解,也为日后在相关领域的研究与实践提供了基础。

通过实验的结果和总结,我们可以得出结论:DSP作为一种数字信号处理的方法,具有广泛的应用前景和重要的实际意义。

DSP实验报告6

DSP第六、七次实验报告1. 实验目的:(1)进一步熟悉Matlab实验环境和语言。

(2)熟悉各种滤波器的结构及Matlab实现语言。

(3)掌握用冲击响应不变法和双线性变换法设计IIR滤波器的方法。

(4)掌握用窗函数法和频率抽样法设计FIR滤波器的方法。

2. 实验内容及总结:1.滤波器结构:(1)IIR滤波器各种结构1、直接型结构例如直接型滤波器系统函数, 则有系数向量a=[1,a1,a2,a3],b=[b0,b1,b2], 利用:Y=filter[b,a,x]求信号x(n)通过此滤波器的输出。

2、由系统函数或差分方程求系统的二阶分式(含一阶分式)的级联结构将例如的系统函数重写为二阶分式节的级联型, 利用:[sos,G]=tf2sos(b,a)3、由二阶分式的级联结构转换成系统函数的直接结构是第二步的逆运算, 调用函数:[b,a] = sos2tf(sos)可以求得系数向量a,b, 从而得到H(z)4、由系统函数求部分分式展开(留数及其极点计算)即求z反变换的部分分式展开法, 利用:[r,p,c]=residuez(b,a)其中极点为p, 留数为r, 直接项系数为c。

5、由r,p,c求系统函数即第4步的逆运算, 利用:[b,a]=residuez(r,p,c)6、由直接型结构转换为并联型结构需开发函数:[C,B,A]=tf2par(b,a)其中, b,a为直接型的系数向量, C,B,A为并联型实系数向量, 基本思想是: 1.反复调用[r,p,c]=residuez(b,a)求出极点及留数;2.利用cplxpair函数把极点、留数对按复共轭极点-留数对, 实极点-留数对的顺序排列;3.开发cplxcomp函数, 保证极点和留数相互对应;4.调用[b,a]=residuez(r,p,c)计算并联二阶节的分子分母。

7、由并联型结构转换成直接型结构开发函数:[b,a]=par2tf(C,B,A)为[C,B,A]=tf2par(b,a)的逆函数。

DSP实验报告_6

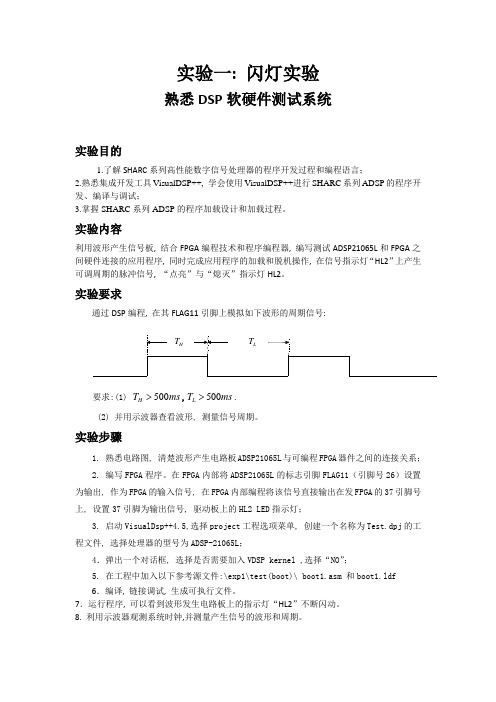

实验一: 闪灯实验熟悉DSP 软硬件测试系统实验目的1.了解SHARC 系列高性能数字信号处理器的程序开发过程和编程语言;2.熟悉集成开发工具VisualDSP++, 学会使用VisualDSP++进行SHARC 系列ADSP 的程序开发、编译与调试;3.掌握SHARC 系列ADSP 的程序加载设计和加载过程。

实验内容利用波形产生信号板, 结合FPGA 编程技术和程序编程器, 编写测试ADSP21065L 和FPGA 之间硬件连接的应用程序, 同时完成应用程序的加载和脱机操作, 在信号指示灯“HL2”上产生可调周期的脉冲信号, “点亮”与“熄灭”指示灯HL2。

实验要求通过DSP 编程, 在其FLAG11引脚上模拟如下波形的周期信号:要求:(1) 500H T ms >,500L T ms >. (2) 并用示波器查看波形, 测量信号周期。

实验步骤1. 熟悉电路图, 清楚波形产生电路板ADSP21065L 与可编程FPGA 器件之间的连接关系;2. 编写FPGA 程序。

在FPGA 内部将ADSP21065L 的标志引脚FLAG11(引脚号26)设置为输出, 作为FPGA 的输入信号, 在FPGA 内部编程将该信号直接输出在发FPGA 的37引脚号上, 设置37引脚为输出信号, 驱动板上的HL2 LED 指示灯;3. 启动VisualDsp++4.5,选择project 工程选项菜单, 创建一个名称为Test.dpj 的工程文件, 选择处理器的型号为ADSP-21065L ;4.弹出一个对话框, 选择是否需要加入VDSP kernel ,选择“NO ”;5. 在工程中加入以下参考源文件:\exp1\test(boot)\ boot1.asm 和boot1.ldf 6.编译, 链接调试, 生成可执行文件。

7.运行程序, 可以看到波形发生电路板上的指示灯“HL2”不断闪动。

8. 利用示波器观测系统时钟,并测量产生信号的波形和周期。

DSP实验报告(综合)

实验报告||实验名称 D SP课内系统实验课程名称DSP系统设计||一、实验目的及要求1. 掌握用窗函数法设计FIR数字滤波器的原理和方法。

熟悉线性相位FIR 数字滤波器特性。

了解各种窗函数对滤波器特性的影响。

2. 掌握设计IIR数字滤波器的原理和方法。

熟悉IIR数字滤波器特性。

了解IIR数字滤波器的设计方法。

3.掌握自适应数字滤波器的原理和实现方法。

掌握LMS自适应算法及其实现。

了解自适应数字滤波器的程序设计方法。

4.掌握直方图统计的原理和程序设计;了解各种图像的直方图统计的意义及其在实际中的运用。

5.了解边缘检测的算法和用途,学习利用Sobel算子进行边缘检测的程序设计方法。

6.了解锐化的算法和用途,学习利用拉普拉斯锐化运算的程序设计方法。

7.了解取反的算法和用途,学习设计程序实现图像的取反运算。

8.掌握直方图均衡化增强的原理和程序设计;观察对图像进行直方图均衡化增强的效果。

二、所用仪器、设备计算机,dsp实验系统实验箱,ccs操作环境三、实验原理(简化)FIR:有限冲激响应数字滤波器的基础理论,模拟滤波器原理(巴特沃斯滤波器、切比雪夫滤波器、椭圆滤波器、贝塞尔滤波器)。

数字滤波器系数的确定方法。

IIR:无限冲激响应数字滤波器的基础理论。

模拟滤波器原理(巴特沃斯滤波器、切比雪夫滤波器、椭圆滤波器、贝塞尔滤波器)。

数字滤波器系数的确定方法。

、自适应滤波:自适应滤波器主要由两部分组成:系数可调的数字滤波器和用来调节或修正滤波器系数的自适应算法。

e(n)=z(n)-y(n)=s(n)+d(n)-y(n)直方图:灰度直方图描述了一幅图像的灰度级内容。

灰度直方图是灰度值的函数,描述的是图像中具有该灰度值的像素的个数,其横坐标表示像素的灰度级别,纵坐标是该灰度出现的频率(像素个数与图像像素总数之比)。

图像边缘化:所谓边缘(或边沿)是指其周围像素灰度有阶跃变化。

经典的边缘提取方法是考察图像的每个像素在某个邻域内灰度的变化,利用边缘临近一阶或二阶方向导数变化规律,用简单的方法检测边缘。

DSP实验报告(一)

实验一 信号系统及系统响应一、实验目的1、 熟悉理想采样的性质,了解信号采样前后的频谱变化,加深对采样定理的理解。

2、 熟悉离散信号和系统的时域特性。

3、 熟悉线性卷积的计算编程方法:利用卷积的方法,观察、分析系统响应的时域特性。

4、 掌握序列傅氏变换的计算机实现方法,利用序列的傅氏变换对离散信号、系统及系统响应进行频域分析。

二、实验原理(一)连续时间信号的采样采样是指按一定的频率从模拟信号抽样获得数字信号。

采样是从连续时间信号到离散时间信号的过渡桥梁。

对一个连续时间信号进行理想采样的过程可以表示为该信号的一个周期冲激脉冲的乘积,即()()()ˆa a x t x t M t =(1)其中连续信号的理想采样,是周期冲激脉冲()()n M t t n T d +=-=-å(2)它也可以用傅立叶级数表示为:1()s jm tn M t eT+W =-=å(3)其中T 为采样周期,Ω是采样角频率。

设是连续时间信号的双边拉氏变换,即有:()()ata a X s x t edt+--=ò(4)此时理想采样信号的拉氏变换为()ˆˆ()()1ˆ()1ˆ()1()s s ataa jm tsta m s jm ta m a s m X s x t e dtxt ee dtTxt e dtT X s jm T+--++W -=--++--W =- -++=--====-W òåòåòåò(5)作为拉氏变换的一种特例,信号理想采样的傅立叶变换1ˆ()[()]aa s m X j X j m T+=-W =W-W å(6)由式(5)和式(6)可知,信号理想采样后的频谱是原信号频谱的周期延拓,其延拓周期等于采样频率。

根据Shannon 取样定理,如果原信号是带限信号,且采样频率高于原信号最高频率分量的2倍,则采样以后不会发生频谱混淆现象。

DSP实验报告3

一种有效的语音信号变调算法及其DSP实现一、实验目的熟悉TMS320VC5402指令体系,熟悉实验开发板的硬件组成,并开发应用程序二、实验设备TMS320VC5402实验板一套,ICETEC_5100USB仿真器一套,电源一个三、实验内容1.使用到的硬件介绍TMS320VC5402是TI公司推出的新一代定点数字信号处理器,采用先进的修正哈佛结构,在片存储器和在片外围电路等硬件,具有功耗低、高度并行等优点。

EPM7128QC100-10是ALTRA公司生产的高性能基于EEPROM可编程逻辑器件,S系列支持JTAG调试,片内可使用门2500个,128个宏单元,10ns响应延迟,引脚电压3.3/5.0V可控等性能。

AD/DA转换使用的是TI公司生产的高性能CODEC芯片,支持模拟电路接口和商业应用,16位宽AD/DA转换,串行编程,89dB信噪比,最高转换频率22.05KHz。

2.程序算法本实验程序的目的是进行声音的变调处理(包括升调和降调),原理图见图1(图1)变调处理原理框图在频域中,如果平移距离过小,平移后的频谱就会有一部分相互交叠,从而使新合成的频谱与原频谱不一致,因而无法准确地恢复原时域信号,这种现象称为混叠。

原因是采样频率fs 太低,原模拟信号不是有限带宽的信号;采取的措施有(1)对非有限带宽的模拟信号,在采样之前先通过模拟低通滤波器滤去高频成分,使其成为带限信号。

这种处理称为抗混叠滤波预处理。

(2)满足采样定理,即fs>=2fh,一般采样频率大大高于信号最高频率DSP变调算法:方案一:利用FFT和IFFT变换,在频域内进行变调处理,算法主要流程是对每帧信号的FFT转换进行展开平移以改变信号的频率特性,图2显示的是升调1.35倍前后的信号谱低频部分(0-3KHz),可以清楚的看到信号的频率向高频方向移动,但噪声干扰明显增加,并能够听到截断噪声。

利用此方法的优点是能够在频率域上对信号进行处理,能够全面反映信号内部特征,在一帧内部可以得到满意的效果;缺点是处理过的数据进行IFFT变换,误差很大,并引入了很多噪音,并且FFT和IFFT在定点处理器中使用误差很大,选取的基点较少时误差不能承受,选取基点较多时,消耗很多的CPU 和RAM资源,不适宜实时处理。

DSP实验报告5_2

DSP 第五次实验1.实验目的:(1)进一步熟悉matlab 实验环境和语言。

(2)掌握求序列圆周翻褶的MATLAB 方法。

(3)掌握求序列DFT 及IDFT 矩阵的MATLAB 方法。

(4)掌握用MATLAB 求解用圆周卷积计算线性卷积的时域的方法。

(5)掌握用FFT 计算有限长序列的线性卷积和线性相关的方法。

2.实验内容及总结:1.圆周翻褶【例3.27】 已知()[2,3,4,5,6],8X n N ==,求x(n)的8点圆周翻褶序列88(())()x n R n -。

代码:clc;clear allx=[2,3,4,5,6];N=8;x=[x,zeros(1,N-length(x))];nx=0:N-1y=x(mod(-nx,N)+1);subplot(121),stem([0:N-1],x);title('原序列');xlabel('n');ylabel('x(n)');grid;subplot(122),stem([0:N-1],y);title('圆周翻褶序列');xlabel('n');ylabel('x((n))8 R8(n)');grid;结果:总结:对于圆周翻褶(0),0()(())()(),11N Nx ny n x n R nx N n n N==-=⎨-≤≤-MA TLAB可用y=x(mode(-nx,N)+1)求得。

因此,要求X(n)=[2,3,4,5,6],N=8的8点圆周翻褶序列,要先将x(n)补零到8点长度再求圆周翻褶。

x=[x,zeros(1,N-length(x))];nx=0:N-1 %x补零到8点长y=x(mod(-nx,N)+1); %圆周翻褶从一开始,因此得到8点长%序列,应该再加一2.DFT矩阵,IDFT矩阵【例3.29】已知N=4的DFT矩阵w4,求IDFT矩阵w4I。

DSP实验报告

DSP第一次上机实验报告班级:学号:姓名:第一部分:实验要求(1) 常用数字信号序列的产生:熟悉Matlab产生数字信号的基本命令,加深对数字信号概念的理解,并能够用Matlab 产生和绘制出一些常用离散信号序列。

请用Matlab画出下列序列的波形(-10<n<10):a) δ(n)b) 单位阶跃序列2 u(n-5)c) 矩形序列R(n)d) y(n)=2sin(0.3πn)+ 0.5cos2(0.6πn)(2) 数字信号的基本运算:加、减、尺度(乘除)和移位是数字信号处理中最基本的算术运算,将上述基本序列进行这些基本运算,得到多个序列构成的组合序列。

请用您的计算机声卡采用一段您自己的声音x(n),长度为45秒,单声道,取样频率44.1kHz,16bit/样值,然后与给定的一段背景音乐y(n) 按下式叠加为一个声音信号z(n):z(n) = 0.7x(n) + 0.3y(n)第二部分:代码及结果截图(a)单位冲激函数δ(n)(b)单位阶跃序列2 u(n-5)c) 矩形序列R(n)d) y(n)=2sin(0.3πn)+ 0.5cos2(0.6πn)组合序列-10-8-6-4-20246810音频处理>> [r,fs,bits]=wavread('Recordd.wav');%读取Recordd文件并赋给变量r,作为录音文件[b,fs,bits]=wavread('adele');% 读取adele文件并赋给变量b,作为背景音乐x=r((fs*0+1:fs*45),:);%录音提取1s到45sy=b((fs*45+1:fs*90),:);%背景音乐提取1s到90sz=0.7*x+0.3*y;%叠加一个声音信号wavwrite(z,fs,bits,'music.wav');subplot(3,1,1),plot(x),title('record');subplot(3,1,2),plot(y),title('background');subplot(3,1,3),plot(z),title('music');%作图0.511.52 2.53 3.54x 105-101record0.511.52 2.53 3.54x 105-101background0.511.522.533.54x 105-101music。

DSP实验报告(二)

DSP实验报告(二)实验二应用FFT对信号进行频谱分析一、实验目的1、在理论学习的基础上,通过本次实验,加深对快速傅里叶变换的理解,熟悉FFT算法及其程序的编写。

2、熟悉应用FFT对典型信号进行频谱分析的方法。

3、了解应用FFT进行信号频谱分析过程中可能出现的问题,以便在实际中正确应用FFT。

二、实验原理与方法①一个连续信号的频谱可以用它的傅立叶变换表示为+ Xa(jW)=-jWtx(t)edtòa-如果对该信号进行理想采样,可以得到采样序列x(n)=xa(nT)同样可以对该序列进行z变换,其中T为采样周期X(z)=+ x(n)z-n+ -令z为ejw,则序列的傅立叶变换X(ejw)=x(n)ejwn-其中ω为数字频率,它和模拟域频率的关系为w=WT=W/fs式中的是采样频率。

上式说明数字频率是模拟频率对采样率的归一化。

同模拟域的情况相似。

数字频率代表了序列值变化的速率,而序列的傅立叶变换称为序列的频谱。

序列的傅立叶变换和对应的采样信号频谱具有下式的对应关系。

1X(e)=Tjw+ - w-2pXa(j)T即序列的频谱是采样信号频谱的周期延拓。

从式可以看出,只要分析采样序列的谱,就可以得到相应的连续信号的频谱。

注意:这里的信号必须是带限信号,采样也必须满足Nyquist定理。

在各种信号序列中,有限长序列在数字信号处理中占有很重要的地位。

无限长的序列也往往可以用有限长序列来逼近。

有限长的序列可以使用离散傅立叶变换。

当序列的长度是N时,定义离散傅立叶变换为:X(k)=DFT[x(n)]=其中W=e2pj-NN-1n=0WNkn它的反变换定义为:1x(n)=IDFT[X(k)]=N根据式和,则有N-1n=0X(k)WNknX(z)|z=Wnk=NN-1n=0x(n)WNnk=DFT[x(n)]j2pN可以得到X(k)2pk的点,就NN是将单位圆进行N等分以后第k个点。

所以,X(k)是z变换在单位圆上的等距采样,或者说是序列傅立叶变换的等距采样。

DSP实验报告

[《DSP原理及应用》课程实验报(软、硬件实验)实验名称:[《DSP原理及应用》实验]专业班级:[ ]学生姓名:[ ]学号:[ ]指导教师:[ ]完成时间:[ ]目录第一部分.基于DSP系统的实验 (1)实验3.1:指示灯实验 (1)实验3.2:DSP的定时器 (3)实验3.5 单路,多路模数转换(AD) (5)第二部分.DSP算法实验 (13)实验5.1:有限冲击响应滤波器(FIR)算法实验 (13)实验5.2:无限冲激响应滤波器(IIR)算法 (17)实验5.3:快速傅立叶变换(FFT)算法 (20)第一部分.基于DSP系统的实验实验3.1:指示灯实验一.实验目的1.了解ICETEK–F2812-A评估板在TMS320F2812DSP外部扩展存储空间上的扩展。

2.了解ICETEK–F2812-A评估板上指示灯扩展原理。

1.学习在C语言中使用扩展的控制寄存器的方法。

二.实验设备计算机,ICETEK-F2812-A实验箱(或ICETEK仿真器+ICETEK–F2812-A系统板+相关连线及电源)。

三.实验原理1.TMS320F2812DSP的存储器扩展接口存储器扩展接口是DSP扩展片外资源的主要接口,它提供了一组控制信号和地址、数据线,可以扩展各类存储器和存储器、寄存器映射的外设。

-ICETEK–F2812-A评估板在扩展接口上除了扩展了片外SRAM外,还扩展了指示灯、DIP开关和D/A设备。

具体扩展地址如下:C0002-C0003h:D/A转换控制寄存器C0001h:板上DIP开关控制寄存器C0000h:板上指示灯控制寄存器详细说明见第一部分表1.7。

-与ICETEK–F2812-A评估板连接的ICETEK-CTR显示控制模块也使用扩展空间控制主要设备:108000-108004h:读-键盘扫描值,写-液晶控制寄存器108002-108002h:液晶辅助控制寄存器2.指示灯扩展原理3.实验程序流程图开始初始化DSP时钟正向顺序送控制字并延时四.实验步骤1.实验准备连接实验设备:请参看本书第三部分、第一章、二。

dsp实验报告

dsp实验报告DSP实验报告一、引言数字信号处理(Digital Signal Processing,DSP)是一种对数字信号进行处理和分析的技术。

它在许多领域中被广泛应用,如通信、音频处理、图像处理等。

本实验旨在通过实际操作,探索和理解DSP的基本原理和应用。

二、实验目的1. 理解数字信号处理的基本概念和原理;2. 掌握DSP实验平台的使用方法;3. 进行一系列DSP实验,加深对DSP技术的理解。

三、实验器材和软件1. DSP开发板;2. 电脑;3. DSP开发软件。

四、实验内容1. 实验一:信号采集与重构在此实验中,我们将通过DSP开发板采集模拟信号,并将其转换为数字信号进行处理。

首先,我们需要连接信号源和开发板,然后设置采样频率和采样时间。

接下来,我们将对采集到的信号进行重构,还原出原始模拟信号,并进行观察和分析。

2. 实验二:滤波器设计与实现滤波器是DSP中常用的模块,用于去除或增强信号中的特定频率成分。

在此实验中,我们将学习滤波器的设计和实现方法。

首先,我们将选择合适的滤波器类型和参数,然后使用DSP开发软件进行滤波器设计。

最后,我们将将设计好的滤波器加载到DSP开发板上,并进行实时滤波处理。

3. 实验三:频谱分析与频域处理频谱分析是DSP中常用的方法,用于分析信号的频率成分和能量分布。

在此实验中,我们将学习频谱分析的基本原理和方法,并进行实际操作。

我们将采集一个包含多个频率成分的信号,并使用FFT算法进行频谱分析。

然后,我们将对频谱进行处理,如频率选择、频率域滤波等,并观察处理后的效果。

4. 实验四:音频处理与效果实现音频处理是DSP中的重要应用之一。

在此实验中,我们将学习音频信号的处理方法,并实现一些常见的音频效果。

例如,均衡器、混响、合唱等。

我们将使用DSP开发软件进行算法设计,并将设计好的算法加载到DSP开发板上进行实时处理。

五、实验结果与分析通过以上实验,我们成功完成了信号采集与重构、滤波器设计与实现、频谱分析与频域处理以及音频处理与效果实现等一系列实验。

北京信息科技大学DSP实验二

实验报告课程名称DSP原理与应用实验项目FIR算法的DSP实现指导教师学院信息与通信工程 _专业电子信息工程班级/学号学生姓名实验日期成绩_______________________实验2 FIR算法的DSP实现一、实验目的1.掌握汇编语言的编程方法。

2.掌握C语言和汇编语言的混合编程。

3.利用MATLAB设计FIR滤波器。

4.编写以浮点和Q15格式产生混合波形数据的函数。

5.编写C语言浮点实现FIR滤波算法函数。

6.编写C可调用汇编语言定点实现FIR滤波器算法函数。

7.使用CCS图形显示窗口观察和分析信号波形及其频谱。

8.进行代码性能测评。

二、实验仪器及工具计算机,安装Windows XP 操作系统、MATLAB 7.0.1、TI 的TMS320C5000 DSP 的开发软件CCS2.21;ICETEK-VC5509教学实验箱。

三、实验内容1.利用MATLAB设计FIR滤波器,以浮点和Q15格式导出滤波器系数。

2.FIR算法的TMS320C55x DSP的C语言浮点及汇编语言定点实现。

四、实验步骤1.编写MATLAB程序,利用MATLAB设计FIR低通或高通滤波器,以浮点和Q15格式导出滤波器系数。

例:利用kaiser窗设计一个低通FIR数字滤波器,通带的范围是0Hz到1100Hz, 阻带的范围是1600 Hz到4000 Hz,通带的波纹最大为0.03,阻带的波纹最大为0.03 。

信号的抽样频率为8000 Hz。

可根据信号的频率更改滤波器的频率。

2.设置CCS为“C55x Cycle Accurate Simulator”软件仿真模式,打开CCS,创建工程,编写.cmd文件,编写主程序文件。

编写以浮点和Q15格式产生混合波形数据的函数。

如产生抽样频率为8000 Hz,600Hz、2000 Hz、2800 Hz的三种频率的混合波形数据,其中混合频率可以自行确定。

添加文件到工程中。

编译、调试、链接、加载、运行程序,使用观测窗查看波形数据;选择菜单View→Graph→Time/Frequency,在弹出的“Graph Property Dialog”对话框中进行相应的配置显示产生波形的时域和频域图。

dsp信号处理实验报告

dsp信号处理实验报告DSP信号处理实验报告一、引言数字信号处理(DSP)是一种将连续信号转换为离散信号,并对其进行处理和分析的技术。

在现代通信、音频处理、图像处理等领域中,DSP技术被广泛应用。

本实验旨在通过对DSP信号处理的实践,加深对该技术的理解与应用。

二、实验目的本实验旨在通过对DSP信号处理的实践,掌握以下内容:1. 学习使用DSP芯片进行信号采集和处理;2. 理解离散信号的采样和重构过程;3. 掌握常见的DSP信号处理算法和方法。

三、实验原理1. 信号采集与重构在DSP信号处理中,首先需要对模拟信号进行采样,将连续信号转换为离散信号。

采样过程中需要注意采样频率的选择,以避免混叠现象的发生。

采样完成后,需要对离散信号进行重构,恢复为连续信号。

2. DSP信号处理算法DSP信号处理涉及到多种算法和方法,如滤波、频谱分析、时域分析等。

其中,滤波是一种常见的信号处理方法,可以通过滤波器对信号进行去噪、增强等处理。

频谱分析可以将信号在频域上进行分析,了解信号的频率成分和能量分布。

时域分析则关注信号的时序特征,如幅值、相位等。

四、实验步骤1. 信号采集与重构在实验中,我们使用DSP芯片进行信号采集与重构。

将模拟信号输入DSP芯片的模拟输入端口,通过ADC(模数转换器)将模拟信号转换为数字信号。

然后,通过DAC(数模转换器)将数字信号转换为模拟信号输出。

2. 滤波处理为了演示滤波处理的效果,我们选择了一个含有噪声的信号进行处理。

首先,使用FIR滤波器对信号进行低通滤波,去除高频噪声。

然后,使用IIR滤波器对信号进行高通滤波,增强低频成分。

3. 频谱分析为了对信号的频率成分和能量分布进行分析,我们使用FFT(快速傅里叶变换)算法对信号进行频谱分析。

通过观察频谱图,可以了解信号的频率特性。

4. 时域分析为了对信号的时序特征进行分析,我们使用时域分析方法对信号进行处理。

通过计算信号的均值、方差、峰值等指标,可以了解信号的幅值、相位等特性。

DSP实验报告(四)

实验四 用窗函数设计FIR 滤波器一、实验目的1、熟悉FIR 滤波器设计的基本方法。

2、掌握用窗函数设计FIR 数字滤波器的原理及方法,熟悉相应的计算机高级语言编程。

3、熟悉线性相位FIR 滤波器的幅频特性和相位特性。

4、了解各种不同窗函数对滤波器性能的响应二、实验原理和方法(一)FIR 滤波器的设计IIR 滤波器的优异幅度响应,一般是以相位的非线性为代价的,非线性相位会引起频率色散。

FIR 滤波器具有严格的相位特性,这对于语音信号处理和数据传输是和重要的。

目前FIR 滤波器的设计方法主要有三种:窗函数法、频率取样法和切比雪夫等波纹逼近的最优化设计方法。

常用的是窗函数法和切比雪夫等波纹逼近的最优化设计方法。

窗函数法是从时域出发,用一个窗函数截取理想的hd(n)得到h(n),以有限长序列h(n)近似理想的hd(n);如果从频域出发,用理想的()j d H e ω在单位圆上等角度取样得到H(k),根据h(k)得到H(z)将逼近理想的hd(z),这就是频率取样法。

(二)窗函数设计法用窗函数设计滤波器首先要对滤波器提出性能指标。

一般是给定一个理想的频率响应()j d H e ω,使所设计的FIR 滤波器的频率响应()j H e ω去逼近所要求的理性的滤波器的响应()j d H e ω。

窗函数法设计的任务在于寻找一个可实现(有限长单位脉冲响应)h(n )的传递函数()()j j n n H e h n e ωω+∞-==∑去逼近理想的幅频响应。

一个理想的频率响应的傅立叶反变换201()()2j j n d d H n H e e d πωωωπ=⎰(1)所得到的理想单位脉冲响应h 往往是一个无限长序列。

对经过适当的加权、截断处理才能得到一个所需要的有限长脉冲响应序列。

对应不同的加权、截断,就有不同的窗函数。

所要寻找的滤波器脉冲响应就等于理想脉冲响应和窗函数的乘积,即()()()d h n h n w n = (2)由此可见,窗函数的性质就决定了滤波器的品质。

DSP实验报告(完美版)

DSP实验报告班级:11050641学号:姓名:指导教师:实验一、二 DSP芯片的开发工具及应用实验1.实验目的(1)熟悉CCS集成开发环境,掌握工程的生成方法;(2)熟悉SEED-DTK DAD实验环境;(3)掌握CCS集成开发环境的调试方法。

2.实验设备DSP实验箱,计算机,CCS软件。

3.实验内容及步骤(1)CCS软件的安装;(2)了解SEED-DTK5416实验环境;(3)打开CCS集成开发环境,进入CCS的操作环境;(4)新建一个工程文件○1在c:\ti\myprojects中建立文件夹volume1(如果CCS安装在其他d:\ti ,则在d:\ti\myprojects中);○2将c:\ti\tutorial\target\volume1拷贝到c:\ti\myprojects\ volume1;○3从在CCS 中的Project 菜单,选择 New;○4在Project Name域中,键入volume1;○5在Location区域中,浏览步骤1所建立的工作文件夹;○6在Project Type 域中,选择Executable(.out);○7在Target域中,选择CCS配置的目标,并单击完成。

(5)向工程中添加文件○1从Project/Add Files to Project,选择 volume.c,单击Open(或右击Project View图标,选择Add Files to Project );○2选择Project/Add Files to Project,在Files of type对话框中,选择Asm Source Files (*.a*, *.s*)。

选择vectors.asm 和 load.asm, 单击Open;○3选择 Project/Add Files to Project,在Files of type 对话框中选择 Linker Command File (*.cmd),选择volume.cmd,单击Open。

dsp实验报告4

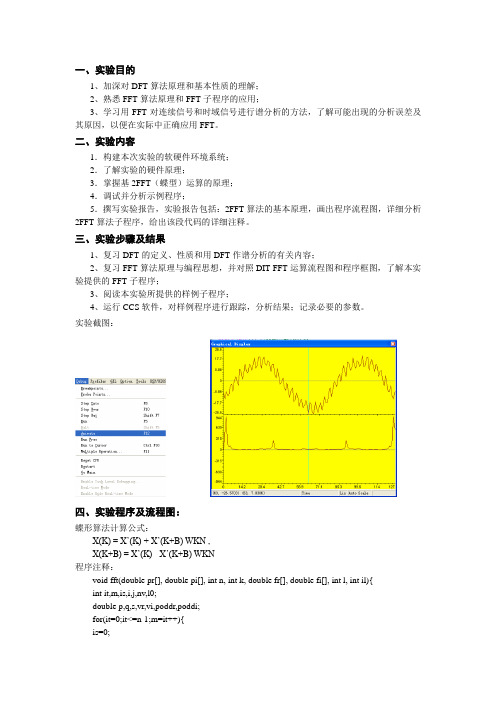

一、实验目的1、加深对DFT算法原理和基本性质的理解;2、熟悉FFT算法原理和FFT子程序的应用;3、学习用FFT对连续信号和时域信号进行谱分析的方法,了解可能出现的分析误差及其原因,以便在实际中正确应用FFT。

二、实验内容1.构建本次实验的软硬件环境系统;2.了解实验的硬件原理;3.掌握基2FFT(蝶型)运算的原理;4.调试并分析示例程序;5.撰写实验报告,实验报告包括:2FFT算法的基本原理,画出程序流程图,详细分析2FFT算法子程序,给出该段代码的详细注释。

三、实验步骤及结果1、复习DFT的定义、性质和用DFT作谱分析的有关内容;2、复习FFT算法原理与编程思想,并对照DIT-FFT运算流程图和程序框图,了解本实验提供的FFT子程序;3、阅读本实验所提供的样例子程序;4、运行CCS软件,对样例程序进行跟踪,分析结果;记录必要的参数。

实验截图:四、实验程序及流程图:蝶形算法计算公式:X(K) = X’(K) + X’(K+B) WKN ,X(K+B) = X’(K) - X’(K+B) WKN程序注释:void fft(double pr[], double pi[], int n, int k, double fr[], double fi[], int l, int il){int it,m,is,i,j,nv,l0;double p,q,s,vr,vi,poddr,poddi;for(it=0;it<=n-1;m=it++){is=0;for(i=0;i<=k-1;i++){j=m/2;is=2*is+(m-2*j);m=j;}fr[it]=pr[is];fi[it]=pi[is];}//-------------------该程序段的作用是另倒序存放pr[0]=1.0;pi[0]=0.0;p=6.283185306/n;pr[1]=cos(p);pi[1]=-sin(p);if (l)pi[1]=-pi[1];for(i=2;i<=n-1;i++){p=pr[i-1]*pr[1];q=pi[i-1]*pi[1];s=(pr[i-1]+pi[i-1])*(pr[1]+pi[1]);pr=p-q;pi=s-p-q;}计算WKN *X2(k),其中X2(k)是偶数部分,将其转换成c语言的形式r存实数部分,i 存虚数部分。

DSP实验报告完美版

DSP实验报告班级:学号:姓名:指导教师:实验一、二 DSP芯片的开发工具及应用实验1.实验目的(1)熟悉CCS集成开发环境,掌握工程的生成方法;(2)熟悉SEED-DTK DAD实验环境;(3)掌握CCS集成开发环境的调试方法。

2.实验设备DSP实验箱,计算机,CCS软件。

3.实验内容及步骤(1) CCS软件的安装;(2)了解SEED-DTK5416实验环境;(3)打开CCS集成开发环境,进入CCS的操作环境;(4)新建一个工程文件○1在c:\ti\myprojects中建立文件夹volume1(如果CCS安装在其他d:\ti ,则在d:\ti\myprojects中);○2将c:\ti\tutorial\target\volume1拷贝到c:\ti\myprojects\ volume1;○3从在CCS 中的Project 菜单,选择 New;○4在Project Name域中,键入volume1;○5在Location区域中,浏览步骤1所建立的工作文件夹;○6在Project Type 域中,选择Executable(.out);○7在Target域中,选择CCS配置的目标,并单击完成。

(5)向工程中添加文件○1从Project/Add Files to Project,选择 volume.c,单击 Open(或右击Project View图标,选择Add Files to Project );○2选择Project/Add Files to Project,在Files of type对话框中,选择Asm Source Files (*.a*, *.s*)。

选择vectors.asm 和 load.asm, 单击Open;○3选择 Project/Add Files to Project,在Files of type 对话框中选择 Linker Command File (*.cmd),选择volume.cmd,单击Open。

DSP实验四(1)(精)

北京电子科技学院(BESTI )实验报告课程: DSP 原理与应用班级: 1011 姓名:学号:成绩:指导教师:实验日期:实验密级:预习程度:实验时间: 10:10-12:40仪器组次:05必修/选修:必修实验序号:04实验名称:快速傅里叶变换实验目的与要求:能出现的分析误差及其原因,以便在实际中正确应用FFT 。

实验仪器:实验内容、步骤与体会(附纸):一、实验目的1.加深对DFT 算法原理和基本性质的理解; 2.熟悉FFT 算法原理和FFT 子程序的应用;3.学习用FFT 对连续信号和时域信号进行谱分析的方法,了解可能出现的分析误差及其原因,以便在实际中正确应用FFT 。

二、实验内容1. 构建本次实验的软硬件环境系统;2. 了解实验的硬件原理;3. 掌握基2FFT (蝶型)运算的原理;4. 调试并分析示例程序;三、基本原理1. 离散傅立叶变换DFT 的定义:将时域的采样变换成频域的周期性离散函数,频域的采样也可以变换成时域的周期性离散函数,这样的变换称为离散傅立叶变换,简称DFT 。

2. FFT 是DFT 的一种快速算法,将DFT 的N 2步运算减少为(N/2)log 2N 步,极大的提高了运算的速度。

3. 旋转因子的变化规律。

4. 蝶形运算规律。

5. 基2FFT 算法。

四、实验步骤1. 启动CCS2.0,Project/Open打开“Algorithm ”目录中“exp01_cpu2”子目录下“exp01.pjt ”工程文件;双击“exp01.pjt ” 及“Source ”可查看各源程序;加载“exp01.out ”;在中断子程序中,flag=0处设置断点;单击“Run ”运行程序,程序将运行至断点处停止, 如图所示;2. View / Graph / Time/Frequency打开一个图形观察窗口;设置该观察图形窗口变量及参数;采用双踪观察在启始地址分别为x 和mo ,长度为128的单元中数值的变化,数值类型为32位浮点数,这两段存储单元中分别存放的是经A/D转换后的输入信号和对该信号进行FFT 变换的结果;3. 单击“Animate ”运行程序,或按F10运行;调整模拟信号源的频率、幅值、种类观察窗口并观察输入信号波形及其FFT 变换结果;单击“Halt ”暂停程序运行,关闭窗口,本实验结束,如图所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CpuTimer0Regs.TCR.bit.FREE=1;

CpuTimer0Regs.TCR.bit.TRB=1;

CpuTimer0RegsБайду номын сангаасTCR.bit.TIE=1;

CpuTimer0.InterruptCount=0;

startCpuTimer0();

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

{

CpuTimer0.InterruptCount++;

// Acknowledge this interrupt to receive more interrupts from group 1

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

CpuTimer0Regs.TCR.bit.TIF=1;

ConfigCpuTimer(&CpuTimer0, 100, 1000000);

#endif

CpuTimer0Regs.PRD.all=0xffff;

CpuTimer0Regs.TPR.all=0;

CpuTimer0Regs.TIM.all=0;

CpuTimer0Regs.TPRH.all=0;

CpuTimer0Regs.TCR.bit.TSS=1;

通过本次实验熟悉了F28335A的定时器、掌握了F28335A定时器的控制方法、掌握了F28335A的中断结构和对中断的处理流程、学会了C语言中断程序设计,以及运用中断方法的程序流程对老师上课讲解的程序加深了理解。

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

//interrupt void cpu_timer1_isr(void);

//interrupt void cpu_timer2_isr(void);

//#define mem (*(unsigned short int *)0x200000)

#define LED (*(unsigned short int *)0x180000)

可屏蔽中断:可以用软件加以屏蔽或解除屏蔽。

不可屏蔽中断:这些中断不能够被屏蔽,将立即响应该类中断并转入相应的子程序去执行。

4.中断的优先级

如果多个中断被同时激发,将按照他们的中断优先级来提供服务。中断优先级是芯片内部已定义好的,不可修改。

4.实验步骤:

1.采用中断方式实现指示灯显示十六进制数0-F。

2.采用中断方式实现指示灯从左到右间隔一定时间的定时闪烁。

3.实验程序参考流程图如图所示。

4.改变“CpuTimer0Regs.PRD.all = 0xffff;”中的值。重新执行程序,观察实验现象。

5.实验结果及分析:

【实验程序】

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

InitXintf16Gpio();//zq

// Step 3. Clear all interrupts and initialize PIE vector table:

CpuTimer0Regs.TCR.bit.TRB=1;

if(ncount==0)

{ LED=uLBD;

uLBD++;uLBD%=16;

}

ncount++;ncount%=194;

}

6.问题与思考

1.指示灯在定时器的定时中断中如何实现定时闪烁。

使用一个定时器中断,让led的开关时间通过程序控制

7.实验总结:

b.响应中断。必须能够响应中断请求。如果中断是可屏蔽的,则必须满足一定的条件,按照一定的顺序去执行。而对于非可屏蔽中断和软件中断,会立即做出响应。

c.准备执行中断服务程序并保存寄存器的值。

d.执行中断服务子程序。调用相应的中断服务程序ISR,进入预先规定的向量地址,并且执行已写好的ISR。

3.中断类别

北京信息科技大学

自动化学院

实验报告

课程名称DSP

实验名称CPU定时器实验

实验仪器计算机,ICETEK-F28335-A实验箱

专业自动化

班级/学号

学生姓名

实验日期

实验地点实验室102

成绩

指导教师

北京信息科技大学

自动化学院

(DSP)实验报告

专业:自动化班级:学号:姓名:

实验名称

CPU定时器实验

实验地点

实验室102

TMS320F28335A内部有三个32位通用定时器(TIMER0/1/2),定时器1和2被保留给实时操作系统(DSPBIOS)用,只有定时器0可以提供给用户使用。

2.中断响应过程

a.接收中断请求。必须由软件中断(从程序代码)或硬件中断(从一个引脚或一个基于芯片的设备)提出请求去暂停当前主程序的执行。

IER |= M_INT1;

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

for(;;)

{

}

}

interrupt void cpu_timer0_isr(void)

InitPieVectTable();

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS; // This is needed to disable write to EALLOW protected registers

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

// Prototype statements for functions found within this file.

interrupt void cpu_timer0_isr(void);

#define startCpuTimer0() CpuTimer0Regs.TCR.bit.TSS=0

int i=0,ncount;

unsigned int uLBD;

void main(void)

{

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

InitCpuTimers(); // For this example, only initialize the Cpu Timers

#if (CPU_FRQ_150MHZ)

ConfigCpuTimer(&CpuTimer0, 150, 1000000);

#endif

#if (CPU_FRQ_100MHZ)

实验时间

1.实验目的:

1.通过实验熟悉F28335A的定时器;

2.掌握F28335A定时器的控制方法;

3.掌握F28335A的中断结构和对中断的处理流程;

4.学会C语言中断程序设计,以及运用中断方法的程序流程

2.实验设备:

计算机,ICETEK-F28335-A实验箱。

3.实验原理及内容:

1.通用定时器介绍及其控制方法

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

// Disable CPU interrupts

DINT;

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags