s3c2440芯片中文手册-11 UART

s3c2410s3c2440处理器介绍

鲁东大学 LUDONG UNIVERSITY

S3C2410A结构框图

S3c2440处理 器结构框图

❖ S3C2410A在片上,S3通C过24A1M0ABA简总介线集成了以下资源:

AHB总线-各类控制器

✓支持STN和TFT的LCD控制器 ✓ NAND Flash 控制器 ✓存储管理器(片选逻辑和SDRAM控制器) ✓时钟及电源管理器

APB总线-设备与接口 ✓ 3通道UART、 ✓ 4通道DMA、 ✓ 4通道PWM定时器、 ✓ I/O口、 ✓ RTC、

: 1M bps

CTS/RTS

Key

Debug

GPS

BT

Matrix

SRAM/ROM /NOR Flash /OneNAND/OneDRAM

1Gbit X 6banks (x8/x16/x32)

UART0 SMC

UART1

NAND

NAND Flash IF

SDRAM/mDDR

1Gbit X 2banks (x16/x32)

PMIC

Main Charger

Li-Ion

USB Charger

Control

Data

5V DC

5V USB

TV-out

TV

TFT/CSTN LCDC + SPI(GPIO) + TSADC RGB I/F

Main TFT LCD & TSP

1/2/4/8/16 bpp Up to QVGA

SD/SDIO IIS I/F

✓ I2C总线接口、 ✓ I2S总线接口、 ✓ USB主设备、USB从设备 ✓ SD主卡和MMC(Multi Media Card,多媒体卡)卡接口 ✓2通道的SPI接口)

SPI驱动程序(S3C2440)

2410_SPI接口与linux驱动以下先从下到上的进行分析:driver/spi下有两个底层相关的spi驱动程序:spi_s3c24xx.c和spi_s3c24xx_gpio.c其中spi_s3c24xx.c是基于s3c24xx下相应的spi接口的驱动程序,spi_s3c24xx_gpio.c允许用户指定3个gpio口接口,模拟标准的spi总线。

s3c2410自带了两个spi接口(spi0和spi1),在此我只研究基于s3c2410下spi接口的驱动程序spi_s3c24xx.c。

首先从spi驱动的检测函数进行分析:static int s3c24xx_spi_probe(struct platform_device *pdev){struct s3c24xx_spi *hw;struct spi_master *master;struct spi_board_info *bi;struct resource *res;int err = 0;int i;master = spi_alloc_master(&pdev->dev, sizeof(struct s3c24xx_spi)); if (master == NULL) {dev_err(&pdev->dev, "No memory for spi_master\n");err = -ENOMEM;goto err_nomem;}hw = spi_master_get_devdata(master);memset(hw, 0, sizeof(struct s3c24xx_spi));hw->master = spi_master_get(master);hw->pdata = pdev->dev.platform_data;hw->dev = &pdev->dev;if (hw->pdata == NULL) {dev_err(&pdev->dev, "No platform data supplied\n");err = -ENOENT;goto err_no_pdata;}platform_set_drvdata(pdev, hw);//dev_set_drvdata(&pdev->dev, hw) init_completion(&hw->done);hw->bitbang.master = hw->master;hw->bitbang.setup_transfer = s3c24xx_spi_setupxfer;hw->bitbang.chipselect = s3c24xx_spi_chipsel;hw->bitbang.txrx_bufs = s3c24xx_spi_txrx;hw->bitbang.master->setup = s3c24xx_spi_setup;dev_dbg(hw->dev, "bitbang at %p\n", &hw->bitbang);res = platform_get_resource(pdev, IORESOURCE_MEM, 0);if (res == NULL) {dev_err(&pdev->dev, "Cannot get IORESOURCE_MEM\n");err = -ENOENT;goto err_no_iores;}hw->ioarea = request_mem_region(res->start, (res->end - res->start)+1, pdev->name);if (hw->ioarea == NULL) {dev_err(&pdev->dev, "Cannot reserve region\n");err = -ENXIO;goto err_no_iores;}hw->regs = ioremap(res->start, (res->end - res->start)+1);if (hw->regs == NULL) {dev_err(&pdev->dev, "Cannot map IO\n");err = -ENXIO;goto err_no_iomap;}hw->irq = platform_get_irq(pdev, 0);if (hw->irq < 0) {dev_err(&pdev->dev, "No IRQ specified\n");err = -ENOENT;goto err_no_irq;}err = request_irq(hw->irq, s3c24xx_spi_irq, 0, pdev->name, hw);if (err) {dev_err(&pdev->dev, "Cannot claim IRQ\n");goto err_no_irq;}hw->clk = clk_get(&pdev->dev, "spi");if (IS_ERR(hw->clk)) {dev_err(&pdev->dev, "No clock for device\n");err = PTR_ERR(hw->clk);goto err_no_clk;}clk_enable(hw->clk);writeb(0xff, hw->regs + S3C2410_SPPRE);writeb(SPPIN_DEFAULT, hw->regs + S3C2410_SPPIN);writeb(SPCON_DEFAULT, hw->regs + S3C2410_SPCON);s3c2410_gpio_setpin(S3C2410_GPE13, 0);s3c2410_gpio_setpin(S3C2410_GPE12, 0);s3c2410_gpio_cfgpin(S3C2410_GPE13, S3C2410_GPE13_SPICLK0); s3c2410_gpio_cfgpin(S3C2410_GPE12, S3C2410_GPE12_SPIMOSI0); s3c2410_gpio_cfgpin(S3C2410_GPE11, S3C2410_GPE11_SPIMISO0);if (!hw->pdata->set_cs) {s3c2410_gpio_setpin(hw->pdata->pin_cs, 1);s3c2410_gpio_cfgpin(hw->pdata->pin_cs, S3C2410_GPIO_OUTPUT); }err = spi_bitbang_start(&hw->bitbang);if (err) {dev_err(&pdev->dev, "Failed to register SPI master\n");goto err_register;}dev_dbg(hw->dev, "shutdown=%d\n", hw->bitbang.shutdown);bi = &hw->pdata->board_info[0];for (i = 0; i < hw->pdata->board_size; i++, bi++) {dev_info(hw->dev, "registering %s\n", bi->modalias);bi->controller_data = hw;spi_new_device(master, bi);}return 0;err_register:clk_disable(hw->clk);clk_put(hw->clk);err_no_clk:free_irq(hw->irq, hw);err_no_irq:iounmap(hw->regs);err_no_iomap:release_resource(hw->ioarea);kfree(hw->ioarea);err_no_iores:err_no_pdata:spi_master_put(hw->master);;err_nomem:return err;}struct spi_master * __init_or_modulespi_alloc_master(struct device *dev, unsigned size) {struct spi_master *master;if (!dev)return NULL;master = kzalloc(size + sizeof *master, SLAB_KERNEL); if (!master)return NULL;class_device_initialize(&master->cdev);master->cdev.class = &spi_master_class;master->cdev.dev = get_device(dev);spi_master_set_devdata(master, &master[1]);return master;}int spi_bitbang_start(struct spi_bitbang *bitbang){int status;if (!bitbang->master || !bitbang->chipselect)return -EINVAL;INIT_WORK(&bitbang->work, bitbang_work, bitbang);spin_lock_init(&bitbang->lock);spi_new_device INIT_LIST_HEAD(&bitbang->queue);if (!bitbang->master->transfer)bitbang->master->transfer = spi_bitbang_transfer;//spi数据的传输就是通过调用这个方法来实现的if (!bitbang->txrx_bufs) {bitbang->use_dma = 0;bitbang->txrx_bufs = spi_bitbang_bufs;if (!bitbang->master->setup) {if (!bitbang->setup_transfer)bitbang->setup_transfer =spi_bitbang_setup_transfer;bitbang->master->setup = spi_bitbang_setup;bitbang->master->cleanup = spi_bitbang_cleanup;}} else if (!bitbang->master->setup)return -EINVAL;bitbang->busy = 0;bitbang->workqueue = create_singlethread_workqueue(bitbang->master->cdev.dev->bus_id);if (bitbang->workqueue == NULL) {status = -EBUSY;goto err1;}status = spi_register_master(bitbang->master);if (status < 0)goto err2;return status;err2:destroy_workqueue(bitbang->workqueue);err1:return status;}int __init_or_modulespi_register_master(struct spi_master *master){static atomic_t dyn_bus_id = ATOMIC_INIT((1<<16) - 1);struct device *dev = master->cdev.dev;int status = -ENODEV;int dynamic = 0;if (!dev)return -ENODEV;if (master->bus_num < 0) {master->bus_num = atomic_dec_return(&dyn_bus_id); dynamic = 1;}snprintf(master->cdev.class_id, sizeof master->cdev.class_id, "spi%u", master->bus_num);status = class_device_add(&master->cdev);//注册设备if (status < 0)goto done;dev_dbg(dev, "registered master %s%s\n", master->cdev.class_id, dynamic ? " (dynamic)" : "");scan_boardinfo(master);status = 0;done:return status;}static void __init_or_modulescan_boardinfo(struct spi_master *master){struct boardinfo *bi;struct device *dev = master->cdev.dev;down(&board_lock);list_for_each_entry(bi, &board_list, list) {struct spi_board_info *chip = bi->board_info;unsigned n;for (n = bi->n_board_info; n > 0; n--, chip++) {if (chip->bus_num != master->bus_num)continue;if (chip->chip_select >= master->num_chipselect&& master->num_chipselect) {dev_dbg(dev, "cs%d > max %d\n",chip->chip_select,master->num_chipselect);continue;}(void) spi_new_device(master, chip);}}up(&board_lock);}int __initspi_register_board_info(struct spi_board_info const *info, unsigned n)struct boardinfo *bi;bi = kmalloc(sizeof(*bi) + n * sizeof *info, GFP_KERNEL);if (!bi)return -ENOMEM;bi->n_board_info = n;memcpy(bi->board_info, info, n * sizeof *info);down(&board_lock);list_add_tail(&bi->list, &board_list);up(&board_lock);return 0;}struct spi_device *__init_or_modulespi_new_device(struct spi_master *master, struct spi_board_info *chip){struct spi_device *proxy;//这个结构很重要,以后就是通过这个结构来操作实际的spi设备的struct device *dev = master->cdev.dev;int status;if (!spi_master_get(master))return NULL;proxy = kzalloc(sizeof *proxy, GFP_KERNEL);if (!proxy) {dev_err(dev, "can't alloc dev for cs%d\n",chip->chip_select);goto fail;}proxy->master = master;proxy->chip_select = chip->chip_select;proxy->max_speed_hz = chip->max_speed_hz;proxy->mode = chip->mode;proxy->irq = chip->irq;proxy->modalias = chip->modalias;snprintf(proxy->dev.bus_id, sizeof proxy->dev.bus_id,"%s.%u", master->cdev.class_id,chip->chip_select);proxy->dev.parent = dev;proxy->dev.bus = &spi_bus_type;proxy->dev.platform_data = (void *) chip->platform_data; proxy->controller_data = chip->controller_data;proxy->controller_state = NULL;proxy->dev.release = spidev_release;status = master->setup(proxy);if (status < 0) {dev_dbg(dev, "can't %s %s, status %d\n","setup", proxy->dev.bus_id, status);goto fail;}status = device_register(&proxy->dev);//真正注册原始设备if (status < 0) {dev_dbg(dev, "can't %s %s, status %d\n","add", proxy->dev.bus_id, status);goto fail;}dev_dbg(dev, "registered child %s\n", proxy->dev.bus_id); return proxy;fail:spi_master_put(master);kfree(proxy);return NULL;}static int s3c24xx_spi_setup(struct spi_device *spi){int ret;if (!spi->bits_per_word)spi->bits_per_word = 8;if ((spi->mode & SPI_LSB_FIRST) != 0)return -EINVAL;ret = s3c24xx_spi_setupxfer(spi, NULL);if (ret < 0) {dev_err(&spi->dev, "setupxfer returned %d\n", ret);return ret;}dev_dbg(&spi->dev, "%s: mode %d, %u bpw, %d hz\n",__FUNCTION__, spi->mode, spi->bits_per_word,spi->max_speed_hz);return 0;}static int s3c24xx_spi_setupxfer(struct spi_device *spi,struct spi_transfer *t){struct s3c24xx_spi *hw = to_hw(spi);unsigned int bpw;unsigned int hz;unsigned int div;bpw = t ? t->bits_per_word : spi->bits_per_word;hz = t ? t->speed_hz : spi->max_speed_hz;if (bpw != 8) {dev_err(&spi->dev, "invalid bits-per-word (%d)\n", bpw);return -EINVAL;}div = clk_get_rate(hw->clk) / hz;div = (div / 2) - 1;//求出预分频值if (div < 0)div = 1;if (div > 255)div = 255;dev_dbg(&spi->dev, "setting pre-scaler to %d (hz %d)\n", div, hz);writeb(div, hw->regs + S3C2410_SPPRE);//设置预分频值spin_lock(&hw->bitbang.lock);if (!hw->bitbang.busy) {hw->bitbang.chipselect(spi, BITBANG_CS_INACTIVE);//修改时钟,先禁用spi}spin_unlock(&hw->bitbang.lock);return 0;}static void s3c24xx_spi_chipsel(struct spi_device *spi, int value){struct s3c24xx_spi *hw = to_hw(spi);unsigned int cspol = spi->mode & SPI_CS_HIGH ? 1 : 0;unsigned int spcon;switch (value) {case BITBANG_CS_INACTIVE:if (hw->pdata->set_cs)hw->pdata->set_cs(hw->pdata, value, cspol);elses3c2410_gpio_setpin(hw->pdata->pin_cs, cspol ^ 1);break;case BITBANG_CS_ACTIVE:spcon = readb(hw->regs + S3C2410_SPCON);if (spi->mode & SPI_CPHA)spcon |= S3C2410_SPCON_CPHA_FMTB;elsespcon &= ~S3C2410_SPCON_CPHA_FMTB;if (spi->mode & SPI_CPOL)spcon |= S3C2410_SPCON_CPOL_HIGH;elsespcon &= ~S3C2410_SPCON_CPOL_HIGH;spcon |= S3C2410_SPCON_ENSCK;writeb(spcon, hw->regs + S3C2410_SPCON);if (hw->pdata->set_cs)hw->pdata->set_cs(hw->pdata, value, cspol);elses3c2410_gpio_setpin(hw->pdata->pin_cs, cspol);break;}}好了,至此spi主控制器(驱动)和板上spi设备注册完毕,以后要使用spi来传输数据的话,只要先获得spi设备交道了(就好像你要操作一个文件,先要获取文件句柄一样,明白吧^_^)原文地址/luofuchong/archive/2007/09/24/33942.html~~~~~~~~~~~~~~~~~~``任何SPI都有4种模式2008-11-06 22:17void McBSPObj::McBSP0Init(void)//McBSP从设备SPI硬件配置{//PCR设置过程(FSM=0,CLKM=0)McBSP0->SPSA = PCR;McBSP1->SPSD = (0 << PCR_XIOEN) //发送非通用I/O模式位| (0 << PCR_RIOEN) //接收非通用I/O模式位| (0 << PCR_FSXM) //外部发送帧同步脉冲(外部片选)| (0 << PCR_FSRM) //外部接收帧同步脉冲(外部片选)| (0 << PCR_CLKXM) //外部发送时钟(外部时钟源)| (0 << PCR_CLKRM) //外部接收时钟(外部时钟源)#if SPIMODE == 0//SPI设置过程00(0--FS高电平有效,0--CLK上升沿收发数据)| (0 << PCR_FSXP) //发送帧同步脉冲极性(高电平有效)| (0 << PCR_FSRP) //接收帧同步脉冲极性(高电平有效)| (0 << PCR_CLKXP) //发送时钟极性(上升沿发送数据)| (0 << PCR_CLKRP);//接收时钟极性(上升沿接收数据)#endif#if SPIMODE == 1//SPI设置过程01(0--FS高电平有效,1--CLK下降沿收发数据)| (0 << PCR_FSXP) //发送帧同步脉冲极性(高电平有效)| (0 << PCR_FSRP) //接收帧同步脉冲极性(高电平有效)| (1 << PCR_CLKXP) //发送时钟极性(下降沿发送数据)| (1 << PCR_CLKRP);//接收时钟极性(下降沿接收数据)#endif#if SPIMODE == 2//SPI设置过程10(1--FS低电平有效,0--CLK上升沿收发数据)| (1 << PCR_FSXP) //发送帧同步脉冲极性(低电平有效)| (1 << PCR_FSRP) //接收帧同步脉冲极性(低电平有效)| (0 << PCR_CLKXP) //发送时钟极性(上升沿发送数据)| (0 << PCR_CLKRP);//接收时钟极性(上升沿接收数据)#endif#if SPIMODE == 3//SPI设置过程11(1--FS低电平有效,1--CLK下降沿收发数据)| (1 << PCR_FSXP) //发送帧同步脉冲极性(低电平有效)| (1 << PCR_FSRP) //接收帧同步脉冲极性(低电平有效)| (1 << PCR_CLKXP) //发送时钟极性(下降沿发送数据)| (1 << PCR_CLKRP);//接收时钟极性(下降沿接收数据)#endif//MCR1设置过程(RMCM=0)McBSP0->SPSA = MCR1;//McBSP0->SPSD = (0 << MCR1_RMCM) //允许接收多通道选择(0)| (0x00 << MCR1_RPBBLK)| (0x00 << MCR1_RPABLK)| (0x00 << MCR1_RCBLK);//MCR2设置过程(XMCM=0)McBSP0->SPSA = MCR2;//McBSP0->SPSD = (0x00 << MCR2_XMCM) //允许发送多通道选择(00b) | (0x00 << MCR2_XPBBLK)| (0x00 << MCR2_XPABLK)| (0x00 << MCR2_XCBLK);//RCERA设置过程McBSP0->SPSA = RCERA;//McBSP0->SPSD = 0;//RCERB设置过程McBSP0->SPSA = RCERB;//McBSP0->SPSD = 0;//XCERA设置过程McBSP0->SPSA = XCERA;//McBSP0->SPSD = 0;//XCERB设置过程McBSP0->SPSA = XCERB;//McBSP0->SPSD = 0;//XCR1设置过程McBSP0->SPSA = XCR1;//McBSP0->SPSD = (0x00 << XCR1_XFRLEN1) //每帧1个字(每帧中断的次数1!!!) // | (0x02 << XCR1_XWDLEN1);//每字16位长(每次中断的字节数2!!!)| (0x00 << XCR1_XWDLEN1);//每字8位长(每次中断的字节数2!!!)//XCR2设置过程McBSP0->SPSA = XCR2;McBSP0->SPSD = (0 << XCR2_XPHASE) //单相帧(其他设置都为0)| (0x00 << XCR2_XCOMPAND)//发送数据从最高位(MSB)开始| (0x00 << XCR2_XDATDLY);//同步后延迟0位数据//RCR1设置过程McBSP0->SPSA = RCR1;McBSP0->SPSD = (0x00 << RCR1_RFRLEN1) //每帧1个字(每帧中断的次数1!!!) // | (0x02 << RCR1_RWDLEN1);//每字16位长(每次中断的字节数2!!!)| (0x00 << RCR1_RWDLEN1);//每字8位长(每次中断的字节数2!!!)//RCR2设置过程McBSP0->SPSA = RCR2;McBSP0->SPSD = (0 << RCR2_RPHASE) //单相帧(其他设置都为0)| (0x00 << RCR2_RCOMPAND)//接收数据从最高位(MSB)开始| (0x00 << RCR2_RDATDLY);//同步后延迟0位数据//SRGR1设置过程McBSP0->SPSA = SRGR1;McBSP0->SPSD = (0x00 << SRGR1_CLKGDV);//1//SRGR2设置过程McBSP0->SPSA = SRGR2;McBSP0->SPSD = (0 << SRGR2_FSGM)| (1 << SRGR2_CLKSM)//由CPU时钟产生的采样率时钟1| (0 << SRGR2_CLKSP)//0| (1 << SRGR2_GSYNC)//| (0x0f << SRGR2_FPER);//0x0f//SPCR1设置过程(CLKSTP=1Xb,RINTM=00b)McBSP0->SPSA = SPCR1;McBSP0->SPSD = (0x00 << SPCR1_RINTM) //接收中断模式00(每帧接收1次中? | (0 << SPCR1_DLB) //禁止回送| (1 << SPCR1_DXENA) //DX使能| (0x00 << SPCR1_RJUST) //接收符号不扩展| (0x02 << SPCR1_CLKSTP);//SPI模式时钟开始于上升沿(无延迟)//SPCR2设置过程(XINTM=02b)McBSP0->SPSA = SPCR2;McBSP0->SPSD = (0x02 << SPCR2_XINTM)//发送中断模式02| (1 << SPCR2_XEMPTY) //发送移位寄存器空| (1 << SPCR2_XRDY); //发送准备好//SPCR1复位过程McBSP0->SPSA = SPCR1;McBSP0->SPSD|= (1 << SPCR1_RRST);//接收器复位//SPCR2复位过程McBSP0->SPSA = SPCR2;McBSP0->SPSD|= (1 << SPCR2_XRST)//发送器复位| (1 << SPCR2_GRST)//采样率发生器复位| (1 << SPCR2_FRST);//帧同步发生器复位//清除允许BXINT0中断过程// SREG->IFR = (1 << IFR_BXINT0);//清除BXINT0中断标志// SREG->IMR |= (1 << IMR_BXINT0);//允许BXINT0中断//清除允许BRINT0中断过程SREG->IFR = (1 << IFR_BRINT0);//清除BRINT0中断标志SREG->IMR |= (1 << IMR_BRINT0);//允许BRINT0中断}void McBSPObj::McBSP1Init(void)//GPIO配置{McBSP1->SPSA = SPCR1;McBSP1->SPSD = 0;McBSP1->SPSA = SPCR2;McBSP1->SPSD = 0;McBSP1->SPSA = PCR;//设置收发。

星S3C2440微处理器

应用实例一:嵌入式系统开发

嵌入式系统开发

星S3C2440微处理器适用于嵌入 式系统开发,其强大的处理能力 和丰富的外设接口使其成为嵌入 式领域的理想选择。

实时操作系统

星S3C2440微处理器支持实时操 作系统(RTOS)的开发,RTOS 能够提供实时任务调度和多任务 处理能力,满足实时系统的需求。

3

APB和ASB总线

APB和ASB总线用于连接低速外设,如GPIO、 UART等。

03

星S3C244ห้องสมุดไป่ตู้微处理器的指令集 架构

指令集架构概述

ARM架构

01

S3C2440微处理器采用ARM架构,属于精简指令集(RISC)的

范畴。

指令集发展历程

02

ARM架构的指令集经过多年的发展,已成为移动设备和嵌入式

指令集功能

数据处理指令

用于执行算术、逻辑、移位等基本操 作。

控制流程指令

用于控制程序的执行流程,如条件判 断、跳转等。

内存访问指令

用于读写内存和访问外部存储器。

协处理器指令

用于执行特定功能,如浮点运算、加 密等。

指令集实现方式

汇编语言

使用汇编语言编写程序,通过汇编器将汇编代码转换 为机器码。

C/C语言

星S3C2440微处理器

• 星S3C2440微处理器概述 • 星S3C2440微处理器的体系结构 • 星S3C2440微处理器的指令集架构

• 星S3C2440微处理器的编程模型 • 星S3C2440微处理器的应用实例

01

星S3C2440微处理器概述

定义与特点

定义

S3C2440是一款由三星公司开发的 ARM920T核的微处理器。

UART(中文版的数据手册)

UART(中⽂版的数据⼿册)第⼗⼀章异步串⼝通信概述S3C2410的UART提供3个独⽴的异步串⾏通信端⼝,每个端⼝可以基于中断或者DMA进⾏操作。

换句话说,UART控制器可以在CPU和UART之间产⽣⼀个中断或者DMA请求来传输数据。

UART在系统时钟下运⾏可⽀持⾼达230.4K 的波特率,如果使⽤外部设备提供的UEXTCLK,UART的速度还可以更⾼。

每个UART通道各含有两个16位的接收和发送FIFO。

S3C2410的UART包括可编程的波特率,红外接收/发送,⼀个或两个停⽌位插⼊,5-8位数据宽度和奇偶校验。

每个UART包括⼀个波特率发⽣器、⼀个发送器、⼀个接收器和⼀个控制单元,如图11-1所⽰。

波特率发⽣器的输⼊可以是PCLK或者UEXTCLK。

发送器和接收器包含16位的FIFO和移位寄存器,数据被送⼊FIFO,然后被复制到发送移位寄存器准备发送,然后数据按位从发送数据引脚TxDn输出。

同时,接收数据从接收数据引脚RxDn按位移⼊接收移位寄存器,并复制到FIFO。

特性—RxD0, TxD0, RxD1, TxD1, RxD2, 和TxD2基于中断或者DMA操作—UART Ch 0, 1, 和 2 具有 IrDA 1.0 & 16 字节 FIFO—UART Ch 0 和 1 具有 nRTS0, nCTS0, nRTS1, 和 nCTS1—⽀持发⽣/接收握⼿图11-1 UART⽅框图串⼝操作下述部分描述了UART的⼀些操作,包括数据发送、数据接收、中断产⽣、波特率发⽣、loop-back模式、红外模式和⾃动流控制。

数据发送发送数据的帧结构是可编程的,它由1个起始位、5-8个数据位、1个可选的奇偶位和1-2个停⽌位组成,这些可以在线控制寄存器ULCONn中设定。

接收器可以产⽣⼀个断点条件——使串⾏输出保持1帧发送时间的逻辑0状态。

当前发送字被完全发送出去后,这个断点信号随后发送。

断点信号发送之后,继续发送数据到Tx FIFO(如果没有FIFO则发送到Tx保持寄存器)。

s3c2440芯片中文手册2

第二章处理器工作模式2.1概述S3C2440采用了非常先进的ARM920T内核,它是由ARM(Advanced RISC Machines) 公司研制的。

2.2 处理工作状态从程序员的角度上看,ARM920T可以工作在下面两种工作状态下的一种:● ARM 状态:执行32位字对齐的ARM指令● THUMB 状态:执行16位半字对齐的THUMB指令。

在这种状态下,PC 寄存器的第一位来选择一个字中的哪个半字注意;这两种状态的转换不影响处理模式和寄存器的内容。

2.3 切换状态进入THUMB 状态进入THUMB 状态,可以通过执行BX指令,同时将操作数寄存器的状态位(0位)置1来实现。

当从异常(IRQ,FIQ,UNDEF,ABORT,SWI等)返回时,只要进入异常处理前处理器处于THUMB状态,也会自动进入THUMB状态。

进入ARM状态进入ARM状态,可以通过执行BX指令,并且操作数寄存器的状态位(0位)清零来实现。

当处理进入异常(IRQ,FIQ,RESET,UNDEF,ABORT,SWI等)。

这时,PC值保持在异常模式下的link寄存器中,并从异常向量地址处开始执行处理程序。

存储空间的格式ARM920T将存储器空间视为从0开始由字节组成的线性集合,字节0到3中保存了第一个字节,字节4到7中保存第二个字,以此类推,ARM920T对存储的字,可以按照小端或大端的方式对待。

大端格式:在这种格式中,字数据的高字节存储在低地址中,而字数据的低字节则存放2.4 指令长度指令可以是32位长度(在ARM状态下) 或16位长度(在THUMB状态) 。

数据类型ARM920T支持字节(8位),半字(16位) 和字(32位) 数据类型。

字必须按照4字节对齐,半字必须是2字节对齐。

2.5 操作模式ARM920T支持7种操作模式:● 用户模式(user模式),运行应用的普通模式● 快速中断模式(fiq模式),用于支持数据传输或通道处理● 中断模式(irq模式),用于普通中断处理● 超级用户模式(svc模式),操作系统的保护模式● 异常中断模式(abt模式),输入数据后登入或预取异常中断指令● 系统模式(sys模式),使操作系统使用的一个有特权的用户模式● 未定义模式(und模式),执行了未定义指令时进入该模式]外部中断,异常操作或软件控制都可以改变中断模式。

S3C2440芯片内部结构

S3C2440芯片内部结构首先是ARM920T内核,它是S3C2440芯片的核心部分,负责执行指令和进行数据计算。

ARM920T是ARM9系列的一款高性能内核,具有5级流水线结构,支持高级数据处理指令和多种存储器接口。

它的内置缓存和分支预测机制可以提高执行效率,充分发挥芯片的计算能力。

其次是外设控制器,S3C2440芯片内置了多个外设控制器,包括UART串口、SPI、I2C总线、USB等接口,以及LCD控制器、触摸屏控制器、MMC/SD卡控制器等功能模块。

这些控制器可以与各种外部设备进行通信和数据交互,为系统提供了丰富的接口和功能。

存储器接口是S3C2440芯片与外部存储器之间的桥梁,它可以连接闪存、SDRAM、NAND Flash等不同类型的存储器。

通过存储器接口,芯片可以读写存储器中的数据,并进行程序的存储和执行。

S3C2440提供了高速的存储器控制器和多种存储器接口,可以满足不同应用场景的需求。

时钟和电源管理模块是S3C2440芯片的核心组成部分,它负责提供系统时钟和电源管理功能。

时钟管理模块可以根据需要设置系统的工作频率,提供外设时钟和CPU时钟等。

电源管理模块可以对芯片的功耗进行控制,实现节能和延长电池寿命。

除了上述主要模块外,S3C2440芯片还具有其他辅助功能,如中断管理、DMA控制、中央处理器监视器等。

中断管理模块可以对外部中断信号进行处理,实现系统的实时响应。

DMA控制模块可以实现高速数据传输,减轻CPU负担。

中央处理器监视器模块可以对系统进行监控和调试,提高系统的可靠性和稳定性。

总结起来,S3C2440芯片的内部结构包括ARM920T内核、外设控制器、存储器接口、时钟和电源管理等模块。

这些模块相互协作,共同完成系统的计算、通信、存储和控制等任务。

有了这些丰富的硬件资源和功能,S3C2440芯片可以满足不同应用领域的需求,为嵌入式系统的开发和应用提供了良好的支持。

S3C2440_LCD控制器中文手册

的GREENVAL[31:0]和BLUELUT寄存器中的BLUEVAL[31:0]作为可编程的查找表入口。与灰度等级 显示类似,在寄存器REDLUR中的8组或者4位域,换言之,REDVAL[31:28],REDLUT[27:24], REDLUT[23:20],,REDLUT[19:16], REDLUT[15:12], REDLUT[11:8],REDLUT[7:4]和REDLUT[3:0] 被分配给每个红色等级。4位(每个域)的可能组合有16种,并且每个红色等级应该被分配16种等级种 的1种。换句话说,用户可以通过该类型的查找表选择合适的红色等级。对于绿色,寄存器GREENLUT 中的GREENVAL[31:0]在查找表中的分配形式与红色是一样的。类似地,寄存器BLUELUT中的 BLUEVAL[31:0]在查找表中也是这样分配的。对于蓝色,2位组成4种颜色等级,与8种红色,绿色等 级是不一样的。 4096 色模式操作

s3c2410中文手册

s3c2410中文手册简介S3C2410 是一种嵌入式处理器,由韩国三星电子公司设计和制造。

它是一款高度集成的 ARM 架构芯片,广泛应用于各种移动设备中,如智能手机、平板电脑、PDA 等。

本手册将详细介绍 S3C2410 芯片的特性、功能和使用方法,帮助开发人员更好地理解和应用该芯片。

芯片特性S3C2410 芯片具有以下主要特性:1.ARM920T 内核: S3C2410 芯片采用了 ARM920T 内核,它是一种高性能、低功耗的 32 位 RISC 处理器。

ARM920T 内核支持 ARMv4T 指令集,并具有强大的计算和处理能力。

2.高度集成的外设: S3C2410 芯片内集成了许多常用的外围设备,包括 UART、SPI、I2C、PWM 等。

这些外设可满足各种应用需求,简化了系统设计和连接。

3.多种接口: S3C2410 芯片提供了丰富的接口,如LCD 控制器、触摸屏控制器、SDIO 控制器等。

这些接口允许连接各种外部设备,如显示屏、输入设备、存储卡等,实现更丰富的功能。

4.低功耗设计: S3C2410 芯片采用先进的低功耗设计技术,具有很低的静态功耗和动态功耗。

这使得它非常适合于移动设备,延长了电池寿命。

芯片功能GPIOS3C2410 芯片提供了多个 GPIO 管脚,用来实现输入和输出功能。

GPIO 管脚可以通过软件配置为输入模式或输出模式,并可以设置电平状态。

开发人员可以利用GPIO 实现各种功能,如控制 LED 灯、读取按键状态等。

UARTS3C2410 芯片内集成了多个 UART 模块,用于串口通信。

每个 UART 模块都提供了数据传输和接收的功能,并支持多种通信协议,如 RS232、RS485 等。

开发人员可以使用 UART 实现与外部设备的串口通信。

LCD 控制器S3C2410 芯片具有强大的 LCD 控制器,支持多种显示模式和分辨率。

LCD 控制器可以控制显示屏的像素点,实现图形显示和文字显示功能。

ARM samsung 2440中文手册 s3c2440a_11UART

的URXHn和UERSTATn必须被读出。

举例

假定UART接收FIFO顺序接收到A、B、C、D、E且在接收B时出现帧错误,在接收D时出现奇偶校

验错误。因为错误接收的字符没有被读取,所以UART接收错误没有产生错误中断。一旦字符被读

取,错误中断产生。

如图 11-3 所示UART接收 4 个字符包括 2 个错误。

溢出错误,奇偶校验错误,帧错误,终止条件是作为接收错误状态来参考,每种错误都可 以引起接收错误状态中断请求,如果在控制寄存器UCONn中的接收错误状态中断使能位置 1。 当接收错误状态中断请求被检测到,该信号引起的请求可以通过读UERSTSTn寄存器的值

S3C2440A 中文 Datasheet 第十一章 UART

10.4.2 数据接收

如数据发送,接收的数据帧是可编程的。其包括一个开始位,5~8 个数据位,一个可选的 奇偶校验位和 1~2 个停止位,其可由线性控制寄存器 ULCONn 来设置。接收器可以侦测溢 出错误,奇偶校验错误,帧错误和终止条件,每个错误都可以设置一个错误标志。 - 溢出错误是指在旧数据被读取前新数据覆盖了旧数据。 - 奇偶校验错误是指接收器侦测到一个不希望的奇偶条件。 - 帧错误是指接收到的数据没有一个有效的停止位。 - 终止条件是指 RxDn 输入保持逻辑 0 状态长于一个帧的传输时间。

波特率错误公差 Baud-Rate Error Tolerance UART帧错误应该少于 1.87%(3/160). tUPCLK = (UBRDIVn + 1) x 16 x 1Frame / PCLK tUPCLK : Real UART Clock tUEXACT = 1Frame / baud-rate tUEXACT : Ideal UART Clock UART error = (tUPCLK – tUEXACT) / tUEXACT x 100% 注: 1. 1Frame = start bit + data bit + parity bit + stop bit. 2. 在特定条件下,我们支持波特率最高达到 921.6K bps。例如,当PCLK为 60MHz, 你可以在 1.69UART错误公差下使用 921.6K bps under UART error of 1.69%.

s3c2440芯片中文手册-16 ADC&TSC

ADCDLY 位

描述

初始值

DELAY

[15:0] (1) 普通转换模式,XY坐标模式,自动坐标模式。

00ff

->AD转换开始延迟值。

(2) 等待中断模式。

当光标按下出现在睡眠模式时,产生一个用于退出睡眠模式

的唤醒信号,有几个毫秒的时间间隔。注:不要用 0 值

注:在ADC转换前,触摸屏使用晶振时钟(3.68MHz),在AD转换中使用GCLK(最大

(3) 自动(连续)XY坐标转换模式

自动(连续)XY坐标转换模式是如下操作,触摸屏控制器连续的转换触摸X坐标和Y坐

标。在触摸控制器写X测量数据到ADCDAT0 且写Y测量数据到ADCDAT1 后,触摸屏接口

产生中断源到自动坐标转换模式下的中断控制器。

XP

XM

YP

YM

X Position Conversion Y Position Conversion

50MHz)。

16.5.4 ADC 转换数据寄存器 0

ADC CONVERSION DATA REGISTER (ADCDAT0)

寄存器

地址

读写

描述

ADCDAT0

0x5800000C

R/W ADC转换数据寄存器

复位值 -

ADCDAT0

UPDOWN

AUTO_PST XY_PST

保留 XPDATA

位

[15]

无操作模式)

XP

XM

YP

YM

Waiting for Interrupt Mode Pull up

Hi-Z

备用模式:

AIN[5]

GND

备用模式在ADCCON[2]置 1 时激活。在此模式下,AD转换操作停止,ADCDAT0 和

S3C2410-UART简介及编程

UART接口 | s3c2410系列ARM

UART初始化

通信模式设置

串行通信协议

先发送起始位,然后是最低有效数据位,最后是停止位

起始位 为低电平

。

起始位

奇偶校验位 可有可无

数据位(5~8位)

停止 位

可设置为 1、1.5、 2位停止位

Start bit LSB

Data bit Data bit Data bit Data bit Data bit Data bit

UART RxD UART RxD

1 start D0 D1 D2 D3 D4 D5 D6 D7 P 1

检测到起始位的下降沿,

速率测量计数器对PCLK 进行计数。

1

start bit

1(LSB of ‘A’ or

’a’) 检测到起始位的上升沿,

速率测量计数器停止。

速率测量计数器

当计数完毕之后,速率测量计数器的值装入除 数锁存寄存器,波特率自动切换为正常模式 。

[5 : 4]

3

2

奇偶选择 奇偶设置 停止位

[1 :0] 字长

UART接口 |s3c2410系列ARM 1 初始化

2 收发数据 3 状态信息

UART状态信息

引脚设置 波特率设置 通信模式设置 工作模式设置 发送单元

接收单元 查询方式

中断方式

UART接口 | s3c2410系列ARM 工作模式设置

UART接口 |s3c2410系列ARM 1 初始化

2 收发数据 3 状态信息

UART状态信息

引脚设置 波特率设置 通信模式设置 工作模式设置 发送单元

接收单元 查询方式

中断方式

UART接口 | s3c2410系列ARM 通信模式设置

S3C2440输入-输出端口

S3C2440输入/输出端口

端口控制描述(详细见S3C2440 的数据手册)

端口配置寄存器(GPACON 至GPJCON)

端口数据寄存器(GPADAT 至GPJDAT)

端口上拉寄存器(GPBUP 至GPJUP)

杂项控制寄存器

外部中断控制寄存器

用一个实例(LED 流水灯)来学习下输入/输出端口

(在TQ2440 开发板中是用GPB5~8 控制LED1~4)

#include”2440addr.h”#defineLED1_ON(rGPBDAT&=~(1其中启动代码那块你需要自己加上去,

说明下2440addr.h:定义2440 寄存器的地址,包括存储器寄存器地址、中断向量地址、DMA 地址、时钟电源管理寄

存器地址、LCD 控制寄存器地址、Nand Flash 地址、UART、PWM 定时器、USB Device、WatchDog、IIC、IIS、I/O

端口、ADC、SPI、SD 卡、ISR 寄存器地址等。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

ARM samsung 2440中文手册 s3c2440a_17RTC

第十七章实时时钟17.1概述实时时钟(RTC)单元在系统电源关闭的情况下可以在备用电池下工作。

RTC可以使用STRB/LDRB ARM操作传输二进制码十进制数的8位数据给CPU。

数据包括秒、分钟、小时、日期、天、月、年的时间信息。

RTC单元可以在32.768KHz的外部晶振下工作,可以可以执行报警功能。

17.2特点-BCD数:秒、分钟、小时、日期、日、月、年-闰年生成器-报警功能:报警中断或从掉电模式中唤醒-已经解决2000年问题-独立电源引脚(RTCVDD)-支持对于实时内核时间节拍的毫秒节拍时间中断17.3实时时钟操作17.3.1闰年发生器闰年发生器可以基于BCDDATE、BCDMON、BCDYEAR的数据,从28、29、30、31中确定每个月的最后一天。

该模块在确定某月最后一天的时候会考虑闰年的因素。

一个8位的计数器仅能代表两个BCD数字,所以它不能确定是否是00年(该年的最后两个数字是00)。

例如,它不能区别1900年和2000年。

为了解决这个问题,S3C2440A的RTC模块有一个硬件逻辑来支持在2000年的闰年。

记录1900年不是闰年而2000年是闰年。

因此两个数字00在S3C2440A中记录的是2000年而不是1900年。

17.3.2读写寄存器为了写RTC模块中的BCD寄存器,RTCCON寄存器的位0必须置1。

为了显示秒分小时星期日月年,CPU应该分别读取在RTC模块中的BCDSEC,BCDMIN,BCDHOUR,BCDDAY,BCDDATE,BCDMON,和BCDYEAR。

但是,因为多寄存器读取可能存在一秒的误差。

例如,当用户读BCDYEAR和BCDMON,结构假定是2059年12月31日23点59分。

当用户读BCDSEC寄存器,值的范围是从1到59(秒)就没有问题,但是如果值是0,年月日就变成了2060年1月1日0时0分因为有刚才提到的1秒误差。

在这种情况下如果BCDSEC为0,用户应该重读BCDYEAR到BCDSEC。

第1讲三星s3c2440微处理器

掉电模式:所有外设和内核的电源都切断了;

1. 可以通过EINT[15:0]或RTC报警中断来从掉电模式中唤醒处

理器

12

S3C2440A特性

中断控制器

60个中断源(1个看门狗定时器,5个定时器, 9个UARTs,24个外部中断,4个DMA,2个 RTC,2 个ADC,1 个IIC,2 个SPI,1个SDI, 2个USB,1 个LCD和1个电池故障,1个NAND 和2个Camera),1个AC97音频

电平/边沿触发模式的外部中断源 可编程的边沿/ 电平触发极性 1. 支持为紧急中断请求提供快速中断服务

13

S3C2440A特性

具有脉冲带宽调制功能的定时器(PWM) 4 通道16位具有PWM功能的定时器,1通道16

位内部定时器,可基于DMA或中断工作 可编程的占空比周期,频率和极性 能产生死区 1. 支持外部时钟源

Main TFT LCD & TSP

1/2/4/8/16 bpp Up to QVGA

SD/SDIO IIS I/F

Audio Codec

TDMB/WLAN

SD/MMC Stereo Speaker Head Set Mic

引言

三星公司推出的16/32位RISC微处理器 S3C2440A,为手持设备和一般类型应用 提供了低价格、低功耗、高性能小型微 控制器的解决方案。

–LCD 实际尺寸的典型值是:640 ×480,320 ×240, 160×160 及其他

–最大虚拟屏幕大小是4M字节

–256 色模式下支持的最大虚拟屏是:4096 ×1024,

2048 ×2048,1024×4096等

17

S3C2440A特性

TFT彩色显示屏 支持彩色TFT的1,2,4或8bbp(像素每位)调色显示 支持16,24bbp无调色真彩显示TFT 在24bbp 模式下支持最大16M色TFT lpc3600定时控制器,为嵌入式lts350Q1-PD1/2(SAMSUNG

S3C2440中文翻译之引脚描述

S3C2440译者:☆翔子★OM[1:0] I 这两bit用于把2440设置成TEST模式,也用于设置nGCS0总线的宽度。

00:nand-boot;01:16bit;10:32bit11:test modeADDR[26:0] O 地址总线。

存储器输出的对应bank的地址线,27bit刚好128M空间。

DATA[31:0] IO 数据总线。

存储器读的时候输入,写的时候输出。

总线宽度可编程:8/16/32bit。

nGCS[7:0] O 通用芯片选择。

当一个存储器的地址命中某个bank的地址范围内时,对应的nGCS[7:0]就被激活。

访问周期号和bank大小可编程。

nWE O 写使能。

指示当前总线周期是一个写周期nOE O 读(输出)使能。

指示当前总线周期是一个读周期nXBREQ I 总线保持请求。

允许其他的总线master去请求本地总线的控制。

BACK有效指示总线控制已经生效(批准了)。

nXBACK I 总线保持应答。

指示2440交出总线控制权给另一个总线master。

nWAIT I 请求延长当前总线周期。

只要该信号是L电平,当前总线周期不能被完成。

SD R A M/SR A MnSRAS O SDRAM行地址strobe (行地址最大限制数)nSCAS O SDRAM列地址strobe (列地址最大限制数)nSCS[1:0] O SDRAM芯片选择DQM[3:0] O SDRAM数据mask(掩码)SCLK[1:0] O SDRAM时钟SCKE O SDRAM时钟使能nBE[3:0] O 高字节/低字节使能(在16bit SRAM情况下使用) nBWE[3:0] O 写字节使能N A N D Fl as hCLE O 命令锁存使能ALE O 地址锁存使能nFCE O Nand flash 芯片使能nFRE O Nand flash读使能nFWE O Nand flash写使能NCON I Nand flash配置FRnB I Nand flash 准备好/忙信号(ready/busy)如果没有使用Nand flash控制器,必须为高电平(VDDMOP)LC DVD[23:0] O STN/TFT/SEC TFT :LCD数据总线LCD_PWREN O STN/TFT/SEC TFT :LCD面板电源使能控制信号VCLK O STN/TFT:LCD时钟信号VFRAME O STN:LCD帧信号VLINE O STN:LCD行信号VM O STN:VM交替行列电压极性。

一起学mini2440裸机开发(六)--UART原理与基础实验

一起学mini2440裸机开发(六)--UART原理与基础实验我个人感觉UART也不算是很难,学过单片机的相信都用过UART,在这里还是说说它吧,并且在写基础实验并调试的时候,出现了一个问题,就是我们平时使用jlink调试程序都是基于在sdram中运行的,由于ram的掉电易失性,所以咱们的裸机程序根本就不能脱机工作,也即是说复位之后程序就没有了,当然,我知道可以利用以后学的知识将它下载到NAND Flash中去,这个以后再说。

貌似还有一个办法,就是使用mdk直接Download到flash,不过需要什么算法之类的,这个算法我还不懂,先不管他了,先把UART的原理实验弄清楚了再说,以后学了nand flash就可以脱机工作了。

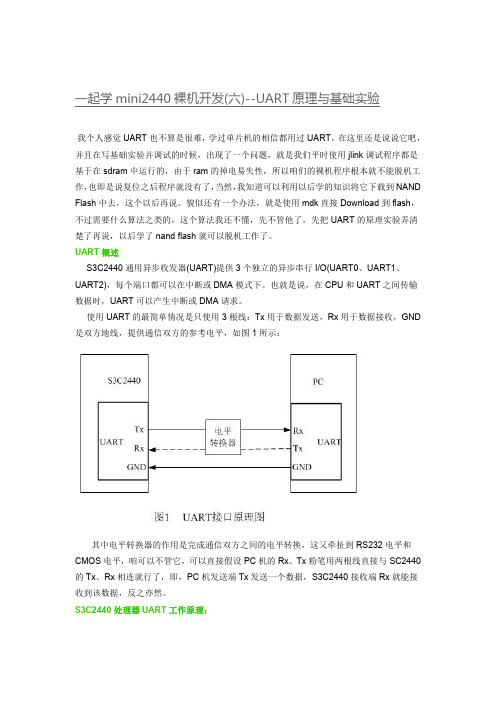

UART概述S3C2440通用异步收发器(UART)提供3个独立的异步串行I/O(UART0、UART1、UART2),每个端口都可以在中断或DMA模式下。

也就是说,在CPU和UART之间传输数据时,UART可以产生中断或DMA请求。

使用UART的最简单情况是只使用3根线:Tx用于数据发送,Rx用于数据接收,GND 是双方地线,提供通信双方的参考电平,如图1所示:其中电平转换器的作用是完成通信双方之间的电平转换,这又牵扯到RS232电平和CMOS电平,咱可以不管它,可以直接假设PC机的Rx、Tx粉笔用两根线直接与SC2440的Tx、Rx相连就行了,即,PC机发送端Tx发送一个数据,S3C2440接收端Rx就能接收到该数据,反之亦然。

S3C2440处理器UART工作原理:S3C240的3个UART包括可编程的波特率,红外(IR)发射/接收,一个或两个停止位,5位、6位、7位或8位的数据宽度,和奇偶校验位。

(不很懂是吧,其实我开始也不懂,这是什么玩意儿)每个UART包含一个波特率发生器、发送器、接收器和一个控制单元,如图2所示。

波特率发生器的输入时钟有3种:PCLK、FCLK/n、UEXTCLK(外部输入时钟)。

S3C2440的UART详解

1、UART原理简介在介绍2440的UART控制器之前,我们首先来了解一下UART的原理UART:Universal Asynchro no us Receiver/Transmitter(通用异步收发送器),用来传输串行数据,发送数据时,CPU将并行数据写入UART,UART按照一定格式在TxD线上串行发出;接收数据时,UART检测到RxD线上的信号,将串行收集放到缓冲区中,CPU即可读取UART获得的这些数据。

UART最精简的连线形式只有3根线,TXD用于发送,RXD用于接收,GND用于提供参考电平。

UART 之间以帧作为数据传输单位,帧由具有完整意义的若干位组成,它包含开始位、数据位、校验位和停止位。

发送数据之前,互相通信的UART之间要约定好数据传输速率(波特率的倒数)、数据的传输格式(多少个数据位、是否使用校验位、奇校验还是偶校验、多少个停止位)。

2、S3C2440 UART的特性S3C2440的通用异步收发器(UART)配有3个独立异步串行I/O(SIO)端口,每个都可以通过产生中断或DMA请求来进行CPU和UART之间的数据传输。

如图1所示:每个UART包含一个波特率发生器、发送器、接收器和一个控制单元,图1 2440UART方框图(带FIFO)波特率发生器可以由PCLK、FCLK/n或UEXTCLK(外部输入时钟)时钟驱动。

UART通过使用系统时钟可以支持最高115.2Kbps的比特率。

如果是使用外部器件提供UEXTCLK的UART,则UART可以运行在更高的速度。

发送器和接收器各包含一个64字节的FIFO和数据移位器。

要发送数据时,先将数据写入到FIFO接着在发送前复制到发送移位器中,随后将数据从发送数据引脚(TXDn)移出;接收数据时,从接收数据引脚(RXDn)移入收到的数据,接着从移位器复制到FIFO。

3、S3C2440 UART的使用对于S3C2440,使用UART之前,首选需要对2440的UART模块进行初始化,需要设置波特率、传输格式(多少个数据位、是否使用校验位、奇校验或偶校验、多少个停止位、是否使用流量控制)、选择所涉及的管脚为UART功能、选择UART通道的工作模式为中断模式或DMA模式。

S3C2440A 中文Datasheet

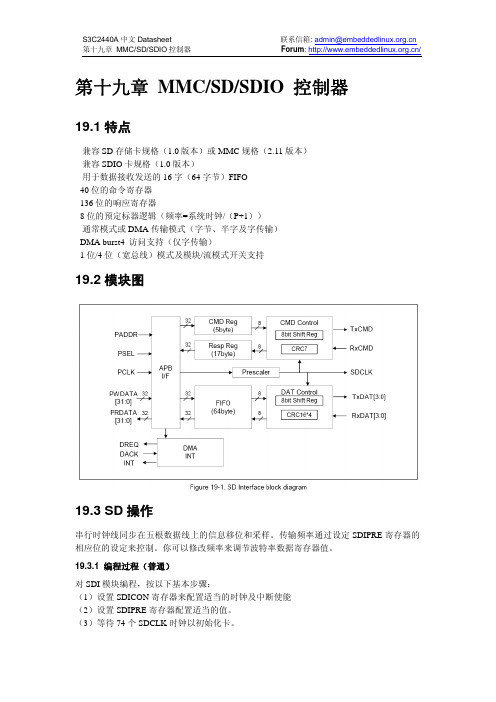

第十九章MMC/SD/SDIO控制器19.1特点-兼容SD存储卡规格(1.0版本)或MMC规格(2.11版本)-兼容SDIO卡规格(1.0版本)-用于数据接收发送的16字(64字节)FIFO-40位的命令寄存器-136位的响应寄存器-8位的预定标器逻辑(频率=系统时钟/(P+1))-通常模式或DMA传输模式(字节、半字及字传输)-DMA burst4访问支持(仅字传输)-1位/4位(宽总线)模式及模块/流模式开关支持19.2模块图19.3SD操作串行时钟线同步在五根数据线上的信息移位和采样。

传输频率通过设定SDIPRE寄存器的相应位的设定来控制。

你可以修改频率来调节波特率数据寄存器值。

19.3.1编程过程(普通)对SDI模块编程,按以下基本步骤:(1)设置SDICON寄存器来配置适当的时钟及中断使能(2)设置SDIPRE寄存器配置适当的值。

(3)等待74个SDCLK时钟以初始化卡。

19.3.2CMD路径编程(1)写命令参数32位到SDICmdArg(2)决定命令类型并通过设置SDICmdCon开始命令传输(3)当SDICmdSta的特殊标志被置位,确认SDICMD路径操作的结束。

(4)如果命令类型是不相应,标志是CmdSent。

(5)如果命令类型是相应,标志是RspFin。

(6)通过对相应位写1,清除SDICmdStaD的标志。

19.3.3数据路径编程(1)写数据超时期间到SDIDTimer(2)写模块大小(模块长度)到SDIBSize(通常是0x80字)(3)确定模块模式,宽总线,DMA等且通过社子SDIDatCon来开始数据传输(4)发送数据->写数据到数据寄存器(SDIDAT),当发送FIFO有效(TFDET置位),或一半(TFHalf置位),或空(TFEmpty置位)。

(5)接收数据->从数据寄存器(SDIDAT)读数据,当接收FIFO有效(RFDET置位),或满(RFFull置位)。

s3c2440的UART用法

s3c2440的UART用法SPI、IIC和UART是最常用的三种串行总线,这三种总线在s3c2440中都被集成了。

在这里我们主要介绍UART,另两个总线在后面的文章中给出。

UART(Universal Asynchronous Receiver/Transmitter,通用异步接收/发送装置)用于异步通信,可以实现全双工发送和接收。

它不仅可以实现不同嵌入式系统之间的通信,还可以实现与PC之间的通信。

s3c2440提供了三个UART端口,它们都可以通过查询、中断和DMA方式传输数据,而且每个UART都分别有一个64个字节的接收FIFO和一个64个字节的发送FIFO。

在这里,我们只给出非FIFO模式,即传输数据不利用FIFO缓存,一个字节一个字节地传输。

下面我们就给出如何用s3c2440来实现非FIFO的UART通信。

要实现某种通信,就必须遵循该通信协议。

UART的协议包括传输数据的位数,停止位的位数,以及是否进行奇偶校验,这些设置是利用ULCONn寄存器完成的。

另一个很重要的地方就是设置波特率。

s3c2440波特率的时钟源有三个:PCLK、FCLK/n和UEXTCLK。

时钟源的选择是由UCONn 的第10位和第11位来完成的。

波特率的具体计算公式为:时钟源频率÷(波特率×16)-1这个计算结果很可能是小数,把该小数取最接近的整数,放入寄存器UBRDIVn中就完成了波特率的设置。

如我们选择波特率的时钟源为PCLK,它为50MHz,我们设置的波特率为115.2kHz,通过上式计算的结果为26.13,取整后得到26,那么我们把26放入UBRDIVn 中即可。

由于我们没有使用FIFO和MODEM,所以可以不用设置FIFO控制寄存器UFCONn 和MODEM控制寄存器UMCONn。

通过以上寄存器的设置,UART就可以正常传输数据。

接收到的数据是放到接收缓存器URXHn中,要发送数据时,是把数据放入发送缓存器UTXHn中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

s3c2440A UART提供了一个参考作为回送模式的测试模式,以帮助孤立通讯连接中的错误。这个模 式结构上使能在UART中的RXD和TXD连接。在此模式下发送的数据通过RXD接收到接收器。该特 点是允许处理器验证内部传输和每个SIO通道的接收数据通道。该模式通过设置UART控制寄2440A 中文 Datasheet 第十一章 UART

10.4.9 红外模式

联系信箱: admin@ Forum: /

波特率错误公差 Baud-Rate Error Tolerance UART帧错误应该少于 1.87%(3/160). tUPCLK = (UBRDIVn + 1) x 16 x 1Frame / PCLK tUPCLK : Real UART Clock tUEXACT = 1Frame / baud-rate tUEXACT : Ideal UART Clock UART error = (tUPCLK – tUEXACT) / tUEXACT x 100% 注: 1. 1Frame = start bit + data bit + parity bit + stop bit. 2. 在特定条件下,我们支持波特率最高达到 921.6K bps。例如,当PCLK为 60MHz, 你可以在 1.69UART错误公差下使用 921.6K bps under UART error of 1.69%.

10.4.2 数据接收

如数据发送,接收的数据帧是可编程的。其包括一个开始位,5~8 个数据位,一个可选的 奇偶校验位和 1~2 个停止位,其可由线性控制寄存器 ULCONn 来设置。接收器可以侦测溢 出错误,奇偶校验错误,帧错误和终止条件,每个错误都可以设置一个错误标志。 - 溢出错误是指在旧数据被读取前新数据覆盖了旧数据。 - 奇偶校验错误是指接收器侦测到一个不希望的奇偶条件。 - 帧错误是指接收到的数据没有一个有效的停止位。 - 终止条件是指 RxDn 输入保持逻辑 0 状态长于一个帧的传输时间。

10.2 特点

- 基于 DMA 或中断操作的 RxD0,TxD0,RxD1,TxD1,RxD2 和 TxD2

- 有红外和 64 位 FIFO 的 UART 通道 0 和 1 - 有 nRTS0,nCTS0,nRTS1 和 nCTS1 的 UART 通道 0 和 1 - 支持握手的发送和接收

S3C2440A 中文 Datasheet 第十一章 UART

联系信箱: admin@ Forum: /

10.4.7 波特率产生

每个UART波特率发生器为发送器和接收器提供串行时钟。波特率发生器的源时钟可以选择 s3c2440A的内部系统时钟或UEXTCLK。换言之,被除数可以设定UCONn中的时钟选择来选择。波 特率时钟通过 16 和由UART波特率除数寄存器(UBRDIVn)中定义的 16 位除数来分频源时钟 (PCLK, FCLK/n or UEXTCLK)产生。UBRDIVn由以下表达式来决定。 UBRDIVn = (int) (UART clock / (buad rate x 16)) –1 (UART clock: PCLK, FCLK/n or UEXTCLK) UBRDIVn应该是从 1 到 216-1,当使用小于PCKL的外部时钟UEXTCLK时应该设置 0。 例如如果波特率是 115200bps且UART时钟是 40MHz, UBRDIVn是 UBRDIVn = (int)(40000000 / (115200 x 16) ) -1 = (int)(21.7) -1 [round to the nearest whole number] = 22 -1 = 21

10.4.3 自动流控制(AFC)

s3c2440A 的 UART0 和 UART1 支持有 nRTS 和 nCTS 的自动流。这种情况下,其可以连接 到外部 UART。如果用户想连接 UART 到 Modem,应使 UMCONn 寄存器中的自动流控制 位无效且通过软件控制 nRTS。

在 AFC 中,nRTS 依赖于接收器的条件,nCTS 信号控制发送器的操作。UART 的发送器传 输数据到 FIFO 仅当 nCTS 信号被激活(在 AFC 中,nCTS 意思是对方的 UART FIFO 准备 好接收数据)。在 UART 接收数据之前,当其接收 FIFO 有大于 32 个字节的空闲空间, nRTS 必须被激活;当其接收 FIFO 有小于 32 个字节的空闲空间,nRTS 必须置非激活。

的触发等级且在三个字时间内没有接收到

任何数据(接收超时),产生中断。该时

间根据字长位设置。

Tx interrupt

只要发送数据达到发送 FIFO 触发等级,中 只要发送缓存为空,由接收

断产生。

发送寄存器生成。

Error interrupt

当帧错误,奇偶错误或终止信号被检测 由错误生成。但是如果其他

到,中断产生。

如果用户想连接UART到Modem接口上,就需要nRTS、nCTS、nDSR、nDTR、DCD和nRI。在这 种情况下,用户可通过软件使用通用IO端口来控制这些信号,因为AFC不支持RS-232C接口。

10.4.5 中断/DMA 请求生成

s3c2440A的每个UART有七个状态(Tx/Rx/Error)信号:溢出错误,奇偶校验错误,帧错 误,终止,接收缓存数据准备好,发送缓存空和发送移位器空,其由相应UART的状态寄 存器(UTRSTATn/UERSTATn)指出。

当接收器在三个字的时间内(其间隔根据字长位的设置)没有收到任何数据且 Rx FIFO 在 FIFO 模式下不为空,接收超时条件出现。

S3C2440A 中文 Datasheet 第十一章 UART

联系信箱: admin@ Forum: /

S3C2440A 中文 Datasheet 第十一章 UART

第十一章 UART

联系信箱: admin@ Forum: /

10.1 概述

s3c2440A 通用异步接收器和发送器(UART)提供了三个独立的异步串行 I/O(SIO)端 口,每个端口都可以在中断模式或 DMA 模式下操作。换言之,UART 可以生成一个中断或 DMA 请求用于 CPU 和 UART 之间的数据传输。UART 使用系统时钟可以支持最高 115.2K bps 的波特率。如果一个外部设备提供 UEXTCLK 给 UART,UART 可以在更高的速度下工 作。每个 UART 通道对于接收器和发送器包括了 2 个 64 位的 FIFO。

UART2 不支持 AFC 功能,因为 s3c2440A 没有 nRTS2 和 nCTS2。

非自动流控制举例(用软件控制 nRTS 和 nCTS) 使用 FIFO 的接收操作 (1)选择接收模式(中断或 DMA 模式) ( 2 ) 检查 UFSTATn 寄存 器 中 的 Rx FIFO 计数 器 。 如 果 其 值 小 于 32 ,用 户 应 该 将

溢出错误,奇偶校验错误,帧错误,终止条件是作为接收错误状态来参考,每种错误都可 以引起接收错误状态中断请求,如果在控制寄存器UCONn中的接收错误状态中断使能位置 1。 当接收错误状态中断请求被检测到,该信号引起的请求可以通过读UERSTSTn寄存器的值

S3C2440A 中文 Datasheet 第十一章 UART

UMCONn[0]的值置 1(激活 nRTS),如果其等于大于 32,用户应该将其置 0。

(3)重复步骤 2 有 FIFO 的发送操作 (1)选择发送模式(中断或 DMA 模式) (2)检查 UMSTATn[0]的值,如果其值为 1,用户写数据到发送 FIFO 寄存器。

10.4.4 RS-232C 接口

错误同时产生,仅一个中断

当达到接收 FIFO 的上限没有读出数据,中 产生。

断产生。

10.4.6 UART 错误状态 FIFO

除了了接收FIFO寄存器,UART有一个错误状态FIFO。错误状态FIFO是指出FIFO寄存器中

有错的数据。当有错的数据准备读出,错误中断就产生。为了清除错误状态FIFO,有错误

来鉴别。

联系信箱: admin@ Forum: /

当接收器传输接收移位器上的数据到在FIFO模式下的接收FIFO寄存器上且接收到的数据数 量达到接收FIFO触发水平,接收中断产生,如果在控制寄存器UCONn中接收模式被置 1(中断请求或查询模式)。在非FIFO模式下,传输接收移位器的数据到接收保持寄存器 将引起在中断请求或查询模式下的接收中断。

如果在控制寄存器中发送模式和接收模式被选定为 DMAn 请求模式,这样 DMAn 请求将取

代上述情形下的接收或发送中断出现。

类型

Rx interrupt

FIFO 模式

非 FIFO 模式

只要接收数据到达接收 FIFO 的触发等级, 只要接收缓存为空,由接收

中断产生。

保持寄存器生成。

当 FIFO 中的数据数量没有达到接收 FIFO

时间

顺序流

错误中断

#0 当没有字符被读出

-

#1 接收到A、B、C、D、E 帧错误(B中)中断出现

#2 在A被读出后

-

#3 在 B 被读出后

-

#4 在 C 被读出后

奇偶校验错误(D中)中断出现

#5 在 D 被读出后

-

#6 在 E 被读出后

-

注

-

‘B’必须被读出 -

‘D’必须被读出 -

S3C2440A 中文 Datasheet 第十一章 UART

当发送器传输接收移位器上的数据到发送 FIFO 寄存器上且在在发送 FIFO 中剩余的数据数 量达到发送 FIFO 触发水平,发送中断产生,如果在控制寄存器 UCONn 中的接收模式被选 定为中断请求或查询模式。在非 FIFO 模式下,传输发送保持寄存器的数据到发送移位器 将引起在中断请求或查询模式下的发送中断。