集成电路设计CADEDA工具实用教程2-Spice_Spectre

集成电路设计CAD_EDA工具实用教程1-Spectre_Verilog数模混合仿真

同时包含模拟和数字两个仿真核

处理速度快,能处理的电路规模极大,但需要解决模拟仿真核和数字 仿真核之间的通信问题;另外,由于数字逻辑仿真器和模拟仿真器的输 入、输出数据是不一样的,还必须在模拟仿真核和数字仿真核之间实现 模拟信号和数字信号的相互转换。

共27页

Q&A

9

Creating Analog Block

3

共27页

高精度模拟/射频电路仿真器

1、Spectre/SpectreRF (Cadence)

2、Hspice/HspiceRF (Synopsys)

3、Ads (Agilent 主要针对RF) 4、Eldo (Mentor Graphics) 5、Saber (Synopsys)

4

共27页

16

Check Block Partition

Change analog & digital stop views to match the stop views in your hierarchy editor (as below)

共27页

17

Check Partition Results

Spectre–Verilog 混合信号仿真

共27页

1

几家EDA软件公司

1、Cadence 2、Synopsys(收购Avanti) 3、Mentor Graphics 4、Silvaco

5、SpringSoft

2

共27页

SPICE仿真器

SPICE : a general-purpose analog circuit simulator developed by the University of California, Berkeley. It is used for nonlinear DC, nonlinear transient, and linear AC analysis. Hspice: a general-purpose circuit simulator from Avanti. It has an extensive set of built-in device models, including models for small geometry MOSFETs and MESFETs. The program is compatible with SPICE input formats. Cadence supports a library of primitives and a full interface for Hspice. Spectre: SPICE-alike analog simulator developed by Cadence.

集成电路芯片设计中的EDA工具分析与应用

集成电路芯片设计中的EDA工具分析与应用随着科技的不断发展,电子信息产业日益壮大,而集成电路芯片作为其中重要的一环,更是日新月异地更新换代。

因此,如何提高设计效率,缩短设计周期,保证设计质量成为许多芯片设计人员重要的任务。

在众多的芯片设计工具中,EDA(Electronic Design Automation)工具更是广受芯片设计人员的欢迎和选择。

本文将就EDA工具在集成电路芯片设计中的应用进行分析和阐述,力求为芯片设计人员提供一些有用的参考和启示。

一、EDA工具的基本概念和分类EDA工具是计算机辅助电子设计的软件工具,主要用于电子系统设计、电路设计、布图设计等方面。

EDA工具主要包括逻辑设计、物理布局和模拟仿真工具。

其中逻辑设计工具包括逻辑合成器、逻辑优化器、逻辑仿真器等;物理布局工具包括版图画图工具、版图编辑器和版图布局工具等;模拟仿真工具包括SPICE仿真器、数字仿真器和混合仿真器等。

在EDA工具的分类中,常见的包括ASIC工具、FPGA工具和PCB工具三种。

ASIC工具主要用于设计大规模集成电路(LSI)和超大规模集成电路(VLSI),主要包括逻辑合成器、布图编辑器、仿真器等。

ASIC工具的主要作用是将逻辑电路转化为物理电路,削减设计周期,缩小设计代价,保证设计质量。

FPGA工具主要用于设计可重构逻辑电路(FPGA),主要包括RTL设计工具、版本管理工具、FPGA逻辑合成器等。

FPGA工具的主要作用是提供硬件逻辑模拟、快速开发逻辑电路的设计、快速验证功能正确与否的载板测试,以及对标准接口的支持等功能。

PCB工具主要用于设计PCB电路板,主要包括电路板布图软件、PCB制造软件等。

PCB工具的主要作用是将芯片设计的电路板经过布图之后制作成PCB板,为芯片的后续步骤做好准备。

二、EDA工具在集成电路芯片设计中的应用分析EDA工具在集成电路芯片设计中的应用,主要有以下几个方面:1.简化设计流程EDA工具能够有效地简化芯片设计的流程。

英语作文-集成电路设计师必备的实用工具与软件介绍

英语作文-集成电路设计师必备的实用工具与软件介绍Integrated circuit (IC) design is a sophisticated field that demands precise tools and software to facilitate efficient development. As an essential part of the semiconductor industry, IC designers rely on a variety of specialized tools throughout the design process. These tools encompass everything from initial concept and simulation to layout and verification. Here, we explore the indispensable tools and software that every IC designer should be familiar with.1. Electronic Design Automation (EDA) Tools:。

At the core of IC design are Electronic Design Automation tools. These software packages enable designers to create and analyze circuits efficiently. EDA tools typically include schematic capture, simulation, and layout functionalities. Cadence Design Systems' suite, including tools like Virtuoso for layout and Spectre for simulation, is widely used in the industry for its comprehensive capabilities. Mentor Graphics (now Siemens EDA) with tools such as Calibre for design verification and HyperLynx for signal integrity analysis also play crucial roles in ensuring design accuracy and reliability.2. SPICE Simulation:。

集成电路EDA与验证技术课件:模拟集成电路设计与仿真

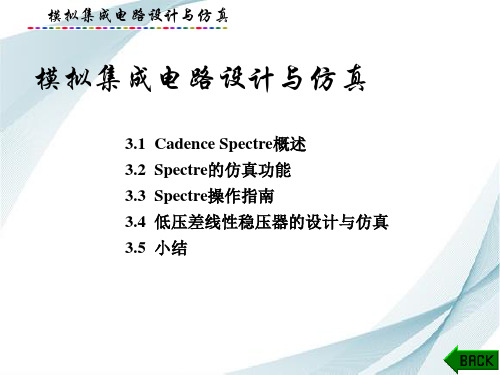

模拟集成电路设计与仿真

常用命令格式: (1) DEFINE 格式:DEFINE <库名> <库路径> 例: DEFINE sample /export/cadence/IC615USER5/tools.lnx86/dfII/samples/cdslib/sa mple (2) INCLUDE 格式:INCLUDE <另外一个cds.lib 的全路径>

模拟集成电路设计与仿真

图3.2 Spectre中包含的各种仿真器

模拟集成电路设计与仿真

2.精确的晶体管模型 Spectre为所有的仿真器提供一致的器件模型,这有利于 消除不同模型间的相关性,从而得到快速收敛的仿真结果。 模型的一致性也保证了器件模型在升级时可以同时应用于所 有的仿真器。 3.高效的程序语言和网表支持 Spectre仿真平台支持多种设计提取方法,并兼容绝大多 数SPICE输入平台。Spectre可以读取Spectre、SPICE以及 Verilog-A格式的器件模型,并支持标准的Verilog-AMS、 VHDL-AMS、Verilog-A、Verilog以及VHDL格式的文本输 入。

模拟集成电路设计与仿真

5.有力衔接了版图设计平台 对于完整的版图设计平台而言,Spectre是不可或缺的重 要环节,它能方便地利用提取的寄生元件参数来快速完成后 仿真(post-layout simulation)的模拟,并与前仿真(pre-layout simulation)的模拟结果作比较,紧密的连接了电路 (Schematic)和版图(layout)的设计。 6.交互的仿真模式 设计者可以在仿真过程中快速改变参数,并在不断调整 参数和模拟之中找到最佳的电路设计结果,减少电路设计者 模拟所花费的时间。

集成电路设计EDA工具应用作业指导书

集成电路设计EDA工具应用作业指导书第1章 EDA工具概述 (5)1.1 EDA工具发展历程 (5)1.2 EDA工具在集成电路设计中的作用 (5)1.3 常用EDA工具简介 (6)第2章集成电路设计流程 (6)2.1 设计准备阶段 (6)2.1.1 需求分析 (6)2.1.2 技术选型 (6)2.1.3 设计规划 (6)2.1.4 电路架构设计 (6)2.2 设计实现阶段 (6)2.2.1 电路设计 (7)2.2.2 仿真验证 (7)2.2.3 布局布线 (7)2.2.4 版图设计 (7)2.3 设计验证阶段 (7)2.3.1 功能验证 (7)2.3.2 时序验证 (7)2.3.3 电源完整性分析 (7)2.3.4 热分析 (7)2.4 设计后处理阶段 (7)2.4.1 版图检查 (7)2.4.2 后仿真分析 (7)2.4.3 生产数据 (7)2.4.4 文档编写 (7)第3章数字集成电路设计 (7)3.1 数字电路设计基础 (8)3.1.1 数字逻辑元件 (8)3.1.2 组合逻辑电路设计 (8)3.1.3 硬件描述语言(HDL) (8)3.2 逻辑合成与优化 (8)3.2.1 逻辑合成 (8)3.2.2 逻辑优化 (8)3.2.3 EDA工具在逻辑合成与优化中的应用 (8)3.3 时序分析 (8)3.3.1 时序分析基础 (9)3.3.2 时序约束与优化 (9)3.3.3 EDA工具在时序分析中的应用 (9)3.4 电源网络设计 (9)3.4.1 电源网络设计基础 (9)3.4.2 电源网络设计方法 (9)3.4.3 EDA工具在电源网络设计中的应用 (9)第4章模拟集成电路设计 (9)4.1 模拟电路设计基础 (9)4.1.1 模拟电路概述 (9)4.1.2 模拟电路设计流程 (9)4.1.3 模拟电路设计方法 (9)4.2 模拟电路仿真 (9)4.2.1 仿真概述 (10)4.2.2 仿真工具与流程 (10)4.2.3 仿真参数设置与优化 (10)4.3 模拟电路布局与布线 (10)4.3.1 布局与布线概述 (10)4.3.2 布局设计 (10)4.3.3 布线设计 (10)4.4 模拟电路后处理 (10)4.4.1 后处理概述 (10)4.4.2 版图检查与修正 (10)4.4.3 后仿真与功能验证 (10)4.4.4 生产工艺与封装 (10)第5章混合信号集成电路设计 (10)5.1 混合信号电路设计基础 (10)5.1.1 混合信号电路概述 (11)5.1.2 混合信号电路设计流程 (11)5.1.3 混合信号电路关键功能指标 (11)5.2 混合信号电路仿真 (11)5.2.1 仿真方法 (11)5.2.2 仿真工具 (11)5.2.3 仿真步骤 (12)5.3 混合信号电路布局与布线 (12)5.3.1 布局与布线概述 (12)5.3.2 布局与布线原则 (12)5.3.3 布局与布线工具 (12)5.4 混合信号电路后处理 (12)5.4.1 后处理概述 (12)5.4.2 后处理流程 (12)5.4.3 后处理工具 (13)第6章射频集成电路设计 (13)6.1 射频电路设计基础 (13)6.1.1 射频信号特性 (13)6.1.2 射频电路元件 (13)6.1.3 射频电路拓扑 (13)6.2 射频电路仿真 (13)6.2.1 电路仿真原理 (13)6.2.2 仿真工具及参数设置 (13)6.2.3 仿真结果分析 (14)6.3 射频电路布局与布线 (14)6.3.1 布局原则 (14)6.3.2 布线技巧 (14)6.3.3 射频电路版图设计 (14)6.4 射频电路后处理 (14)6.4.1 参数提取 (14)6.4.2 功能评估 (14)6.4.3 优化策略 (14)第7章系统级集成电路设计 (14)7.1 系统级电路设计基础 (14)7.1.1 设计流程概述 (15)7.1.2 设计规范与要求 (15)7.1.3 顶层模块划分 (15)7.1.4 通信协议与接口设计 (15)7.2 系统级电路仿真 (15)7.2.1 仿真工具与流程 (15)7.2.2 仿真模型与参数设置 (15)7.2.3 功能仿真与功能仿真 (15)7.2.4 仿真结果分析 (15)7.3 系统级电路布局与布线 (15)7.3.1 布局布线概述 (15)7.3.2 布局布线策略与方法 (15)7.3.3 布局布线工具与流程 (16)7.3.4 布局布线优化与后处理 (16)7.4 系统级电路后处理 (16)7.4.1 后处理概述 (16)7.4.2 版图检查与修正 (16)7.4.3 参数提取与后仿真 (16)7.4.4 设计交付与生产 (16)第8章设计验证与测试 (16)8.1 功能验证 (16)8.1.1 验证目的 (16)8.1.2 验证方法 (16)8.1.3 验证步骤 (16)8.2 时序验证 (17)8.2.1 验证目的 (17)8.2.2 验证方法 (17)8.2.3 验证步骤 (17)8.3 功耗验证 (17)8.3.1 验证目的 (17)8.3.2 验证方法 (17)8.3.3 验证步骤 (17)8.4 DFT与测试 (18)8.4.1 DFT(Design for Testability)设计 (18)8.4.2 测试方法 (18)8.4.3 测试步骤 (18)第9章设计收敛与优化 (18)9.1 设计收敛策略 (18)9.1.1 确定设计目标 (18)9.1.2 分阶段收敛 (18)9.1.3 迭代优化 (18)9.1.4 设计收敛监控 (19)9.2 逻辑合成优化 (19)9.2.1 逻辑简化 (19)9.2.2 逻辑层次优化 (19)9.2.3 时序优化 (19)9.2.4 功耗优化 (19)9.3 布局与布线优化 (19)9.3.1 布局优化 (19)9.3.2 布线优化 (19)9.3.3 热点分析与优化 (19)9.4 电源网络优化 (19)9.4.1 电源规划 (19)9.4.2 电源网络分割 (19)9.4.3 电源网络优化算法 (20)9.4.4 电源噪声分析与控制 (20)第10章 EDA工具在特定领域应用 (20)10.1 EDA工具在嵌入式系统设计中的应用 (20)10.1.1 硬件描述语言(HDL)设计 (20)10.1.2 仿真验证 (20)10.1.3 逻辑综合 (20)10.1.4 布局布线 (20)10.2 EDA工具在人工智能芯片设计中的应用 (20)10.2.1 高层次综合 (21)10.2.2 基于FPGA的加速 (21)10.2.3 数据流优化 (21)10.3 EDA工具在物联网芯片设计中的应用 (21)10.3.1 低功耗设计 (21)10.3.2 射频设计 (21)10.3.3 系统集成 (21)10.4 EDA工具在汽车电子设计中的应用 (21)10.4.1 功能安全 (21)10.4.2 硬件在环仿真 (21)10.4.3 系统级设计 (22)第1章 EDA工具概述1.1 EDA工具发展历程电子设计自动化(Electronic Design Automation,EDA)工具起源于20世纪60年代,集成电路(Integrated Circuit,IC)技术的飞速发展,EDA工具逐渐成为集成电路设计领域不可或缺的辅助工具。

集成电路设计流程中的EDA工具使用教程

集成电路设计流程中的EDA工具使用教程综合电路设计是电子工程师在集成电路设计中经常进行的一项重要任务。

通过使用EDA(电子设计自动化)工具,设计师能够更高效地完成设计流程。

本文将介绍集成电路设计流程中常用的EDA工具及其使用方法。

一、设计综合工具设计综合是集成电路设计流程中的第一步,它将高级硬件描述语言(如VHDL或Verilog)转换为逻辑网表。

常用的设计综合工具包括Synopsys Design Compiler、Cadence Genus等。

设计综合工具能够根据设计规范和约束,实现功能实现和性能优化。

在使用设计综合工具时,首先需要准备好设计规范和约束文件,以确保综合结果能够满足设计要求。

然后,通过命令行或图形界面界面加载设计文件,设置综合选项并运行综合流程。

二、逻辑综合工具逻辑综合是将逻辑网表转换为标准单元库的过程,并执行功耗优化和时序约束等操作。

常用的逻辑综合工具包括Synopsys Design Compiler、Cadence Genus等。

在使用逻辑综合工具时,首先需要准备好逻辑网表文件和约束文件。

然后,通过命令行或图形界面界面加载设计和约束文件,设置综合选项,并运行逻辑综合流程。

逻辑综合工具还可以生成时序分析所需的约束文件,并进行时序分析。

三、布局布线工具布局布线是在物理空间中放置和布线所有电路元件的过程,以满足电路设计的约束条件。

布局布线工具能够根据设计规范和约束,生成良好的物理布局和可靠的布线。

常用的布局布线工具包括Cadence Innovus、SynopsysIC Compiler等。

在使用布局布线工具时,首先需要准备好物理约束文件和逻辑网表。

然后,通过命令行或图形界面界面加载设计和约束文件,设置布局布线选项,并运行布局布线流程。

布局布线工具还可以执行时序优化操作,以满足时序约束。

四、仿真工具仿真是验证电路设计功能和性能的关键步骤。

通过使用仿真工具,设计师可以在真实环境中模拟电路行为,并对其进行调试和优化。

电路仿真工具比较与选择指南

电路仿真工具比较与选择指南电路仿真工具在电子设计领域扮演着重要的角色,它们可以帮助工程师验证设计的正确性、提高设计效率和减少试错成本。

然而,市场上存在众多不同类型的电路仿真工具,如SPICE仿真器、EDA工具、嵌入式系统仿真工具等,选择合适的工具变得至关重要。

在本文中,我将对几种常见的电路仿真工具进行比较,并提供选择指南,帮助工程师们更好地选择适合自己需求的工具。

1. SPICE仿真器SPICE(Simulation Program with Integrated Circuit Emphasis)是一种通用的电路仿真工具,具有广泛的应用范围。

它可以模拟各种电路,包括模拟电路、数字电路、混合信号电路等。

SPICE仿真器的核心是基于各种电路元件的数学模型进行计算,能够准确地模拟电路的行为和特性。

然而,SPICE仿真器的计算速度比较慢,对于大型复杂电路的仿真可能会耗费较长的时间。

2. EDA工具EDA(Electronic Design Automation)工具是一类专门用于电子设计的集成软件工具,包括原理图绘制、电路仿真、PCB设计、封装设计等功能。

EDA工具在电子设计过程中起着至关重要的作用,可以帮助工程师快速、高效地完成设计任务。

常见的EDA工具有Cadence、Mentor Graphics、Altium Designer等,它们提供了强大的仿真功能,适用于各种不同类型的电路设计。

3. 嵌入式系统仿真工具嵌入式系统仿真工具主要用于嵌入式系统设计,可以帮助工程师验证系统的功能和性能,减少硬件设计和调试的时间。

常见的嵌入式系统仿真工具有ModelSim、Quartus II等,它们具有强大的仿真和调试功能,能够帮助工程师快速验证系统设计的正确性。

在选择电路仿真工具时,工程师应根据自己的设计需求和预算来进行评估和比较。

以下是一些建议的选择指南:1. 确定设计需求:首先要明确自己的设计需求,包括电路类型、仿真规模、仿真精度等,然后选择功能和性能适合的仿真工具。

Cadence cdsSPICE的使用说明

第一章.Cadence cdsSPICE的使用说明Cadence cdsSPICE 也是众多使用SPICE内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE相同。

这里我将侧重讲一下它的一些特殊用法。

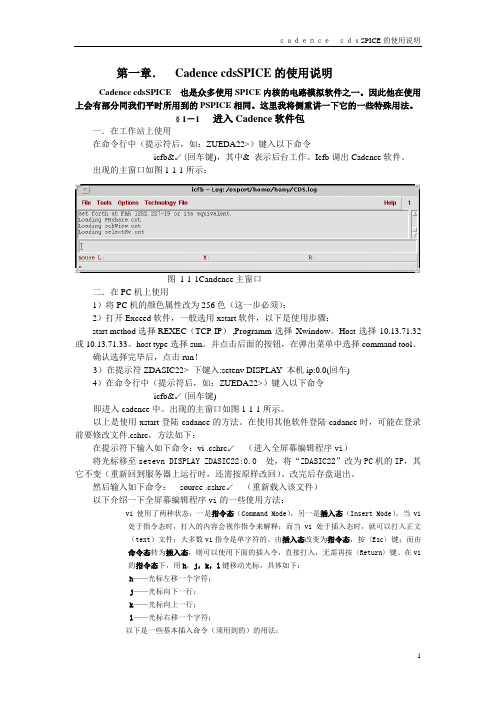

§ 1-1 进入Cadence软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb调出Cadence软件。

出现的主窗口如图1-1-1所示:图1-1-1Candence主窗口二.在PC机上使用1)将PC机的颜色属性改为256色(这一步必须);2)打开Exceed软件,一般选用xstart软件,以下是使用步骤:start method选择REXEC(TCP-IP) ,Programm选择Xwindow。

Host选择10.13.71.32 或10.13.71.33。

host type选择sun。

并点击后面的按钮,在弹出菜单中选择command tool。

确认选择完毕后,点击run!3)在提示符ZDASIC22> 下键入:setenv DISPLAY 本机ip:0.0(回车)4)在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键)即进入cadence中。

出现的主窗口如图1-1-1所示。

以上是使用xstart登陆cadance的方法。

在使用其他软件登陆cadance时,可能在登录前要修改文件.cshrc,方法如下:在提示符下输入如下命令:vi .cshrc↙(进入全屏幕编辑程序vi)将光标移至setevn DISPLAY ZDASIC22:0.0 处,将“ZDASIC22”改为PC机的IP,其它不变(重新回到服务器上运行时,还需按原样改回)。

改完后存盘退出。

然后输入如下命令:source .cshrc↙(重新载入该文件)以下介绍一下全屏幕编辑程序vi的一些使用方法:vi使用了两种状态,一是指令态(Command Mode),另一是插入态(Insert Mode)。

集成电路_Spice,Spectre仿真总结

集成电路_Spice,Spectre仿真总结Designers-Guide to Spice and Spectre 1995 USA Designers-Guide to Spice a nd Spectre — Ken Kundert 11.1 绪论 1. 为什么要读这本书①该书是介于算法和教你如何操作软件之间的一本书可以帮助你更好的使用Simulator的设置。

② Simulator仿出的结果可靠不精确不是否收敛应该如何处理如何设置③读完这本书你应该会 1 Simulator如何计算结果 2 Simulator会产生何种错误如何识别 3 如何提高仿真精度 4 如何克服不收敛的情况 5 对于一些特殊电路会产生什么错误如何识别 6 明白仿真器里设置convergenceerror control的一些重要参数 7 能知道仿真器的错误信息出在什么地方如何解决 2. 电路仿真软件的发展历史①直接方法求出电路的微分方程组用数值积分方法差分化然后用牛顿迭代法求解非线性代数方程组。

⇒是最准确可靠最通用的方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多 3. Spice Options ① Global Options: Abstol控制电流默认为1pA Vntol控制电压默认为1uV Reltol相对误差对于牛顿收敛准则和截断误差准则同时起作用默认10-3对于重要电路这个应该设置小一些比如说10-5或者10-6Gmin防止非线性器件关断后的浮空节点默认为10-12 Ω-1LimptsPivrelPivtol无用处② DC Analysis Options: ltl1DC工作点最大牛顿迭代次数默认100 ltl2DC Sweep最大牛顿迭代次数默认50 ltl6Source Stepping的最大步长数增加以上3个值可以增加DC牛顿迭代收敛但是会降低速度。

EDA技术实用教程

EDA技术实用教程EDA是电子设计自动化(Electronic Design Automation)的缩写,指的是利用计算机技术和工具自动辅助设计和验证电子系统的过程。

EDA 技术的应用广泛,包括芯片设计、电路设计、电子系统设计等。

本文将介绍EDA技术的基本概念和常用工具,以及它们在电子系统设计中的应用。

1.EDA技术概述EDA技术是利用计算机技术和工具实现电子系统设计自动化的一系列技术方法。

它能够大大提高设计效率和设计质量,缩短设计周期,降低成本。

EDA技术包括模拟电路设计、数字电路设计、封装设计、布线设计等多个方面。

2.EDA常用工具常用的EDA工具包括电路仿真工具、逻辑综合工具、版图设计工具、时序分析工具、布局布线工具等。

这些工具在EDA技术中发挥着重要的作用,帮助设计人员完成不同层次的设计任务。

3.电路仿真工具电路仿真是EDA技术中最基础也是最重要的环节之一、它通过建立模型,对电路进行数学分析和计算,模拟电路的工作状态和性能。

常用的电路仿真工具有SPICE、SPECTRE等。

电路仿真工具能够帮助设计人员在设计之前评估电路的性能,并发现潜在的问题,优化设计。

4.逻辑综合工具5.版图设计工具版图设计是将逻辑电路网表进行物理布局和布线的过程。

版图设计工具可以根据约束条件自动进行版图布局和布线,生成满足电路性能和约束条件的版图。

常用的版图设计工具有ICC、Innovus等。

6.时序分析工具7.布局布线工具布局布线是指将版图中的电路元件进行布置和互连的过程。

布局布线工具可以根据电路性能和约束条件进行自动布局和布线,生成满足性能和约束的物理布局和互连。

常用的布局布线工具有Olympus、Innovus等。

8.EDA技术在电子系统设计中的应用EDA技术在电子系统设计中有着广泛的应用。

它可以帮助设计人员设计和验证复杂的电路和系统,提高设计效率和设计质量。

在芯片设计中,EDA技术可以辅助完成电路设计、逻辑综合、版图设计、布局布线等任务。

集成电路设计CADEDA工具实用2-Spice_Spectre

Cadence中Spectre的模拟仿真 Hspice的使用 Ultrasim仿真技术

2020/1/30

共79页

1

模拟集成电路的设计流程

1.交互式电路图输入

2.电路仿真 3.版图设计

全定制

4.版图的验证(DRC LVS)

5.寄生参数提取

6.后仿真

7.流片

2020/1/30

2020/1/30

共79页

16

2020/1/30

工具栏介绍

从上至下:

1.Check and Save

2.Save

3.Zoom in by 2 ]

4.Zoom out by 2 [

5.Stretch

s

6.Copy

2020/1/30

共79页

4

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: ASIC 设计

全定制IC设计工具Virtuoso Schematic Composer 电路仿真工具Analog Design Environment FPGA 设计 PCB设计

2020/1/30

共79页

12

Tools菜单

在Tools菜单下,比较常 用的菜单项有

Library Manager

Library Path Editor

Technology File Manager

Library Manager项打开的是库管 理器。在窗口的各部分中,分别 显示的是Library、Category、Cell、 View相应的内容。

共79页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

集成电路设计CAD_EDA工具实用教程1-Spectre_Verilog数模混合仿真

共27页

26

THANK YOU!

共27页

27

同时包含模拟和数字两个仿真核

处理速度快,能处理的电路规模极大,但需要解决模拟仿真核和数字 仿真核之间的通信问题;另外,由于数字逻辑仿真器和模拟仿真器的输 入、输出数据是不一样的,还必须在模拟仿真核和数字仿真核之间实现 模拟信号和数字信号的相互转换。

共27页

Q&A

9

Creating Analog Block

共27页

8

Mixed-Signal Simulator 的基本结构

以模拟电路仿真器为核心

在处理数模混合电路时将数字部分等效为相应的简化的模拟电路、或 者采用解析函数来表示逻辑模块的行为,然后对整个系统采用模拟电路 的方法进行模拟。优点:模拟结果精确、能处理的电路规模比较大,模 拟速度也有显著提高。缺点:比逻辑模拟器还是慢很多。

共27页

24

Submit the Simulation

Execute the simulation job with Run, or create the netlist with Netlist

start simulation

共27页

25

Results

数 字 输 出 数字 /模 拟输 入

模 拟 输 出

选择SpectreVerilog

共27页 23

Choose Analysis Type

Invoke the analysis setting window

For Mixed-Signal simulation, only tran is meaningful Set the simulation time Check this box to enable this simulation

集成电路设计师必备的实用工具与软件介绍

集成电路设计师必备的实用工具与软件介绍As a Baidu Wenku document creator, I will introduce the necessary tools and software for integrated circuit designers. 。

Integrated circuit designers require various practical tools and software to effectively carry out their work. In this essay, I will introduce several essential tools and software that every integrated circuit designer should have.Firstly, simulation software is crucial for circuit designers. It allows designers to simulate and analyze the performance of their circuits before actually implementing them. One widely used simulation software is SPICE (Simulation Program with Integrated Circuit Emphasis). SPICE provides accurate and reliable circuit analysis, helping designers identify potential issues and optimize circuit performance.In addition to simulation software, design software is also essential for integrated circuit designers. Design software, such as Cadence and Mentor Graphics, enables designers to create and layout circuit designs. These software tools offer a wide range of features, including schematic capture, layout design, and design rule checking. With these tools, designers can efficiently design and implement complex circuits.Apart from simulation and design software, hardware tools are also necessary for circuit designers. One important hardware tool is the field-programmable gate array (FPGA) development board. FPGA development boards allow designers to prototype and test their circuits in a real-world environment. These boards provide flexibility and reconfigurability, making them ideal for rapid prototyping and system verification.Another indispensable hardware tool is the logic analyzer. Logic analyzers help designers debug and analyze digital circuits. They can capture and display digital signals, allowing designers to examine the behavior of their circuits at a detailed level. With the information obtained from a logic analyzer, designers can identify and fix issues in their circuit designs effectively.In summary, integrated circuit designers require various practical tools and softwareto carry out their work effectively. Simulation software, design software, and hardware tools such as FPGA development boards and logic analyzers are essential for circuit designers. By utilizing these tools, designers can simulate, design, and analyze circuits, ensuring optimal performance and functionality. It is crucial for integrated circuit designers to stay updated with the latest tools and software in order to excel in their field. 。

spice和spectre软件使用和运放的仿真方法

【:缩小显示 】:放大显示 R:旋转 R+F3:水平或垂直镜像翻转 其它常用操作: W后按鼠标右键:改变连线方式,折线→直线 按住Ctrl左键拖动:不带连线关系拖动 按住Shift选择:同时选择

Cadence仿真

两种仿真工具:

Spectre(所用模型后缀为.scs) Hspice (所用模型后缀为.lib)

基本语法

1. 不区分大小写(case insensitive) 2. 注释:* or $ 3. 数量级表示符号:

T

E12

G

E9

MEG

E6

K

E3

M

E-3

U

E-6

N

E-9

p

E-12

F

E-15

(关键不要搞错M和MEG) 4.赋值单位可以省略

仿真网表的五个主要组成部分

1.电路网表 2.激励 3.仿真分析语句 4.输出命令 5.模型库文件

end用montecarlo仿真来分析失配导致的失调分布失调分布分析30次montecarlo仿真结果由此可见ota的失调分布可达10mv10mv可增大晶体管来减小vos但是会带来速度问题压摆率分析在输入端输入一个较大的脉冲信号以观察输出端的电压摆率在otanet中将vvac的定义换成

软件使用和运放主要 指标的仿真方法

电路网表

包含的内容有器件连接关系、模型名、参 数值、(赋值)、并联个数、(初始值) 例: R1 N1 N2 R W=10u L=1u R2 N1 N2 10K C1 N1 N2 C W=10u L=1u C2 N1 N2 10p C3 N1 N2 10p IC=1

电路网表

L1 N1 N2 1m D1 N1 N2 diode Q1 NC NB NE bjt M=8

OrCad培训教材-原理图capture-电路板layout-仿真pspice

OrCAD 培训教材深圳光映计算机软件有限公司——洪永思Capture FeaturesVendor specific librariesIntegration with all other OrCAD EDA toolsNetlist interface to other PCB desig1packagesCross-probing and bi-directional annotation between schematic and PCB designs.Integration of company parts database (Capture CIS).Customized Bill of Materials reportsPSpice Features提供一个对电路进行仿真的环境分析验证你的电路对电路进行参数优化对器件的模型参数进行提取Layout Features提供对PCB板进行设计的环境周到齐全的EDA软件接口功能强大的机械设计环境(Visual CCAD)与制作加工相结合的GerbTool工具功能多样的策略与模板OrCAD的基础知识OrCAD常用文档类型*.opj—项目管理文件*.dsn—电路图文件*.olb—图形符号库文件*.lib—仿真模型描述库文件*.mnl—网络表文件*.max—电路板文件*.tch—技术档文件*.gbt—光绘文件*.llb—PCB封装库文件*.log *.lis—记录说明文件*.tpl—板框文件*.sf—策略档文件OrCAD软件包含的库1、*.olb-Capture专用的图形符号库只有电气特性,没有仿真特性的库。

此类库没有相应的*.lib库,且器件属性中没有PspiceTemplate属性。

能够利用PSpice进行仿真的库。

此类库有相应的*.lib库,且器件属性中有PspiceTemplate属性。

2、*.lib-PSpice仿真库,利用Spice语言对Capture中的图形符号进行功能定义与描述,可以编辑。

集成电路器件及SPICE模型通用课件

场效应管的SPICE模型

场效应管SPICE模型是模拟场效应管特性的数学模型。

场效应管SPICE模型包括沟道电流、阈值电压等参数,用于模拟场效应管在电路 中的行为。

集成电路器件SPICE模型的参数提取与优化

异构集成与三维集成中的SPICE模型挑战

随着集成电路技术的发展,异构集成和三维集成已经成为趋势。在异构集成和三维集成中, 不同材料和器件之间的相互作用和耦合效应更加复杂,因此需要更加精细的SPICE模型来模 拟。

现有的SPICE模型主要是针对单一器件或单一材料的仿真而设计的,因此在异构集成和三维 集成中需要进行改进和扩展。这需要研究新的建模方法和参数提取技术,以适应不同材料和 器件之间的耦合效应。

电阻器

电阻器是限流元件,用于调节 电路中的电流和电压,分为线 绕、薄膜和厚膜电阻器等类型。

电容器

电容器是储能元件,用于隔直、 滤波和旁路等作用,分为陶瓷、

薄膜和电解电容器等类型。

集成电路器件的工作原理

双极型晶体管工作原理

双极型晶体管利用载流子的扩散与漂移运动 控制电流,具有电流放大作用。

二极管工作原理

优化设计

基于SPICE模型的仿真结果,可以对 电路设计进行优化,改进电路的性能 指标,降低功耗和提高稳定性。

元件匹配与版图布局

元件匹配

SPICE模型可以模拟元件之间的匹配 情况,帮助设计者找到元件的最佳配 置,以确保电路性能的稳定。

版图布局

利用SPICE模型进行版图布局的模拟, 可以预测元件之间的耦合效应和信号 干扰,从而优化版图设计。

VS

效率

Spectre仿真器在集成电路设计的应用

卢小冬 大唐微电子,集成电路设计部

摘要: Spectre是一个非常重要的、非直接继承SPICE(Simulation Program with Integrated Circuit Emphasis)的电路数值模拟器之一。通过一个众所周知的集成电路单元-CMOS运算放大器的参 数仿真提取,本文简要介绍了如何在模拟集成电路的设计自动化中使用Spectre工具。总的来说, Spectre仿真器不但能以更快的速度和更好的收敛特性支持现有的所有SPICE分析,还能提供很 多额外的功能。通过将Spectre工具引入集成电路设计自动化,好处远不止得到一个强大的分析 工具本身。

两个网表分别存储在文件 model.scs 和 ova.scs 中。可以使用 Spectre 仿真器的“include”语 句将这两个网表包含中仿真的网表文件中,这样通过在仿真文件的电路网表中实现图 2 的不同 配置电路即可进行所有的仿真。

Vdiff/2 +

Vcom

+ + Vdiff/2

_ A

+

Vout Cload

本文介绍了在CMOS模拟电路仿真中如何使用Spectre仿真器进行基本的分析。一个CMOS 的电压运算放大器(OVA)被用来作为介绍仿真器使用的电路实例。为了简单起见,文章不涉 及AMS设计环境,而是用Spectre的网表(Netlist)仿真模式。由于难以在此详尽展示Spectre仿 真器的强大功能,因此在结尾又额外添加了一段独立强调了Spectre的重要特性。

(Miller-effect)补偿电容 Cm 。电路单元的管脚包括:电源(VDD 和VSS / GND ), 差分信号 输入Vin− 和Vin+ ,信号输出Vout 。

Spectre仿真器在集成电路设计的应用

无论是手工设计还是数值模拟,电路设计的目标都是确定上述参数。这样,在复杂的电路系统 中,运算放大器单元就可以使是用于 Spectre 仿真分析的、经典结构的运算放大器。其中晶体管 M8 和 M9 构 成电流参考源,它用于偏置放大电路。其他电路包括:由 M1 和 M2 组成的差分输入级,有源 负载(M3 和 M4),电流源(M7)和反向输出级(M6,由 M5 提供电流源)和一个密勒效应

Spectre是一个非常重要的、不是直接由SPICE继承而来的电路仿真工具。经过多年作为 cdsSpice(Cadence公司早期的SPICE类仿真工具)仿真工具以外选项之后,Spectre已经完全被 集成到Cadence的AMS设计环境之中,并作为仿真环境下标准的模拟电路仿真工具。它能够提供 SPICE仿真具有的直流(DC),小信号交流(AC)、瞬态(TRAN)标准分析功能,也能提供基 于工艺参数的灵敏度(sensitivity)和蒙特卡洛(Monte Carlo)分析,基于电路拓扑(无源元件 参数)的分析,以及其他重要的电路分析功能。

表 3 参数提取-仿真电路配置关系

参数

配置

分析功能

IR

Open Loop

OR

Vcom = 2.5V DC sweep of Vdiff

CMR

VTC Vout vs Vdiff

Follower

Voff

Follower

DC sweep of Vin VTC Vout vs Vin

Vin = 2.5V

Monte Carlo of Operating Point

集成电路_Spice,Spectre仿真总结

集成电路_Spice,Spectre仿真总结Designers-Guide to Spice and Spectre 1995 USA Designers-Guide to Spice a nd Spectre — Ken Kundert 11.1 绪论 1. 为什么要读这本书①该书是介于算法和教你如何操作软件之间的一本书可以帮助你更好的使用Simulator的设置。

② Simulator仿出的结果可靠不精确不是否收敛应该如何处理如何设置③读完这本书你应该会 1 Simulator如何计算结果 2 Simulator会产生何种错误如何识别 3 如何提高仿真精度 4 如何克服不收敛的情况 5 对于一些特殊电路会产生什么错误如何识别 6 明白仿真器里设置convergenceerror control的一些重要参数 7 能知道仿真器的错误信息出在什么地方如何解决 2. 电路仿真软件的发展历史①直接方法求出电路的微分方程组用数值积分方法差分化然后用牛顿迭代法求解非线性代数方程组。

⇒是最准确可靠最通用的方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多 3. Spice Options ① Global Options: Abstol控制电流默认为1pA Vntol控制电压默认为1uV Reltol相对误差对于牛顿收敛准则和截断误差准则同时起作用默认10-3对于重要电路这个应该设置小一些比如说10-5或者10-6Gmin防止非线性器件关断后的浮空节点默认为10-12 Ω-1LimptsPivrelPivtol无用处② DC Analysis Options: ltl1DC工作点最大牛顿迭代次数默认100 ltl2DC Sweep最大牛顿迭代次数默认50 ltl6Source Stepping的最大步长数增加以上3个值可以增加DC牛顿迭代收敛但是会降低速度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2018/1/16

共79页

8

方法二

1、安装winvnc软件 2、运行putty软件键入 用户名和密码,在提示 符处键入 vncserver命 令申请vnc端口 3、运行winvnc,填入 主机名称:端口号码

2018/1/16

共79页

9

二、建立可进行SPECTRE模拟 的单元文件

主窗口分为信息窗口 CIW、命令行以及主 菜单。信息窗口会给 出一些系统信息(如 出错信息,程序运行 情况等)。在命令行 中可以输入某些命令。

Schematic Symbol

Library

2018/1/16

Cell

Layout Verilog

(View)

共79页

11

Library,Cell以及View

1、library(库)的地位相当于文件夹,它用来存放一整个设计 的所有数据,包括子单元(cell)以及子单元(cell)中的 多种视图(view)。新建时注意选择是否链接techfile。 2、Cell(单元)可以是一个简单的单元,像一个与非门, 也可以是比较复杂的单元(由symbol搭建而成)。 3、View则包含多种类型,常用的有schemetic,symbol, layout,extracted,ivpcell等等 ,新建Cellview要注意选择 View的类型。

2018/1/16

共79页

4

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: ASIC 设计 全定制IC设计工具Virtuoso Schematic Composer 电路仿真工具Analog Design Environment FPGA 设计 PCB设计

2018/1/16

共79页

3

高精度电路仿真器

1、Spectre/SpectreRF(cadence) 2、Hspice/HspiceRF(avanti) 3、Ads(Agilent 主要针对RF) 4、eldo(Mentor Graphics) 5、saber(Synopsys)

共79页

2

各种仿真器简介

SPICE : 由UC Berkeley 开发。用于非线性 DC分析,非 线性瞬态分析和线性的AC分析。

Hspice: 作为业界标准的电路仿真工具,它自带了许多器 件模型,包括小尺寸的MOSFET和MESFET。Cadence提 供了hspice的基本元件库并提供了与Hspice的全面的接口。 Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

content

Cadence中Spectre的模拟仿真 Hspice的使用 Ultrasim仿真技术

2018/1/16

共79页

1

模拟集成电路的设计流程

1.交互式电路图输入 2.电路仿真

全定制

3.版图设计

4.版图的验证(DRC LVS) 5.寄生参数提取 6.后仿真 7.流片

2018/1/16

2018/1/16

共79页

5

Cadence中Spectre的模拟仿真

1、进入Cadence软件包 2、建立可进行SPECTRE模拟的单元文件 3、编辑可进行SPECTRE模拟的单元文件 4、模拟仿真的设置(重点) 5、模拟仿真结果的显示以及处理 6、分模块模拟(建立子模块) 7、运算放大器仿真实例

2018/1/16

共79页

16

工具栏介绍

从上至下: 1.Check and Save 2.Save 11.Wire(Narrow) 12.Wire(Wide) w

3.Zoom in by 2

2018/1/16

共79页

12

Tools菜单

在Tools菜单下,比较常 用的菜单项有 Library Manager Library Path Editor Technology File Manager

Library Manager项打开的是库管 理器。在窗口的各部分中,分别 显示的是Library、Category、Cell、 View相应的内容。

主菜单包括: 1、File菜单 2、Tools菜单 3、Options菜单

2018/1/16

共79页

10

File菜单

在File菜单下,主要的菜单 项有New、Open、Exit等 New菜单项的子菜单下有 Library、Cell view两项。 Library项打开New Library窗 w File窗口。 Open菜单项打开相应的 Open File窗口。 Exit项退出Cadence软件包。

2018/1/16

共79页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

2018/1/16

共79页

7

1、键入用户名和密码, 在提示符处键入: source/opt/demo/cds. env(回车) 2、setenv DISPLAY 本机ip:0.0(回车),再 键入icfb&,出现的主 窗口如图所示:

14

Options菜单

Options菜单主要是对 Cadence的一些参数 进行调整和设置,如 快捷键等。一般无需 设置,直接使用默认 值。

2018/1/16

共79页

15

三、编辑可进行SPECTRE模拟 的单元文件

选择主窗口 File→Open→Open file, 打开相应的Schematic View,即进入了 Composer-Schematic Editing 窗口,如右图 所示。

2018/1/16 共79页 13

Library Path Editor & Technology File Manager

Library Path Editor 可以对本用户的文件 路径进行修改

2018/1/16

共79页

Technology File Manager基本上都是和 工艺相关的功能和设置。 比较常用的是Edit Layers 可以使用在版图 编辑中,用来修改原始 图层的一些属性。