基于主_从结构的多CPU系统的研究与实现

多核处理器的发展前景和存在问题综述

多核处理器的发展前景和存在问题综述目录1.概述 (2)2.处理器的发展趋势 (2)从单核到多核 (3)同构多处理器与异构多处理器 (3)多核处理器发展面临的挑战 (4)多核与多线程技术 (4)3.多核处理器的高速缓存一致性问题 (4)增强一致性的基本方案 (5)目录式Proximity-aware 协议 (5)4.多核加速串行程序的主要方法 (8)并行编译器 (8)推测多线程 (9)基于线程的预执行机制 (9)5. 总结 (10)参考文献 (11)1. 概述在过去的几十年时间里,处理器的性能一直按照莫尔定律在发展。

提高处理器性能的基本方法就是不断提升主频。

从初期的几十MHz到不久前IBM的Power 6达到了,设计人员甚至想过提升到7G~8GHz。

不过,进入2002年以来,CPU 提升主频的困难越来越大,因为主频的提升带来了散热和功耗的大幅增加等问题。

在几年前,英特尔和AMD都调整了研究方向,开始研究在同一CPU中放置多个执行内核。

说到底,出现多核处理器的最根本原因是人们对计算能力永无止境的追求。

尽管这些年来,处理器从来没有停止过前进的脚步,但每一次性能的突破,换来的只是对更高性能的需求,特别是在油气勘探、气象预报、虚拟现实、人工智能等高度依赖于计算能力的场合,对性能的渴求更加迫切。

既然单处理器的发展已经到了瓶颈,而多核将会引领以后处理器发展的潮流,那么我们就看看多核处理器带给我们什么样的性能提升,多核处理器要全面应用到各个领域所需解决的问题。

多核的好处非常明显。

首先,由于是多个执行内核可以同时进行运算,因此可以显著提升计算能力,而每个内核的主频可以比以前低,因而总体功耗增加不大。

其次,与多CPU相比,多核处理器采用与单CPU相同的硬件架构,用户在提升计算能力的同时无需进行任何硬件上的改变,这对用户来说非常方便。

然而,多核处理器要发挥它的作用必须要解决许多问题,不像CPU的频率提升,无论如何你都可以从中受益,要从多核处理器中受益,首先在设计多核处理器时,要注意不同核心之间的通信与数据的一致性,另外,在软件层次上也需要对多核进行改进,以充分利用多核的性能。

CPU的多核心架构及计算单元详解

CPU的多核心架构及计算单元详解中央处理器(CPU)是计算机系统中的核心组件之一,它承担着执行计算和控制操作的任务。

随着计算机的快速发展,人们对于性能的要求也越来越高。

为了满足用户对于多任务处理和高性能计算的需求,CPU的多核心架构逐渐兴起。

本文将详细介绍CPU的多核心架构以及其中的计算单元。

一、CPU的多核心架构1.1 多核心概念及发展多核心是指在一个CPU芯片上集成多个独立的处理器核心。

与传统的单核心CPU相比,多核心架构能够同时处理多个线程或任务,提升计算机的整体性能。

多核心架构的发展源于摩尔定律的进展。

根据摩尔定律,集成电路中的晶体管数量每18个月翻倍,这意味着CPU的计算能力也在同期间不断提升。

然而,到了一定程度,提升频率并不能显著增加CPU的性能,因为频率增加会导致功耗和发热的问题。

因此,为了进一步提升性能,多核心架构成为了解决方案。

1.2 多核心的优势多核心架构具有如下几个优势:1.2.1 提升系统性能:多核心能够同时处理多个任务或线程,有效提高了系统的整体性能。

特别是对于多线程应用程序或者同时执行多个任务的场景,多核心能够更好地满足用户需求。

1.2.2 节能降耗:与提升频率相比,多核心架构能更好地平衡性能和功耗。

通过将任务分配到多个核心上执行,每个核心的工作频率可以降低,从而减少功耗和发热,延长电池续航时间。

1.2.3 增强并行计算能力:多核心为并行计算提供了强大的支持。

对于需要大量计算的应用程序,多个核心可以同时进行计算,加速处理过程。

1.3 多核心架构的实现方式多核心架构的实现方式主要有对称多处理(SMP)和复杂指令集计算(CISC)。

对称多处理(SMP)是指每个核心拥有相同的访问权限和权力,可以独立运行不同的任务。

SMP架构中,每个核心可以共享同一份操作系统,从而实现大部分应用程序的并行执行。

复杂指令集计算(CISC)则是在一个CPU芯片上,集成多个核心以及专用的计算单元,每个计算单元负责执行特定类型的计算任务。

高性能微处理器结构设计与优化研究

高性能微处理器结构设计与优化研究在当今数字化的时代,微处理器已经成为了一个非常重要的基础设施。

微处理器广泛应用在各种电子产品中,如手机、电脑、服务器等等,作为CPU的核心部件,其性能直接影响着整个系统的工作效率和稳定性。

在这样的背景下,高性能微处理器的研究和优化也变得越来越重要。

从最初的微处理器出现至今,性能的发展已经取得了巨大的进步。

英特尔公司的X86系列处理器已经发展成为了全球性能最快的产品之一。

例如,最近发布的英特尔酷睿i9-11900K处理器拥有8个核心、16个线程,最高主频可达到5.3GHz,配合高速内存和大容量存储,可以提供前所未有的运行速度和快速响应。

高性能微处理器的构成一般由多个部分组成,其中最为核心的部分就是计算单元。

计算单元可以分为算术逻辑单元(ALU)和浮点逻辑单元(FPU)两种。

ALU主要完成整数运算,如加减乘除等,而FPU则主要用于浮点运算,如加减乘除、开根、三角函数等。

同时,高性能微处理器还包括缓存、穿透缓存、磁盘控制器等模块,以及一些特殊用途的协处理器和图像加速器等。

高性能微处理器的设计和优化是一个非常复杂的任务,需要多个专业领域的知识和技术结合才能完成。

优化技术非常多,如:1. 指令优化技术指令优化技术主要是通过改变指令执行的顺序和方式来提高微处理器的性能。

例如,采用超标量设计和预测分支等方式可以提高处理器的吞吐量和效率。

2. 缓存优化技术缓存优化技术主要是通过调整缓存大小和级别,改善缓存访问策略,以及采用智能预取等方法来提高缓存的利用率和效率。

3. 浮点运算优化技术浮点运算优化技术主要是通过改善浮点运算单元的设计和实现方式,如使用超标量技术和硬件浮点加速器等,来提高浮点运算的速度和精度。

近年来,随着人工智能、深度学习、云计算等领域的快速发展,高性能微处理器也面临巨大的挑战。

为了满足这些新应用的需求,微处理器的设计和优化技术需要不断地更新和升级。

同时,新的硬件架构和虚拟化技术也在不断涌现。

《基于FPGA的多核处理器系统的研究与设计》范文

《基于FPGA的多核处理器系统的研究与设计》篇一一、引言随着科技的快速发展,处理器性能的需求不断提升,传统单核处理器已经难以满足日益增长的计算需求。

因此,多核处理器系统成为了研究的热点。

本文以基于FPGA(现场可编程门阵列)的多核处理器系统为研究对象,对其进行了详细的研究与设计。

二、研究背景及意义FPGA作为一种可编程的硬件设备,具有高度的并行性、灵活性和可定制性,因此被广泛应用于高性能计算、信号处理等领域。

而多核处理器系统则通过集成多个处理器核心,实现了更高的计算性能和更快的处理速度。

将FPGA和多核处理器系统相结合,可以构建出高性能、高灵活性的多核处理器系统,对于提高计算性能、降低功耗、增强系统稳定性等方面具有重要的意义。

三、FPGA多核处理器系统的设计(一)系统架构设计基于FPGA的多核处理器系统主要由多个FPGA芯片组成,每个FPGA芯片上集成了多个处理器核心。

系统采用共享内存的方式,实现了各个处理器核心之间的数据交换和通信。

此外,系统还包含了控制模块、接口模块等部分,以实现系统的整体控制和外部接口的连接。

(二)处理器核心设计处理器核心是FPGA多核处理器系统的核心部分,其设计直接影响到整个系统的性能。

在处理器核心设计中,需要考虑指令集设计、数据通路设计、控制单元设计等方面。

指令集设计需要考虑到指令的兼容性、可扩展性和执行效率;数据通路设计需要考虑到数据的传输速度和带宽;控制单元设计则需要考虑到处理器的控制流程和时序。

(三)系统通信设计系统通信是FPGA多核处理器系统中非常重要的一部分,它涉及到各个处理器核心之间的数据交换和通信。

在系统通信设计中,需要考虑到通信协议的设计、通信接口的选择、通信速度和带宽等方面。

常用的通信协议包括总线协议、消息传递协议等,需要根据具体的应用场景进行选择和设计。

四、系统实现与测试(一)硬件实现在硬件实现阶段,需要根据设计要求选择合适的FPGA芯片和开发工具,完成电路设计和布局布线等工作。

基于同构多核处理器的任务调度①-计算机系统应用

基于同构多核处理器的任务调度①许雍祯, 陈香兰, 李曦, 周学海(中国科学技术大学计算机科学与技术学院, 合肥 230001)摘 要: 随着现代应用对计算机性能要求的提高, 计算机主频不断提升. 由于功耗和半导体工艺的限制, 仅靠提高单核主频难以继续维持“摩尔定律”, 同构多核处理器(Homogeneous Multi-core)应运而生. 在同构多核处理器的支持下, 一个芯片汇集多个地位对等、结构相同的通用处理器核, 以最小的代价满足了提高系统性能、负载均衡、处理器容错的需要. 并行体系结构需要结合与之适应的软件实现性能效益的倍增. 本文从操作系统层面, 针对处理器结构的变化, 研究并实现多核任务调度. 系统采用混合调度策略, 簇间独立调度, 簇内统一调度. 从调度模式、调度算法、分配算法、调度时机等方面详细分析了多核调度的原理和实现机制. 最后通过模拟实验证明功能正确性及算法可调度性.关键词: 同构多核处理器; 任务调度; 分簇混合调度; 查找算法; 分配算法Scheduling on Homogeneous Multi-Core SystemXU Yong-Zhen, CHEN Xiang-Lan, LI Xi, ZHOU Xue-Hai(School of Computer Science and Technology, University of Science and Technology of China, Hefei 230001, China)Abstract: The frequency of CPU has boosted in recent years to meet the requirement of modern application on compute performance. However, the “Moore Law” can’t be maintained only by increasing the frequency of single chip, the homogeneous multi-core system has appeared to compensate this insufficient. With the support of homogenous multi-core processors, the chip puts multiple processors with same status and structure together to minimize the cost of performance improving, load balancing and fault tolerance. The performance of parallel system is doubling when combining with appropriate software. In this paper, our research is focused on the multi-core task scheduling along with the changes in processor architecture from operating system level. The system uses hybrid scheduling which is composited of independent inter-cluster scheduling and unified inner-cluster scheduling. We do some deep analyzing on multi-core scheduling theory and implementation strategy from different aspects, including scheduling model, scheduling algorithm, dispatch algorithm and scheduling occasion. The experiment results prove the correctness and schedulability of the algorithms.Key words: homogeneous multi-core processor; task scheduling; hybrid scheduling; search algorithm; distribute algorithm1引言随着应用需求的扩展和软件技术的进步, 处理器性能提升需求激增. 通过提高处理器频率来提升系统性能的方法受到功耗、成本及体积的限制, 单核处理器验证以继续维持“摩尔”定律[1], 同构多处理器,(Homogeneous Multi-core)应运而生. 同构多核处理器是指在一块芯片上使用多个地位对等、结构相同的的通用处理器核, 各核执行相同或相似任务, 整个芯片作为一个统一的结构对外提供服务, 输出性能, 以最小的代价满足提高性能、实现负载均衡的需要[2].①基金项目:国家自然科学基金(61272131)收稿时间:2014-03-02;收到修改稿时间:2014-04-02单靠多核处理器平台并不能实现性能的倍增效益, 需要与多核硬件相适应的软件, 才能真正发挥多核的性能. 操作系统作为计算机的系统软件, 能否针对处理器结构的改变, 管理硬件并且为应用软件提供基础平台, 是多核处理器结构应用的基础问题.操作系统的任务调度对充分发挥多处理器结构的并行性起到决定性的作用. 如何通过恰当的调度机制和策略保证多核的负载均衡, 并充分发挥各处理器的性能特点、提高整个系统的吞吐量, 是多核任务调度的研究核心. 本文以多核处理器为具体硬件环境, 研究并实现同构多核上的任务调度.2 调度模式的选择调度模式是指运行调度程序的处理器选择, 即哪个处理器来执行调度, 有 “集中调度模式”和 “分布调度模式”两种模式. 2.1 集中调度模式集中调度模式指定一个特定的处理器作为主处理器(Master), 负责整个系统中所有任务的调度, 包括任务的初始化、任务的切分、任务的分配、任务的合并等工作, 如图1. 系统中其他剩余的处理器作为从处理器(Slave), 用于执行主处理器分配的任务.1 集中式调度模式 若集中式调度模式应用在大规模并行处理器MPP 结构中, 主处理器很可能成为整个系统的瓶颈. 另一方面, 若系统中仅存在较少的处理器, 主处理器可能成为较闲的处理器, 造成资源的浪费. 2.2 分布式调度模式本系统采取分布式调度模式, 所有处理器处于平等地位, 每个处理器都可以运行调度程序.在分布式调度模式中, 需要保证各核对共享资源(如: 公共就绪队列)的互斥访问, 因此存在多核同步问题. 同时, 由于该模式中所有核对等运行调度程序, 假设核A 选择核B 执行新的就绪任务, 此时需要核A 通知核B 进行任务切换, 因此存在多核通信问题. 2.2.1 多核同步本系统设计自旋锁(spin lock)保证各核对共享资源的互斥访问. 以公共就绪队列为例, 访问公共就绪队列前, 需要获得自旋锁. 某核申请自旋锁时, 若自旋锁没有被占用, 就占用该自旋锁, 执行代码; 若自旋锁已经被另一CPU 占用, 则该CPU 采取 “忙等”方式, 循环执行申请锁的指令, 直到锁被释放. 申请自旋锁的伪代码如下:_SMP_lock_spinlock_Obtain(lock){ do { 内存屏障; SMP_CPU_SWAP( lock, previous );内存屏障;} while (previous == 1);}其中, SMP_CPU_SWAP 等价下列汇编语言片段: lock;xchgl *address, Per_CPU_Control->lock; SMP_CPU_SWAP 暂时锁住总线保证操作的原子性, 并利用xchgl 指令一直读入lock 变量所在内存address 中的新值. 2.2.2 多核通信本系统中通过彼此发送核间中断来实现多核之间的通信. 进一步地, 通过给核间中断附加动作, 不同的CPU 可以在某种程度上彼此进行控制.与单核处理器不同, 多核处理器系统并不采用一个外部中断控制器, 而采用高级可编程中断控制器 APIC ( Advanced Programmable Interrupt Controller)[3]. 如图2, APIC 分为两个部分: I/O APIC 和本地APIC.图2 APIC① I/O APIC 接收由I/O 设备引起的中断, 利用中断重定向表, 查找中断的目的CPU, 将外部中断请求通过APIC 总线转发到目标CPU 的本地 APIC. ② 本地APIC 负责收集I/O APIC 转发的中断以及CPU 之间产生的核间中断, 再将其发送给 CPU 处理. 上述的核间中断只能够打断目的核的原执行序列, 并不能够让其了解具体的下一步工作. 需要设置核间通信消息, 用以给核间中断附加动作. 本系统为每个核配置一个消息池, 用来存放核间通信消息. 如图3所示, 发生核间通信时, 通信发起方往目标核的消息池中插入一条消息, 并向目标核发送核间中断. 收到中断的通信响应方暂停当前的执行序列, 进入中断处理程序, 中断处理程序通过中断向量号判断收到的中断为核间中断后, 调用核间中断处理程序. 核间中断服务例程读取本核消息池中的消息, 并根据消息的内容作出相应的工作. 特别地, 消息SMP_CONTEXT_SWITCH_NECESSARY 用来通知目的核执行重调度和任务切换.图3 多核通信流程3 调度策略的选取调度策略按照就绪队列的组织方式可以分为: “全局调度”和“局部调度”[4].全局调度是指系统中只存在唯一的就绪队列, 由所有CPU 核共同维护, 如图4. 调度时机产生时, 调度程序选择全局就绪队列中具有最高优先级的任务执行. 当系统规模很大时, 任务数的增多会使全局调度队列的开销急剧增大, 全局就绪队列容易成为瓶颈影响多核系统的并行性.图4 全局调度就绪队列组织方式局部调度是指为每个处理器核配置一个就绪队列. 任务按照一定的规则分配给处理器核后, 各核独立调度本地就绪队列中的任务, 如图5.图5 局部调度就绪队列组织方式局部调度可能会造成某些 CPU 忙, 而某些 CPU 却处于空闲状态[5,6]. 为了实现负载平衡, 系统需要每隔一段时隙, 检查所有就绪队列的负荷, 选择负荷最大的就绪队列, 将该队列上部分任务迁移到另一负荷值较小的就绪队列[7]. 负载平衡算法较为复杂, 时间复杂度与任务的个数相关, 预测性不强, 有不确定性.本系统采用分簇混合调度, 将系统中的所有可用核分组, 共享高速缓存的多个核作为一个簇集, 每个簇集内建立一个本地调度队列. 混合调度策在簇间独立调度, 类似与局部调度策略, 首先将任务静态的分配到各个处理器簇集. 然后各簇集各自调度本地队列中的就绪任务, 簇内各核统一调度. 在基于簇集的混合调度算法调度方案如图6所示.不同于局部调度算法, 混合调度算法中每个簇集包含有两个或两个以上的处理器核, 当任务分配算法将利用率很高的任务分配到一个处理器核后, 该处理器核剩余的处理能力可与同一簇集内的其他处理器核所剩余的处理能力合并, 因此, 混合调度算法中处理器核的处理能力可得到更充分的利用.图6 混合调度就绪队列组织方式不同于全局调度策略, 采用混合调度策略的系统中, 每个簇内都有一个调度队列, 当系统规模很大时,任务数的增多并不会使调度开销急剧增大. 另一方面,分簇混合调度策略仅允许任务在簇内迁移, 而不能够在簇间迁移, 因此在一定程度上减少了由于任务迁移引起的系统开销.4簇内全局调度采用分簇混合调度时, 将系统中共享高速缓存的多个核作为一个簇集, 可将存在数据依赖的任务分配到同一簇集, 以减少缓存失效率. 本系统由用户在调度程序运行前, 通过对簇集任务入口点main_entry的填写, 将任务静态的分配到各个簇集, 然后再簇内进行全局调度. 因此, 下文重点研究簇内的全局调度.4.1 调度算法根据任务对实时性的要求, 可以将任务分为普通任务和实时任务. 进一步的, 根据任务是否周期性释放, 可分为周期任务和非周期任务. 根据对任务的截止时限(Deadlines)要求, 可分为硬实时任务和软实时任务. 调度是目的是为了能够更好的使用处理器和分配资源, 需要针对操作系统所要执行任务的特点选择合适的调度方法.本系统将任务划分为普通任务和实时任务, 普通任务拥有普通优先级(高于RPRIO), 实时任务拥有实时优先级(低于RPRIO). 针对普通任务, 本系统提供基本的静态优先级调度算法, 基本思想为: 任务创建时按照用户指定的参数为每个任务赋予一个优先级,调度程序按照高优先级任务先调度, 不同优先级可抢占, 同优先级可轮转的调度策略进行任务的调度, 以确保系统内任何一个处理节点上运行的任务是处于就绪状态中优先级最高的那一个任务.针对周期任务, 系统提供了根据任务执行周期长短决定优先级的RM(Rate-Monotonic)调度算法[8], 周期越短优先级越高. 另一方面, 系统支持典型的动态优先级算法EDF(Earliest Deadline First)算法[9], 根据就绪队列中的各个任务根据它们的截止期限(Deadline)来分配优先级, 具有最近的截止期限的任务具有最高的优先级.为了同时支持上述不同调度算法, 本系统设计如图7所示的通用调度框架, 利用面向对象的思想, 以模块化的方式实现这些策略. 每个任务增设如下几项属性作为任务调度的依据:图7 调度框架① Priority: 任务的优先级② Finish-Time: 任务的结束时间③ Budget: 任务在运行期间所要使用的资源量④ Scheduler_info: 指明任务使用的调度策略每种调度策略都需要提供以下几种接口:① Scheduler_Assign: 初始化就绪队列.② Scheduler_Enqueue: 就绪队列插入就绪任务.③ Scheduler_Extract: 就绪队列剔除就绪任务.④ Scheduler_Yield: 进程主动放弃处理器控制权.⑤ Scheduler_Block: 任务阻塞.⑥ Scheduler_Unblock: 任务解除阻塞.⑦ Scheduler_Schedule: 激活调度.4.2 查找算法多核环境下, 查找算法的主要任务是: 从就绪队列队首开始遍历, 挑选出前N个(N 为可用核个数)没有分配处理器核并且优先级最高的任务[10]. 最高优先级查找算法应尽量选择 O(1)复杂度的算法[11]. 若簇内仅设置唯一的公共就绪队列, 那么将任务插入或者剔除就绪队列的操作, 都需要从前往后遍历整个就绪队列, 时间复杂度都为0(N)(N 为就绪任务个数). 为了满足大部分实时应用的的需求, 将簇内的全局队列划分为如图8所示的256个就绪队列. 任务按照自身优先级并结合FIFO 原则插入对应的队列. 此时, 插入和剔除任务的操作时间复杂度变为O(1).图8 多级就绪队列查找算法首先从队头往后遍历优先级最高的队列, 如果此队列中有未分配处理器核的任务, 则选择此任务为后备任务. 否则, 从下一优先级队列继续查找.另一方面, 加入位图, 使查找后备任务这个过程的效率更高. 本系统使用_Priority_Major_bit_map 与_Priority_Bit_map 数组一起表示含256个优先级的位图, 指明给定优先级列表上是否存在就绪任务, 如图9. _Priority_Major_bit_map 一共16bits, 其中每个bit 对应_Priority_Bit_map 数组中的一个元素. _Priority_Bit_map 数组一共有16个元素, 每个_Priority_Bit_map 元素对应16个优先级. 当有任务就绪, _Priority_Bit_map位图的相应位置1,_Priority_Bit_map 中16个优先级都为0时, _Priority_Major_bit_map 置0, 否则置1.图9 任务优先级位图此时, 查找系统中最高优先级的任务这一操作转化为了查找位图中被设置的第一个位. 因此, 查找最高优先级的N 个任务, 所需要的时间并不依赖于就绪任务的个数, 而是恒定的常数, 集杂度为O(1). 4.3 分配算法多核环境下, 分配算法的主要任务是根据系统中所有处理器核的负载情况, 以及任务优先级, 逐一地为查找算法提交的N 个就绪任务分配合适的处理器核资源, 新的就绪任务将成为被选中核上的后备任务(heir 任务, 下一次调度时机占有CPU 资源的任务), 等待该处理器产生调度时机调度执行.假设CPU 核A 从就绪队列中取出任务R, 分配算法思想如下:① 遍历所有可用CPU 核, 若有空闲核直接将空闲核的heir 任务指针修改为指向就绪任务R(原指向本核的idle 任务), 该空闲核将作为合适的处理器核资源分配给该就绪任务.② 若没有空闲的cpui. 比较各核上heir 进程, 选择优先级最低的任务所在的核作为备选核;ii. 若各核的优先相同, 选择已运行时间最长的任务所在的核作为备选核;iii. 若各核的已运行时间最长, 选择不可抢占的任务所在的核作为备选核;③ 找到合适的备选核后, 将该核的heir 任务指针指向就绪任务R;综合考虑任务优先级, 可抢占性, 已运行时间等因素, 选定某核分配给新的就绪任务后, 该任务将成为被选中核上的备选任务. 此时, 若更新后的heir 任务比该CPU 核正在执行的任务优先级更高, 且可抢占, 则设置该核的重调度标志位dispatch_necessary 为1, 表明本核需要重调度, 而内核会在接下来的适当时机完成该请求, 将正在执行的任务切换出去, 而执行新分配的任务. 分配算法流程图10如下: 4.4 调度时机 4.4.1 主调度机制在内核中许多地方, 需要将CPU 分配给与当前活动任务不同的另一个任务, 如: ①当前任务主动执行可能引起阻塞的操作, 例如, 磁盘I/O 操作或睡眠. 该任务转换为阻塞状态后, 调度程序将选择当前最高优先级的任务执行.②当前进程并没有执行任何可能引起阻塞的操作, 由于分配给该任务的时间片用完, 或是高优先级的任务等待的I/O 事件发生, I/O 中断唤醒了等待队列中的更高优先级任务. 此时, 当前任务将被迫让出CPU, 重新插入就绪队列. 在中断返回前夕, 由调度程序选择就绪队列中的更高优先级进程占有CPU.图10 分配算法流程本系统设计_Schedule_Schedule( )接口, 在上述情况下, 直接激活调度程序, 伪代码如下: _Schedule_Schedule( ){for(任务R=查找算法提交的第一个备选任务; 任务R=查找算法提交的第N+1个备选任务;任务R=查找算法提交的下一个备选任务){ if ( !分配算法( R ) )break;if ( ++已遍历的CPU 个数 >= 簇内可用核数)break;} }_Schedule_Schedule( )逐一地为查找算法提交的N 个就绪任务分配合适的处理器核资源, 直到某一次分配核资源失败, 说明此时系统中正在执行的任务已经是优先级最高的任务. 4.4.2 周期机制另一种通过周期机制激活调度程序. 本系统设计Schedule_Tick()接口以固定的频率(tick)激活调度程序, 该接口检查重调度标志位, 判断是否有必要进行进程切换. 为了实现Schedule_Tick()接口的固定频率tick, 将其内嵌在时钟中断服务例程clock_tick()中. Schedule_Tick()伪代码如下: _Scheduler_Tick {for ( cpu=0 ; cpu <可用的核数 ; cpu++ )_Scheduler_Tick_helper( cpu ); _Schedule_Schedule( ); }具体完成下面两个任务:① 利用_Scheduler_Tick_helper( )更新各核与调度相关的统计量, 如任务时间预算、已用时间等. ② 利用_Scheduler_Schedule, 检查重调度标志位, 如果重调度标志位为1, 重新选择需要激活的任务. 4.5 任务切换在分配算法中, 仅仅选择了合适的核分配给某一就绪任务, 改变了该核的重调度标志位. 如何让被选中的核感知自己被选中, 中断原执行序列, 真正切换到新的就绪任务是本节需要解决的问题.如上文所述, 本系统通过CPU 核彼此发送核间中断, 并且定义核间通信消息给核间中断附加动作, 来实现多核之间的控制.设计SMP_Request_other_cores_to_dispatch( )接口发送核间中断. 该接口遍历所有的核, 如果某核的重调度标志位为1, 将向选中的核发送核间通信消息CONTEXT_SWITCH_NECESSARY , 伪代码如下: SMP_Request_other_cores_to_dispatch( ){ for (i=1 ; i < 可用核数; i++ ) {if ( 本核的重调度标志位为零)continue; SMP_Send_message(i,CONTEXT_SWITCH_NECESSARY); } }其中, _SMP_Send_message()完成两个任务:①在目的CPU的消息池中填入核间通信消息, 消息内容为CONTEXT_SWITCH_NECESSARY .②向目的CPU发送一次核间中断.目的CPU接受到核间中断后, 进入中断处理程序, 根据中断向量号判断该中断为核间中断后, 调用核间中断服务例程, 该中断服务例程主要三个工作:①应答核间中断;②读取本核消息池中的消息;③根据消息的内容作出相应的工作.与CONTEXT_SWITCH_NECESSARY消息对应的工作即为任务切换. 具体地, 调用_Thread_Dispatch()更新相关任务的时间变量, 并调用_Context_Switch执行进程上下文切换, 它的工作是保存当前进程的上下文, 恢复新进程的上下文.综上, 多核环境下, 任务切换的具体过程如图11:图11 任务切换流程5实验本文使用QEMU模拟包含4个核的同构多核结构,QEMU是一款面向完整 PC 系统的开源仿真器. 首先设计功能性测试, 证明系统能够正确进行任务调度和任务切换, 验证了任务调度模块功能的正确性. 其次,设计可调度性测试, 对比全局调度和局部调度, 证明系统的可调度上限性能的提高.5.1 功能性测试簇间任务分配由用户在系统运行前通过对任务入口点main_entry的填写, 静态地将任务分配到各个簇.因此, 功能测试主要是对簇内4个同构核的全局调度,编写如下测试用例, 其中任务TA1代码段Test_task1( )填入簇集1的main_entry作为初始任务, 优先级为2.Test_task1( ){create_task( “TA2”,Test_task2, 1);//TA1创建任务TA2, 入口点为Test_task2, 优先级为1;while(1);}Test_task2( ){create_task( “TA3”,Test_tasks, 2);create_task( “TA4”,Test_tasks, 2);create_task( “TA5”,Test_tasks, 1);//TA2创建任务TA3、TA4、TA5, 代码入口点为Test_tasks, 优先级分别为都为2、2、1;create_task( “TA6”,Test_task6, 1);//创建任务TA6, 入口点为Test_task6, 优先级为1;while(1) ;}Test_tasks( ){while(1) ;}Test_task6( ){shut_down ( );}运行结果图如图12, 可以看出, 任务TA5被创建时, 各核正在执行的任务优先级最低的为核1上的TA1, 因此TA5抢占TA1的处理器资源执行. 任务TA6被创建时, TA3和TA4的优先级都为2, 但TA3的运行时间较长, 所以TA6选择抢占TA3的处理器执行.通过该实验, 证明了该系统在多核环境下, 以下内容成立:①所有核处于平等地位, 都能够执行调度程序;②调度程序能够综合考虑优先级、已运行时间以及任务的抢占性等因素, 分配合适的核给就绪任务;③执行调度程序的核能够正确的通知被选中核进行任务切换;④被选中的核能够中断原执行程序, 切换到新分配的就绪任务.5.2 可调度性测试可调度性测试使用QEMU模拟包含4个核的同构多核结构, 并将其平均分成两个簇集, 分别为Cluster1={CPU1, CPU2}和Cluster2={CPU3, CPU4}.给定如表1任务集待调度:表1 待调度任务集任务周期执行时间截止时间1 32 32 3 2 33 3 2 34 3 2 35 6 4 66 6 3 6将任务1、任务2、任务3的代码段写入Cluster1的任务入口点main_entry1, 表明任务1、任务2、任务3静态分配给簇集1. 同样地, 将任务4、任务5、任务6分配给簇集2. 另一方面, 考虑该任务集中中任务皆为具有截止时间的实时任务, 将所有任务的属性Scheduler_info指向EDF调度器类, 指明该任务集使用EDF最早截止时间调度策略.运行调度算法后, 该任务集一次调度的情况如图所示, 其中横坐标表示时间, 纵坐标表示CPU核资源.图13 混合调度运行结果可知, 混合调度算法可调度该任务集, 所有任务均在截止时限前完成. 另一方面, 修改配置, 将系统中的所有CPU核分配在同一簇中, 即Cluster1 ={CPU1, CPU2, CPU3, CPU4}, 并将所有任务的代码段写入簇集1的main_entry1, 以混合调度的这一特殊情况模拟全局调度. 再次运行调度算法, 该任务集的调度情况如图14所示:图14 全局调度运行结果可知, 任务5、任务6都错过了截止时限. 同样地,局部调度算法不能调度该任务集, EDF算法调度硬实时周期任务集是, 可调度的充分必要条件是任务集的总负载≥1. 每个核被分配一个任务后, 没有足够的容量容纳其他剩余的任务, 否则将使处理中容纳的任务其总利用率大于1, 超过处理器的处理能力.通过本实验可以看出, 混合调度算法在一定条件下, 综合了局部调度和全局调度算法的优点, 使得系统的可调度上限性能提高了.6总结本文基于同构多核处理器, 研究并实现了多核任务调度. 就绪队列方面, 采用分簇混合调度策略, 将共享数据缓存的多个核分为一个簇集, 簇间独立调度,簇内设置公共就绪队列实现簇内全局调度. 调度模式方面, 采用本系统采取分布式调度模式, 所有处理器对等运行调度程序, 并解决了分布式调度模式中存在通信和同步问题. 然后从调度算法、查找算法、分配算法等方面研究了簇内全局调度的实现. 最后通过模拟实验验证了调度模块功能的正确性、分析了调度算法的可调度性.参考文献1 Schaller RR. Moore’s law: Past, present and future. Spectrum,IEEE, 1997, 34(6): 52–59.2 何军,王飙.多核处理器的结构设计研究.计算机工程,2007,33(16):208–210.3 何翔,任晓瑞.支持多核的嵌入式操作系统关键技术研究.航空计算技术,2013,43(4):86–90.4 张惠娟,翟鸿鸣,周利华.多处理器系统的实时调度算法研究.计算机工程与设计,2004,25(8):1233–1235.5 Ding W, Guo R. An effective RM-based scheduling algorithm for fault-tolerant real-time systems. International Conference on Computational Science and Engineering(CSE’09). IEEE. 2009, 2. 759–764.6 Luo W, Qin X, Tan X C, Qin K. Exploiting redundancies to enhance schedulability in fault-tolerant and real-time distributed systems. IEEE Transactions on Systems, Man and Cybernetics, Part A: Systems and Humans, 2009, 39(3): 626–639.7 He Y, Liu J, Sun H. Scheduling functionally heterogeneous systems with utilization balancing. Parallel & Distributed Processing Symposium (IPDPS), 2011 IEEE International. IEEE. 2011. 1187–1198.8 叶明,罗克露,陈慧.单调比率(RM)调度算法及应用.计算机应用,2005,25(4):889–890.9 邢群科,郝红卫,温天江.两种经典实时调度算法的研究与实现.计算机工程与设计,2006,27(1):117–119.10 刘怀,胡继峰.实时系统的多任务调度.计算机工程,2002,28(3):43–44.11 李娟,任晓瑞,叶宏,时磊.一种基于实时性考虑的对称多处理机任务调度策略的设计.航空计算技术,2007,37(2): 49–52.。

基于龙芯开源CPU的计算机组成原理实验课程改革

图 3 单周期 CPU 的大致框图

学生的理论知识和实际动手能力有较高要求,且 程序调试较复杂。为此,在教学实践中,笔者将 该实验设置为可选,鼓励学有余力的学生完成。 2.8 静态五级流水 CPU 的实现

最后一个实验要求学生设计一个五级流水 CPU。该 CPU 的主体部分使用 2.7 节完成的多周 期 CPU,但此处要求将指令拓展到 40 条以上, 并 在 此 前 基 础 上 加 入 延 时 槽 技 术。 此 外, 该 实 验在每个模块中加入 allow_in 信号和 over 信号, 以此使该模块不断运作,从而实现流水线效果。 该实验使用了大量的控制信号来维持流水线的 秩序,要求学生对 CPU 功能结构有深入的了解, 并能把各模块联系起来,最后还要通过仿真器分 析设计结果,做出改进。在教学实践中,笔者将 该实验设置为可选,鼓励学有余力的学生完成。

计算机教育

156

Computer Education

2018

一系列教学改革尝试。在实验过程中,通过指导 学生动手实践,从零开始逐步完成一个可真实运 行的 CPU 核心,激发了学生的学习主动性,巩 固了学生的课堂知识,使学生对所学知识融会贯 通,取得了较好的教学成果。基于龙芯开源 CPU 的计算机组成原理实验平台已在南京邮电大学的 2014、2015 级计算机专业本科生中试用,在教 学过程中取得了较好的教学效果。 3.1 教改成效

此外,龙芯具有较好的社会影响力,配套培 训较多,学生学习热情高。例如,2017 年 6 月, 龙芯公司在南京航空航天大学进行了全国大学生 计算机系统能力培养大赛的相关培训 [8],在培训 过程中,龙芯开发人员介绍了龙芯开源 CPU 的 设计流程,对实验箱进行了演示,详细介绍了所 用的 MIPS 指令集,极大地提高了学生对于计算 机整体系统的认识。 3.2 存在的问题和思考

高性能计算机体系结构研究综述

高性能计算机体系结构研究综述引言随着计算机技术的不断发展,高性能计算机的应用范围越来越广泛。

高性能计算机是指能够提供高性能计算能力的计算机体系结构,主要用于进行复杂的科学计算、工程仿真等领域。

随着计算机应用场景的不断扩大,如何提高高性能计算机的计算能力和效率成为了计算机领域的核心问题。

本文综述了高性能计算机体系结构相关的研究进展和热点问题。

第一章高性能计算机体系结构概述高性能计算机体系结构是指计算机硬件系统的组成部分和相互连接方式。

高性能计算机与传统计算机系统的差别在于,高性能计算机使用了一种特殊的并行处理技术和高速通信技术。

高性能计算机主要由计算节点、存储节点、网络节点三个部分组成。

其中,计算节点用于执行计算任务,存储节点用于存储数据,网络节点用于实现节点之间的通信。

第二章并行计算体系结构并行计算体系结构是高性能计算机体系结构的重要组成部分,也是高性能计算机计算能力提高的核心。

并行计算体系结构主要有集中式共享存储架构、分布式存储架构、混合存储架构等。

其中,集中式共享存储架构具有计算能力强、资源利用率高等优点,是高性能计算机比较成熟的体系结构之一。

第三章高性能计算机并行计算模型高性能计算机并行计算模型是指对高性能计算机进行并行计算的理论模型和计算模型。

高性能计算机并行计算模型主要包括共享存储模型、分布式存储模型、混合存储模型等。

其中,共享存储模型是高性能计算机并行计算模型中的重要一种模型,具有良好的可扩展性和灵活性。

第四章高性能计算机芯片架构高性能计算机芯片架构是指高性能计算机中的处理器芯片架构。

高性能计算机芯片架构主要采用多核处理器的设计方式,如Intel的Xeon、AMD的Opteron、IBM的PowerPC等。

这些多核处理器的设计方式具有计算能力强、性能高等优点,可以提高高性能计算机的计算能力和效率。

第五章高性能计算机网络架构高性能计算机网络架构是指高性能计算机中节点之间的通信方式和通信协议。

多核CPU体系结构

1.3.2 片上多核处理器体系结构片上多核处理器(Chip Multi-Processor,CMP)就是将多个计算内核集成在一个处理器芯片中,从而提高计算能力。

按计算内核的对等与否,CMP可分为同构多核和异构多核。

计算内核相同,地位对等的称为同构多核,现在Intel和AMD主推的双核处理器,就是同构的双核处理器。

计算内核不同,地位不对等的称为异构多核,异构多核多采用“主处理核+协处理核”的设计,IBM、索尼和东芝等联手设计推出的Cell处理器正是这种异构架构的典范。

处理核本身的结构,关系到整个芯片的面积、功耗和性能。

怎样继承和发展传统处理器的成果,直接影响多核的性能和实现周期。

同时,根据Amdahl定理,程序的加速比受制于串行部分的比例和性能,所以,从理论上来看似乎异构微处理器的结构具有更好的性能。

CMP处理器的各CPU核心执行的程序之间需要进行数据的共享与同步,因此其硬件结构必须支持核间通信。

高效的通信机制是CMP处理器高性能的重要保障,目前比较主流的片上高效通信机制有两种,一种是基于总线共享的Cache结构,一种是基于片上的互连结构。

总线共享Cache结构是指每个CPU内核拥有共享的二级或三级Cache,用于保存比较常用的数据,并通过连接核心的总线进行通信。

这种系统的优点是结构简单,通信速度高,缺点是基于总线的结构可扩展性较差。

基于片上互连的结构是指每个CPU核心具有独立的处理单元和Cache,各个CPU核心通过交叉开关或片上网络等方式连接在一起。

各个CPU核心间通过消息通信。

这种结构的优点是可扩展性好,数据带宽有保证;缺点是硬件结构复杂,且软件改动较大。

如何有效地利用多核技术,对于多核平台上的应用程序员来说是个首要问题。

客户端应用程序开发者多年来一直停留在单线程世界,生产所谓的“顺序软件”,但是多核时代到来的结果是软件开发者必须找出新的开发软件的方法,选择程序执行模型。

程序执行模型的适用性决定多核处理器能否以最低的代价提供最高的性能。

基于多核处理器的高性能计算任务调度与优化策略研究

基于多核处理器的高性能计算任务调度与优化策略研究高性能计算(HPC)是一种能够处理大规模复杂问题的计算方式,它依赖于强大的计算能力和高效的任务调度策略。

随着科学技术的不断发展和计算机硬件的快速进步,多核处理器成为实现高性能计算的重要工具之一。

在多核处理器上进行任务调度和优化是提高计算性能的关键因素之一。

本文将依次介绍多核处理器、高性能计算任务调度和优化策略的研究现状,分析多核处理器上的任务调度问题,并提出一种基于多核处理器的高性能计算任务调度与优化策略。

首先,我们来了解多核处理器的概念。

多核处理器是指在一颗集成电路芯片上集成了多个处理器核心。

与传统单核处理器相比,多核处理器能够同时处理更多的任务,并提供更高的计算效率。

多核处理器的出现极大地推动了高性能计算的发展。

然而,多核处理器的任务调度和优化面临着很多挑战和难题。

高性能计算任务调度是指如何合理地将任务分配给不同的处理器核心,以最大化系统资源利用率,实现高性能计算效果。

目前已有许多任务调度算法被提出和研究,如FCFS(First-Come-First-Served)调度算法、SJF(Shortest-Job-First)调度算法、RR(Round-Robin)调度算法等。

然而,这些传统算法往往无法有效地适应多核处理器的特点,并且在面对大规模复杂任务时,性能表现不佳。

针对多核处理器上的高性能计算任务调度问题,研究人员提出了许多优化策略。

其中一种常用的策略是任务合并。

任务合并是指将多个任务合并为一个较为复杂的任务,然后再将这个较为复杂的任务分配给处理器核心。

通过任务合并,可以减少任务切换的开销,提高系统的计算效率。

此外,还有一些研究者提出了基于机器学习的任务调度优化策略。

这些策略通过分析任务的特性和处理器的性能,来预测任务的执行时间和资源需求,以优化任务调度效果。

除了任务调度优化策略外,还有一些其他的优化方法可以提高多核处理器上的高性能计算效果。

例如,任务划分和负载均衡。

基于多微处理器主从式核物位监测系统的研制

321 探 测器 ..

核仪表 按探 测器 的不 同 , 可分 为 闪烁 体 、盖 革计数

管 、电离 室等几 种 。在本 课题 中 , 过综 合 比较 , 经 探测 器 选用 了盖格计 数管 。优 点 : 成本 低 、温度影 响小 、外

围 电路 简单、工作可靠 。缺点 : 探测效率 低( 相对于 闪烁 体探测器 ) 。根据盖革计 数管的特点 , 计了如 图所示 的 设

和 自 动 控 制 技 术 的 研 究

( 接第 6 上 9页 )

0 毒

,

参考 文献 :

[]李 朝 晖 , 弘 . 字 图像 处 理 及 应 用 【 . 京 : 械 工 业 1 张 数 M】北 机 出 版 社 ,0 4 1-8 . 2 0 :0 0 []卢 结 成 , 龙 标 , 2 吴 宋卫 国 . 种 火 灾 图像 探 测系 统 的研 究 一

d为 介质 厚 度 ;

当盛 装 介质 的容器 内有 、 无 介质 时其 射 线 强度 将 分 别 为 I l I2 、 。根 据 公 式 则有 I l 10e一“ 、 =

I 2= 1 一 0 e

式 中 I 为 有介 质 时 的射 线强 度 ;I, 介 质 时射 无

作 者 简介: 林奇峰 ( 8 一 , 研 究生 , 究方向 : 1 5 ) 男, 9 研 虚拟仪 器

与硬件在 环仿真 。

T c n u so tmai & A pi t n 77 e h i e f o t n q Au o p l ai s I c o

图2

核物 位监 测 系统各 部分 外形 结构 图

线强度 , d, 0时的 射线 强度 。 即 =

由于 上述 公 式 中 e 0 因子的作 用 ,I, > I 的 > 将被 测 的两 种状态 下 的射线 强度进行 N  ̄ 比较 , I t J 即 可判 断介质 的 “ ”“ ” 空 满 。

计算机系统结构-量化研究方法(多处理器和线程级并行)

4.2 多处理器的Cache一致性

4.2.1 对称式共享存储器系统和多处理器的 Cache一致性 Cache一致性 4.2.2 分布式共享存储器系统和基于目录的 Cache一致性 Cache一致性

4.2.1 对称式共享存储器系统和多处理器的Cache一致性 对称式共享存储器系统和多处理器的Cache一致性

4.2.1.2 多处理器的Cache一致性 多处理器的Cache一致性 所谓多处理器的Cache一致性问题 所谓多处理器的Cache一致性问题,是指由 一致性问题, 于缓存共享数据, 于缓存共享数据,两个不同的处理器所保存 的存储器视图可能是通过各自的Cache 得到 的存储器视图可能是通过各自的 Cache得到 因此,如果没有其它的防范措施, 的。因此,如果没有其它的防范措施,则会 导致两个处理器分别得到两个不同的值。 导致两个处理器分别得到两个不同的值。 解决多处理器的Cache一致性问题的方法有 解决多处理器的Cache一致性问题的方法有 软件方法、总线监听法和目录表法。 软件方法、总线监听法和目录表法。

4.1.1 简介

2、多处理机结构由若干台独立的计算机组成, 每台计算机能够独立执行自己的程序,又称多 指令流多数据流(MIMD)结构。多处理机系统 中的处理机之间通过某种方式(如互连网络) 互连,从而实现程序之间的数据交换和同步。

4.1.1 简介

3、使用多处理机的主要目的是利用多台处理 机并发地执行一个作业,使得执行速度比 单处理机快;有时候,使用多处理机的主 要目的是提高可靠性而不是高性能,如果 某台处理机出现故障,那么它的程序可以 由系统中其它处理机来执行。

第 4 章 多 处 理 器 和 线 程 级 并 行

4.1

多处理器构成的系统结构

4.2

计算机体系结构的研究重点与发展方向分析

计算机体系结构的研究重点与发展方向分析【摘要】:本文首先简要说明了现代计算机的两种主要体系结构CISC 体系和RISC 体系,指出了基于冯·诺伊曼体系结构的现代计算机体系存在的问题及研究重点,并展望了未来计算机体系的发展方向。

【关键词】:体系结构;CIST 体系;RISC 体系一、引言计算机体系结构主要指计算机的系统化设计和构造,不同的计算机体系结构适用于不同的需求或应用。

现代计算机的两种主要体系结构是CISC 体系和RISC 体系。

其中RISC是近20 年的研究主流。

而随着计算机应用的普及,RISC 结构也出现了许多与以多媒体处理和个人移动计算机为主要内容的应用趋势的不协调。

为了消除这些不协调,未来计算机体系结构将会向什么方向发展呢?本文将对这些问题进行阐述和说明。

二、两种主要的计算机体系结构说明当今的计算机体系结构,从传统意义指令界面上来看基本划分成两大类:一类是CISC 体系结构,如INTEL 的X86芯片,另一类是RISC 体系结构,如SPARC、MIPS、POWERPC、等。

不管是CISC 体系结构还是RISC 体系结构,人们在计算机体系结构的设计上均追求两方面的目标:1.面向应用(软件)描述方面设计的计算机体系在面向应用(软件)描述方面使得自己的指令语义层次比较高,这点CISC 较为明显,因为它有许多指令可以直接支持高级语言的语义。

而RISC 则比较隐蔽,它是靠精简指令的优化编译(即通过若干条精简指令有机组合)来支持高级语言的语义。

2.面向应用处理方面设计的计算机体系在面向应用处理方面,使得自己的指令处理速度明显提高,进而加速应用处理的速度。

这点RISC表现的比较明显,因为它的指令硬件译码直接实现和采用流水线技术等大大提高了它的处理速度,而在CISC 中,当初增加硬件的资源支持复杂的高层次的语义的指令,本身就意味着提高应用的处理速度。

在过去的20 年里,RISC 技术不断发展,逐渐取代C1SC成为工作站和服务器的主流技术。

基于国产化CPU的操作系统设计与实现

基于国产化CPU的操作系统设计与实现随着国内半导体产业的快速发展和技术的日益成熟,越来越多的国产化CPU开始出现在市场上。

这为我们设计和实现基于国产化CPU的操作系统提供了非常好的机遇。

本文将探讨基于国产化CPU的操作系统设计与实现的相关内容。

一、国产化CPU的特点与需求国产化CPU通常具有自主研发的架构和技术,其设计与传统的国际厂商的CPU有所不同。

因此,在设计基于国产化CPU的操作系统时,我们需要考虑以下几个特点和需求。

首先,我们需要了解国产化CPU的架构和指令集。

这些信息可以从厂商提供的技术文档中获取。

我们需要知道CPU支持的指令集,内存管理机制,中断处理机制等,以便针对这些特点进行操作系统的设计。

其次,国产化CPU往往具有与国际厂商的CPU不同的性能和能耗特点。

我们需要对其进行性能分析和测试,了解其最大运算速度,能耗情况以及对外设的支持能力等。

这些信息对于我们为其设计优化的操作系统至关重要。

最后,我们还需要考虑国产化CPU的兼容性。

在国产化CPU的起步阶段,为了能够顺利过渡到国产化CPU,我们需要设计支持多种CPU架构的操作系统内核。

这样可以保证我们的操作系统可以运行在不同的CPU上,为用户提供灵活的选择。

二、操作系统内核的设计与实现基于国产化CPU的操作系统设计与实现,主要涉及操作系统内核的设计和实现。

下面将从内核的结构、任务调度、内存管理和设备驱动等方面进行详细介绍。

1. 内核结构操作系统内核是系统的核心,它负责管理系统资源,调度任务,提供接口供应用程序使用。

在设计基于国产化CPU的操作系统内核时,可以参考传统的内核结构,如微内核、宏内核等。

根据国产化CPU的特点,我们可以针对其架构进行合理设计和优化。

2. 任务调度任务调度是操作系统内核的重要功能之一。

在基于国产化CPU的操作系统中,任务调度需要考虑多个因素,如任务优先级、时间片大小、IO等待等。

根据国产化CPU的特点和性能需求,我们可以采用合适的调度算法,如优先级调度、轮转调度等。

高性能计算机体系结构研究

高性能计算机体系结构研究第一章引言高性能计算机体系结构是当代计算机科学研究的热点和重点之一,是计算机领域的核心技术之一。

在大规模科学计算,高速数据处理,人工智能等方面,高性能计算机的运算速度远超过传统计算机,并且可以处理更为复杂的问题。

因此,研究高性能计算机体系结构对于计算机技术的发展具有重要意义。

第二章高性能计算机体系结构的基本概念高性能计算机体系结构作为计算机科学中的一门学科,主要研究计算机硬件的设计与实现,涉及到计算机的CPU、内存、总线等硬件要素。

高性能计算机体系结构通常具备以下两个基本特征:1. 高并行性。

高性能计算机的针对于大规模的科学计算、图形处理、人工智能、大数据分析等计算密集型应用而设计,需要同时运行多个程序,因此,在硬件设计上注重高并行性和多线程处理。

2. 大规模的记忆容量。

高性能计算机通常需要处理更为复杂的问题,并且需要大规模的数据进行分析,因此需要更大的内存容量来存储数据。

第三章高性能计算机体系结构的种类目前高性能计算机体系结构根据不同的原则进行分类,常见的体系结构分类有以下几种:1. SIMD:单指令流多数据流。

这种体系结构的计算机通过使用单条指令处理多个数据项来实现高效并行处理。

通常用于对于相同类型的数据项进行处理,并且数据项的处理方式一样。

2. MIMD:多指令流多数据流。

每个CPU拥有独立的程序计数器和处理器状态等,使得多个计算机程序可以并行处理。

在图形处理以及科学计算等方面,常常使用MIMD的体系结构。

3. 多级体系结构。

这种体系结构一般包括多个不同的计算单元,每个计算单元可以单独运行程序。

其中一些计算单元可以处理数据,另外一些负责控制等操作。

第四章高性能计算机体系结构的实现高性能计算机体系结构的实现主要涉及到以下几个方面:1. 硬件设计:主要涉及到计算机的CPU、内存、总线等硬件要素。

在硬件设计上,通常优先考虑高并行性和多线程处理。

2. 并行编程技术:在高性能计算机中,并行编程技术是必不可少的一部分。

CPU国产化及生态深度研究

CPU国产化及生态深度研究目前几乎所有冯·诺伊曼型计算机的CPU的工作流程可以分为:提取指令、指令编译、指令执行、访问主存并读取操作数、写回等五个阶段。

CPU的几大主要结构在过程中的作用如下:控制单元(Control Unit)作为CPU的控制中心,负责将存储器中的数据发送至运算单元并将运算后的结果存回到存储器中,其一切行为均来自于指令。

运算单元(Arithmetic/Logic Unit)可以执行算术运算和逻辑运算。

它执行来自于控制单元的命令。

存储单元(Registers、Cache)是CPU 中数据暂时存储的位置,其中寄存有待处理或者处理完的数据。

寄存器(Registers)较内存相比,可以减少CPU访问数据的时间,也可以减少CPU访问内存的次数,有助于提高CPU的工作速度。

目前CPU架构主要分为CISC(复杂指令集)和 RISC(精简指令集)。

1971年美国英特尔公司推出世界第一款商用计算机微处理器Intel 4004,被认为是CPU发展史的开端。

作为4位处理器,Intel 4004由10um制程工艺在2英寸晶圆上打造,集成了2300个晶体管,主频为740kHz。

到了2020年,第十一代酷睿处理器芯片基于英特尔10nm工艺打造,将集成超过百亿个晶体管,最高主频可高达4.8Ghz。

这颗CPU芯片不再是单一的CPU,而是集成了全新架构的Willow Cove内核、Iris X图形处理器、内存控制器、图像处理器、媒体解码器、电源管理、神经元加速器和各类高速接口控制器等各种组件。

其中Willow Cove内核正是这颗CPU芯片集成的传统意义上的CPU。

CPU的发展史,按照其处理信息的字长,可以分为:四位微处理器、八位微处理器、十六位微处理器、三十二位微处理器以及六十四位微处理器等等。

英特尔X86指令集中的单指令多数据流指令集可以划分为MMX、SSE、AVX。

英特尔的指令集采用叠加的方式向前发展,从奔腾的MMX 到Skylake的AVX512,指令集的位数从64位升级至了512位。

并行计算中的多核CPU架构研究

并行计算中的多核CPU架构研究第一章: 引言近年来,信息技术的飞速发展,推动了高性能计算的发展。

多核CPU是高性能计算领域中的一个重要组成部分,其并行计算的能力成为计算速度提升的重要手段。

多核CPU架构研究就成为高性能计算领域中的一个热点研究方向。

本文旨在对多核CPU架构进行深入探讨和研究,掌握多核CPU的构成和工作原理,提升高性能计算领域的研究和应用水平。

第二章:多核CPU架构概述2.1多核CPU定义多核处理器,或称为多核中央处理器,是包含两个或者更多核心(即计算单元)的中央处理器。

多核处理器被设计成在计算机系统上有一个或更多的物理核心,例如在单个晶片上。

多核处理器最主要的设计目标是提高计算性能和吞吐量。

2.2多核CPU的分类多核处理器可以根据其不同的架构方式进行分类,目前主要包括对称多处理(SMP)、非对称多处理(ASMP)、网络处理器(NP)、多线程处理器等。

其中,对称多处理是应用比较广泛的多核处理器架构,未来趋势是采用非对称多处理。

2.3多核CPU的优点相对于单核处理器,多核CPU的优点如下:(1) 更高的处理性能和吞吐量:多核CPU有多个核心可以并行处理任务,加快数据计算和处理的速度。

(2) 更好的能耗控制:可以通过关闭不必要的核心或电压/频率调整等方案调整功率,实现更优的能源管理方式。

(3) 更低的成本:因为整个系统只需要一个管脚,可以减少必须的硬件芯片数量,从而降低整个系统的生产成本。

第三章:多核CPU架构实现和运作原理3.1多核CPU架构多核CPU由多个core组成,每个core都可以执行独立的计算任务。

多核CPU可以采用不同的架构,常见的有对称多处理(SMP)和非对称多处理(ASMP)。

(1) 对称多处理(SMP)对称多处理是一种多核CPU的通用架构,所有的核心都具有相同的功能,并且共享主存储器。

SMP的每个核心执行的任务必须通过主存储器来共享,这使得SMP在处理共享内存多任务时具有较好的性能优势,但同时也需要考虑不同核心之间的同步和数据一致性问题。

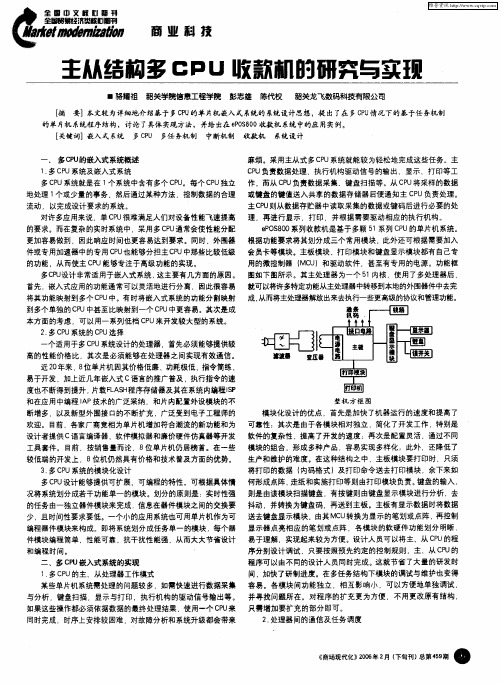

主从结构多CPU收款机的研究与实现

首先 . 嵌入式应用的功能通常可以灵活地进行分离 .因此很容易 就可以将许多特定功能从主处理器中转移到本地的外围器件中去完 从而将主处理器解放出来去执行一些更高级的协议和管理功能。 将其功能映射到多个CU中。 P 有时将嵌入式系统的功能分割映射 成. 到 多个单独 的C U P 中甚 至比映射到一个 CU中更容易。其次是成 P 本方面的考虑 ,可以用一 系列低档 C U来开发较大型的系统 。 P

U转换为显示的笔划或点 阵 , 再控制 少, 且时间性要求要低 一个小的应用系统也可用单片机作为可 送去键盘显示模块 .由其 MC 编程器件模块来构成。即将系统划分成任务单一的模块, 每个器 显示器点亮相应的笔划或点阵 .各模块 的软硬 件功能划分 明晰 . 易于理解 ,实现起 来较 为方便 。设计人员可以将主 从 C U的程 P 件模块编程简单 . 性能可靠 . 抗干扰性能强 .从而 大大节省设计 和编程 时间。 序分 别设计调试 .只要 按照预 先约定 的控制规则 .主 从 C U的 P 程序可 以由不 同的设计人员同时完成 。这就节省 了大量的研发时

件或专用加速器 中的专用 C U也能够分担 主C U中那些比较低级 会 员卡等模块 主板模块 打 印模块和键盘显示模 块都有 自己专 P P 的功能 .从而使 主 C U能够专注于高级功能的实现 P 用的微控制器 ( U)和驱动软件 ,甚至有专用 的电源。功能框 MC 1 多C U P 设计非常适用于嵌入式 系统 , 这主要有几方面的原 因。 图如下 图所示。其 主处理器 为一个 5 内核 ,使用 了多处理器后 ,

流动 以完成设计 要求的系统 。

主C U P 则从数据存贮器 中读取采集 的数据或键码后进行必要的处

对许多应 用来说 ,单 CU P 很难满足人们对设备性能飞速提 高 理 ,再进 行显 示,打 印 并根据需要驱动相应 的执行机构 的要求。而在复杂的实时系统中 采用多 C U P 通常会使性能分配 eO 80 P S0 系列收款机是基于多颗 5 系列C U 1 P 的单片机系统。 更加容易做到 ,因此响应 时间也更容易达 到要 求。同时 ,外围器 根据功能要求将其划分成三个常用模块 .此外还可根据需 要加入

高性能计算硬件架构设计与优化技术研究综述

高性能计算硬件架构设计与优化技术研究综述在计算机科学领域,高性能计算是指通过使用特殊硬件和软件技术来实现超过传统计算机能力的计算任务。

在现代科学、工程和商业应用中,高性能计算已成为一项关键技术。

为了实现高性能计算,硬件架构设计和优化技术起到了关键作用。

本文将对高性能计算的硬件架构设计和优化技术进行综述。

首先,高性能计算的硬件架构设计需要考虑计算机的处理器、存储器和网络互连等方面。

处理器是计算机的核心,其设计和优化对于高性能计算至关重要。

常见的高性能计算处理器包括多核处理器和向量处理器。

多核处理器能够同时执行多个线程,提高计算速度。

向量处理器则能够并行处理同一指令下的多个数据,提高向量计算的速度。

此外,存储器的设计和优化也对高性能计算起到至关重要的作用。

高性能计算通常需要大容量的存储器来存储大规模的数据和计算结果。

因此,设计高效的存储层次结构和具有高带宽的存储器是重要的硬件架构优化技术。

此外,高性能计算还需要高速的网络互连来实现不同节点之间的通信和数据传输。

因此,网络拓扑的设计和优化也是高性能计算硬件架构设计的重要内容之一。

其次,高性能计算的硬件架构设计和优化还需要考虑功耗和散热问题。

随着处理器性能的提高,功耗和散热问题变得越来越突出。

在高性能计算中,处理器和其他组件之间的能量消耗需要得到合理的分配和管理,以保证计算机的稳定工作。

因此,设计低功耗的硬件架构和有效的散热措施成为硬件架构设计和优化的重要方向之一。

例如,通过优化处理器的电源管理技术和采用高效的散热技术,可以有效降低计算机的功耗和温度。

另外,高性能计算的硬件架构设计和优化还需要考虑并行计算和加速器技术。

并行计算是高性能计算的核心概念之一,它通过同时执行多个计算任务来提高计算速度。

硬件架构设计和优化需要考虑如何实现有效的并行计算,包括多核处理器的设计和优化、多节点系统的设计和优化以及任务调度和负载均衡等技术。

此外,加速器技术也成为高性能计算的重要组成部分。

基于国产CPU/OS的办公信息系统研究与设计

基于国产CPU/OS的办公信息系统研究与设计张忠革;郑年斌;周泽峰;彭革刚;沈清;石猛【摘要】Along with the development of enterprise information construction, in many government departments office automation system have been successfully implemented but most of these systems use foreign hardware and software equipment, this reduces information system security and cannot meet the safety requirements for government office system. The paper presents the design and implementation method for office information system based on domestic software and hardware, and introduces the architecture, design and implementation method for the office information system. The actual operation situation shows that the system can improve current office information system and meet the requirements for e-government application security, integration and localization services.%随着我国企业信息化建设的深入,办公自动化系统在许多政府部门都已经成功实施,但大部分采用国外的软硬件设备,降低了信息系统整体安全性,难以满足政府办公的信息安全要求。

基于多CPU控制系统的设计与实现

基于多CPU控制系统的设计与实现

叶青;方文森;谌勇

【期刊名称】《工业控制计算机》

【年(卷),期】2007(20)12

【摘要】设计了一个由双单片机、一个ARM7构成的三CPU系统,该系统不仅能够向上位机传送生产数据,同时也能够判断出主单片机的运行情况,一旦主单片机发生故障,系统将自动切换到备份机运行;提出了一个识别主机状态的算法,算法的处理速度为35ms/帧.

【总页数】2页(P9-10)

【作者】叶青;方文森;谌勇

【作者单位】昆明理工大学信息工程与自动化学院,云南,昆明,650051;昆明理工大学信息工程与自动化学院,云南,昆明,650051;昆明理工大学信息工程与自动化学院,云南,昆明,650051

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于VxWorks的多CPU高性能控制系统 [J], 肖铁妹;朱春毅;李崇坚

2.基于RS-485总线多CPU控制系统简化网络模型及其通讯协议 [J], 刘俊伟

3.基于多CPU控制平台的提花袜机控制系统设计 [J], 乔桥

4.基于多CPU的油井作业监测系统的设计与实现 [J], 李萍

5.基于RS-485总线多CPU控制系统简化网络模型及其通讯协议 [J], 刘俊伟

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

各模块间功能独立, 相互影响小, 可以方便地单独调

试, 并寻找问题所在。对程序的扩充更为方便, 不用更

改原有结构, 只需增加要扩充的部分即可。

2.2 处理器间的通信及任务调度

在只有一个 CPU 的情况下, 传统的单片机系统监

控程序通常是基于单任务机制的。这种机制具有简单

直观, 易于控制的优点。然而由于程序只能按单一的

技

术 图 1 整机方框图

创

模块化设计的优点, 首先是加快了机器运行的速

度和提高了可靠性; ቤተ መጻሕፍቲ ባይዱ次是由于各模块相对独立, 简

新 化了开发工作, 特别是软件的复杂性, 提高了开发的

速度; 再是配置灵活, 通过不同模块的组合, 形成多种

产品, 容易实现多样化; 此外, 还降低了生产和维护的

难度。在这种结构之中, 主板模块要打印时, 只须将打

片 机 系 统 程 序 结 构 ,讨 论 了 具 体 实 现 方 法 , 并 给 出 在 ePOS800 收 款 机 系 统 中 的 应 用 实 例 。

关键词:嵌入式系统;多 CPU;多任务机制;中断机制;收款机;系统设计

中 图 分 类 号 : T P 368.1

文献标识码:B

Abstr act:This text introduce in detail comparatively, Have put forward the systematic procedure structure based on task mechanism

- 14 - 360元 / 年 邮局订阅号: 82-946

《 现场总线技术应用 200 例》

您的论文得到两院院士关注

嵌入式系统应用

4. 模块的睡眠—唤醒技术 在主/从式的多 CPU 系统中, 有些从属模块可 能 在较长时间内没有工作, 此时可使该模块休眠, 待需 要时再唤醒。除了可减低功耗之外, 从属模块的休眠 也可大大减低电磁辐射。 2.3 模块之间的数据传输 多 CPU 系统中一个非常重要的问题, 是如何解决 好各 CPU 之间数据的合理流动问题。在多 CPU 设计 中, 处理器之间必须能够相互通信, 以便控制对共享 资源的访问。同时也出现了一个怎样实现各器件模块间 交换信息的问题。文献中给出了数据交换的一些方式。 ePOS800 系列收款机的模块化结构要求主模块与 其它从属模块之间能保证正常的数据传输。如采用并行 总线方式的数据传输设计, 虽然可获得较高的传输速 度, 但是需要使用大量的接口电路和连接电缆, 增加设 计成本, 可靠性也很难保证。所以在 ePOS800 系列收款 机中, 各模块之间的数据传输大量采用了串行总线数据 传输方式, 使电路得到简化, 连接更简洁, 系统的稳定性 和抗干扰能力得到提高, 同时也相应减低成本。 2.4 关键部分的选择 为 解 决 串 行 总 线 数 据 传 输 速 度 的 问 题 , ePOS800 系 统 使 用 了 具 备 SPI 串 行 接 口 的 CPU 来 完 成 主 板 与 打 印 、显 示 模 块 之 间 的 数 据 交 换 。 EPOS800 系 统 具 有 5 个 串 口 和 1 个 并 口 的 外 部 接口。为保证能较好的控制设计成本, 仅用了一片 16C552 作为扩展接口, 其余则有效的利用了系统内多 CPU 的优点, 充分的利用了各 CPU 的串口资源。 为解决二类收 款机的显示 和汉字输入 的问题, e- POS800 采 用 了 15 行 *40 列 的 点 阵 图 形 液 晶 显 示 模 块, 采 用 全 拼 汉 字 输 入 , 并 可 外 接 PC 键 盘 , 这 样 用 户 可以象操作 PC 机一样使用 ePOS800。 ePOS800 系列收款机在设计时, 充分考虑到了用 户在使用过程中的操作简便性, 设计了非常友好的人 机界面和全中文化菜单。通过完善的软件设计, 可支 持多种销售模式, 菜单导航, 操作方便简单。为了让用 户能更好地进 行二次开发 , ePOS800 系 列 收 款 机 为 用 户设计了完善的底层 WINDOWS 接口库, 用 户可以自 行设计自己的后台软件和管理系统。

键 码 后 进 行 必 要 的 处 理 , 再 进 行 显 示 、打 印 , 并 根 据 需要驱动相应的执行机构。

ePOS800 系列收款机是基于多颗 51 系列 CPU 的 单片机系统。根据功能要求将其划分成三个常用模 块, 此外还可根据需要加入会员卡等模块。主板模块、 打印模块和键盘显示模块都有自己专用的微控制器 ( MCU) 和驱动软件, 甚至有专用的电源。功 能框图如 图 1 所示。其主处理器为一个 51 内核, 使用了多处理 器后, 就可以将许多特定功能从主处理器中转移到本 地的外围器件中去完成, 从而将主处理器解放出来去 执行一些更高级的协议和管理功能。

(1. 韶关学院;2.韶关龙飞数码科技有限公司)骆 耀 祖 1 李 强 1 陈 代 权 2 彭 志 雄 2

LUO YAOZU LI QIANG CHEN DAIQUAN P ENG ZHIXONG

摘要: 本 文 较 为 详 细 地 介 绍 基 于 多 CPU 的 单 片 机 嵌 入 式 系 统 的 系 统 设 计 思 想 , 提 出 了 在 多 CPU 情 况 下 的 基 于 任 务 机 制 的 单

不断增多, 以及新型外围接口的不断扩充, 广泛受到

术 电子工程师 的欢迎。目前 , 各家厂商竞 相为单片机 增 创 加 符 合 潮 流 的 新 功 能 和 为 设 计 者 提 供 C 语 言 编 译

器 、软 件 模 拟 器 和 廉 价 硬 件 仿 真 器 等 开 发 工 具 套 件 。

新 目 前 , 按 销 售 量 而 论 , 8 位 单 片 机 仍 居 榜 首 。 在 一 些

under multi- CPU embedded system, Having discussed the concrete implementation method, and the application instance of giving ap-

pearing in ePOS 800 cash register system.

您的论文得到两院院士关注 文章编号:1008- 0570(2006)11- 2- 0013- 03

嵌入式系统应用

基于主/从结构的多 CPU 系统的研究与实现

Im p le m e n ta tio n o f m a in /s la ve s tru ctu re a n d m u tli- CPU e m b e d d e d s ys te m

多任务机制是现代操作系统才具有的突出优点。 在这种机制下, CPU 的运行时间被划分为许多小的时 间片, 由某种调度( Scheduling) 算法按不同优先级别分 配给不同的进程。

主系统必须担负起调度进程的责任, 不断地切换 进程, 以提高系统的效率。

1. 轮询方式 单片机完成的系统功能往往可以分解为若干相 对独立的模块, 可以将这些模块理解为子任务, 并引 进多任务机制进行管理, 从而形成多 CPU 的功能模块 结构和一种崭新的程序结构。在这种结构下, 执行顺 序也比较灵活, 且可在程序运行过程中动态地改变执 行结构。 各子任务的执行频率要求表现为它们的优先 级, 优先级越高的子任务单位时间内执行次数越多, 从而其执行频率越高。通过合理设计时间片大小和 各任务的优先级, 可以自然地满足系统内各种复杂 的定时要求。 2. 中断方式 在单片机系统中引入多任务机制, 可以有效改善 程序结构, 满足复杂系统的要求。任何多任务本质上 都借助于中断机制。通用单片机中都允许使用中断, 从而保证了在单片机系统中实现多任务的切实可行。 3.抢 占 式 调 度 策 略 在单 CPU 的情况下, 通常对具有某种紧迫性的实 时进程采用 FIFO 的调度方式, 即排在运行队列前 面 的进程先 运行, 直到它主 动放弃 CPU 后 , 才 能 轮 到 下 一个进程运行。 如果进程执行的任务比较短小, 这种算法勉强还 能满足实时的需要, 若是任务比较大, 就会出现某些 紧急的任务因为当前进程没有执行完毕而无法获得 CPU, 导致任务被迫等待而无法满足实时要求。对于这 种情况, 可采用抢占式的优先权算法, 当没有中断发 生时, 调度器根据就绪任务的优先级来决定任务的运 行次序。事实证明, 抢占式的优先权调度算法是很有 效率的。

能够提供较高的性能价格比, 其次是必须能够在处理 机构的驱动信号输出等。如果这些操作都必须依据

器之间实现有效通信。

数 据 的 最 终 处 理 结 果 , 使 用 一 个 CPU 来 同 时 完 成 ,

近 20 年来, 8 位单片机因其价格低廉、功耗极低、 时 序 上 安 排 较 困 难 , 对 故 障 分 析 和 系 统 升 级 都 会 带

Key wor ds:Embedded system,Multi- CPU,Multi- task mechanisms,inter r upt mechanism,cash r egister ,system design

技

1 多 CPU 的嵌入式系统概述

1.1 多 CPU 系统及嵌入式系统 多 CPU 系统就是在 1 个系统中含有多个 CPU。每 个 CPU 独立地处理 1 个或少量的事务, 然后通过某种 方法, 控制数据的合理流动, 以完成设计要求的系统。 对许多应用来说, 单 CPU 很难满足人们对设备性 能飞速提高的要求。而在复杂的实时系统中, 采用多 CPU 通常会使性能分配更加容易做到, 因此响应时间 也更容易达到要求。同时, 外围器件或专用加速器中 的专用 CPU 也能够分担主 CPU 中那些比较低级的功 能, 从而使主 CPU 能够专注于高级功能的实现。 多 CPU 设 计 非 常 适 用 于 嵌 入 式 系 统 , 这 主 要 有 几 方 面 的 原 因 。首 先 , 嵌 入 式 应 用 的 功 能 通 常 可 以 灵 活地进行分离, 因此很容易将其功能映射到多个 CPU 中 。 有 时 将 嵌 入 式 系 统 的 功 能 分 割 映 射 到 多 个 单 独 的 CPU 中 甚 至 比 映 射 到 一 个 CPU 中 更 容 易 。其 次 是 成 本 方 面 的 考 虑 , 可 以 用 一 系 列 低 档 CPU 来 开