USB 协会标准

USB3.0协会标准

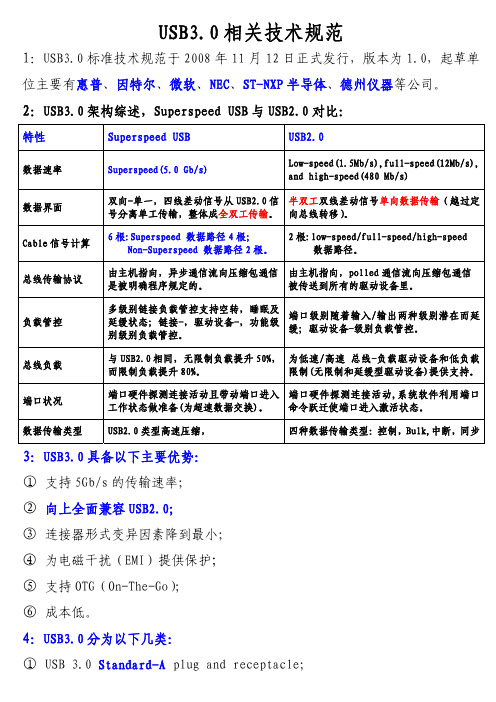

USB3.0相关技术规范1:USB3.0标准技术规范于2008年11月12日正式发行,版本为1.0,起草单位主要有惠普、因特尔、微软、NEC、ST-NXP半导体、德州仪器等公司。

2:USB3.0架构综述,Superspeed USB与USB2.0对比:特性 Superspeed USB USB2.0数据速率 Superspeed(5.0 Gb/s) Low-speed(1.5Mb/s),full-speed(12Mb/s), and high-speed(480 Mb/s)数据界面 双向-单一,四线差动信号从USB2.0信号分离单工传输,整体成全双工传输。

半双工双线差动信号单向数据传输(越过定向总线转移)。

Cable信号计算 6根:Superspeed 数据路径4根;Non-Superspeed 数据路径2根。

2根:low-speed/full-speed/high-speed数据路径。

总线传输协议 由主机指向,异步通信流向压缩包通信是被明确程序规定的。

由主机指向,polled通信流向压缩包通信被传送到所有的驱动设备里。

负载管控 多级别链接负载管控支持空转,睡眠及延缓状态;链接-,驱动设备-,功能级别级别负载管控。

端口级别随着输入/输出两种级别潜在而延缓;驱动设备-级别负载管控。

总线负载 与USB2.0相同,无限制负载提升50%,而限制负载提升80%。

为低速/高速 总线-负载驱动设备和低负载限制(无限制和延缓型驱动设备)提供支持。

端口状况 端口硬件探测连接活动且带动端口进入工作状态做准备(为超速数据交换)。

端口硬件探测连接活动,系统软件利用端口命令跃迁使端口进入激活状态。

数据传输类型 USB2.0类型高速压缩, 四种数据传输类型:控制,Bulk,中断,同步3:USB3.0具备以下主要优势:① 支持5Gb/s的传输速率;② 向上全面兼容USB2.0;③ 连接器形式变异因素降到最小;④ 为电磁干扰(EMI)提供保护;⑤ 支持OTG(On-The-Go);⑥ 成本低。

USB3.0协会标准

USB3.0相关技术规范1:USB3.0标准技术规范于2008年11月12日正式发行,版本为1.0,起草单位主要有惠普、因特尔、微软、NEC、ST-NXP半导体、德州仪器等公司。

2:USB3.0架构综述,Superspeed USB与USB2.0对比:特性 Superspeed USB USB2.0数据速率 Superspeed(5.0 Gb/s) Low-speed(1.5Mb/s),full-speed(12Mb/s), and high-speed(480 Mb/s)数据界面 双向-单一,四线差动信号从USB2.0信号分离单工传输,整体成全双工传输。

半双工双线差动信号单向数据传输(越过定向总线转移)。

Cable信号计算 6根:Superspeed 数据路径4根;Non-Superspeed 数据路径2根。

2根:low-speed/full-speed/high-speed数据路径。

总线传输协议 由主机指向,异步通信流向压缩包通信是被明确程序规定的。

由主机指向,polled通信流向压缩包通信被传送到所有的驱动设备里。

负载管控 多级别链接负载管控支持空转,睡眠及延缓状态;链接-,驱动设备-,功能级别级别负载管控。

端口级别随着输入/输出两种级别潜在而延缓;驱动设备-级别负载管控。

总线负载 与USB2.0相同,无限制负载提升50%,而限制负载提升80%。

为低速/高速 总线-负载驱动设备和低负载限制(无限制和延缓型驱动设备)提供支持。

端口状况 端口硬件探测连接活动且带动端口进入工作状态做准备(为超速数据交换)。

端口硬件探测连接活动,系统软件利用端口命令跃迁使端口进入激活状态。

数据传输类型 USB2.0类型高速压缩, 四种数据传输类型:控制,Bulk,中断,同步3:USB3.0具备以下主要优势:① 支持5Gb/s的传输速率;② 向上全面兼容USB2.0;③ 连接器形式变异因素降到最小;④ 为电磁干扰(EMI)提供保护;⑤ 支持OTG(On-The-Go);⑥ 成本低。

聊聊TYPEC数据线的铜丝规格怎么选择

聊聊TYPEC数据线的铜丝规格怎么选择⾃从TYPE C数据线开始跑3A,5A电流以后,铜丝规格如何选择来满⾜电流和功率的问题就开始经常有⼈问到,今天我们就⼀起聊聊TYPE C数据线的铜丝规格怎么选择,USB数据线,最基本的电器参数就是电阻,压降,电压等,其实被客⼈问最多的当然就是对应数据线可以承受多少的电流,⽤多⼤的导体⽐较划算,今天我们就⼀起聊聊。

在TYPE C数据线的数据线⾥⾯,涉及到电流传输的PIN⾓定义为VBUS和GND,我们再⼀起回顾下USB Type-C脚位说明,然后再回到这个主题以上信号按照功能主要可以分为5类:第⼀类:Power有关的信号,包括a)VBUS,USB线缆的bus power(和我们通常意义上VBUS保持⼀致)。

b)VCONN(只有在插头上才会有该信号),⽤于向插头供电(由此可以推测出有些插头中可能会有电路)。

c)GND,接地第⼆类:USB 2.0数据线,D+/D-,它们在插头端只有⼀对,和旧的USB 2.0规范⼀致。

但为了⽀持正反随意插。

在插座端定义了两组,这样插座端可以根据实际情况进⾏合适的mapping。

第三类:USB3.1数据线,TX+/-和RX+/-,⽤于⾼速的数据传输。

插头和插座端都有两组,⽤于⽀持正反随意插。

第四类:⽤于Configuration的信号,对插头来说,只有⼀个CC,对插座来说,有两个CC1和CC2。

第五类:扩展功能所需的信号,具体使⽤场景由相应的扩展功能决定。

⼀个电源的电压经过⼀段线路或其他部件的传送电压有⼀部分就会被消耗从⽽降低,这降低的部分就是这段线路的电压降,测量电源起点处的电压与终点处的电压,两者之差就是电压降.举个简单的例⼦,例如变电站的输出电压是220V,⽽你家的电压是215V,那么从变电站到你家的这段电路的电压降就是220V-215V=5V.电压降应该这样解释:电线本⾝存在电阻,当电流沿导线流动时,必须施加⼀个电压来克服这个电阻,否则电流就不能通过;在同样⼀根电线上,通过的电流越⼤,需要来克服这个电阻的电压就越⾼(V=I*R),克服这个电阻的电压对于供电电源来说,就是造成了“电压降”(送过去的电压降低了),⽤电量越⼤(I 加⼤)电压降也就越⼤,导线电阻率越⼤、导线截⾯积越⼩、导线越长(R 加⼤)电压降也越⼤.从以上可以看出,衡量电压降⽐单纯的电流靠谱稳定和更加全⾯。

USB接口类移动电源行业标准

中国化学与物理电源行业协会标准China Industrial Association of Power SourcesCIAPS0001-2014CD稿USB接口类移动电源Power bank with USB ports2014-05-01发布2014-05-01实施中国化学与物理电源行业协会发布CIAPS0001-2014CD稿目录前言 (3)1范围 (4)2规范性引用文件 (4)3定义 (4)4要求 (5)5试验方法 (8)6型式检验 (12)7标志、包装、运输和贮存 (13)8附录A (15)CIAPS0001-2014CD稿前言本标准参考GB/T18287-2013《移动电话用锂离子蓄电池及蓄电池组总规范》编制部分条款,在技术内容中融合了UL2054《家用或商用蓄电池组》的有关要求,能够指导、约束移动电源厂商在设计、生产、销售各阶段的行为;同时本标准能够满足移动电源的技术性能和环境使用的要求,将更好的促进移动电源行业的发展。

本标准由中国化学与物理电源行业协会提出本标准由中国化学与物理电源行业协会归口本标准由欣旺达电子股份有限公司组织起草本标准由标准编写工作组共同完成。

工作组组长单位:欣旺达电子股份有限公司;副组长单位:广东品胜电子股份有限公司、深圳市万拓电子技术有限公司、深圳市创明电池技术有限公司、宁波维科电池股份有限公司、深圳市电母科技有限公司;成员单位:惠州市德赛电池有限公司、惠州市豪鹏科技有限公司、深圳市倍斯特电源有限公司、四川长虹新能源科技有限公司、惠州市瑞能德电子有限公司、东莞市鼎酷科技有限公司、浙江超威创元实业有限公司、浙江天能能源科技有限公司、群赞科技(深圳)有限公司、深圳先进储能材料国家工程中心有限公司、钰泰科技(上海)有限公司本标准首次发布日期:2014年05月01日本标准主要起草人:许辉勇关世强杨贺钦唐高文赵国成孙中伟罗莺曹长河USB接口类移动电源1范围本标准规定了USB接口类移动电源(以下简称为移动电源)的定义、要求、试验方法及标志、包装、运输和贮存。

usb,type,c,协会规范

竭诚为您提供优质文档/双击可除usb,type,c,协会规范篇一:usb3.1type-c公对公接点图usb3.1(type-c)接点图usb3.1type-c公对公接点图pin的四种类型:1、usb3.1中Rx、tx为高速pin;2、usb2.0数据pin;3、边频带信号pin;4、电源及地线pin.图表中a6,a7为usb2.0的数据pin;a8,b8为预留pin;a5,b5为配置通道或有源器件电源;配置通道的功能:1、探测usbtypec连接器端口是否插配,从而决定如何配置电源的供应;2、探测usbtypec公头连接器的方向性,从而决定采用哪侧的高速信号pin组传输信号;3、建立连接的主从关系;4、探测连接的额电流水平/大小,控制或配置电源的供应水平;5、usbpd通讯;6、给有源器件供应电源;7、功能延伸。

usbtypec连接器-公头设计指南:使用高性能的pcb基板材料。

推荐pcb厚度应该有一个公差小于或等于±10%的usb插针间距;篇二:typec数据线规格书typec数据线规格书V1.0关键词:typec、数据线摘要:本文介绍了数据线的规格,性能及测试规范。

缩略语:1范围标准适用于typeatoc数据线需求规格书,未尽规格描述以typec协会规范V1.1为准。

2编写依据3数据线正常工作和存储条件3.1数据线应能在下列条件下正常工作:3.1.1工作环境温度:-20℃~+55℃;(仅作单体验证目的,与整机匹配时以整机试验环境为准);3.1.2相对湿度:5%~95%;3.1.3大气压力:86kpa~106kpa;3.1.4数据线的存储温度:-40℃~+85℃;4数据线主要参数4.1数据线连线规格详细尺寸以及工艺要求以3d图档为准1、typec金属插头,要求必须是整体拉伸成型,不能是折弯成型,不接受接缝;2、金属插头部分,要求做不锈钢原色,表面喷砂处理:50u”~150u”mattnickelplatingoVeRall3、保证至少3a通流能力整条线缆产品详细规格(bom清单,包括端子图纸2d&可拆解版本的3d)要有确认才能认可(认证时必须提供以上文件)。

线材行业高频线性能测试规范

一.目的:确保实验室测试人员能正确执行测试标准.特性定此办法二.范围: 实验室所有测试线材均适用三.高频线测试标准如下:B2.0线材特性测试标准(引用标准USB2.0协会标准 .相关规范 EIA-364-101 EIA-364-102EIA-364-103 EIA-364-08规范)B3.0线材特性测试标准. (引用标准USB3.0协会标准 .相关规范 EIA-364-101 EIA-364-102EIA-364-103 EIA-364-08规范)3. DVI线材特性测试标准(引用标准DVI协会标准 .相关规范 EIA-364-101 EIA-364-102EIA-364-103 EIA-364-08规范)标题高频线特性测试规范生效日期核准:审核:制文:4. HDMI1.4线材特性测试标准(引用标准HDMI协会标准 .相关规范 EIA-364-101 EIA-364-102EIA-364-103 EIA-364-08规范)标题高频线特性测试规范生效日期核准:审核:制文:5.Displayport线材测试标准.(相关规范 EIA-364-101 EIA-364-102 EIA-364-103 EIA-364-08规范标题高频线特性测试规范生效日期核准:审核:制文:标题高频线特性测试规范生效日期核准:审核:制文:6. 网络线材CAT.5E特性测试标准:(引用EIA/TIA规范)6.1IMPZ 要求100+/-15 Ohm6.2Return LossParameter: Return Loss Unit: dB Start 1 4 8 10 16 20 25 31.25 62.5 100 1 10 20 End 1 4 8 10 16 20 25 31.25 62.5 100 10 20 100 SPEC Hi -20 -23 -24.5 -25 -25 -25 -24.3 -23.6 -21.5 -20.1 Fn:1 -25 Fn:1 6.3 AttenuationParameter: Attenuation@20℃Start 1 4 8 10 16 20 25 31.25 62.5 100End 1 4 8 10 16 20 25 31.25 62.5 100SPEC Hi -- -- -- -- -- -- -- -- -- --实验室文件修订履历表。

[usb3.0传输速度是多少]请问USB3.0的U盘在USB2.0接口下写入速度有多少..

![[usb3.0传输速度是多少]请问USB3.0的U盘在USB2.0接口下写入速度有多少..](https://img.taocdn.com/s3/m/1028073fa4e9856a561252d380eb6294dd88227e.png)

[usb3.0传输速度是多少]请问USB3.0 的U 盘在USB2.0接口下写入速度有多少?篇一: 请问USB3.0 的U盘在USB2.0接口下写入速度有多少?[usb2.0速度]请问USB3.0 的U盘在USB2.0接口下写入速度有多少?刚买了一个U盘,USB3.0的,但是写入速度不到10M/s,商家说dt100 u盘速度在2.0接口下:读取速度:20MB/s 写入速度:5MB/s;在3.0的接口下:读取速度:30MB/s 写入速度:8MB/s dt101 u盘速度写入3m左右,读8m左右dtse9 u盘速度写入4m左右,读8m左右。

请问下大神这个数据是不是假的下面就看看小编为您搜集整理的参考答案吧。

网友杨文松对[usb2.0速度]请问USB3.0 的U盘在USB2.0接口下写入速度有多少?给出的答复:基本属于理论值没报给你Mb/s不错了仅仅理论值不排除主板,线质系统等原因网友沈少Neo对[usb2.0速度]请问USB3.0 的U盘在USB2.0接口下写入速度有多少?给出的答复:差不多,最好的3.0在2.0下也不过30m左右。

一般的3.0就10m 上下吧。

网友蒙面大侠对[usb2.0速度]请问USB3.0 的U盘在USB2.0接口下写入速度有多少?给出的答复:USB2.0理论传输速度是60MB/s,但是根据很久以前一篇关于在Windows7下通过补丁和注册表修改缓冲区提高速度文章中,我重点了解USB2.0的编码方式。

在编码、缓存和干扰的作用下,USB2.0实际速度最高是读取33MB/s,这是在多数U盘优秀主控使用双通道SLC测试的情况下得出的。

而在USB3.0使用USB2.0速度提升貌似也是因为编码等原因会有一定的提升,一般在5MB/s以内。

而且现在金士顿同一型号的U盘在不同阶段使用不同的主控和颗粒,最终的速度也大相近庭。

所以我没有办法根据速度判断真假,至少我没有使用DT100。

而我们一般看真假是看主控型号、颗粒型号实际可用容量是否正常,能拆开基本能确认。

USB3.1最新技术及测试方案

Allion Japan Shanghai Taiwan

XXCAL Japan

SGS Taiwan

Hong Kong STC

*Test Labs Currently Qualified for USB 3.0 Certification Approved labs are listed at /developers/compliance/labs

LFPS

TBD

TX 5G Eye

Eye, Tj

TX 10G Eye

Eye, Tj

SSC Mod Rate, UI and Deviation

ECN15, 18

SSC Mod Rate, UI and Deviation

Max Slew Rate

Rj

SSC df/dt

Rj

Vcm, Vdiff, rt/ft, DCycle, tPeriod, tBurst, tRepeat

• We’re active in standards meetings, workshops, plugfests, and seminars .

• We get involved so you benefit with the right solutions when you need them

SKPOS with variable number of SKPs

LFPS CDR

Training, warm reset or side band signaling protocol (pwr mgmt)

JTF BW 4.9Mhz

Device host capability negotiation is done during LFPS phase using LFPS modulation schemes

MicroUSB行业协会标准

Universal Serial Bus Micro-USB Cables and ConnectorsSpecificationRevision 1.01April 4, 2007Revision HistoryDate Comment Revision Issue0.6 1/30/2006 Revisions to all sections0.7 3/24/2006 Added revised Micro-USB drawings to Rev.0.80.8 4/19/2006 Editorial changes and additions by Jan Fahllund (Nokia)Corrections to the 0.8 version (based by comments from contributors)0.8b 4/26/2006Corrections based on comments from the 0.8b version0.9 6/7/20061.0RC 8/2/2006 Added lubricant recommendation, LLRC delta change specified1.01RC 11/10/2006 Editorial changes and addition based on Oct-06 USB-IF CCWGmeeting.1.02RC 12/10/2006 Shell material thickness tolerances changed so that material can be0.25 mm or 0.3 mm; edited three pictures (Figure 4-10, 4-11 and 4-12).1.03RC 12/11/2006 Two pictures edited (Figure 4-8 and 4-9). In fig 4-8 max height to be2.8mm MAX. In fig 4-9 R0.25mm MAX to be R0.30mm MAX.1.0RC3 12/19/2006 For BoD approvalApproved1.0 1/12/20071.0 1/22/2007 Cosmetic edits for publication1.01 4/4/2007 Editorial corrections and additions to contributor list. Reinserted shelland plug material requirements as section 6.10. Clarified wording onPlating Recommendations.Copyright © 2007 USB Implementers Forum, Inc. (USB-IF).All rights reserved.A LICENSE IS HEREBY GRANTED TO REPRODUCE THIS SPECIFICATION FOR INTERNAL USEONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, ISGRANTED OR INTENDED HEREBY.USB-IF AND THE AUTHORS OF THIS SPECIFICATION EXPRESSLY DISCLAIM ALL LIABILITY FOR INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. USB-IF AND THE AUTHORS OF THISSPECIFICATION ALSO DO NOT WARRANT OR REPRESENT THATSUCH IMPLEMENTATION(S) WILL NOT INFRINGE THE INTELLECTUAL PROPERTY RIGHTS OF OTHERS.THIS SPECIFICATION IS PROVIDED "AS IS" AND WITH NO WARRANTIES, EXPRESS ORIMPLIED, STATUTORY OR OTHERWISE. ALL WARRANTIES ARE EXPRESSLY DISCLAIMED. NO WARRANTY OF MERCHANTABILITY, NO WARRANTY OF NON-INFRINGEMENT, NO WARRANTY OF FITNESS FOR ANY PARTICULAR PURPOSE, AND NOWARRANTY ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.IN NO EVENT WILL USB-IF OR USB-IF MEMBERS BE LIABLE TO ANOTHER FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA OR ANY INCIDENTAL, CONSEQUENTIAL, INDIRECT, ORSPECIAL DAMAGES, WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THE USE OF THIS SPECIFICATION, WHETHER OR NOT SUCHPARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.All product names are trademarks, registered trademarks, or service marks of their respective owners.ContributorsMark Rodda, (editor) Motorola Kevin Fang, Longwell ElectronicsJan Fahllund, (editor) Nokia Morgan Jair, Main Super Co.Jim Koser, (CCWG Chairman), Foxconn Tom Kawaguchi, Matsushita Electric Works Glen Chandler, Advanced-Connectek (Acon) Ron Ward, Matsushita Electric Works Charles Wang, Advanced-Connectek (Acon) Satoshi Yamamoto, Matsushita Electric Works Toshinori Sasaki, Across Techno Yasuhiko Shinohara, MitsumiMinoru Ohara, Allion Atsushi Nishio, MitsumiBrad Brown, ATL Hitoshi Kawamura, MitsumiChristopher Mattson, ATL Scott Sommers, MolexMarcus Darrington, ATL Kevin Delaney, MolexJaremy Flake, ATL Technology Kieran Wright, MolexGeorge Olear, Contech Research Padraig McDaid, MolexRoy Ting, Elka Mikko Poikselka, MolexSophia Liu, ETC Sam Liu, Newnex Technology Corp.Bill Northey, FCI Richard Petrie, NokiaTsuneki Watanabe, Foxconn Kai Silvennoinen, NokiaJim Zhao, Foxconn Panu Ylihaavisto, NokiaDavid Ko, Foxconn Arthur Zarnowitz, PalmJong Tseng, Foxconn Douglas Riemer, SMKJack Lu, Foxlink Eric Yagi, SMKTim Chang, Foxlink Abid Hussain, Summit Microelectronics Sathid Inthon, Fujikura Kaz Osada, TycoToshi Mimura, Fujijura Masaru Ueno, TycoAlan Berkema, Hewlett-Packard Yoshikazu Hirata, TycoKarl Kwiat, Hirose Ed Beeman, USB Implementers Forum Shinya Tono, Hirose Mark Paxson, USB Implementers Forum Kazu Ichikawa, HiroseRyozo Koyama, HiroseYousuke Takeuchi, HiroseTsuyoshi Kitagawa, HosidenJim Eilers, HosidenKazuhiro Saito, JAERon Muir, JAEMark Saubert, JAEYasuhira Miya, JSTTakahiro Diguchi, JSTYoichi Nakazawa, JSTTable of Contents1Introduction (6)1.1General (6)1.2Objective of the Specification (6)1.3Intended Audience/Scope (6)1.4Related Documents (6)2Acronyms and Terms (7)3Significant Features (8)3.1USB 2.0 Specification Compliance (8)3.2On-The-Go Device (8)3.3Connectors (8)3.4Compliant Cable Assemblies (8)3.5Plug Overmolds (9)4Cables and Connectors (10)4.1Introduction (10)4.2Micro-Connector Mating (10)4.3Color Coding (11)4.4Device, Cable and Adapter Delays (11)4.5Compliant Usage of Connectors and Cables (12)4.5.1Cables (12)4.5.2Overmolds (12)4.5.3Mechanical Interfaces (12)4.5.4Surface mount standard version drawings (12)4.5.5DIP-type and Midmount-type receptacles (12)4.5.6Connector Keying (12)4.5.7Right Angle Plugs (12)4.5.8Adapters (13)4.6Drawings (13)5Electrical Compliance Requirements (33)5.1Data Rates Beyond USB 2.0 (480Mb/s -->) (33)5.2Low Level Contact Resistance (33)5.3Contact Current Rating (33)5.3.1Signal Contacts Only (2, 3, and 4) (33)5.3.2With Power Applied Contacts (1 and 5) (33)6Mechanical Compliance Requirements (34)6.1Operating Temperature Range (34)6.1.1Option I (34)6.1.2Option II (34)6.2Insertion Force (34)6.3Extraction Force (34)6.4Plating (34)6.4.1Option I (35)6.4.2Option II (35)6.5Solderability (35)6.6Peel Strength (Reference Only) (35)6.7Wrenching Strength (Reference Only) (35)6.8Lead Co-Planarity (35)6.9RoHS Compliance (36)6.10Shell & Latch Materials (36)FiguresFigure 4-1 Micro-A to Micro-B Cable (14)Figure 4-2 Standard-A to Micro-B Cable (15)Figure 4-3 Micro-A to Captive Cable (16)Figure 4-4 Micro-A Plug Overmold, Straight (17)Figure 4-5 Micro-B Plug Overmold, Straight (18)Figure 4-6 Micro-A Plug Interface (19)Figure 4-7 Micro-B Plug Interface (20)Figure 4-8 Micro-A/B Plug Interface (Cut-section) (21)Figure 4-9 Micro-AB receptacle interface (22)Figure 4-10 Micro-B receptacle interface (23)Figure 4-11 Micro-AB Receptacle Design (24)Figure4-12 Micro-B Receptacle Design (25)Figure 4-13 Micro-A Plug Blockage (26)Figure 4-14 Micro-B Plug Blockage (27)Figure 4-15 Micro-A Plug, Side Right Angle (28)Figure 4-16 Micro-A Plug, Down Right Angle (29)Figure 4-17 Micro-B Plug, Side Right Angle (30)Figure 4-18 Micro-B Plug, Down Right Angle (31)Figure 4-19 Adapter, Standard-A receptacle to Micro-A plug (32)TablesTable 4-1. Plugs Accepted By Receptacles (10)Table 4-2. Micro-A Plug Pin Assignments (10)Table 4-3. Color Coding for Plugs and Receptacles (11)Table 4-4. Maximum Delay for Micro-Connector and Cable (11)Table 4-5. Maximum Delay for Standard Connector Cable (11)1 Introduction1.1 GeneralUSB has become a popular interface for exchanging data between cell phone and portable devices. Many of these devices have become so small it is impossible to use standard USB components as defined in the USB 2.0 specification. In addition the durability requirements of the Cell Phone and Portable Devices market exceed the specifications of the current interconnects. Since Cell Phones and other small Portable Devices are the largest market potential for USB, this specification is addressing this very large market while meeting all the requirements for electrical performance within the USB 2.0 specification.1.2 Objective of the SpecificationThe purpose of this document is to define the requirements and features of a Micro-USB connector that will meet the current and future needs of the Cell Phone and Portable Devices markets, while conforming to the USB 2.0 specification for performance, physical size and shape of the Micro-USB interconnect.This is not a stand-alone document. Any aspects of USB that are not specifically changed by thisspecification are governed by the USB 2.0 Specification and USB On-The-Go Supplement.1.3 Intended Audience/ScopeCell phone and Portable Devices have become so thin that the current Mini-USB does not fit well within the constraints of future designs. Additional requirements for a more rugged connector that will have durability past 10,000 cycles and still meet the USB 2.0 specification for mechanical and electrical performance was also a consideration. The Mini-USB could not be modified and remain backward compatible to the existing connector as defined in the USB OTG specification.1.4 Related DocumentsUSB 2.0USB OTG Supplement2 Acronyms and TermsThis chapter lists and defines terms and abbreviations used throughout this specification.A-Device A device with a Type-A plug inserted into its receptacle. The A-devicesupplies power to V BUS and is host at the start of a session. If the A-device is On-The-Go, it may relinquish the role of host to an On-The-GoB-device under certain conditions,Application A generic term referring to any software that is running on a device thatcan control the behavior or actions of the USB port(s) on a device.B-Device A device with a Type-B plug inserted into its receptacle. The B-device isa peripheral at the start of a session. If the B-device is OTG, it may begranted the role of host from an OTG A-device.DIP-type A connector with contact and shield solder tails that are soldered throughthe printed circuit boardFS Full Speed (max 12Mb/s)Higher than HS (480Mb/s ---> 5 Gb/s)HS High Speed (max 480 Mb/s)Host A physical entity that is attached to a USB cable and is acting in the roleof the USB host as defined in the USB Specification, Revision 2.0. Thisentity initiates all data transactions and provides periodic Start of Frames.HNP Host Negotiation ProtocolID Identification. Denotes the pin on the Micro connectors that is used todifferentiate a Micro-A plug from a Micro-B plug.LS Low Speed (max 1,5 Mb/s)Midmount-type A connector that is mounted in a cut-out in the printed circuit boardbetween the top and bottom surfaces.OTG On-The-GoOTG device A device with the host and peripheral capabilitiesPeripheral A physical entity that is attached to a USB cable and is currentlyoperating as a “device” as defined in the USB Specification, Revision 2.0.The Peripheral responds to low level bus requests from the Host.PCB Printed circuit boardUSB Universal Serial BusUSB-IF USB Implementers Forum3 Significant FeaturesThis section identifies the significant features of the Micro-USB specification. The purpose of this section is not to present all the technical details associated with each major feature, but rather to highlight itsexistence. Where appropriate, this section references other parts of the document where further details can be found.3.1 USB 2.0 Specification ComplianceAny device with Micro-USB features is first and foremost a USB peripheral that is compliant with the USB2.0 specification.3.2 On-The-Go DeviceAny OTG Micro-USB device shall conform to the OTG requirements as set forth in the On-The-GoSupplement to the USB 2.0 Specification.3.3 ConnectorsThe USB 2.0 specification defines the following connectors:•Standard-A plug and receptacle,•Standard-B plug and receptacle, and•Mini-B plug and receptacle.The Micro-USB specification defines the following additional connectors:•Micro-B plug and receptacle• Micro-AB receptacle• Micro-A plug.The Micro-AB receptacle is only allowed on OTG products. All other uses of the Micro-AB receptacle are prohibited. The Micro-AB receptacle accepts either a Micro-A plug or a Micro-B plug.It is recommended that the Micro-AB continue to support HNP as requested and support full functionality asa peripheral when a Micro-B plug is inserted.3.4 Compliant Cable AssembliesThe USB 2.0 specification defines the following cables:•Standard-A plug to Standard–B plug,•Standard-A plug to Mini-B plug, and•Captive cable with Standard-A plug.The Micro-USB specification defines the following additional cables:•Micro-A plug to Micro-B plug,•Micro-A plug to Standard-A receptacle•Micro-B plug to Standard-A plug, and•Hardwired Captive cable with Micro-A plug. (Hardwired Captive cable is a cable, connected internally to a device, which is not designed to be removed by the end user of that device.) No other types of cables are allowed by either the USB specification, or by the OTG supplement. Cables are not allowed to have receptacles on either end unless they meet the mechanical and electricalrequirements of adapters defined in this document.3.5 Plug OvermoldsThe Micro-USB specification constrains the size and the shape of the overmolds for the Micro-A and Micro-B plugs.The Micro-A plug’s overmold has a rectangular shape, and the Micro-B plug’s overmold is rectangular with chamfers. This allows easy recognition and differentiation of the two plugs by the consumer See pictures Figure 4-4 and Figure 4-5.4 Cables and Connectors4.1 IntroductionThis chapter provides the mechanical and electrical specifications for the cables, connectors and cable assemblies used to interconnect devices as well as constraints on the design of the overmolds for the Micro-A and Micro-B plugs.4.2 Micro-Connector MatingThe following table summarizes the plugs accepted by each of the receptacles.Table 4-1. Plugs Accepted By ReceptaclesReceptacle PlugsAcceptedStandard-A Standard-AStandard-B Standard-BMini-B Mini-BMicro-B Micro-BMicro-AB Micro-A or Micro-BThe usage and wiring assignments of the five pins in the Micro-A plug are defined in the following table.Table 4-2. Micro-A Plug Pin AssignmentsContact Number Signal Name Typical WiringAssignment1 VBUS Red2 D- White3 D+ Green4 ID <Ra_PLUG_ID5 GND BlackShell Shield DrainWireThe ID pin on a Micro-A plug shall be connected to the GND pin. The ID pin on a Micro-B plug is not connected or is connected to ground by a resistance of greater than Rb_PLUG_ID (100kΩ MIN). An On-The-Go device is required to be able to detect whether a Micro-A or Micro-B plug is inserted by determining if the ID pin resistance to ground is less than Ra_PLUG_ID (10Ω MAX) or if the resistance to ground is greater than Rb_PLUG_ID . Any ID resistance less than Ra_PLUG_ID shall be treated as ID = FALSE and any resistance greater than Rb_PLUG_ID shall be treated as ID = TRUE.4.3 Color CodingThe following colors are mandated for the plastic inside the Micro-USB connectors defined in thisspecification.Table 4-3. Color Coding for Plugs and ReceptaclesConnector ColorMicro-A plug WhiteMicro-B receptacle BlackMicro-B plug BlackMicro-AB receptacle Gray4.4 Device, Cable and Adapter DelaysIn Figure 7-11 of the USB 2.0 specification, four test planes are defined along the transmission path fromthe host transceivers to the peripheral transceivers. These test planes (TP) are as follows:•TP1: pins of host transceiver chip•TP2: contact points of host Standard-A receptacle•TP3: contact points of peripheral Standard-B or Micro-B receptacle•TP4: pins of peripheral transceiver chipThe maximum total delays are as follows:•On-The-Go device - TP1 to TP2: 1 ns• Adapter: 1 ns•Any cable with a Micro-A or Micro-B plug: 10 nsThe maximum delays for the two worst cases of connection are shown in the following tables.Table 4-4. Maximum Delay for Micro-Connector and CableTimeLocation DelayUSB 2.0 Compliant Host – TP1 to TP2 3 nsStandard-A receptacle to Micro-A plug adapter 1 nsMicro-A plug to Micro-B plug cable 10 nsUSB 2.0 Compliant B-device – TP3-TP4 1 nsns Total 15Table 4-5. Maximum Delay for Standard Connector CableTimeLocation DelayOn-The-Go Compliant Device – TP1 to TP2 1 nsMicro-A plug to Standard-A receptacle adapter 1 nsStandard-A plug to Standard-B plug cable 26 nsUSB 2.0 Compliant B-device – TP3 to TP4 1 nsns Total 294.5 Compliant Usage of Connectors and CablesCable assemblies and connectors not described below or not allowed by other amendments to the USB specification are not compliant with the USB specification and may not be labeled as such.4.5.1 CablesThe cables allowed by the Micro-USB specification are shown in Figure 4-1, Figure 4-2, and Figure 4-3.Cables must have a propagation delay of 10 ns or less, have a physical length of no more than 2.0 meters, and meet all other requirements of a USB cable.4.5.2 OvermoldsThe size and shape of the Micro-A and Micro-B plug overmolds must conform to the constraints shown in Figure 4-4 and Figure 4-5 .Interfaces4.5.3 MechanicalThe mechanical interface dimensions for the Micro-A and Micro-B plugs are shown in Figure 4-6 and Figure 4-7. Mechanical interface dimensions for Micro-AB and Micro-B receptacles are shown in Figure 4-9 and Figure 4-10.4.5.4 Surface mount standard version drawingsBy following these instructions, receptacles from different manufacturers can be used interchangeably on the same printed circuit board (PCB). In the case of the “surface mount standard version”, the dimensions of the contact tail and shield tail must comply with figures 4-11 and 4-12.Note: PCB-layout drawings are included for reference only.Figure 4-11 and Figure4-12 shows designs for the Micro-AB and Micro-B receptacles respectively.4.5.5 DIP-type and Midmount-type receptaclesDIP-type (contact and shield tails soldered through PCB) and Midmount-type (connector that is mounted ina cut-out in the printed circuit board between the top and bottom surfaces.) receptacle connectors are notdefined in this standards document. These mounting styles are allowed under the standard as long as all intermating conditions are met. Mechanical dimensions and mechanical durability values may vary from the Surface mount standard connector but must comply with all minimum values.4.5.6 ConnectorKeyingThis Micro connector series has been designed so as to prevent the Micro-A and Micro-B plugs from being incorrectly inserted into a receptacle. The amount of metal blocking various possible incorrect insertions is shown in Figure 4-13 and Figure 4-14, and is always greater than 0.35 mm.4.5.7 Right Angle PlugsThe overmolds for right / down angle plugs are required to comply with the same shape constraints that apply to straight plugs. Reference drawings for right / down angle plugs are shown in Figure 4-15, Figure 4-16, Figure 4-17 and Figure 4-18 .4.5.8 AdaptersRequirements:•The propagation delay of the adapter shall be less than 1 ns.•The physical length shall not exceed 150 mm.•The resistance of the adapter through V BUS and GND, including contacts, shall not exceed 70 mΩ.4.5.8.1 Standard-A receptacle to Micro-A plugThis adapter is used to connect a cable with a Standard-A plug to an On-The-Go device that has a Micro-AB receptacle. A reference drawing for this adapter is shown in Figure 4-19.4.6 DrawingsThis section contains the mechanical drawings that are referenced in the previous section.Figure 4-1 Micro-A to Micro-B CableFigure 4-2 Standard-A to Micro-B CableFigure 4-3 Micro-A to Captive CableFigure 4-4 Micro-A Plug Overmold, StraightFigure 4-5 Micro-B Plug Overmold, StraightFigure 4-6 Micro-A Plug InterfaceFigure 4-7 Micro-B Plug InterfaceFigure 4-8 Micro-A/B Plug Interface (Cut-section)Figure 4-9 Micro-AB receptacle interfaceFigure 4-10 Micro-B receptacle interfaceFigure 4-11 Micro-AB Receptacle DesignFigure4-12 Micro-B Receptacle DesignFigure 4-13 Micro-A Plug BlockageFigure 4-14 Micro-B Plug BlockageFigure 4-15 Micro-A Plug, Side Right AngleFigure 4-16 Micro-A Plug, Down Right AngleFigure 4-17 Micro-B Plug, Side Right AngleFigure 4-18 Micro-B Plug, Down Right AngleFigure 4-19 Adapter, Standard-A receptacle to Micro-A plugElectrical requirements are unchanged from the USB 2.0 specification (Chapter 6; Table 6-7) and the On-The-Go Supplement to the USB 2.0 Specification, unless otherwise specified here.5.1 Data Rates Beyond USB 2.0 (480Mb/s -->)This section will be amended as requirements for higher data rates (beyond the current USB 2.0specification) become available.5.2 Low Level Contact Resistance30mΩ(Max) initial when measured at 20mV (Max) open circuit at 100mA. Maximum change (delta) of +10 mΩafter 10,000 insertion/extraction cycles at a maximum rate of 500 cycles per hour.(When manually operated, mating speed should be below 200 cycles per hour.)5.3 Contact Current Rating5.3.1 Signal Contacts Only (2, 3, and 4)1A minimum when measured at an ambient temperature of 25 degrees Celsius. With power applied to the contacts, the delta temperature must not exceed +30degrees Celsius at any point in the USB connector under test.5.3.2 With Power Applied Contacts (1 and 5)1.8A for contacts 1 and 5 and at the same time 0.5A for contacts 2, 3 & 4, minimum when measured at anambient temperature of 25 degrees Celsius. With power applied to the contacts, the delta temperature must not exceed +30degrees Celsius at any point in the USB connector under test.The following requirements will take precedence over the requirements set forth in the USB 2.0specification (Chapter 6; Table 6-8) and the On-The-Go Supplement to the USB 2.0 Specification.6.1 Operating Temperature RangeI6.1.1 Option-30°C to +80°CII6.1.2 Option-30°C to +85°C (and above)6.2 Insertion ForceRecommendations:- It is recommend to use a non-silicon based lubricant on the latching mechanism toreduce wear. If used the lubricant may not affect any other characteristic of the system.- 35 Newton’s maximum at a maximum rate of 12.5 mm(0.492") per minute.6.3 Extraction Force- 8N (MIN) after 10000 insertion/extraction cycles (at a maximum rate of 12.5mm(0.492") per minute).- No burs or sharp edges are allowed on top of locking latches (hook surfaces which will rub against receptacle shield).- It is recommend to use a non-silicon based lubricant on the latching mechanism to reduce wear. If used the lubricant may not affect any other characteristic of the system.6.4 PlatingRecommendations:- Contact plating should be done after stamping and forming- Burrs should not be present on contact areas- Contact area as smooth as possible before plating- Use a sealing treatment to control plating porosity (contact area)I6.4.1 Option6.4.1.1 ReceptacleContact area: (Min) 0.05 µm Au + (Min) 0.75 µm Ni-Pd on top of (Min) 2.0 µm NiContact tail: (Min) 0.05 µm Au on top of (Min) 2.0 µm Ni6.4.1.2 PlugContact area: (Min) 0.05 µm Au + (Min) 0.75 µm Ni-Pd on top of (Min) 2.0 µm NiII6.4.2 Option6.4.2.1 ReceptacleContact area: (Min) 0.75 µm Au on top of (Min) 2.0 µm NiContact tail: (Min) 0.05 µm Au on top of (Min) 2.0 µm Ni6.4.2.2 PlugContact area: (Min) 0.75 µm Au on top of (Min) 2.0 µm Ni6.5 SolderabilitySolder shall cover a minimum of 95% of the surface being immersed, when soldered at temperature 255℃ +/-5℃ for immersion duration 5S (component is to be lead-free component) using Type R flux.6.6 Peel Strength (Reference Only)Minimum 150N when soldered connector is pulled up from PCB in the vertical direction.6.7 Wrenching Strength (Reference Only)Perpendicular Force Test : This test shall be performed using virgin parts. Perpendicular forces (Fp) are applied to a plug when inserted at a distance (L) of 15mm from the edge of the receptacle. Testingconditions & method should be agreed with all parties. These forces are to four direction (left, right, up, down). Compliant connectors will meet the following force thresholds with the following results :- No plug or receptacle damage: 0 - 25N- The plug can be damaged, but in such a way that the receptacle does not sustain damage: 25 - 50N 6.8 Lead Co-PlanarityCo-planarity of all SMT leads shall be within 0.08mm range.6.9 RoHS ComplianceComponent is to be RoHS compliant. Lead Free plug and receptacle materials must conform to Directive 2002/95/EC of January 27, 2003 on Restriction of Hazardous Substances (RoHS).6.10 Shell & Latch MaterialsShell and latch materials for both plug and receptacle shall be stainless steel or mechanically equivalent material.。

USB 2 0

特点

(1)速度快:接口的传输速度高达480 Mbit/s,完全能满足高速数据交换的要求; (2)连接简单快捷:所有的 USB设备利用通用的连接器,无需打开主机机箱就可简单方便地连人计算 机,实现热拔插; (3)无需外接电源:USB电源向低压设备提供 5V电源; (4)有不同的带宽和连接距离:USB 2.0提供全速与高速 2种传输数率规格,使用户有足够的带宽供新 的外设使用; (5)良好的兼容性:系统检测到 1.1版本的接口类型时,会自动按照 12 Mbit/s的速度传输,而其他采 用 2.0版本的外设还是能以2.0所规定的速率传输。

2000年制定的USB 2.0标准是真正的USB 2.0,被称为USB 2.0的高速(High-speed)版本,理论传输速度 为480 Mbps,即60 MB/s,但实际传输速度一般不超过30 MB/s,采用这种标准的USB设备也比较多。

支持ห้องสมุดไป่ตู้统

USB接口定义Microsoft Windows 98 SE Microsoft Windows Me Microsoft Windows 2000(确保已安装Service Pack 4) Microsoft Windows XP Microsoft windows Vista Microsoft Windows 7 Microsoft Windows 8 Microsoft Windows Server 2003/2008/2008 R2/2012/2012 R2/2016 Microsoft Windows 10 Mac OS X Linux内核的各版本各品牌系统

规范

注意:本文所说的Mbps乃是“兆位每秒”,并不是我们日常用的“兆字节每秒”。一字节等于八位。

这里有必要先说清楚一下USB2.0规范的由来。USB2.0技术规范是有由Compaq、Hewlett Packard、Intel、 Lucent、Microsoft、NEC、Philips共同制定、发布的,规范把外设数据传输速度提高到了480Mbps,是USB 1.1设备的40倍!但按照原定计划新的USB 2.0标准只是准备把这个标准定在240Mbps,后来,经过努力将它提高 到了480Mbps。

解读USBIF电池充电规范

解读USBIF电池充电规范背景2009年4月,全球移动通信系统协会(GSMA)联合OTMP(手机开放组织联盟)17家移动运营商和制造商宣布实施跨行业的通用充电器标准,此标准采纳了USB-IF的micro-USB接口作为手机数据和充电的统一接口,并采纳USB-IF的Battery Charging 规范作为充电规范。

USB-IF公布了1.1版的Battery charging规范(以下简称为BC规范),比起两年前公布的1. 0版本,这个新版本有了较大更新和补充。

同时,与之配套的测试规范也正在制定中,预计将在年内颁布和实施。

届时USB Battery Charging相关测试项目将纳入到USB兼容测试认证中。

电池充电规范原有USB2.0规范并没有考虑到使用USB接口为便携式设备的电池进行充电的需求,而这样的需求却越来越多。

BC规范要解决的就是这个问题,符合规范的设备和系统即向下兼容USB2.0标准,又针对充电做出了特别的优化。

实际上,BC规范的核心内容就是引入了充电端口识别机制。

一个符合BC规范的便携式USB设备或OTG设备通过这套机制可以识别出是插到了一个标准的USB下行接口(Standard Downstream Port );一个USB专用充电器(USB Charger);还是一个针对充电做过优化的USB 下行接口(Charging Downstream Port)。

然后,这些设备将根据不同的情况,按照BC规范的要求来获取不同的电流。

便携式设备和三种USB充电接口● Portable DevicePortable Device(以下简称PD)指电池供电的便携式USB外设或者OTG设备,可以通过USB接口来为自身的电池充电。

BC规范建议这些的PD应该具备相应的端口识别能力和对从USB总线获取电流的控制能力。

● Standard Downstream Port基本上,这个Standard Downstream Port指符合现有USB2.0规范的主机(HOST)或集线器(HUB)上的下行USB接口。

usb0协会标准

usb0协会标准USB0协会标准。

USB0协会标准是指由USB0协会制定的关于USB接口的技术规范和标准。

USB(Universal Serial Bus)是一种用于连接计算机和外部设备的通用接口标准,它的出现极大地方便了人们使用各种外部设备,如打印机、键盘、鼠标、摄像头等。

USB0协会标准的制定对于推动USB技术的发展和应用具有重要意义。

首先,USB0协会标准对USB接口的物理连接进行了规范。

它规定了USB接口的外形尺寸、引脚定义、插拔方式等方面的要求,确保了不同厂家生产的USB设备之间的互插性和兼容性。

这使得用户可以更加方便地选择和使用各种USB设备,而不必担心接口不匹配的问题。

其次,USB0协会标准对USB接口的电气特性进行了规范。

它规定了USB接口的电压、电流、信号传输速率等参数,保证了USB设备在连接和通信过程中的稳定性和可靠性。

这为USB设备的正常工作提供了技术保障,同时也为USB接口的进一步发展提供了基础。

此外,USB0协会标准还对USB接口的通信协议进行了规范。

它定义了USB设备之间的通信方式、数据传输格式、命令和数据的交互过程等内容,确保了不同USB设备之间可以进行有效的数据交换和通信。

这为USB设备的应用提供了统一的技术标准,使得USB技术在各种应用场景中得以广泛应用。

总的来说,USB0协会标准的制定为USB技术的发展和应用奠定了坚实的基础。

它规范了USB接口的物理连接、电气特性和通信协议,保证了USB设备之间的互插性、兼容性和稳定性,推动了USB技术的不断创新和进步。

随着科技的不断发展,相信USB0协会标准将会继续发挥重要作用,推动USB技术在各个领域的广泛应用。

USB接口指标测试指导书的参考学习分享

USB接口指标测试指导书1、USB接口指标描述为了顺应市场的要求,目前的产品大部分都出的是USB2.0的接口,而且我们产品都是作为HOST端,USB2.0一共提供3种速率,如下表。

数据速率上升时间Low Speed 1.5Mbps 75~300ns Full Speed 12Mbps 4~20ns High Speed 480Mbps >500ps 当我们的设备是作为HOST端是,数据方向是Down Stream,其关注的指标有:1、信号质量1)眼图测试(Eye-Diagram testing) 2)信号速率(Signal Rate) 3)包结尾宽度(End of Packet Width) 4)JK抖动(JK jitter) 5)KJ抖动(KJ jitter) 6)连续抖动(Consecutive jitter) 7)单调性测试(Monotonic test (for HS)) 8)上升与下降时间(Rise and Fall times) 2、Droop(电压跌落) 3、Chirp (Shake Hands) 2、USB接口指标测试方法(1)信号质量测试由于我们的设备都是作为HOST端,在这里只介绍HOST端的接口指标测试方法。

1)USB High Speed信号质量测试方法信号质量测试方法a)连接好被测设备(DUT)、测试夹具和示波器,具体的连接示意图如图1所示。

图 1 High Speed 信号质量测试连接示意图信号质量测试连接示意图b) DUT 上电,启动USB 测试包,发送测试命令,使USB 端口能够发送出测试码流,具体的码流波形如图具体的码流波形如图 2所示。

所示。

图 2 High Speed 信号质量测试波形信号质量测试波形c) 运行示波器上的USB 测试软件,在Analyze 菜单中选择USB2.0 Test 启动后的界面如图面如图 3所示。

在软件的Measurements 菜单中选择Select ,然后选择High Speed ,选择测试项,在这里可以点击Select All ,将信号质量的测试项全部选上。

USB 协会标准

USB3.0相关技术规范1:USB3.0标准技术规范于2008年11月12日正式发行,版本为1.0,起草单位主要有惠普、因特尔、微软、NEC、ST-NXP半导体、德州仪器等公司。

2:USB3.0架构综述,Superspeed USB与USB2.0对比:特性 Superspeed USB USB2.0数据速率 Superspeed(5.0 Gb/s) Low-speed(1.5Mb/s),full-speed(12Mb/s), and high-speed(480 Mb/s)数据界面 双向-单一,四线差动信号从USB2.0信号分离单工传输,整体成全双工传输。

半双工双线差动信号单向数据传输(越过定向总线转移)。

Cable信号计算 6根:Superspeed 数据路径4根;Non-Superspeed 数据路径2根。

2根:low-speed/full-speed/high-speed数据路径。

总线传输协议 由主机指向,异步通信流向压缩包通信是被明确程序规定的。

由主机指向,polled通信流向压缩包通信被传送到所有的驱动设备里。

负载管控 多级别链接负载管控支持空转,睡眠及延缓状态;链接-,驱动设备-,功能级别级别负载管控。

端口级别随着输入/输出两种级别潜在而延缓;驱动设备-级别负载管控。

总线负载 与USB2.0相同,无限制负载提升50%,而限制负载提升80%。

为低速/高速 总线-负载驱动设备和低负载限制(无限制和延缓型驱动设备)提供支持。

端口状况 端口硬件探测连接活动且带动端口进入工作状态做准备(为超速数据交换)。

端口硬件探测连接活动,系统软件利用端口命令跃迁使端口进入激活状态。

数据传输类型 USB2.0类型高速压缩, 四种数据传输类型:控制,Bulk,中断,同步3:USB3.0具备以下主要优势:① 支持5Gb/s的传输速率;② 向上全面兼容USB2.0;③ 连接器形式变异因素降到最小;④ 为电磁干扰(EMI)提供保护;⑤ 支持OTG(On-The-Go);⑥ 成本低。

(仅供参考)USB协会标准

USB 2.0 Specification Engineering Change Notice (ECN) #1: Mini-B connector Date: 10/20/2000Reason for ECN:The USB 2.0 specified device-side connector – the B connector – is too large for use with a new generation of handheld and mobile devices, e.g., cell phones which would benefit from connectivity to the PC. This ECN incorporates a specification of a device-side mini connector (hereafter referred to as a mini-B connector). The new connector only applies to upstream facing ports, i.e., connectors on devices.Summary of ECN:The bulk of the ECN specifies the mechanical requirements for the mini-B plug, receptacle and cable assembly. It also identifies the usage scope of this connector. The last part of the ECN describes the minimum test criteria and performance requirements for the new connector.Benefits of ECN:The ECN enables standardization of miniature device-side USB connectors and consequent economies of scales and lower cost for a new and growing class of devices which will benefit from connectivity to the PC. The standardization also allows leveraging of the compliance test and certification model which is already in place for USB connectors.Assessment of Impact on Current Specification and Current USB Products:The connector specified in the ECN will not have any impact on hardware or software of existing USB products. The current USB spec already allows for vendor-specific device side connectors – such cable assemblies are called captive assemblies. All that the ECN does is to identify one such connector for use in devices which need the smaller size of connector. There is a potential for some end-user confusion because of two standard cable options; but this can be mitigated by appropriate end-user education.Structure of ECN:The ECN is in the form of a new Chapter 6 with the mini-B connector requirements inserted into the appropriate locations. This format enables specification of the new connector in context.Universal Serial Bus Specification Revision 2.0Chapter 6MechanicalThis chapter provides the mechanical and electrical specifications for the cables, connectors, and cable assemblies used to interconnect USB devices. The specification includes the dimensions, materials,electrical, and reliability requirements. This chapter documents minimum requirements for the external USB interconnect. Substitute material may be used as long as it meets these minimums.6.1 Architectural OverviewThe USB physical topology consists of connecting the downstream hub port to the upstream port of another hub or to a device. The USB can operate at three speeds. High-speed (480 Mb/s) and full-speed (12 Mb/s) require the use of a shielded cable with two power conductors and twisted pair signal conductors. Low-speed (1.5 Mb/s) recommends, but does not require the use of a cable with twisted pair signal conductors.The connectors are designed to be hot plugged. The USB Icon on the plugs provides tactile feedback making it easy to obtain proper orientation.6.2 Keyed Connector ProtocolTo minimize end user termination problems, USB uses a “keyed connector” protocol. The physicaldifference in the Series “A” and “B” (or “mini-B”) connectors insures proper end user connectivity. The “A” connector is the principle means of connecting USB devices directly to a host or to the downstream port of a hub. All USB devices must have the standard Series “A” connector specified in this chapter. The “B” (or “mini-B”) “B” connector allows device vendors to provide a standard detachable cable. This facilitates end user cable replacement. Figure 6-1Figure 6-1 illustrates the keyed connector protocol.85Universal Serial Bus Specification Revision 2.086"B" Receptacles(Upstream Input to theUSB Device or Hub)"A" Receptacles(Downstream Outputfrom the USB Host orHub)Series "mini-B" Connectors♦ Series "mini-B" plugs arealways orienteddownstream towards the"mini-B"Plugs(Fromthe HostSystem)Figure 6-1. Keyed Connector ProtocolUniversal Serial Bus Specification Revision 2.087The following list explains how the plugs and receptacles can be mated:• Series “A ” receptacle mates with a Series “A ” plug. Electrically, Series “A ” receptacles function as outputs from host systems and/or hubs.• Series “A ” plug mates with a Series “A ” receptacle. The Series “A ” plug always is oriented towards the host system.• Series “B ” receptacle mates with a Series “B ” plug (male). Electrically, Series “B ” receptacles function as inputs to hubs or devices.• Series “B ” plug mates with a Series “B ” receptacle. The Series “B ” plug is always oriented towards the USB hub or device.• Series “mini-B ” receptacle mates with a Series “mini-B ” plug (male). Electrically, Series “mini-B ”receptacles function as inputs to hubs or devices.•Series “mini-B ” plug mates with a Series “mini-B ” receptacle. The Series “mini-B ” plug is always oriented towards the USB hub or device.6.3 CableUSB cable consists of four conductors, two power conductors, and two signal conductors.High-/full-speed cable consists of a signaling twisted pair, V BUS , GND, and an overall shield. High-/full-speed cable must be marked to indicate suitability for USB usage (see Section 6.6.2). High-/full-speed cable may be used with either low-speed, full-speed, or high-speed devices. When high-/full-speed cable is used with low-speed devices, the cable must meet all low-speed requirements.Low-speed recommends, but does not require the use of a cable with twisted signaling conductors.6.4 Cable AssemblyThis specification describes three USB cable assemblies: standard detachable cable, high-/full-speed captive cable, and low-speed captive cable.A standard detachable cable is a high-/full-speed cable that is terminated on one end with a Series “A ” plug and terminated on the opposite end with a series “B ” (or “mini-B ”) “B ” plug. A high-/full-speed captive cable is terminated on one end with a Series “A ” plug and has a vendor-specific connect means (hardwired or custom detachable) on the opposite end for the high-/full-speed peripheral. The low-speed captive cable is terminated on one end with a Series “A ” plug and has a vendor-specific connect means (hardwired or custom detachable) on the opposite end for the low-speed peripheral. Any other cable assemblies are prohibited.The color used for the cable assembly is vendor specific; recommended colors are white, grey, or black.6.4.1 Standard Detachable Cable AssembliesHigh-speed and full-speed devices can utilize the “B ” (or “mini-B ”) “B ” connector. This allows the device to have a standard detachable USB cable. This eliminates the need to build the device with a hardwired cable and minimizes end user problems if cable replacement is necessary.Devices utilizing the “B ” (or “mini-B ”) “B ” connector must be designed to work with worst casemaximum length detachable cable. Standard detachable cable assemblies may be used only on high-speed and full-speed devices. Using a high-/full-speed standard detachable cable on a low-speed device may exceed the maximum low-speed cable length.Figure 6-2Figure 6-2 and Figure 6-3 illustrate s a standard detachable cable assembl iesy .Universal Serial Bus Specification Revision 2.088Figure 6-22. USB Standard Detachable Cable AssemblyUniversal Serial Bus Specification Revision 2.0Figure 6-3. USB Standard Mini-connector Detachable Cable Assembly89Universal Serial Bus Specification Revision 2.090Standard detachable cable assemblies must meet the following electrical requirements:•The cable must be terminated on one end with an overmolded Series “A” plug and the opposite end is terminated with an overmolded Series “B” (or “mini-B”) “B” plug.•The cable must be rated for high-speed and full-speed.•The cable impedance must match the impedance of the high-speed and full-speed drivers. The drivers are characterized to drive specific cable impedance. Refer to Section 7.1.1 for details.•The maximum allowable cable length is determined by signal pair attenuation and propagation delay.Refer to Sections 7.1.14 and 7.1.17 for details.•Differences in propagation delay between the two signal conductors must be minimized. Refer to Section 7.1.3 for details.•The GND lead provides a common ground reference between the upstream and downstream ports.The maximum cable length is limited by the voltage drop across the GND lead. Refer to Section 7.2.2 for details. The minimum acceptable wire gauge is calculated assuming the attached device is high power.•The V BUS lead provides power to the connected device. For standard detachable cables, the V BUS requirement is the same as the GND lead.6.4.2 High-/full-speed Captive Cable AssembliesAssemblies are considered captive if they are provided with a vendor-specific connect means (hardwired or custom detachable) to the peripheral. High-/full-speed hardwired cable assemblies may be used with either high-speed, full-speed, or low-speed devices. When using a high-/full-speed hardwired cable on a low-speed device, the cable must meet all low-speed requirements.Figure 6-3 Figure 6-4 illustrates a high-/full-speed hardwired cable assembly.Universal Serial Bus Specification Revision 2.0Figure 6-36-4. USB High-/full-speed Hardwired Cable Assembly91Universal Serial Bus Specification Revision 2.092High-/full-speed captive cable assemblies must meet the following electrical requirements:•The cable must be terminated on one end with an overmolded Series “A” plug and the opposite end is vendor specific. If the vendor specific interconnect is to be hot plugged, it must meet the sameperformance requirements as the USB “B” connector.•The cable must be rated for high-speed and full-speed.•The cable impedance must match the impedance of the high-speed and full-speed drivers. The drivers are characterized to drive specific cable impedance. Refer to Section 7.1.1 for details.•The maximum allowable cable length is determined by signal pair attenuation and propagation delay.Refer to Sections 7.1.14 and 7.1.17 for details.•Differences in propagation delay between the two signal conductors must be minimized. Refer to Section 7.1.3 for details.•The GND lead provides a common reference between the upstream and downstream ports. The maximum cable length is determined by the voltage drop across the GND lead. Refer to Section 7.2.2 for details. The minimum wire gauge is calculated using the worst case current consumption.•The V BUS lead provides power to the connected device. The minimum wire gauge is vendor specific.6.4.3 Low-speed Captive Cable AssembliesAssemblies are considered captive if they are provided with a vendor-specific connect means (hardwired or custom detachable) to the peripheral. Low-speed cables may only be used on low-speed devices.Figure 6-4Figure 6-5 illustrates a low-speed hardwired cable assembly.Universal Serial Bus Specification Revision 2.0Figure 6-46-5. USB Low-speed Hardwired Cable Assembly936.5 Connector Mechanical Configuration and Material RequirementsThe USB Icon is used to identify USB plugs and the receptacles. Figure 6-5Figure 6-6 illustrates the USB Icon.All dimensions are ± 5%Figure 6-5Figure 6-6. USB Icon6.5.1 USB Icon LocationThe USB Icon is embossed, in a recessed area, on the topside of the USB plug. This provides easy user recognition and facilitates alignment during the mating process. The USB Icon and Manufacturer’s logo should not project beyond the overmold surface. The USB Icon is required, while the Manufacturer’s logo is recommended, for both Series “A” and “B” (or “mini-B”) “B” plug assemblies. The USB Icon is also located adjacent to each receptacle. Receptacles should be oriented to allow the Icon on the plug to be visible during the mating process. Figure 6-6Figure 6-7 and Figure 6-8 illustrate s the typical plugorientation s.95Top ViewSection A - A(Plug Cross-Section)Figure 6-6Figure 6-7. Typical USB Plug Orientation 96976.5.2 USB Connector Termination DataTable 6-1Table 6-1 provides the standardized contact terminating assignments by number and electrical value for Series “A” and Series “B” connectors.Table 6-1. USB Series “A” and Series “B”Connector Termination AssignmentContact Number Signal NameTypical WiringAssignment1VBUS Red2D-White3D+Green4GND BlackShell Shield Drain WireTable 6-2 provides the standardized contact terminating assignments by number and electrical value for Series “mini-B” connectors.Table 6-2. USB Series “mini-B” Connector Termination AssignmentContact Number Signal NameTypical WiringAssignment1VBUS Red2D-White3D+Green4ID not connected5GND BlackShell Shield Drain Wire6.5.3 Series “A” and Series “B” (or “Mini-B”) “B” ReceptaclesElectrical and mechanical interface configuration data for Series "A" and Series "B" receptacles are shown in Figure 6-7Figure 6-9 through Figure 6-12 and Figure 6-8. Also, refer to Figure 6-12Figure 6-17 through Figure 6-20, Figure 6-13, and Figure 6-14 at the end of this chapter for typical PCB receptacle layouts.98Figure 6-7Figure 6-9. USB Series "A" Receptacle Interface and Mating Drawing99Figure 6-8Figure 6-10. USB Series "B" Receptacle Interface and Mating Drawing 100101Figure 6-12. USB Series “Mini-B” Receptacle Interface Drawing (Detail) 1026.5.3.1 Receptacle Injection Molded Thermoplastic Insulator MaterialMinimum UL 94-V0 rated, thirty percent (30%) glass-filled polybutylene terephthalate (PBT) orpolyethylene terephthalate (PET) or better.Typical Colors: Black, gray, and natural. The “mini-B” receptacle insulator must be black in color.Flammability Characteristics: UL 94-V0 rated.Flame Retardant Package must meet or exceed the requirements for UL, CSA, VDE, etc.Oxygen Index (LOI): Greater than 21%. ASTM D 2863.6.5.3.2 Receptacle Shell Materials“A” and Series “B”6.5.3.2.1 SeriesSubstrate Material: 0.30 + 0.05 mm phosphor bronze, nickel silver, or other copper based high strength materials.Plating:1.Underplate: Optional. Minimum 1.00 micrometers (40 microinches) nickel. In addition,manufacturer may use a copper underplate beneath the nickel.2.Outside: Minimum 2.5 micrometers (100 microinches) bright tin or bright tin-lead.“mini-B”6.5.3.2.2 SeriesSubstrate Material: 0.3 mm minimum phosphor bronze, nickel silver, or other suitable material.The plating information below describes an example of acceptable "mini-B" receptacle plating.Plating:1.Underplate: Optional. Minimum 1.00 micrometers (40 microinches) nickel. In addition, manufacturermay use a copper underplate beneath the nickel.2.Outside: Minimum 2.5 micrometers (100 microinches) bright tin or bright tin-lead.6.5.3.3 Receptacle Contact Materials“A” and Series “B”6.5.3.3.1 SeriesSubstrate Material: 0.30 + 0.05 mm minimum half-hard phosphor bronze or other high strength copper based material.Plating:Contacts are to be selectively plated.A.Option I1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.70 micrometers (28 microinches) palladium.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.B.Option II1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.1032.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.75 micrometers (30 microinches) palladium-nickel.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.C.Option III1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.75 micrometers (30 microinches) gold.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.6.5.3.3.2 Series“mini-B”Substrate Material: 0.2 mm minimum half-hard phosphor bronze or other high strength suitable material.Plating:Contacts are to be selectively plated.The following underplate, mating area, and solder tails options below describe examples of acceptable "mini-B" receptacle contact plating.D.Option I1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.70 micrometers (28 microinches) palladium.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.E.Option II1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.75 micrometers (30 microinches) palladium-nickel.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.F.Option III1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.75 micrometers (30 microinches) gold.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.6.5.4 Series “A” and Series “B” (or “Mini-B”) “B” PlugsElectrical and mechanical interface configuration data for Series "A" and Series “B” (or “mini-B”) "B"plugs are shown in Figure 6-9Figure 6-13 through Figure 6-15 and Figure 6-10.104Universal Serial Bus Specification Revision 2.0Figure 6-9Figure 6-13. USB Series "A" Plug Interface DrawingUniversal Serial Bus Specification Revision 2.0Universal Serial Bus Specification Revision 2.0Low-speed captive cable assemblies must meet the following electrical requirements:•The cable must be terminated on one end with an overmolded Series “A” plug and the opposite end is vendor specific. If the vendor specific interconnect is to be hot plugged, it must meet the sameperformance requirements as the USB “B” connector.•Low-speed drivers are characterized for operation over a range of capacitive loads. This value includes all sources of capacitance on the D+ and D-lines, not just the cable. Cable selection mustinsure that total load capacitance falls between specified minimum and maximum values. If thedesired implementation does not meet the minimum requirement, additional capacitance needs to beadded to the device. Refer to Section 7.1.1.2 for details.•The maximum low-speed cable length is determined by the rise and fall times of low-speed signaling.This forces low-speed cable to be significantly shorter than high-/full-speed. Refer to Section 7.1.1.2 for details.•Differences in propagation delay between the two signal conductors must be minimized. Refer to Section 7.1.3 for details.•The GND lead provides a common reference between the upstream and downstream ports. The maximum cable length is determined by the voltage drop across the GND lead. Refer to Section 7.2.2 for details. The minimum wire gauge is calculated using the worst case current consumption.•The V BUS lead provides power to the connected device. The minimum wire gauge is vendor specific.6.4.4 Prohibited Cable AssembliesUSB is optimized for ease of use. The expectation is that if the device can be plugged in, it will work.By specification, the only conditions that prevent a USB device from being successfully utilized arelack of power, lack of bandwidth, and excessive topology depth. These conditions are well understood by the system software.Prohibited cable assemblies may work in some situations, but they cannot be guaranteed to work in all instances.•Extension cable assemblyA cable assembly that provides a Series “A” plug with a series “A” receptacle or a Series “B” plugwith a Series “B” receptacle or a Series “mini-B” plug with a Series “mini-B” receptacle. Thisallows multiple cable segments to be connected together, possibly exceeding the maximumpermissible cable length.•Cable assembly that violates USB topology rulesA cable assembly with both ends terminated in either Series “A” plugs or Series “B” (or “mini-B”) “B” receptacles. This allows two downstream ports to be directly connected.Note: This prohibition does not prevent using a USB device to provide a bridge between two USBbuses.•Standard detachable cables for low-speed devicesLow-speed devices are prohibited from using standard detachable cables. A standard detachablecable assembly must be high-/full-speed. Since a standard detachable cable assembly is high-/full-speed rated, using a long high-/full-speed cable exceeds the capacitive load of low-speed.6.5.4.1 Plug Injection Molded Thermoplastic Insulator MaterialMinimum UL 94-V0 rated, thirty percent (30%) glass-filled polybutylene terephthalate (PBT) orpolyethylene terephthalate (PET) or better.Typical Colors: Black, gray, and natural. The “mini-B” plug insulator must be black in color.Flammability Characteristics: UL 94-V0 rated.Flame Retardant Package must meet or exceed the requirements for UL, CSA, and VDE.Oxygen Index (LOI): 21%. ASTM D 2863.6.5.4.2 Plug Shell Materials“A” and Series “B”6.5.4.2.1 SeriesSubstrate Material: 0.30 + 0.05 mm phosphor bronze, nickel silver, or other suitable material.Plating:A.Underplate: Optional. Minimum 1.00 micrometers (40 microinches) nickel. In addition,manufacturer may use a copper underplate beneath the nickel.B.Outside: Minimum 2.5 micrometers (100 microinches) bright tin or bright tin-lead.“mini-B”6.5.4.2.2 SeriesSubstrate Material: 0.2 mm minimum phosphor bronze, nickel silver, or other suitable material.The information below describes an example of acceptable "mini-B" plug plating.Plating:1.Underplate: Optional. Minimum 1.00 micrometers (40 microinches) nickel. In addition,manufacturer may use a copper underplate beneath the nickel.2.Outside: Minimum 2.5 micrometers (100 microinches) bright tin or bright tin-lead.6.5.4.3 Plug (Male) Contact Materials“A” and Series “B”6.5.4.3.1 SeriesSubstrate Material: 0.30 + 0.05 mm half-hard phosphor bronze.Plating:Contacts are to be selectively plated.A.Option I1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.70 micrometers (28 microinches) palladium.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.B.Option IIUniversal Serial Bus Specification Revision 2.01.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.75 micrometers (30 microinches) palladium-nickel.3.Wire Crimp/Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead overthe underplate.C.Option III1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.75 micrometers (30 microinches) gold.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.“mini-B”6.5.4.3.2 SeriesSubstrate Material: 0.2 mm minimum half-hard phosphor bronze or other suitable material.Plating:Contacts are to be selectively plated.The underplate, mating area, and solder tails options below describe examples of acceptable "mini-B" plug contact plating.D.Option I1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.70 micrometers (28 microinches) palladium.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.E.Option II1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.05 micrometers (2 microinches) gold over a minimum of0.75 micrometers (30 microinches) palladium-nickel.3.Wire Crimp/Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead overthe underplate.F.Option III1.Underplate: Minimum 1.25 micrometers (50 microinches) nickel. Copper over base materialis optional.2.Mating Area: Minimum 0.75 micrometers (30 microinches) gold.3.Solder Tails: Minimum 3.8 micrometers (150 microinches) bright tin-lead over theunderplate.Universal Serial Bus Specification Revision 2.06.6 Cable Mechanical Configuration and Materi al RequirementsHigh-/full-speed and low-speed cables differ in data conductor arrangement and shielding. Low-speed recommends, but does not require, use of a cable with twisted data conductors. Low speed recommends, but does not require, use of a cable with a braided outer shield. Figure 6-11Figure 6-16 shows the typical high-/full-speed cable construction.Figure 6-11Figure 6-16. Typical High-/full-speed Cable Construction6.6.1 DescriptionHigh-/full-speed cable consists of one 28 to 20 AWG non-twisted power pair and one 28 AWG twisted data pair with an aluminum metallized polyester inner shield, 28 AWG stranded tinned copper drain wire,> 65% tinned copper wire interwoven (braided) outer shield, and PVC outer jacket.Low-speed cable consists of one 28 to 20 AWG non-twisted power pair and one 28 AWG data pair (a twist is recommended) with an aluminum metallized polyester inner shield, 28 AWG stranded tinned copper drain wire and PVC outer jacket. A > 65% tinned copper wire interwoven (braided) outer shield isrecommended.Universal Serial Bus Specification Revision 2.06.6.2 ConstructionRaw materials used in the fabrication of this cable must be of such quality that the fabricated cable is capable of meeting or exceeding the mechanical and electrical performance criteria of the most current USB Specification revision and all applicable domestic and international safety/testing agencyrequirements; e.g., UL, CSA, BSA, NEC, etc., for electronic signaling and power distribution cables in its category.Table 6-32. Power PairAmerican Wire Gauge (AWG)Nominal ConductorOuter DiameterStranded TinnedConductors280.381 mm (0.015”)0.406 mm (0.016”)7 x 36 19 x 40260.483 mm (0.019”)0.508 mm (0.020”)7 x 34 19 x 38240.610 mm (0.024”)0.610 mm (0.024”)7 x 32 19 x 36220.762 mm (0.030”)0.787 mm (0.031”)7 x 30 19 x 34200.890 mm (0.035”)0.931 mm (0.037”)7 x 28 19 x 32Note: Minimum conductor construction must be stranded tinned copper.Non-Twisted Power Pair:A.Wire Gauge: Minimum 28 AWG or as specified by the user contingent upon the specified cablelength. Refer to Table 6-3Table 6-2.B.Wire Insulation: Semirigid polyvinyl chloride (PVC).1.Nominal Insulation Wall Thickness: 0.25 mm (0.010”)2.Typical Power (V BUS) Conductor: Red Insulation3.Typical Ground Conductor: Black InsulationSignal Pair:A.Wire Gauge: 28 AWG minimum. Refer to Table 6-4Table 6-3.。

SuperSpeed_Inter-Chip_Supplement_release_draft_1_02__19May2014