一类基于FPGA的m序列发生器的设计

两种利用FPGA产生m序列的算法分析

序 会 在 初 始 时 刻 自 动 进 行 一 次 复 位 操 作 ,将 系 统 初

59

列,由图 1 可以看出,两种算法所产生的 m 序列波形相

同,且在短时间内可视为随机序列。经过检测,确定两

Abstract:In order to produce m sequence with high performance and resource⁃saving,two algorithms based on FPGA,which

respectively named as Logic Description and IP Core Transfer,are provided,and the implementation steps of the two algorithms

自带 100 MHz 内部晶振,最高可以提供高达 300 MHz 的

运算速度。

收稿日期:2Biblioteka 13⁃11⁃19逻辑法Verilog HDL 为 IEEE 确 认 的 标 准 硬 件 描 述 语 言 。

逻辑法采用 Verilog HDL 语言,在逻辑层面对移位寄存

器 的 功 能 进 行 行 为 描 述 ,并 通 过 ISE 编 程 软 件 进 行

0

引

1

言

m 序列的实现算法

下 面 以 特 征 方 程 为 f (x) = 1 + x2 + x3 + x4 + x8 的 m 序

伪随机序列作为一种信号形式,具有良好的相关特

性和伪随机性,可应用于扩频通信和信号加密等领域。

列为例,分别介绍两种算法。

根据应用场合的不同,可以将伪随机序列设计成具有不

基于FPGA的m序列发生器的设计

的周期最长的一种基本序 列。本文首先分析m序列 的基本原 理 、结构 、性质 ,然 后实现了1 位m序列 的仿真 以 5 及硬件 实现 ,最终用示波器 观察 波形。实验表 明 ,使 用该方法实现 的m 序列发生器 , 结构简单, 快, 用范 速度 适

围广。

关键词 :m序列 ;伪随机码 ;F GA P

号 , 还可用作噪声源及在保密通 信中起加密作用等 。伪噪声

发生器在 测距 、通信 等领域的应用 日益受 到人 们重视 。有

灵活性 , 且由于 F G 并 P A便于实现大规模的数字系统 , 中 其

中 图 分 类 号 : N9 5 . T 2 +9 文献标识码 : A

D e i f di t lt a m it r ba e sgn o gia r ns t e s d on FPG A

G oL i h nZ i a g a e,C e hq n ,W uLh i P  ̄i g i iu , uNa a n ( n tue f i a Ca tr g&P o e igT c n lg , a ie i f hn , a u n0 0 5 , hn ) Istt g l p i i oSn u n r c sn eh oo yNo hUnv r t o ia i a ,3 0 C ia s sy C T y 1

2 " 年 8月 o 第 8期

电 子

测

试

ELECTR0N I C T ES T

Aug. 2011 N o. 口

基于F G P A的m序列 发生器 的设 计★

高磊 ,陈志强 ,吴黎 慧 ,蒲南江 ( 中北大 学信息探测 与处理技术研究所 ,山西 太原 0 0 5 ) 3 0 1 摘要 :随机码越来越受 到人 们的重视 ,被广泛应用于导弹 、卫 星、飞船轨道 测量和 跟踪 、雷达 、导航 、移动通 信 、保密通 信和通 信系统性能的测量 以及 数字信息处理系统 中。1序 列是 伪随机码 中,带线性反馈移位寄存器 T I

基于FPGA的M序列的设计与实现

0 引言

扩频 通信 系统 与传统 通信 系统 的区别 在 于其

利 用伪 随机序 列来 实现 扩频 与解 扩步 骤 。而伪 随 机 序列 作为扩 频通 信系 统 的关 键 ,将 直接 影 响到

系统 的性 能 。

实 现 同步 与 捕获 等 都 与 扩频 码 的设 计 密 切相 关 。

自相关 函数 .即 :

6 电 子元 器 件 主 用 20. 4 079

. dan e c c c

维普资讯

第9 卷

期 2 7第月 0年 9 0 9

莲钎渗

V1 N. o o . 9 9

S . 2 07 ep 0

f l

当r 0 =

香农在 证 明编码 定理 的时候 ,也 提 出 了使 用具 有 白噪声 统计特性 的信号 来编码 。

通 常采 用 的 二 电平 ( ,1 0 )伪 随 机 序列 的结 构 已预先 确定 ,但 它们 都具 有类 似 白噪声 的相 关 特性 ,只是 幅度概 率分 布不 再服 从高 斯分 布 。伪

22 基 于 V D 语 言 的 F G . H L P A实 现

FG P A器 件 具 有 集 成 度 高 、编 程 灵 活 、阵 列 引脚 数 多 、功 耗 低 、设 计 编程 速 度 快 等 特 点 [ 4 1 。 Q ats1 . A tr 司第 五 代 可 编 程 逻 辑 器 u r 0是 l a公 u I5 e 件 的集 成开 发 环 境 。该 软件 可 提供 从 设 计 输入 、 设计 编译 、功能 仿 真 、设 计处 理 、时 序仿 真 到器

尺 小 于C,二 是 编 码 的 码 长 周 期 足 够 长 。 同 时 ,

以确保 抗 侦破 、抗 干扰 的要求 。

基于 FPGA 一种真随机数生成器的设计和实现

基于 FPGA 一种真随机数生成器的设计和实现吴飞;李艳萍【摘要】Aiming at the application of random number in secure communication , we design and implement a new FPGA-based true random number generator ( TRNG) in this paper .It takes the metastability of RS flip-flop as the random source to reduce the phase shift of clock signal and minimises the process differences of internal components so as to guarantee the randomness of output sequence .The outputs of multi-triggers are conducted the XOR operations and are added the post-processing module for enhancing the quality of random sequences and increasing the entropy per bit .This design has been implemented on Xilinx Spartan 3 XC3S400 platform, the random sequence generated can pass the NIST test , and all the indexes meet the design requirements .The true random number generator consists of common logic unites only, it can be quickly transplanted into ASIC design and shorten the development cycle .%针对随机数在保密通信中的应用,设计并实现一种基于FPGA的真随机数生成器,将RS触发器的亚稳态作为随机源,减小时钟信号的相位偏移,最小化内部元件的工艺差异,从而保证输出序列的随机性,对多个触发器的输出进行异或操作并且加入后处理模块来提高随机序列的质量和增加每比特的熵。

基于FPGA的m序列信号发生器设计

基于FPGA的m序列信号发生器设计摘要:m序列是一种伪随机序列(PN码),广泛用于数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域。

基于FPGA与Verilog硬件描述语言设计井实现了一种数据率按步进可调、低数据误码率、反馈多项式为的m序列信号发生器。

系统时钟为20MHz,m序列信号发生器输出的数据率为20~100 kbps,通过2个按键实现20 kbps步进可调与系统复位,输出误码率小于1%。

m序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种伪随机序列。

是由移位寄存器、反馈抽头及模2加法器组成。

m序列一旦反馈多项式及移位寄存器初值给定,则就是可以预先确定并且可以重复实现的序列,该特点使得m序列在数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域使用广泛。

因此,深入学习研究m序列具有重要的实际意义。

1 m序列信号发生器的组成基于FPGA的m序列信号发生器硬件结构极其简单,仅需两个独立按键(一个是复位按键与另一个控制数据率切换按键)、一个48 MHz 的用于提供系统时钟有源晶振、系统电源、一块配置芯片、几个简单的电阻与电容即可实现。

按键去抖动、按键复位、按键切换数据率、时钟分频等功能均在FPGA内部编程实现。

2 m序列信号发生器的关键设计本文中m序列信号发生器的反馈多项式为。

其反馈及移位寄存器的关系图如图2所示。

从本设计中的反馈及移位寄存器的关系图可以看出,一个时钟周期,移位寄存器右移一位,最高位输入为x0、x2、x3、x4及x8的异或(模2相加)。

m序列的输出是移位寄存器的最低位。

图2所示的关系是m序列呈现为随机性、周期性的根本原因。

为了满足信号发生器输出数据率20 kbps的步进通过按键可调,则生成按步进20 kbps可调的时钟是实现该功能的关键。

当按键发生,时钟的输出频率加20 kbps。

在实际电路中,按键会有很大抖动,对系统会造成很大的不稳定性,因此,必须想办法减小这样的不利影响。

基于FPGA的M序列的设计与实现_冀勇钢

参考文献

ቤተ መጻሕፍቲ ባይዱ

[1] Application Using the TMS320C6000 Enhanced DMA . TI,2001.

66

2007.9 www.ecda.cn

!!!!!!!!!!!!!"

!!!!!!!!!!!!!!!!!!!!"

[2] TMS320C6000 Optimizing Compiler User’s Guide .TI , 2001.

0 引言

扩频通信系统与传统通信系统的区别在于其 利用伪随机序列来实现扩频与解扩步骤。而伪随 机序列作为扩频通信系统的关键, 将直接影响到 系统的性能。

信息论的奠基人香农提出的编码定理指出: 只要信息速率Rb小于信道容量C, 那么, 就总 可 以找到某种编码方法, 在码周期相当长的条件 下, 几乎无差错的从受到高斯噪声干扰的信号中 复制出原来发送的信息。这里有两个条件: 一是 Rb小 于C, 二 是 编 码 的 码 长 周 期 足 够 长 。 同 时 , 香农在证明编码定理的时候, 也提出了使用具有 白噪声统计特性的信号来编码。

[3] 江 思 敏 、刘 畅.TMS320C6000DSP应 用 开 发 教 程[M].北 京: 机械工业出版社, 2005.

!!!!!!!!!!!!!!!!!!!!"

本刊启事

为适应我国信息化建设, 扩大本刊及作 者知识信息交流渠道, 本刊已被CNKI中国期 刊全文数据库网络出版, 其作者著作权使用 费与本刊发表费用一次性处理。如作者不同 意文章被收录, 请在来稿时向本刊声明, 本 刊将做适当处理。

行仿真, 本例程在QuartusII下得到的寄存器传输 级电路图和仿真波形如图5所示。

3 结束语

基于FPGA可配置m序列发生器的设计与实现

基于FPGA可配置m序列发生器的设计与实现作者:晏浩文陈伟吴琼黄庆超刘建国祝宁华来源:《现代电子技术》2018年第08期摘要:针对某些设计场合对可变m序列的需求,提出并验证了一种基于FPGA的m序列发生器方案。

该方案采用线性反馈移位寄存器的结构,可通过外设对发生器的初始状态进行配置来改变所产生的m序列。

使用ModelSim仿真软件对此设计进行了仿真,并将该m序列发生器应用于某光跳频保密通信系统中完成了实验验证。

结果表明,使用该方案实现的m序列发生器结构简单、易于集成,可产生大量不同的m序列,且具有可动态配置的特点。

关键词: FPGA; m序列;信号发生器;移位寄存器; ModelSim仿真软件;光跳频通信系统中图分类号: TN911⁃34; TN918 文献标识码: A 文章编号: 1004⁃373X(2018)08⁃0001⁃04Abstract: In allusion to the demand of variable m⁃sequence in some design occasions, anm⁃sequence generator scheme based on FPGA is proposed and verified. In the scheme, the linear feedback shift register structure is adopted, and the generated m⁃sequence can be changed by using peripherals to configure the initial state of the generator. The Modelsim simulation software is used to perform simulation for the design, and the m⁃sequence generator is applied to a certain optical frequency hopping secure communication system to accomplish the experimental verification. The results show that the m⁃sequence generator realized by this scheme has simple structure, is easy to be integrated, can produce a large number of different m⁃sequences, and has the characteristic of dynamic configuration.Keywords: FPGA; m⁃sequence; signal generator; shift register; ModelSim simulation software; optical frequency hopping communication systemm序列作为伪随机序列[1]的一种,具有优良的伪随机序列性质,在雷达[2]、导航[3]、常规通信[4⁃5]、保密通信[6]、地球物理勘察[7]和电子对抗[8]等领域中都有着广泛的应用。

基于FPGA的简易m序列信号发生器

基于FPGA的简易m序列信号发生器【摘要】本系统基于FPGA为控制核心,采用EXCD-XC3S500E开发板及模拟电路,完成了简易数字m序列信号发生器的设计,实现对数字m序列信号的生成与发送。

【关键词】FPGA;m序列信号;曼彻斯特编码1.方案论证与比较数字信号为m序列,m序列发生器是一种反馈移位型结构的电路,它由n 位移位寄存器加异或反馈网络组成,反馈多项式为本原多项式。

实现移位寄存器的长与反馈式的编程选择,即可实现对m序列的控制。

m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1 。

序列信号发生器一般有两种结构形式:一种是反馈移位型,另一种是计数型。

方案一:反馈移位型序列信号发生器反馈移位型序列码发生器的结构框图如图1所示,它由移位寄存器和组合反馈网络组成,从移存器的某一输出端可以得到周期性的序列码。

方案二:计数型序列码发生器计数型序列码发生器结构框图如图2所示。

它由计数器和组合输出网络两部分组成,序列码从组合输出网络输出。

综合比较,本次设计时由于已知数字信号和伪随机信号各自的f(x)表达式,故采用方案一,采用VHDL硬件描述语言,在XILINX的开发板上编程实现产生所要求的数字信号。

2.系统设计数字信号V为f(x)=1+x +x +x +x 的m序列,采用线性移位寄存器发生器产生数字信号和对应的时钟信号,要求数据率10~100kbps,步进值10kbps,其误差绝对值不大于1%,输出信号为TTL电平。

m序列数字信号是基于FPGA的存储器结构,采用线性移位寄存器发生器产生m序列的本原多项式,并且可以对任意级数的m序列发生器采用VHDL语言进行编写。

其产生原理是m序列信号发生器是在n级线性移位寄存器的基础上可以产生多个m序列,而每一个m序列有对应着一个确定的反馈函数,m序列线性移位寄存器在逻辑上仅可用加法器实现。

其反馈函数:本原多项式f1(x)=1+x +x +x +xm序列的移位寄存器逻辑反馈:f1(x)=x(8)⊕x(4)⊕x(3)⊕x(2)反馈移位寄存器的逻辑功能图如图3所示。

一类基于FPGA的m序列发生器的设计

[收稿日期]20060525 [作者简介]邹学玉(1965),男,1988年大学毕业,副教授,博士生,现主要从事现代通信理论与技术、网络通信新技术方面的教学与研究工作。

一类基于FPGA 的m 序列发生器的设计 邹学玉,易国华 (长江大学电子信息学院,湖北荆州434023)[摘要]基于FP GA 的存储器结构,设计了产生m 序列的本原多项式的存储格式及其查询算法,并且提出了对任意级数n 的m 序列发生器的产生方法。

试验表明,使用该方法实现的m 序列发生器,结构简单,速度快,适用范围广。

[关键词]m 序列;信号发生器;FP GA[中图分类号]TP312;TN91414[文献标识码]A [文章编号]16731409(2006)03008403m 序列是伪随机序列[1~3]的一种,结构简单,实现方便。

在现代工程实践中,m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如,在连续波雷达中可用作测距信号,在遥控系统中可用作遥控信号,在多址通信中可用作地址信号,在数字通信中可用作群同步信号,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

有关产生m 序列发生器的方法很多。

其中,用通用数字器件构成[4]的特点是速度可以很快,但硬件电路不便修改特性,只能产生单一n 级m 序列;用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数n 的本原多项式系数,从而实现m 序列的产生,但速度受到单片机工作速度的限制[5]。

而FP GA 具有硬件电路实现的优点,又具有设计上的灵活性,并且由于FP GA 便于实现大规模的数字系统,其中内嵌了一定数量的E 2PROM 。

为此,笔者将m 序列的本原多项式系数以表格的形式存储于FP GA 的E 2PROM 中,根据级数n 来查询本原多项式系数表,以得到其相应的本原多项式系数,由此设计出m 序列发生器。

1 基于FPGA 的m 序列产生原理m 序列信号发生器是在n 级线性移位寄存器[2]的基础上,加上反馈逻辑电路构成的。

基于FPGA的m序列发生器

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

(3)VHDL与CPLD实现由于CPLD的高集成度,而且VHDL语言编程较为方便,故可以大大减少电路的装调的困难。

文章提出VHDL语言实现,,l序列电路是周期、初相位可编程变化的,其应用较为灵活,通过微处理器对其进行适当的初始化,即可产生用户所需周期、初相位的m序列输出。

用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数 n 的本原多项式系数 ,从而实现 m 序列的产生 , 但速度受到单片机工作速度的限制。

而 FPGA 具有硬件电路实现的优点 , 又具有设计上的灵活性 , 并且由于FPGA 便于实现大规模的数字系统。

1.1 理论基础m 序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种序列。

基于FPGA的VHDL语言m序列生成详解+源码

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心局部,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元构造如下:如上图,假设N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进展直通反应,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反应〔B(N)为1时反应〕;C〔N〕为本级反应;C〔N-1〕为下一级反应。

具体原理参看m序列组成构造。

此外,本程序还参加了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形根本一致,只是它与CP进展了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以到达为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

〔注意:STA要采用自锁定开关,高电平有效〕三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一〔注意:按键建议采用自弹跳按键,如过需要软件去除按键震颤的话,我再做发给你〕,没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

fpga实验m系列 实验报告

实验报告课程名称:FPGA设计实验实验项目:m序列产生器实验时间:2013 .4. 8实验班级:xx电本总份数:一份指导教师:xxxxxx电信学院工业中心实验室二〇一三年四月八日广东技术师范学院实验报告学院:电信学院专业:电子信息工程班级:xxx 成绩:姓名:xxx 学号:xxxxxxxxx 组别:组员:实验地点:工业中心实验日期:2013.4.8 指导教师签名:实验一项目名称:m序列产生器一、实验目的:学习应用移位寄存器理论实现基于FPGA的伪随机序列发生器的方法,明白m序列本原多项式与m序列移位寄存器反馈多项式之间的关系。

分别采用SSRG和MSRG结构的m序列产生器电路,并以QuartusⅡ软件为开发平台的m序列的仿真波形。

二、实验主要仪器设备:QuartusⅡ软件为开发平台三、.实验原理:m序列又称为最长线性反馈移位寄存器序列,该序列具有很好的相关性能,所以在直接序列抗频中应用广泛。

m序列的产生比较简单,可以利用r级移位寄存器产生长度为2^r-1的m序列。

m序列产生器的结构主要分为两类,一类被称为简单型码序列发生器(SSRG),另一类被称为模块型码序列发生器(MSRG)。

r级移位寄存器的反馈路径由m序列的特征多项式决定:(1)对于SSRG结构,m序列特征多项式的一般表达式为:f(X)=CrX^r+Cr-1X^(r-i)+……+C3X^3+C2X^2+C1X^1+C0X^0 (2)对于MSRG结构,m序列特征多项式的一般表达式为:f(X)=D0X^r+d1x^r-1+……+Dr-3X^3+Dr-2X^2+Dr-1X^1+DrX^0 可以看出,SSRG结构的特征多项式系数Cr,Cr-1,…C0)与MSRG结构特征多项式系数(D0,的,…Dr)之间的对应关系为:Ci=Dr-i, 其中,i=0.1.2…..r四、实验内容和步骤:(1)采用SSRG结构实现的m序列产生器图8.2是采用SSRG结构的m序列产生器电路。

基于FPGA可配置m序列发生器的设计与实现

现代电子技术Modern Electronics Technique2018年4月15日第41卷第8期Apr.2018Vol.41No.8DOI :10.16652/j.issn.1004⁃373x.2018.08.001m 序列作为伪随机序列[1]的一种,具有优良的伪随机序列性质,在雷达[2]、导航[3]、常规通信[4⁃5]、保密通信[6]、地球物理勘察[7]和电子对抗[8]等领域中都有着广泛的应用。

有关产生m 序列发生器的方案很多。

其中,基于专用集成电路的m 序列发生器,其发生速率可以很快,但由于硬件电路不便修改的特性,只能产生单一的m 序列;基于软件的m 序列发生器[9]采用灵活的数据查询方式可以获得任意的m 序列,因而得到了大量的关注和研究,但其产生速率不及硬件实现方式且实现过程较为复杂,故而在许多高速设计场合往往使用更为简单的FPGA 实现方式。

FPGA 即现场可编程门阵列,使用FPGA 来实现设计,既具有硬件电路实现的优点,又具有设计上的灵活性。

本文提出了一种基于FPGA 的m 序列发生器,具有初始状态可配置的特点,可以通过配置线性反馈移位寄存器的初始值来改变产生的m 序列,并给出了一个在保密通信系统中的应用实例,对工程应用有一定的现实意义。

1m 序列发生器的设计原理传统的m 序列发生器有Fabonacci 和Galois 两种类型[10],其中前者是在n 级线性移位寄存器的基础上,加上反馈回路构成的,结构简单,易于实现,具体结构如图1所示。

图1中的c i 是反馈系数,由本原多项式系数确定,当c i =1时,反馈回路连接,当c i =0时,反馈回路断开。

a i 用于表示各级触发器的状态,a i 只能等于0或1,表示触发器的储值是0还是1。

发生器工作时,产基于FPGA 可配置m 序列发生器的设计与实现晏浩文1,2,陈伟1,吴琼1,黄庆超1,刘建国1,祝宁华1(1.中国科学院半导体研究所,北京100083;2.中国科学院大学,北京100049)摘要:针对某些设计场合对可变m 序列的需求,提出并验证了一种基于FPGA 的m 序列发生器方案。

一类基于FPGA的m序列发生器的设计

1 基于 F G P A的 m 序列产生原理

m 序列 信号 发生 器是 在 级线 性移 位 寄存 器L 的基础 上 ,加上 反 馈逻 辑 电路构 成 的 。m序 列信 号发 2 生 器有 2种结 构 :F b n ci 和 Gaos ao ac型 li 型 。笔 者采 用 F b n ci a o a c 型移 位 寄 存 器产 生 m 序 列 。该结 构 的特点是 移位 寄存 器 的反馈抽 头 位置 与本 原 多项式 一致 ,序列与 初 始状 态相 对应 ,码 序 列 的产生速 度 主 要 受反馈 网络 的时 延 限制 。 个 元 级 F b n ci 一 a o ac型移 位 寄存器 模 型如 图 1 示 , 者 主要讨 论 一 2时 所 笔

作 噪声 源及 在保 密通 信 中起 加 密作 用等 。伪 噪声 发生 器 在测 距 、通 信 等 领 域 的应 用 日益受 到 人 们重 视 。

有 关产 生 m 序 列 发生器 的 方法 很 多 。其 中,用 通用 数 字 器 件构 成L 的特 点 是 速度 可 以很快 ,但硬 件 电 4 J

an = 一

图 1 P元 n级 F bn c 型线 性 移 位 寄 存 器 模 型 a o ad

∑ , 卜 i

i- 一l

该序 列 的递 推关 系式 为 :

[ 收稿 日期]2 0 0 6—0 5—2 5 [ 作者 简介]邹学玉 (9 5 ) 16 一 ,男,18 年大学毕业 ,副教授 , 98 博士生 ,现主要从事现代通信 理论与技术 、 网络通信新技术方面的教学与 研 究 工作 。

系统 ,其 中内嵌 了一定 数 量的 E P 。ROM。为此 ,笔 者将 m 序列 的本原 多项 式 系数 以表 格 的形 式 存储 于 F GA 的 E P OM 中 ,根 据级 数 来查 询本 原 多项式 系 数表 ,以得 到 其 相 应 的本 原 多项式 系数 ,由此 P 。R

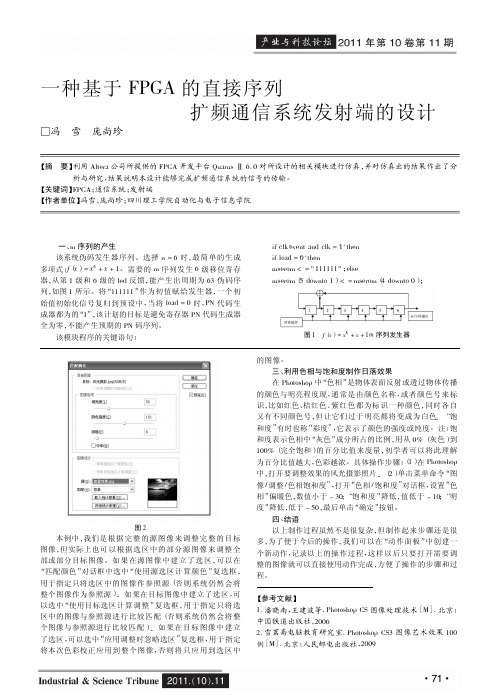

一种基于FPGA的直接序列扩频通信系统发射端的设计

□冯 雪 庞尚珍

【摘 要】利用 Altera 公司所提供的 FPGA 开发平台 Quarus Ⅱ 6. 0 对所设计的相关模块进行仿真,并对仿真出的结果作出了分 析与研究,结果说明本设计能够完成扩频通信系统的信号的传输。

【关键词】FPGA; 通信系统; 发射端 【作者单位】冯雪,庞尚珍; 四川理工学院自动化与电子信息学院

·71·

mserom( 0) < = mserom( 0) xor mserom( 5) ; mout < = mserom( 0) ; end if; end if; 在 QuartusII6. 0 软件进行编译,生成的波形图如图 2 所示:

否得到正确的恢复。这就防止了“倒”方式,发生在 2PSK 接 收端接收到正确的信息差异。2PSK 转变必须先确定二进制 输入参考基准相位。

图2

本例中,我们是 根 据 完 整 的 源 图 像 来 调 整 完 整 的 目 标 图像,但实际上 也 可 以 根 据 选 区 中 的 部 分 源 图 像 来 调 整 全 部或部分目标 图 像 。 如 果 在 源 图 像 中 建 立 了 选 区 ,可 以 在 “匹 配 颜 色 ”对 话 框 中 选 中“使 用 源 选 区 计 算 颜 色 ”复 选 框 , 用于指定只将选区中的图像作参照源( 否则系统仍然会将 整个图像作为参照源) 。如果在目标图像中建立了选区,可 以选中“使用目标 选 区 计 算 调 整 ”复 选 框 ,用 于 指 定 只 将 选 区中的图像与参照源进行比较匹配( 否则系统仍然会将整 个图像与参照源进行比较匹配) 。如果在目标图像中建立 了选区,可以选中“应用调整时忽略选区”复选框,用于指定 将本次色彩校 正 应 用 到 整 个 图 像 ,否 则 将 只 应 用 到 选 区 中

基于FPGA的m序列发生器要点

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

(3)VHDL与CPLD实现由于CPLD的高集成度,而且VHDL语言编程较为方便,故可以大大减少电路的装调的困难。

文章提出VHDL语言实现,,l序列电路是周期、初相位可编程变化的,其应用较为灵活,通过微处理器对其进行适当的初始化,即可产生用户所需周期、初相位的m序列输出。

用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数 n 的本原多项式系数 ,从而实现 m 序列的产生 , 但速度受到单片机工作速度的限制。

而 FPGA 具有硬件电路实现的优点 , 又具有设计上的灵活性 , 并且由于FPGA 便于实现大规模的数字系统。

1.1 理论基础m 序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种序列。

M序列发生器的设计与实现毕业论文

1 引言本文的主要内容是移位寄存器74LS194的研究和m序列码发生器的产生原理以及基于MAX+PLUS II、Protel 99SE软件的实现。

m序列码发生器的产生原理和实现是CDMA通信中的核心,具有重要的理论价值和广阔的应用前景。

文中基于对74LS194移位寄存器的研究,对伪随机序列的特性及对m序列发生器的结构进行了分析,运用MAX+PLUS II的模拟仿真和Protel 99SE进行印刷电路板设计,验证其正确性,最终产生m序列码。

1.1 研究此课题的目的伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

这些特性使得伪随机序列得到了广泛的应用。

1.2 伪随机序列的应用和意义1.2.1在通信加密中的应用m序列自相关性较好,容易产生和复制,而且具有伪随机性,利用m序列加密数字信号使加密后的信号在携带原始信息的同时具有伪噪声的特点,以达到在信号传输的过程中隐藏信息的目的;在信号接收端,再次利用m序列加以解密,恢复出原始信号[1]。

1.2.2 在雷达信号设计中的应用近年兴起的扩展频谱雷达所采用的信号是已调制的具有类似噪声性质的伪随机序列,它具有很高的距离分辨力和速度分辨力。

这种雷达的接收机采用相关解调的方式工作,能够在低信噪比的条件下工作,同时具有很强的抗干扰能力。

该型雷达实质上是一种连续波雷达,具有低截获概率性,是一种体制新、性能高、适应现代高技术战争需要的雷达。

采用伪随机序列作为发射信号的雷达系统具有许多突出的优点。

首先,它是一种连续波雷达,可以较好地利用发射机的功率。

其次,它在一定的信噪比时,能够达到很好的测量精度,保证测量的单值性,比单脉冲雷达具有更高的距离分辨力和速度分辨力。

最后,它具有较强的抗干扰能力,敌方要干扰这种宽带雷达信号,将比干扰普通的雷达信号困难得多[2]。

1.2.3 在通信系统中的应用伪随机序列是一种貌似随机,实际上是有规律的周期性二进制序列,具有类似噪声序列的性质,在CDMA中,地址码都是从伪随机序列中选取的,在CDMA中使用一种最易实现的伪随机序列:m序列,利用m序列不同相位来区分不同用户;为了数据安全,在CDMA的寻呼信道和正向业务信道中使用了数据掩码(即数据扰乱)技术,其方法是用长度为2的42次方减1的m序列用于对业务信道进行扰码(注意不是扩频),它在分组交织器输出的调制字符上进行,通过交织器输出字符与长码PN码片的二进制模工相加而完成。

一种新型基于FPGA的伪随机序列发生器设计

一种新型基于FPGA的伪随机序列发生器设计作者:赵怡余稀来源:《电子技术与软件工程》2013年第18期摘要:本文提出了一种具有可调特性的伪随机序列发生器,并使用硬件描述语言Verilog HDL和QuartusⅡ8.0进行描述和仿真电路。

结果表明,该设计在线性反馈移位寄存器基础上,产生的随机序列具有3~16任意级数可调和反馈系数可控的特点。

该设计与其他常见设计相比,具有灵活性好优点,可以广泛用于通信、信息安全等领域。

【关键词】FPGA 伪随机序列线性反馈移位寄存器可调1 引言伪随机序列是一种可以预先确定并可以重复产生和复制,且具有随机统计特性的二进制码序列。

伪随机序列的伪随机性表现在预先的可确定性、可重复产生与处理,虽然不是真正的随机序列,但是当伪随机序列周期足够长时,它便具有随机序列的良好统计特性。

在现代工程实践中,在信息安全、数字网络、移动通信、导航、雷达和保密通信、通信系统性能的测量等领域中有着广泛的应用。

本文设计利用Verilog HDL语言描述电路中各模块。

所设计的伪随机序列发生器具有3~16级的级数可调,且反馈函数中的反馈系数也可控。

相较于其他伪随机序列发生器[4-8],本设计具有级数可调的特性,还具有反馈系数可调的特性。

2 m序列的产生m序列是最别广泛采用的伪随机序列之一,除此之外,还有其他的伪随机序列,如Gold 序列、M序列等,本文设计的伪随机序列发生器是采用m序列设计的。

反馈函数可以写为:(模2加)。

反馈线的连接状态用ci表示,ci=1表示反馈线连通,即有反馈参加;ci=0,则表示此反馈线断开。

反馈线的连接状态的不同,就可能改变此移位寄存器输出序列的周期。

因此, ci的取值决定了移位寄存器的反馈连接和序列的结构。

级数(n)和反馈系数一旦确定,反馈移位寄存器的输出序列就确定了。

反馈移位寄存器的级数不同,m序列的反馈系数也不同。

本文将级数(n)和反馈系数设计成灵活可调的输入,使伪随机序列发生器输出序列可调,增加电路的灵活性。

M序列发生器设计实验指导书

M序列发生器设计实验一、实验原理:M序列码也称伪随机序列码,其主要特点是:(1)每个周期中,“1”码出现2n-1次,“0”码出现2n-1次,即0、1出现概率几乎相等。

(2)序列中连1的数目是n,连0的数目是n-1。

(3)分布无规律,具有与白噪声相似的伪随机特性。

由于具有这些特点,m序列码在通信、雷达、系统可靠性测试等方面获得了广泛地应用。

m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1,只有一个多余状态即全0状态,所以称为最大线性序列码发生器。

由于其结构已定型,且反馈函数和连接形式都有一定的规律,因此利用查表的方式就设计出m 序列码。

列出部分m序列码的反馈函数F和移存器位数n的对应关系。

如果给定一个序列信号长度M,则根据M=2n-1求出n,由n查表便可以得到相应的反馈函数F。

二、基于DSP Builder 的设计M 序列发生器可由线性反馈寄存器(Linear Feedback Shift Registers,LFSR )来产生,如图1所示。

图1 线性反馈移位寄存器的构成其特征多项式可表示为:∑==ni i i x C x F 1)(在图1中涉及的乘法和加法都是指模二运算的乘法和加法,即逻辑与和逻辑或。

要产生最长的线性反馈移位寄存器序列的n 级移位寄存器,其特征多项式必须是n 次本原多项式。

例如n=5,可以生成M 序列的5级LFSR 的特征多项式,即:125++x x ,此式可生成的M 序列的周期为:125-。

下面以M 序列发生器模型125++x x 为例,利用DSP Builder 构建一个伪随机序列发生器。

图2显示了上式的DSP Builder 模型表述,这里采用相连的延时单元级作为移位寄存器,用异或(XOR )完成模二加运算,输出为Output 。

图2 M 序列发生器模型但应注意,图2所示的电路一般无法正常工作。

这是由于在DSP Builder 默认的延时单元在开始工作时,存储内容为0,而对于M 序列来说,起始序列为全0,那么根据多项式,输出序列也将为0.全0序列不是正常的M 序列。

m序列发生器的设计与实现

第1章绪论1.1 课题背景在信息化社会,通信系统担负着信息传输、交换和处理的重要任务。

通信技术的发展代表了一个国家科学技术的发展现状,也成为国家经济发展的一个重要推动力。

扩展频谱通信是通信的一个重要分支和发展方向,它是扩展频谱技术和通信技术相结合的产物。

由于扩展频谱即使具有抗干扰能力强、截获率低、多址能力强、抗多径、保密性好及测距能力强等一系列的优点,使得扩展频谱通信越来越受到人们的重视。

随着大规模或超大规模集成电路技术、微电子技术、为处理技术的迅猛发展以及一些新型器件的广泛应用,扩展频谱通信的发展迈上了一个新的台阶,它不仅在军事通信中占有重要地位,而且正迅速地渗透到民用通信中。

可以毫不夸张地讲,在现代通信系统,特别是无线通信系统,没有扩展频谱技术,这些系统想生存都是比较困难的。

在扩展频谱系统中,伪随机序列起着重要的作用。

在直扩系统中,用伪随机序列将传输信息扩展,在接收时又用它将信息压缩,并使干扰信息功率扩展,提高了系统的抗干扰能力;在跳频系统中,用伪随机序列控制频率合成器产生的频率随机地跳变,躲避干扰;在跳时系统中,用伪随机序列控制脉冲发送的时间和持续时间。

由此可见,伪随机序列性能的好坏,直接关系到整个系统性能的好坏,是一个至关重要的问题。

m序列是最长线性移位寄存器序列,是伪随机序列中最重要的序列中的一种,这种序列易于产生,有优良的自相关特性。

在直扩系统中m序列用于扩展要传递的信号,在跳频系统中m序列用来控制跳频系统的频率合成器,组成随机跳频图案。

电子设计技术由于计算机技术的发展而产生了巨大变化。

本设计是利用电子设计方法,用电路图表示设计思想,用实验电路板搭载实验电路,进行模拟、仿真,用电子测试仪器进行功能、性能测试。

20世纪80年代,计算机辅助设计(CAD)技术开始发展,许多CAD工具软件开始流行。

在信息学科领域也和其他学科一样,计算机辅助设计技术步入了发展轨道。

由于电子科学是计算机科学的基础,计算机学科的发展离不开电子学科的支持,但是计算机科学又反作用于电子科学,加速了电子学科的发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[收稿日期]20060525[作者简介]邹学玉(1965),男,1988年大学毕业,副教授,博士生,现主要从事现代通信理论与技术、网络通信新技术方面的教学与研究工作。

一类基于FPGA 的m 序列发生器的设计邹学玉,易国华(长江大学电子信息学院,湖北荆州434023)[摘要]基于F PGA 的存储器结构,设计了产生m 序列的本原多项式的存储格式及其查询算法,并且提出了对任意级数n 的m 序列发生器的产生方法。

试验表明,使用该方法实现的m 序列发生器,结构简单,速度快,适用范围广。

[关键词]m 序列;信号发生器;F PG A [中图分类号]T P 312;T N 91414[文献标识码]A[文章编号]16731409(2006)03008403m 序列是伪随机序列[1~3]的一种,结构简单,实现方便。

在现代工程实践中,m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如,在连续波雷达中可用作测距信号,在遥控系统中可用作遥控信号,在多址通信中可用作地址信号,在数字通信中可用作群同步信号,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

有关产生m 序列发生器的方法很多。

其中,用通用数字器件构成[4]的特点是速度可以很快,但硬件电路不便修改特性,只能产生单一n 级m 序列;用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数n 的本原多项式系数,从而实现m 序列的产生,但速度受到单片机工作速度的限制[5]。

而FPGA 具有硬件电路实现的优点,又具有设计上的灵活性,并且由于FPGA 便于实现大规模的数字系统,其中内嵌了一定数量的E 2PROM 。

为此,笔者将m 序列的本原多项式系数以表格的形式存储于FPGA 的E 2PROM 中,根据级数n 来查询本原多项式系数表,以得到其相应的本原多项式系数,由此设计出m 序列发生器。

1 基于FPGA 的m 序列产生原理m 序列信号发生器是在n 级线性移位寄存器[2]的基础上,加上反馈逻辑电路构成的。

m 序列信号发生器有2种结构:Fabo nacci 型和Galois 型[2]。

笔者采用Fabonacci 型移位寄存器产生m 序列。

该结构的特点是移位寄存器的反馈抽头位置与本原多项式一致,序列与初始状态相对应,码序列的产生速度主要受反馈网络的时延限制。

一个p 元n 级Fabo nacci 型移位寄存器模型如图1所示,笔者主要讨论p =2时的情形。

图1 p 元n 级Fabonacci 型线性移位寄存器模型图1中,n 个小方框表示n 个寄存器D ,把它们从左至右依次叫做第1级,第2级,,,第n 级寄存器。

对于系数c i ,当c i =1时,表示第i 级输出a i 参与反馈;当c i =0时,表示第i 级输出a i 不参与反馈。

开始时,设第1级的内容为a n -1,第2级的内容为a n -2,,,第n 级的内容为a 0,即n 级移位寄存器的初始状态为(a 0,a 1,,,a n -1)(非0初态)。

则加法器的输出,即反馈到第1级的输入为:a n =-6ni=1c ian -i(1)该序列的递推关系式为:#84#长江大学学报(自科版) 2006年9月第3卷第3期理工卷Journal of Y angtze University (Nat Sci Edit) Sep 12006,Vo l 13N o 13Sci &Eng Va j =-6ni=1c iaj-ij \n (2)即n 级线性移位寄存器序列所对应的反馈逻辑。

另外,图1的2元n 级移位寄存器的联接多项式为:f (x )=1+c 1x +,+c n -1x n -1+c n x n(3)该多项式应为2元有限域GF (2)上的n 次本原多项式,其非0序列周期为2n -1,x 取值为0或1。

图2 本原多项式系数表结构该设计要求级数n 可变,故采用查询本原多项式系数表的方式获取本原多项式的系数特征(c 1,c 2,,,c n )。

其系数表结构如图2所示。

该表由FPGA 中内嵌的E 2PROM 构成,只要给定n,经过级数调整模块运算得到其相应地址ADD _Table,即可从E 2PROM 的输出端OU T _T able 输出其本原多项式的系数。

其中,第0次的系数始终为1,可以不列入系数表中,以节省E 2PROM 的开销。

系数表根据级数n 从小到大依次顺序存储相应级数m 序列本原多项式各次的系数。

若设计级数的最小级数为n s ,最大级数为n e ,则E 2PROM 的地址空间范围为从0至n e -n s 。

图3 任意可变级数n 的m 序列发生器的主要硬件框图2 模块设计该任意可变级数n 的m 序列发生器采用Altera 公司的FPA G 芯片EPF10K10B,其内部包含3个嵌入式阵列块(EAB:embedded ar ray block),每个EAB 提供2048位来构造RAM ,ROM ,FIFO 或双口RAM 等功能,系统的主要硬件框图如图3所示,主要包括输入级数n 调整模块、级数n 显示模块、系数表存储模块、移位存储器模块、反馈网络模块、m 序列输出模块。

所有模块采用VH DL 语言描述。

考虑到EA B 提供存储容量限制,该设计的级数n 的范围为32~63。

其中,/级数n 调整0模块设计成具有可逆计数功能电路,其计数值变化范围为32~63,因此计数器的模为32。

故模块的输出数据宽度为5位。

在3个外输入控制信号中,/加/减(up _dow n)0用来控制级数n 是增加方向;/调整(adjust)0是配合/加/减0使用来调整n 加1或减1;/启动(start)0用来控制级数n 调整后模块的一路输出QB 至/系数表存储器0的地址端ADD _Table 。

另外一路输出QA 送至/级数n 显示0模块实时显示。

其中QA 与QB 的编码完全相同。

表1 QA 的值与n 的对应关系QA n 00000320000133,,1111163由于/级数n 调整0模块输出为5位二进制数据QA,QA 与级数n 的对应关系如表1所示,因此/级数n 显示0模块需将该二进制码译码为供2位数码管显示的7段编码,该编码极性取决于数码管的极性。

/表地址产生器0模块需要将/级数n 调整0模块输出的6位的二进制转换为/系数表存储器0地址空间相一致的编码,即地址线宽度为5位。

/系数表存储器0模块由ROM 构成,因最高级数为63,故系数表输出数据线宽度设为64bit;地址空间为32,故地址线宽度为5位,因此可以直接将计数器的输出到/系数表存储器0的地址线。

该系数表可以用一个EA B 中的2048位的ROM 来实现。

#85#第3卷第3期邹学玉等:一类基于FP GA 的m 序列发生器的设计图4 反馈网络原理图移位存储器模块设计成具有左移功能的n e 级移位存储器,其最低位为a n -1。

反馈网络的设计直接关系到m 序列的产生速度,其原理如图4所示。

其中,系数表存储器中的数据作为反馈网络的控制输入,移位寄存器的数据接至反馈网络的数据输入端。

当c i =0时,q i =0,当c i =1时,q i =a n -i 。

模2加法器的结构由M axplus Ⅱ的进行快速设置后,再进行综合。

经过仿真的定时结果进行分析表明,模2运算的矢量长度增加为10倍时,其增加的时延不到原来的1倍。

3 结 语采用FPGA 实现m 序列时,由于用VH DL 语言描述复杂的数字硬件电路,编程实现简单,也使得基于ROM 表的硬件查询方式可以快速地获得产生任意级数n 的m 序列本原多项式系数,级数切换速度快,并且由此实现的m 序列发生器的速度也更快,因此该m 序列产生方法具有较强的适应性和较广的应用范围。

本文提供的应用实例对速度要求较高,级数n 可变的应用特别适用,并且在伪噪声信号发生器中得到了应用。

由于VH DL 编程具有较好的移植性,因此对发生器要求具有更高产生速度的实际应用,可以根据具体情况选择速度更高的FPGA 芯片,重新对项目进行综合。

[参考文献][1]万哲先1代数和编码[M ]1第2版1北京:科学出版社,19801[2]林可祥,汪一飞1伪随机码的原理与应用[M ]1北京:人民邮电出版社,19981[3]肖国镇,梁传甲,王育民1伪随机序列及其应用[M ]1北京:国防工业出版社,19851[4]张涛1双通道伪随机信号发生器的研究[J]1电子测量与仪器学报,1997,11(2):11~151[5]吴先用,邹学玉1一种m 序列伪码发生器的产生方法[J]1测控技术,2003,22(9):56~591[编辑] 易国华#86# 长江大学学报(自科版)2006年9月LI Ke-ju(Yan gtz e Univ ersity,Jingz h ou434023)Abstract:The issues concerning netw ork safety,national safety and its sig nificance of economic con-struction are analyzed1M easures co ncer ning the netw ork safety strateg y,such as law s,technical m anagement and reso urces are described by analyzing the latest adv ances of netw ork safety technolo-gies and a feasible preventive strategy of com puter safety manag ement is obtained1Key words:netw ork safety;netw or k structure;strategy75Structure and Design of Digital C ampu s Network)))By Taking the C onstruction of Digital Network of Yangtze University for Example TAO Zhou,WANG Yi-ju,H UANG Dong-ping,CHEN Fei(Yang tz e Univ ersity,J ingz hou434023)Abstract:A netw ork infrastructure is very impo rtant fo r dig ital cam pus netwo rk construction1In con-sideration of the pro blems ex isted in its cur rent construction in Yangtze U niv er sity and in co mbinatio n w ith the netw o rk location,o peratio n platfo rm o f the sy stem,manag em ent system and demands o f application,the com po sitio ns of critical subsy stem s and their linking modes are deter mined,and the ov erall structure of digital cam pus netw ork is designed1Key words:digitalized campus netw ork;campus netw or k;netw ork structur e;com bined netw o rk 79Design of A USB FlashDisk Data Acquisition SystemXU Ai-jun,WAN Tia n-jun,LI Jia-xu(Yang tze Unive rsity,J ingz hou434023)Abstract:A mass storage data acquisitio n system is desig ned based on USB H ost device CH375inter-face w ith enhanced micro controller ST C89C51RD1T he system is used to o bser ve USB mass storag e class Bulk-Only and UFI,suppo rt FA T16file system1Lo cal m ass data can be stored in U SB Flash-Disk as soon as possible1Stor ed data can also be read back for display on LCD in tex t o r curve for-mat1Local data acquisition and office data analy sis can be easily conducted for easy data exchanging betw een U SB FlashDisk and computer1Key words:micro controller;USB FlashDisk;data acquisitio n;file system82An Interpolation Method for Improving Stability Precision for Fuzzy C ontrol of Frequ ency Converter Air C onditionerYU Shi-qiu(Yang tze Univ ersity,J ingz hou434023)Abstract:In consideration of the problem s of poor stability pr ecision in conventional fuzzy contro l o f frequency converter air conditio ner,based on the data o f indoo r operation of a frequency converter air conditioner,a basic fuzzy control table is designed,and one dimensional linear interpolatio n is used to calculate the fuzzy contro l output1T est result sho w s that the stability pr ecision o f fuzzy control is improved w ith the m ethod1Key words:frequency conv er ter air co nditioner;fuzzy co ntrol;stability pr ecision;interpolatio n84A Kind of Design of M-sequence Generator Based on FPGAZOU Xue-yu,YI Guo-hua(Yang tz e Unive rsity,J ing z hou434023)Abstract:The primitiv e po lynomial.s non-zero coefficient storage structure and its sear ch algo rithm are designed based on the sto rage structure of Altera.s FPGA chip,a producing metho d of m-se-quence g enerator for arbitrary r ank n is introduced1Test result show s that hardw are structure is sim-ple,the speed of its output is high,and the application o f the method is w idely used for realizing m-sequence;gener ator1Key words:m-sequence;sig nal generator;FPGA##Ⅶ。