Verilog程序设计-四位全加器

4位二进制全加器的设计

4位二进制全加器的设计摘要加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运行速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行加法器的资源占用差距也会越来越大。

我们采用4位二进制并行加法器作为折中选择,所选加法器为4位二进制先行进位的74LS283,它从C0到C4输出的传输延迟很短,只用了几级逻辑来形成和及进位输出,由其构成4位二进制全加器,并用Verilog HDL进行仿真。

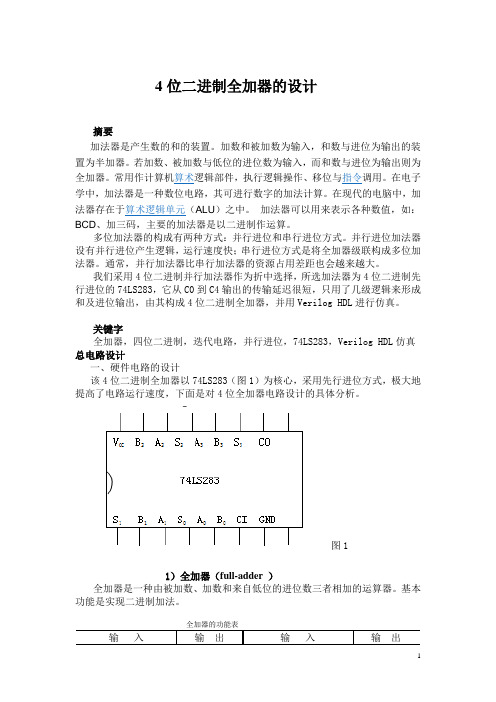

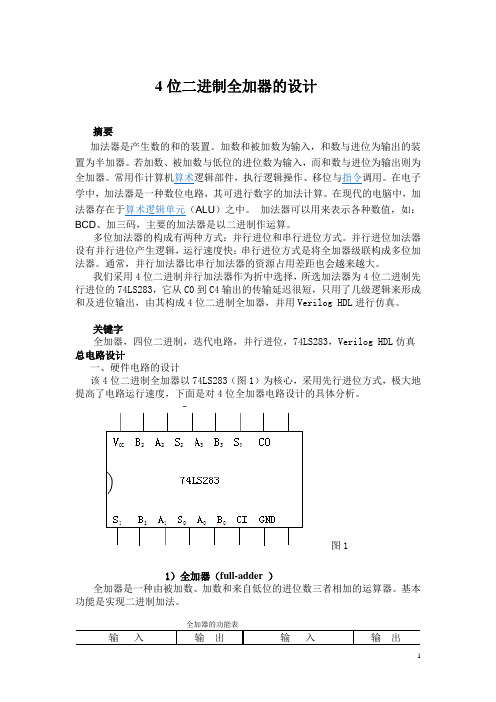

关键字全加器,四位二进制,迭代电路,并行进位,74LS283,Verilog HDL仿真总电路设计一、硬件电路的设计该4位二进制全加器以74LS283(图1)为核心,采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是一种由被加数、加数和来自低位的进位数三者相加的运算器。

基本功能是实现二进制加法。

全加器的功能表输入输出输入输出逻辑表达式:CIB A S ⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()AB CI B A CO ++=其中,如果输入有奇数个1,则S 为1;如果输入有2个或2个以上的1,则CO=1。

实现全加器等式的门级电路图如图2所示,逻辑符号如图3所示.图2 图32)四位二级制加法器 a) 串行进位加法器四位二进制加法器为4个全加器的级联,每个处理一位。

verilog的15个经典设计实例

begin b=a; c=b; end endmodule

【例 5.11】模为 60 的 BCD 码加法计数器

module count60(qout,cout,data,load,cin,reset,clk);

【例 5.6】用 fork-join 并行块产生信号波形

`timescale 10ns/1ns module wave2; reg wave; parameter cycle=5; initial

fork wave=0;

#(cycle) wave=1; #(2*cycle) wave=0; #(3*cycle) wave=1; #(4*cycle) wave=0; #(5*cycle) wave=1; #(6*cycle) $finish; join initial $monitor($time,,,"wave=%b",wave); endmodule

else

out<=out+1;

end

endmodule

//同步复位 //计数

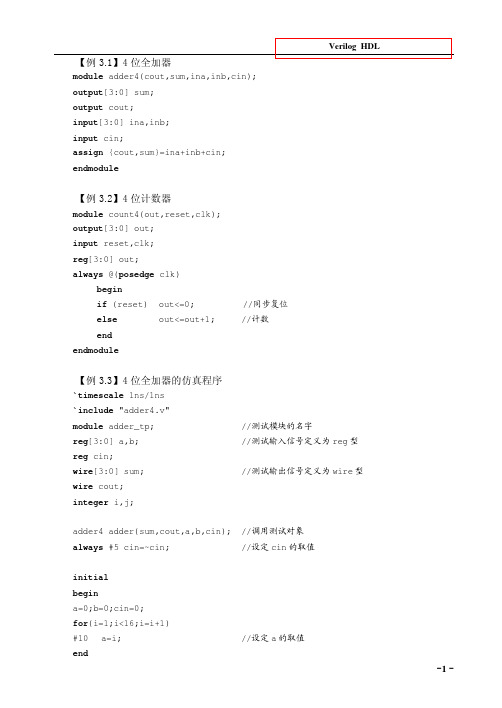

【例 3.3】4 位全加器的仿真程序

`timescale 1ns/1ns `include "adder4.v" module adder_tp; reg[3:0] a,b; reg cin; wire[3:0] sum; wire cout; integer i,j;

output[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

四位全加器实验Verilog

实验四四位全加器一、实验目的l. 用组合电路设计4位全加器。

2.了解Verilog HDL语言的行为描述的优点。

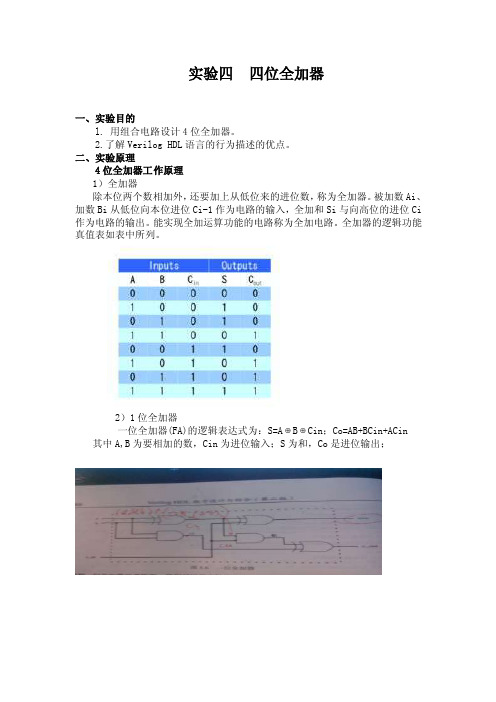

二、实验原理4位全加器工作原理1)全加器除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

被加数Ai、加数Bi从低位向本位进位Ci-1作为电路的输入,全加和Si与向高位的进位Ci 作为电路的输出。

能实现全加运算功能的电路称为全加电路。

全加器的逻辑功能真值表如表中所列。

2)1位全加器一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin;Co=AB+BCin+ACin 其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;这两幅图略微有差别,但最后的结果是一样的。

3)4位全加器4位全加器可看作4个1位全加器串行构成, 具体连接方法如下图所示:采用Verilog HDL语言设计该4位全加器,通过主模块调用子模块(1位全加器)的方法来实现。

三、实验步骤四、实验连线K1-K4:14-11K5-K8:18-15L5-L8:7-10VIJN:83L4:64KHZ:80五、心得体会首先,实现这一段全加器代码并不难,但是由于困惑给的三个时钟输入,没有太懂意思,所以只写了全加器控制LED灯的代码;后来问清楚后,运行全加器代码,有错误,原来是建文件时用的是verilog hdl,我建的是其他类型的;后来还有错,原来是把冒号打成分号;编译成功后,LED不亮,后来发现是硬件老化,换了箱子。

这一部分做好后,我准备把控制声音的加上去,本来准备再加一个模块,可是不能有两个顶层块,就对主模块做了补充,用case命令调用不同的状态,因为时间紧迫,所以代码写得比较简单,没有用经典的分频代码。

这里附一小段,是我在研究分频控制时看懂的网上的经典分频代码,适合乐曲自动播放等高级的实现,仅供分享assign preclk=(divider==16383)?1:0;//divider==16383,preclk=1always @(posedge clk) //基频上升沿触发beginif(preclk) //preclk=1divider=origin;elsedivider=divider+1;endalways @(posedge preclk) //调整占空比beginspeaker=~speaker; //2 分频产生方波信号end这部分实现了分频功能,其中origin+divider=16384=2^14,这个数根据自己的需要而定。

verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave)

verilog之四位全加器的编译及仿真(⽤开源免费的软件——iverilog+GTKWave)四位全加器的verilog的代码⽐⽐皆是,这⾥上⼀个⽐较简单的:/*4位全加器全加器需要有输⼊输出,需要有下级向上进位的输⼊,需要有向上⼀位进位的输出。

⼤家看⼀下,这个模块已经包含全部的输⼊输出信息。

⼤家都知道,N位加法器得出来的出来的和最多是N+1位因此可以清晰从下⾯代码中看到相关信息。

然后assign⽤的是阻塞赋值。

相加即满⾜相关的需求。

*/module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule在写testbeach⽂件之前,先普及⼀点testbeach的知识:⼀般来讲,在数据类型声明时,和被测模块的输⼊端⼝相连的信号定义为reg类型,这样便于在initial语句和always语句块中对其进⾏赋值;和被测模块输出端⼝相连的信号定义为wire类型,便于进⾏检测。

Testbench模块最重要的的任务就是利⽤各种合法的语句,产⽣适当的时序和数据,以完成测试,并达到覆盖率要求。

那么testbeach⽂件如下:/*File Name : test_adder4.vDescription : The testbench of the adder_4.vWritten By : LiMingData : 2011/04/18 20:13modefied : 在仿真的时候,把延时从10ns改为5ns: cout显⽰为2位*///test_adder4 (top-level module)`timescale 1ns/1nsmodule test_adder4;//Declare variableswire[3:0] sum;wire cout;reg[3:0] ina,inb;reg cin;//Instantiate the module adder4adder4 adder4_1(cout,sum,ina,inb,cin);//Stimulate the inputs, Finish the stimulation at 90 time unitsinitialbegin#0 ina = 4'b0001; inb = 4'b1010; cin = 1'b0;#5 ina = 4'b0010; inb = 4'b1010; cin = 1'b1;#5 ina = 4'b0010; inb = 4'b1110; cin = 1'b0;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0111; inb = 4'b1001; cin = 1'b0;#5 ina = 4'b0001; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b0;#5 ina = 4'b0111; inb = 4'b1111; cin = 1'b1;#5 $finish;endinitial$monitor("At time %t, ina(%b) + inb(%b) + cin(%b) = sum(%b)(%2d),cout(%b)",$time, ina, inb, cin, sum, sum, cout);initialbegin$dumpfile("test.vcd");$dumpvars(0,test_adder4);endendmodule由于是在windows的cmd下进⾏命令⾏的运⾏,所以有时候每次输⼊⼀个命令显得很费时间,所以我这⾥⼜写了⼀个(批处理⽂件)bat⽂件:go.batECHO OFFECHO *********************************ECHO * Batch fileECHO *********************************ECHO *ECHO ONiverilog -o test adder4.v test_adder4.vvvp -n test -lxt2cp test.vcd test.lxtgtkwave test.lxt(说明⼀下,我在windows下安装了gnuwin的软件,即能在windows下⽤gnu的⼀些⼩的实⽤的⼯具!)哈哈,这⾥就可以⼀键运⾏了,上⾯的⼀些命令的解释可以到我的“wndows下如何⽤Iverilog+GTKWave进⾏verilog的编译和查看仿真波形”的博⽂⾥去看看吧。

4位全加器设计解析

可编程逻辑器件设计大作业题目四位全加器设计学院自动化与电气工程学院班级姓名学号2104年12月30 日目录摘要 (1)1.设计目的 (2)2.设计要求 (2)3.设计原理 (2)3.1.四位全加器 (2)3.2.四位全加器的原理图 (4)4.设计方案 (4)4.1.仿真软件 (4)4.2.全加器原理 (5)4.2.1一位全加器的设计与原理 (5)4.2.2四位全加器的原理及程序设计 (5)5.程序设计 (7)6.仿真及结果 (8)总结与体会 (10)参考文献 (11)摘要VHDL主要用于描述数字系统的结构,行为,功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

本次设计是用VHDL语言设计四位全加器,并用Quartus II仿真。

关键词:VHDL 四位全加器Quartus II四位全加器设计1.设计目的复习加法器的原理,掌握加法器的设计实现方法,设计实现数字系统设计中常用的4位全加器,在此基础上进一步熟悉MAX+PLUSⅡ或Quartus II软件的使用方法,熟练掌握EDA的图形编程方法、开发流程、以及组合逻辑电路的设计、分析、综合、仿真方法。

2.设计要求1)复习EDA的相关技术与方法;2)掌握VHDL或者Verilog语言,并要求能编写程序。

3)Quartus软件的使用:掌握程序编辑、编译、调试、仿真方法。

4)设计相关简单的电路,完成既定的功能。

3.设计原理3.1.四位全加器加法器是数字系统中的基本逻辑器件。

4位二进制全加器的设计

4位⼆进制全加器的设计4位⼆进制全加器的设计摘要加法器是产⽣数的和的装置。

加数和被加数为输⼊,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输⼊,⽽和数与进位为输出则为全加器。

常⽤作计算机算术逻辑部件,执⾏逻辑操作、移位与指令调⽤。

在电⼦学中,加法器是⼀种数位电路,其可进⾏数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以⽤来表⽰各种数值,如:BCD、加三码,主要的加法器是以⼆进制作运算。

多位加法器的构成有两种⽅式:并⾏进位和串⾏进位⽅式。

并⾏进位加法器设有并⾏进位产⽣逻辑,运⾏速度快;串⾏进位⽅式是将全加器级联构成多位加法器。

通常,并⾏加法器⽐串⾏加法器的资源占⽤差距也会越来越⼤。

我们采⽤4位⼆进制并⾏加法器作为折中选择,所选加法器为4位⼆进制先⾏进位的74LS283,它从C0到C4输出的传输延迟很短,只⽤了⼏级逻辑来形成和及进位输出,由其构成4位⼆进制全加器,并⽤Verilog HDL进⾏仿真。

关键字全加器,四位⼆进制,迭代电路,并⾏进位,74LS283,Verilog HDL仿真总电路设计⼀、硬件电路的设计该4位⼆进制全加器以74LS283(图1)为核⼼,采⽤先⾏进位⽅式,极⼤地提⾼了电路运⾏速度,下⾯是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是⼀种由被加数、加数和来⾃低位的进位数三者相加的运算器。

基本功能是实现⼆进制加法。

全加器的功能表输⼊输出输⼊输出逻辑表达式:CI B A S ⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()AB CI B A CO ++=其中,如果输⼊有奇数个1,则S 为1;如果输⼊有2个或2个以上的1,则CO=1。

实现全加器等式的门级电路图如图2所⽰,逻辑符号如图3所⽰.图2 图32)四位⼆级制加法器 a) 串⾏进位加法器四位⼆进制加法器为4个全加器的级联,每个处理⼀位。

Verilog实现的4位串行进位加法器精编版

Verilog实现的4位串行进位加法器精编版在数字电路中,加法器是最基本的电路之一、串行进位加法器是一种将两个二进制数相加的电路,通过逐位相加的方式实现。

本文将介绍如何使用Verilog语言实现一个4位串行进位加法器的精编版。

首先,我们需要定义输入和输出端口。

对于一个4位的串行进位加法器,我们需要4个输入端口A[3:0]和B[3:0],以及一个输出端口Sum[3:0]。

另外,还需要一个输入端口CarryIn和一个输出端口CarryOut,用于传递进位信号。

```module SerialCarryAdderinput [3:0] A,input [3:0] B,input CarryIn,output [3:0] Sum,output CarryOut```接下来,我们可以定义内部信号。

对于一个4位的串行进位加法器,我们需要4个内部信号,分别代表每一位的进位信号。

```wire C0, C1, C2, C3;```然后,我们可以开始实现每一位的加法逻辑。

首先,我们定义一个内部信号XOROut,用于存储每一位的异或结果。

然后,我们使用XOR门实现异或逻辑。

```wire XOROut;assign XOROut = A[0] ^ B[0];```接下来,我们定义一个内部信号ANDOut,用于存储每一位的与结果。

然后,我们使用AND门实现与逻辑。

```wire ANDOut;assign ANDOut = A[0] & B[0];```然后,我们定义一个内部信号Sum0,用于存储第一位的和结果。

然后,我们使用XOR门实现异或逻辑。

```wire Sum0;assign Sum0 = XOROut ^ CarryIn;```然后,我们定义一个内部信号Carry0,用于存储第一位的进位结果。

然后,我们使用OR门实现或逻辑。

```wire Carry0;assign Carry0 = ANDOut , (XOROut & CarryIn);```接下来,我们可以依次实现剩余3位的加法逻辑。

4位全加器verilog课程设计

4位全加器verilog课程设计一、课程目标知识目标:1. 理解4位全加器的原理和功能,掌握其Verilog硬件描述语言实现方法。

2. 学习并掌握数字电路中加法器的基本结构和工作原理。

3. 掌握Verilog模块化编程,能够实现并测试4位全加器的基本功能。

技能目标:1. 能够运用Verilog语言编写4位全加器的代码,并进行功能仿真。

2. 学会使用硬件描述语言进行数字电路的设计,提高实际问题解决能力。

3. 能够对4位全加器进行调试和优化,提升编程实践技能。

情感态度价值观目标:1. 培养学生的团队合作意识,提高学生在项目实践中的沟通与协作能力。

2. 增强学生对数字电路设计领域的兴趣,激发学生的创新精神。

3. 引导学生树立正确的价值观,认识到科技发展对社会进步的重要性。

课程性质:本课程为电子信息工程及相关专业高年级的数字电路设计课程,旨在通过4位全加器的Verilog实现,让学生掌握数字电路设计的基本方法和实践技能。

学生特点:学生已具备一定的数字电路基础和Verilog编程知识,具备分析问题和解决问题的能力。

教学要求:注重理论与实践相结合,鼓励学生积极参与课堂讨论,培养学生的动手能力和实际操作技能。

通过课程学习,使学生在知识、技能和情感态度价值观方面均取得明显进步。

二、教学内容本课程教学内容主要包括以下几部分:1. 数字加法器原理回顾:介绍加法器的基本原理,重点讲解4位全加器的工作流程和关键特性。

- 教材章节:数字电路基础,第3章第2节。

2. Verilog硬件描述语言基础:复习Verilog的基本语法,强调模块化编程方法。

- 教材章节:硬件描述语言Verilog,第4章。

3. 4位全加器的Verilog设计:- 设计原理:讲解4位全加器的设计思路和实现方法。

- 代码编写:引导学生编写4位全加器的Verilog代码,并进行模块化设计。

- 教材章节:数字电路设计,第5章第3节。

4. 功能仿真与调试:- 介绍仿真工具和仿真方法,指导学生进行4位全加器的功能仿真。

verilog四位BCD加法器实验报告

1.实验目的1 2 3进一步熟悉modelsim 仿真工具的使用方法。

学会设计验证的方法和流程。

编写一个4位BCD加法器,并且用modelsim 对其仿真。

2.实验任务进一步熟悉modelsim 仿真基本流程。

并完成一个4位BCD加法器,用modelsim对其仿真。

3.实验内容及步骤3.1 实验内容进一步熟悉modelsim 仿真基本流程:①建一个工作库②编译设计文件③运行仿真④调试结果实验步骤:1.启动modelsim。

2.创建一个新工程:①在主菜单窗口的主菜单中选择“File→New→Project”。

②在项目名称域中输入工程名称(如adder_bcd),如下图所示。

③单击Browse 按钮选择工程文件存储的目录。

④确认默认库名称为work,单击OK按钮。

3. 创建新设计的文件:①单击OK按钮接受工程设置后,在主窗口的工作区将出现一个工程标签,同时弹出向工程添加项目的对话框。

单击“Create New File”,在新弹出的窗口中,输入文件名(如adder_1bit),特别需要注意的是,“Add file as type”里边要选择“verilog”类型。

②如果还需要写新的模块,在project对话框中点右键,选择“Add to Project→New File”。

在弹出的对话框中输入新的文件名(如adder_bcd_1bit;adder_bcd_4bit;test),同样注意“Add file as type”里边要选择“verilog”类型。

4.向工程输入有效的设计单元:把设计的源文件输入到工程里边。

4.在主窗口中选择“Compile→Compile All”完成工程的编译。

对于modelsim正确编译的设计文件,都打上“√”标志;对于编译失败的情况,打上“×”标志,此时可在右侧的脚本状态窗中查看出错信息,修正后再编译。

6. 完成工程正确的编译后,在主窗口中单击Library标签,进入编译库页,打开work库,双击测试单元(如test),加载测试单元。

verilog generate for时序逻辑

Verilog中的generate for语句是用于生成时序逻辑的重要工具。

在数字电路设计中,时序逻辑是指数字电路系统中的各个元件在时钟信号的控制下按特定时序完成各种功能。

Verilog generate for语句可以在编程中简化时序逻辑的设计和实现,提高代码的可读性和可维护性。

1. generate for语句的基本概念Verilog的generate for语句使用类似于C语言的for循环语法,可以在编程中方便地生成重复的时序逻辑。

它的基本结构如下:```veriloggenvar i;generatefor (i = 0; i < N; i=i+1) begin// 时序逻辑代码endendgenerate```2. generate for语句的应用生成时序逻辑的典型应用场景包括定制嵌套模块、生成复杂的状态机、生成多个相似的处理器等。

在这些场景下,使用generate for语句可以大大简化设计和编程工作,提高代码的可维护性和可复用性。

3. generate for语句的优点使用generate for语句可以减少代码冗余、提高代码的可读性和可维护性。

在时序逻辑设计中,往往涉及大量的重复代码,使用generate for语句可以将这些代码整合到一个循环中,简化代码的结构,提高代码的重用性。

4. generate for语句的注意事项在使用generate for语句时,需要注意循环变量的作用域和命名规范,以避免和其他部分的代码产生冲突。

另外,需要注意循环次数的控制,避免出现死循环或者循环次数不够导致功能不完整的情况。

5. generate for语句的实例下面我们以一个简单的例子来演示generate for语句的使用。

假设我们需要生成一个4位的加法器,我们可以使用generate for语句来简化这个过程。

```veriloggenvar i;generatefor (i = 0; i < 4; i=i+1) beginfull_adder fa (.a(a[i]),.b(b[i]),.cin(cin),.sum(sum[i]),.cout(cout));assign cin = cout;endendgenerate```在这个例子中,我们使用generate for语句生成了4个全加器,并通过assign语句将它们串联起来,实现了一个4位的加法器。

组合逻辑课程设计4位二进制全加器全减器原创

组合逻辑电路课程设计——4位二进制全加器/全减器作者:学号:课程设计题目要求:使用74LS283构成4位二进制全加/全减器。

阐述设计思路。

列出真值表。

画出设计的逻辑图。

用VHDL对所画电路进行仿真。

目录摘要错误!未定义书签。

1总电路设计错误!未定义书签。

硬件电路的设计错误!未定义书签。

全加器(full-adder )错误!未定义书签。

四位二级制加法器错误!未定义书签。

串行进位加法器错误!未定义书签。

超前进位加法器错误!未定义书签。

超前位链结构加法器错误!未定义书签。

全减器(full-substracter )错误!未定义书签。

总电路设计错误!未定义书签。

2设计思路错误!未定义书签。

全加器错误!未定义书签。

全减器错误!未定义书签。

3真值表错误!未定义书签。

4逻辑图与仿真错误!未定义书签。

5软件程序的设计错误!未定义书签。

6结果分析与总结错误!未定义书签。

摘要加法器是数字系统中产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

例如:为了节省资源,减法器和硬件乘法器都可以用加法器来构成。

但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成主要有两种:并行进位和串行进位。

并行进位加法器设有并行进位产生逻辑,运行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多位加法器。

加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

本文将采用4位二进制并行加法器作为折中选择,所选加法器为74LS283,74LS283是4位二进制先行进位的加法器,它只用了几级逻辑来形成和及进位输出,故由其构成4位二进制全加器;而四位全减器可以用加法器简单的改造而来,最后本文采用VHDL对四位全加器/全减器进行仿真。

4位全加器设计

目录摘要 (1)1.设计目的 (2)2.设计要求 (2)3.设计原理 (2)3.1.四位全加器 (2)3.2.四位全加器的原理图 (4)4.设计方案 (4)4.1.仿真软件 (4)4.2.全加器原理 (5)4.2.1一位全加器的设计与原理 (5)4.2.2四位全加器的原理及程序设计 (5)5.程序设计 (7)6.仿真及结果 (8)总结与体会 (10)参考文献 (11)摘要VHDL主要用于描述数字系统的结构,行为,功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

本次设计是用VHDL语言设计四位全加器,并用Quartus II仿真。

关键词:VHDL 四位全加器Quartus II四位全加器设计1.设计目的复习加法器的原理,掌握加法器的设计实现方法,设计实现数字系统设计中常用的4位全加器,在此基础上进一步熟悉MAX+PLUSⅡ或Quartus II软件的使用方法,熟练掌握EDA的图形编程方法、开发流程、以及组合逻辑电路的设计、分析、综合、仿真方法。

2.设计要求1)复习EDA的相关技术与方法;2)掌握VHDL或者Verilog语言,并要求能编写程序。

3)Quartus软件的使用:掌握程序编辑、编译、调试、仿真方法。

4)设计相关简单的电路,完成既定的功能。

3.设计原理3.1.四位全加器加法器是数字系统中的基本逻辑器件。

例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

用Verilog HDL语言编写的四位超前进位加法器

四位超前进位加法器

——Verilog HDL语言

四位超前进位加法器的进位是并 行同时产生的,能够极大的减 少加法器由进位引起的延时。 增加了逻辑器件,但有效的减 少的延迟。进位是由ALU部件超 前算出,本位是由四个不含进 位的加法器算出。

Verilog HDL代码如下: module jiafaqi_4(x,y,c0,c4,f); //四位超前进位加法器 input [4:1]x; //四位x值 input [4:1]y; //四位y值 output [4:1]f; //四位加和f input c0; //上一的级进位 output c4; //向下一级的进位 wire [3:1]c; //超前进位 wire [4:1]p; wire [4:1]g; wire [4:1]cd; assign p=x|y; assign g=x&y;

// 在BASYS2开发板上的管脚配置 NET "c4" LOC = N5; NET "c0" LOC = A7; NET "x[1]" LOC = P11; NET "x[2]" LOC = L3; NET "x[3]" LOC = K3; NET "x[4]" LOC = B4; NET "y[1]" LOC = G3; NET "y[2]" LOC = F3; NET "y[3]" LOC = E2; NET "y[4]" LOC = N3; NET "f[1]" LOC = M5; NET "f[2]" LOC = M11; NET "f[3]" LOC = P7; NET "f[4]" LOC = P6;

4位二进制全加器的设计

4位二进制全加器的设计摘要加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运行速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行加法器的资源占用差距也会越来越大。

我们采用4位二进制并行加法器作为折中选择,所选加法器为4位二进制先行进位的74LS283,它从C0到C4输出的传输延迟很短,只用了几级逻辑来形成和及进位输出,由其构成4位二进制全加器,并用Verilog HDL进行仿真。

关键字全加器,四位二进制,迭代电路,并行进位,74LS283,Verilog HDL仿真总电路设计一、硬件电路的设计该4位二进制全加器以74LS283(图1)为核心,采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是一种由被加数、加数和来自低位的进位数三者相加的运算器。

基本功能是实现二进制加法。

输入输出输入输出CI B A S ⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()AB CI B A CO ++=其中,如果输入有奇数个1,则S 为1;如果输入有2个或2个以上的1,则CO=1。

实现全加器等式的门级电路图如图2所示,逻辑符号如图3所示.图2 图32)四位二级制加法器 a) 串行进位加法器四位二进制加法器为4个全加器的级联,每个处理一位。

1FPGA实验报告4位全加器—徐艺萍

1FPGA实验报告4位全加器—徐艺萍试验⼀4位全加器实验1.实验原理全加器能进⾏加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。

全加器的真值表如表1所⽰。

表1 全加器真值表4位全加器可以采⽤四个1位全加器级连成并⾏相加串⾏进位的加法器,实现框图如图1所⽰,其中CSA为1位全加器。

由图可以看出,每1位的进位信号送给下1位作为输⼊信号,因此,任1位的加法运算必须在低1位的运算完成之后才能进⾏,因此它的延迟⾮常可观,⾼速运算肯定⽆法胜任。

图1 4位串⾏进位加法器实现框图在图1中,A和B为加法器的输⼊位串,对于四位全加器则位宽为4位,D 为加法器输出位串,和输⼊位串相同,C为进位输⼊( Ci ) 或输出( Co )。

实现代码为:module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule2.实验⽬的⒈熟悉ISE9.1 开发环境,掌握⼯程的⽣成⽅法;⒉了解Verilog HDL语⾔在FPGA 中的使⽤;⒊了解4位全加器的Verilog HDL语⾔实现。

3.实验内容⒈⽤Verilog HDL语⾔设计4位全加器,进⾏功能仿真验证。

⒉使⽤Chipscope Pro ⽣成VIO/ICON 核,在线观测调试。

4.实验准备⒈将USB 下载电缆与计算机及XUPV2Pro 板的J8 连接好;⒉将RS232 串⼝线⼀端与计算机连接好,另⼀端与板卡的J11 相连接;⒊启动计算机,当计算机启动后,将XUPV2Pro 板的电源开关SW11 打开到ON 上。

观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指⽰灯是否均亮。

若有不亮的,请断开电源,检查电源;5.实验步骤⒈创建⼯程及设计输⼊⑴在E:\project\⽬录下,新建名为count8的新⼯程器件族类型(Device Family)选择“Virtex2P”,器件型号(Device)选“XC2VP30 ff896 -7”,综合⼯具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator(VHDL/Verilog)”。

《Verilog HDL硬件描述语言》实验教学大纲

《Verilog HDL硬件描述语言》实验教学大纲

课程代码:MICR3001

课程名称:Verilog HDL硬件描述语言

英文名称:Verilog HDL

实验室名称:微电子实验室

课程学时:72实验学时:18

一、本课程实验教学目的与要求

通过实验要求学生掌握用Verilog HDL硬件描述语言进行集成电路设计的流程和方法。

学会使用Max+plusⅡ,QuartusⅡ设计软件,掌握从HDL源代码的输入→编译→仿真→管脚锁定→下载全过程。

学会用ModelSim设计软件,用Verilog HDL编写测试码对设计模块进行仿真。

二、主要仪器设备及现有台套数

PC,现有35台; EDA实验箱,25套;

1、实验报告:有设计代码,仿真结果,管脚排列,验证结果。

2、考核方式:

(1)实验课的考核方式:教师验收评定成绩。

(2)实验课考核成绩:根据实验完成情况和实验报告是否完整确定,实验课成绩占课程总成绩的10%。

五、实验教材、参考书

1、教材:在编

2、参考书:J.Bhasker著,夏宇闻等译《Verilog HDL入门》.北京航空航天大学出版社.2008出版。

FPGA4位全加器的设计

目录一、设计原理 (1)二、设计目的 (1)三、设计内容 (2)四、设计步骤 (2)五、总结与体会 (6)4位全加器设计报告一、设计原理全加器是指能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位。

4位加法器可以采用4个以为全加器级连成串行进位加法器,如下图所示,其中CSA 为一位全加器。

显然,对于这种方式,因高位运算必须要等低位进位来到后才能进行,因此它的延迟非常可观,高速运算无法胜任。

A 和B 为加法器的输入位串,对于4位加法器其位宽为4位,S 为加法器输出位串,与输入位串相同,C 为进位输入(CI )或输出(CO )。

实现代码为: 全加器真值表如下:module adder4(cout,sum,ina,inb,cin); output[3:0]sum; output cout;input[3:0]ina,inb; input cin;assign {count,sum}=ina+inb+cin; endmodule二、设计目的⑴熟悉ISE9.1开发环境,掌握工程的生成方法。

⑵熟悉SEED-XDTK XUPV2Pro 实验环境。

⑶了解Verilog HDL 语言在FPGA 中的使用。

⑷了解4位全加器的Verilog HDL 语言实现。

输 入 输 出Xi Yi Ci-1 SiCi 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 11111三、设计内容用Verilog HDL语言设计4位全加器,进行功能仿真演示。

四、设计步骤1、创建工程及设计输入。

⑴在E:\progect\目录下,新建名为count8的新工程。

⑵器件族类型(Device Family)选择“Virtex2P”器件型号(Device)选“XC2VP30 ff896-7”综合工具(Synthesis Tool)选“XST(VHDL/Verilog)”仿真器(Simulator)选“ISE Simulator”⑶下面一直next和确定。