74LV573

74LVT573MTCX,74LVT573MTC,74LVT573MSAX,74LVT573SJX,74LVT573WM,74LVT573WMX, 规格书,Datasheet 资料

74LVT573, 74LVTH573 — Low Voltage Octal Transparent Latch with 3-STATE OutputsLow Voltage Octal Transparent Latch with 3-STATE OutputsFeatures■ Input and output interface capability to systems at 5V V CC■Bushold data inputs eliminate the need for external pull-up resistors to hold unused inputs (74LVTH573), also available without bushold feature (74LVT573) ■ Live insertion/extraction permitted■ Power Up/Down high impedance provides glitch-free bus loading■ Outputs source/sink –32mA/+64mA■ Functionally compatible with the 74 series 573 ■ Latch-up performance exceeds 500mA ■ESD performance:– Human-body model > 2000V – Machine model > 200V– Charged-device model > 1000VGeneral DescriptionThe LVT573 and LVTH573 consist of eight latches with 3-STATE outputs for bus organized system applica-tions. The latches appear transparent to the data when Latch Enable (LE) is HIGH. When LE is low, the data satisfying the input timing requirements is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the bus output is in the high impedance state.The LVTH573 data inputs include bushold, eliminating the need for external pull-up resistors to hold unused inputs.These octal latches are designed for low-voltage (3.3V)V CC applications, but with the capability to provide a TTL interface to a 5V environment. The LVT573 and LVTH573 are fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.Ordering InformationDevice also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.All packages are lead free per JEDEC: J-STD-020B standard.Order NumberPackage NumberPackage Description74LVT573WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74LVT573SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74LVT573MSA MSA2020-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide 74LVT573MTC MTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide74LVTH573WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74LVTH573SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74LVTH573MSA MSA2020-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide 74LVTH573MTCMTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePin DescriptionFunctional DescriptionThe LVT573 and LVTH573 contain eight D-type latches with 3-STATE standard outputs. When the Latch Enable (LE) input is HIGH, data on the D n inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D-type input changes. When LE is LOW, the latches store the infor-mation that was present on the D-type inputs a setup time preceding the HIGH-to-LOW transition of LE. The 3-STATE standard outputs are controlled by the Output Enable (OE) input. When OE is LOW, the standard out-puts are in the 2-state mode. When OE is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.IEEE/IECTruth TableH = HIGH Voltage LevelL = LOW Voltage LevelZ = High ImpedanceX = ImmaterialO0= Previous O0 before HIGH to LOW transition of Latch EnablePin Names DescriptionD0–D7Data InputsLE Latch Enable InputOE Output Enable InputO0–O73-STATE Latch OutputsInputs OutputsLE OE D n O nX H X ZH L L LH L H HL L X O074LVT573, 74LVTH573 — Low Voltage Octal Transparent Latch with 3-STATE Outputs74LVT573, 74LVTH573 — Low Voltage Octal Transparent Latch with 3-STATE Outputs Please note that this diagram is provided only for the understanding of logic operations and should not be used toestimate propagation delays.74LVT573, 74LVTH573 — Low Voltage Octal Transparent Latch with 3-STATE OutputsNote:1.I O Absolute Maximum Rating must be observed.Recommended Operating ConditionsThe Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.V CC Supply Voltage –0.5V to +4.6V V I DC Input Voltage –0.5V to +7.0V V ODC Output Voltage Output in 3-STATE–0.5V to +7.0V Output in HIGH or LOW State (1)–0.5V to +7.0VI IK DC Input Diode Current, V I < GND –50mA I OK DC Output Diode Current, V O < GND –50mA I ODC Output Current, V O > V CC Output at HIGH State 64mA Output at LOW State128mA I CC DC Supply Current per Supply Pin ±64mA I GND DC Ground Current per Ground Pin ±128mAT STGStorage Temperature–65°C to +150°CSymbolParameter MinMaxUnitsV CC Supply Voltage 2.7 3.6V V I Input Voltage5.5V I OH HIGH-Level Output Current –32mA I OL LOW-Level Output Current 64mA T A Free-Air Operating Temperature–4085°C ∆ t / ∆ VInput Edge Rate, V IN = 0.8V–2.0V , V CC =3.0V10ns/VNotes:2.All typical values are at V CC=3.3V, T A= 25°C.3.Applies to bushold versions only (74LVTH573).V O≥ V CC – 0.1VV IL Input LOW Voltage 2.7–3.60.8V V OH Output HIGH Voltage 2.7–3.6I OH= –100µA V CC – 0.2 V2.7I OH= –8mA 2.43.0I OH= –32mA 2.0V OL Output LOW Voltage 2.7I OL= 100µA 0.2VI OL= 24mA0.53.0I OL= 16mA 0.4I OL= 32mA0.5I OL= 64mA 0.55I I(HOLD)(3)Bushold Input MinimumDrive 3.0V I= 0.8V75µAV I= 2.0V –75I I(OD)(3)Bushold Input Over-DriveCurrent to Change State 3.0(4)500µA(5)–500I I Input Current 3.6V I= 5.5V10µAControl Pins 3.6V I= 0V or V CC±1Data Pins 3.6V I= 0V–5V I= V CC 1I OFF Power Off Leakage Current 00V ≤ V I or V O≤ 5.5V±100µAI PU/PD Power up/down 3-STATEOutput Current 0–1.5V O= 0.5V to 3.0V,V I= GND or V CC±100µAI OZL3-STATE Output LeakageCurrent3.6V O= 0.5V–5 µAI OZH3-STATE Output LeakageCurrent3.6V O= 3.0V5µAI OZH+3-STATE Output LeakageCurrent3.6V CC< V O≤ 5.5V 10µAI CCH Power Supply Current 3.6Outputs HIGH0.19mA I CCL Power Supply Current 3.6Outputs LOW5mA I CCZ Power Supply Current 3.6Outputs Disabled 0.19mA I CCZ+Power Supply Current 3.6V CC≤ V O≤ 5.5V,Outputs Disabled0.19mA∆I CC Increase in Power SupplyCurrent(6)3.6One Input at V CC – 0.6V,Other Inputs at V CC orGND0.2mA74LVT573, 74LVTH573 — Low Voltage Octal Transparent Latch with 3-STATE Outputs10.Skew is defined as the absolute value of the difference between the actual propagation delay for any twoseparate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL) or LOW-to-HIGH (t OSLH).Capacitance(11)Symbol Parameter Conditions Typical UnitsC IN Input Capacitance V CC= Open, V I= 0V or V CC4pFC OUT Output Capacitance V CC= 3.0V, V O= 0V or V CC6pF Note:Figure 1. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:/packaging/Figure 2. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify orFigure 3. 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,Figure 4. 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner©1999 Fairchild Semiconductor Corporation 74LVT573, 74LVTH573 Rev. 1.7.011subsidiaries,and is not intended to be an exhaustive list of all such trademarks.ACEx ®Build it Now™CorePLUS™CROSSVOLT ™CTL™Current Transfer Logic™EcoSPARK ®EZSWITCH™*™®Fairchild ®Fairchild Semiconductor ®FACT Quiet Series™FACT ®FAST ®FastvCore™FlashWriter ®*FPS™FRFET ®Global Power Resource SM Green FPS™Green FPS™e-Series™GTO™i-Lo ™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MillerDrive™Motion-SPM™OPTOLOGIC ®OPTOPLANAR ®®PDP-SPM™Power220®POWEREDGE ®Power-SPM™PowerTrench ®Programmable Active Droop™QFET ®QS™QT Optoelectronics™Quiet Series™RapidConfigure™SMART START™SPM ®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SupreMOS™SyncFET™®The Power Franchise ®TinyBoost™TinyBuck™TinyLogic ®TINYOPTO™TinyPower™TinyPWM™TinyWire™µSerDes™UHC ®Ultra FRFET™UniFET™VCX™*EZSWITCH™and FlashWriter ®are trademarks of System General Corporation,used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY,FUNCTION,OR DESIGN.FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS,NOR THE RIGHTS OF OTHERS.THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS,SPECIFICALLY THE WARRANTY THEREIN,WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body or (b)support or sustain life,and (c)whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury of the user.2.A critical component in any component of a life support,device,or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationFormative or In DesignThis datasheet contains the design specifications for productdevelopment.Specifications may change in any manner without notice.Preliminary First ProductionThis datasheet contains preliminary data;supplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.74LVT573, 74LVTH573 — Low Voltage Octal Transparent Latch with 3-STATE Outputs芯天下--/。

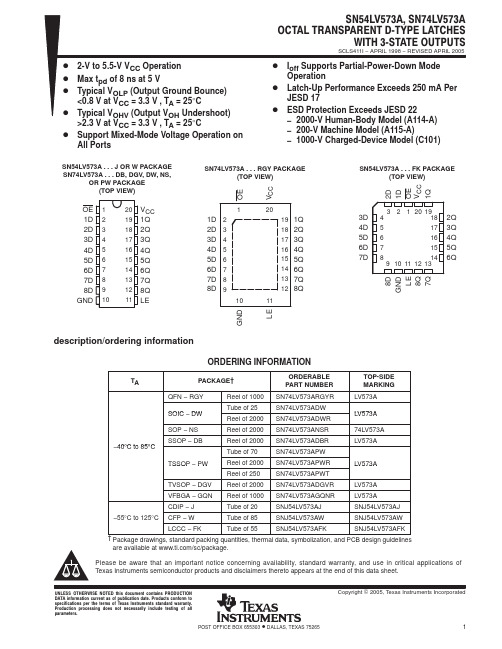

SN74LVC573APW(表贴三态输出八D锁存器)

IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

SN74LVC573A中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

hc573完整中文资料

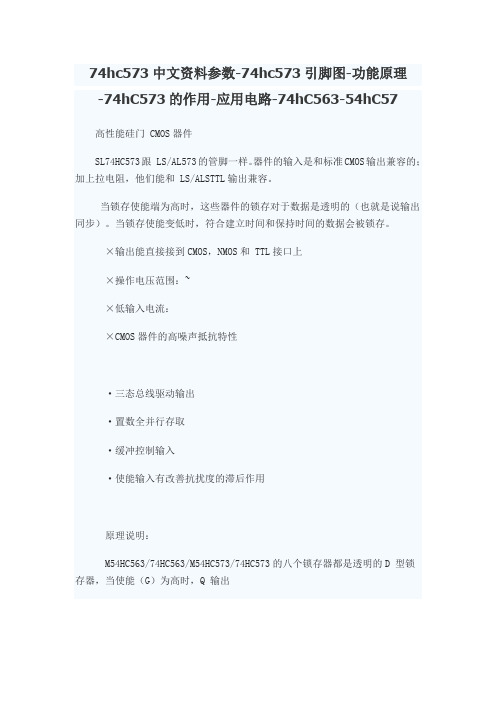

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门 CMOS器件SL74HC573跟 LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和 LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和 TTL接口上×操作电压范围:~×低输入电流:×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

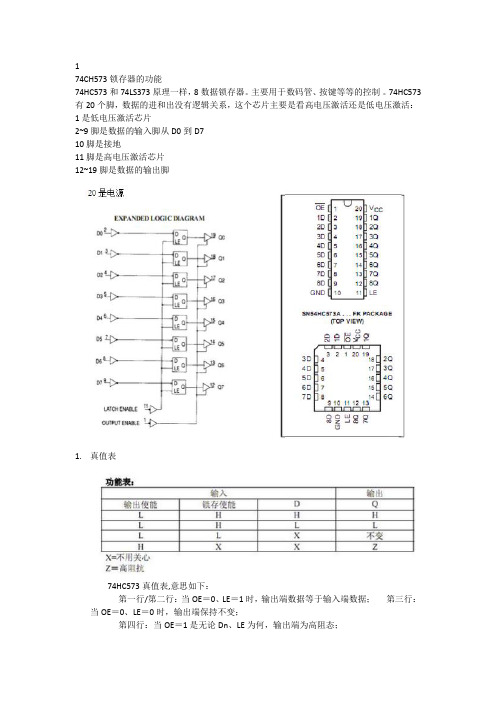

HC563引脚功能表:HC573引脚功能表:12,13,14,15,16,17,18,19Q0 to Q7 3 State Latch Outputs 3态锁存输出11LE Latch Enable Input 锁存使能输入10GND Ground接地(0V)20VCC Positive Supply Voltage电源电压图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6HC573 逻辑图图7 输入输出等效电路真值表:INPUTS 输入Outputs输出OE LE D Q (HC573) Q (HC563)H X X Z ZL L X NO CHANGE *NO CHANGE * L H L L HL H H H LABSOLUTE MAXIMUM RATINGS绝对最大额定值:TopOperating Temperature: M54HC Series M74HC Series操作温度: M54HC 系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC = 2V0 to 1000ns VCC =0 to 500VCC = 6V0 to 400VOHHigh Level Output Voltage输出高电平电压VI = VIH or VILIO=-20 μ 4.54.44 Level Output Voltage输出低电平电压VI = VIH or VILIO=20μ Leakage Current输入漏电流 =VCC or GND--±±1±1μAIOZState Output Off State Current关断状态3态输出电流 =VIH or VIL VO =VCC or GND--±±±10μAICCQuiescent Supply Current静态电源电流 =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

中微爱芯逻辑芯片AIP74LV AIP74LVC系列

概述:AiP74LVC1G18是2选1的同相多路分解器,具有3态输出。

设备根据输入的状态是否缓冲输入A上的数据并将其传递给输出1Y或2Y 输入(引脚S)为LOW或HIGH。

可以从3.3或5V设备驱动输入。

这些功能允许在3.3V和5V混合环境中使用这些设备。

该设备完全指定用于使用IOFF的部分掉电应用。

IOFF电路会禁用输出,以防止在断电时通过设备的有害回流电流。

特点:宽电源电压范围为1.65V至5.5V 5V耐压输入,可与5V逻辑±24mA 输出驱动器接口(VCC = 3.0V)CMOS低功耗锁存性能超过250mA 具有TTL电平的直接接口在-40℃至+ 85℃包装信息:SOT-23-6 / SOT-363AiP74LVC2G04概述:AiP74LVC2G04提供了双反相缓冲器。

输入可以由3.3V或5V器件驱动。

这些功能允许在3.3V和5V混合环境中使用这些器件。

该器件完全指定用于使用IOFF的部分掉电应用。

IOFF电路禁用输出,以防止在断电时流经该器件的有害回流电流。

宽电源电压范围为1.65V至5.5V5V耐压输入,用于与5V逻辑接口高抗扰度±24mA输出驱动(VCC = 3.0V)CMOS低功耗闩锁性能超过250mA与TTL电平直接接口输入可接受高达5V的电压多种包装选择规定温度为-40℃至+ 85℃包装信息:SOT23-6 / SOT36374系列产品AiP74HC/HCT/LVC系列:拥有74HC/HCT/LVC等系列品种上百款,可完全替换进口TI/NXP/ON等公司逻辑产品。

74系列产品广泛应用各种电子产品中,如家电、数码产品、仪器仪表、工业设备、电信及网络设备等,用于数据放大、运算、锁存、移位等处理,工作温度范围-40℃到85℃。

74HCXXX、74HCTXXX、74LVCXXX等是指对应的芯片系列,“XXX”表示芯片具体型号。

>> 有批量现货产品如下:•门电路AiP74HC00,AiP74HCT00,AiP74HC02,AiP74HC05,AiP74HC08,AiP74HCT08,AiP74HC20,AiP74HC32,AiP74HC86,AiP74HCT86•反相器/缓冲器/驱动器/收发器AiP74HC04,AiP74HCT04,AiP74HC07,AiP74HC14,AiP74HC125,AiP74HC126,AiP74HC244,AiP74HCT244,AiP74HC245,AiP74HCT245•编码器/译码器AiP74HC138,AiP74HCT138,AiP74HCT139,AiP74HC148,AiP74HC238•数字复用器AiP74HC157•触发器AiP74HC74,AiP74HC273,AiP74HC374,AiP74HC574•锁存器AiP74HC373,AiP74HC563,AiP74HC573,AiP74HCT573•移位寄存器AiP74HC164,AiP74HC165,AiP74HC595•计数器AiP74HC191,AiP74HC192,AiP74HC193•多频振荡器74HC123>> 可接受提前一个月订货产品如下:•门电路AiP74HCT02,AiP74HC03,AiP74HCT03,AiP74HC10,AiP74HCT10,AiP74HC11,AiP74HCT11,AiP74HCT20,AiP74HC21,AiP74HCT21,AiP74HC27,AiP74HCT27,AiP74HC30,AiP74HCT30,AiP74HCT32,AiP74HC58,AiP74HCT58,AiP74HC132,AiP74HCT132,AiP74HC4002,AiP74HCT4002,AiP74HC4075,AiP74HCT4075,AiP74HC7266,AiP74HCT7266•反相器/缓冲器/驱动器/收发器AiP74HCT05,AiP74HCT14,AiP74HCT125,AiP74HCT126,AiP74HC240,AiP74HCT240,AiP74HC241,AiP74HCT241,AiP74HC243,AiP74HCT243,AiP74HC365,AiP74HCT365,AiP74HC366,AiP74HCT366,AiP74HC367,AiP74HCT367,AiP74HC368,AiP74HCT368,AiP74HC540,AiP74HCT540,AiP74HC541,AiP74HCT541,AiP74HC640,AiP74HCT640,AiP74HC4049,AiP74HCT4049,AiP74HC4050,AiP74HCT4050,AiP74HC7014•编码器/译码器AiP74HC42,AiP74HCT42,AiP74HC47,AiP74HC48,AiP74HC137,AiP74HCT137,AiP74HCT139,AiP74HC147,AiP74HCT147,AiP74HCT148,AiP74HC237,AiP74HCT237,AiP74HC238,AiP74HCT238•数字复用器AiP74HC151,AiP74HCT151,AiP74HC153,AiP74HCT153,AiP74HCT157,AiP74HC158,AiP74HCT158,AiP74HC251,AiP74HCT251,AiP74HC253,AiP74HCT253,AiP74HC257,AiP74HCT257,AiP74HC258,AiP74HCT258•触发器AiP74HCT74,AiP74HCT273,AiP74HCT374,AiP74HC534,AiP74HCT534,AiP74HC564,AiP74HCT564,AiP74HCT574•锁存器AiP74HCT373,AiP74HCT563•计数器AiP74HC160,AiP74HCT160,AiP74HC161,AiP74HCT161,AiP74HC162,AiP74HC162,AiP74HC163,AiP74HCT163,AiP74HC190,AiP74HCT190,AiP74HCT191,AiP74HCT192,AiP74HCT193•数字比较器/多频振荡器/奇偶校验器/全加器AiP74HC85,AiP74HCT85,AiP74HCT123,AiP74HC280,AiP74HCT280,AiP74HC283,AiP74HCT283>> 有现货产品如下:•门电路AiP74LVC00,AiP74LVC08,AiP74LVC32,AiP74LVC1G00,AiP74LVC1G08,AiP74LVC1G27,AiP74LVC1G32,AiP74LVC1G38,AiP74LVC1G86,AiP74LVC2G08 •反相器/缓冲器/驱动器/收发器AiP74LVC04,AiP74LVC1G04,AiP74LVC1G07,AiP74LVC1G14,AiP74LVC1G17,AiP74LVC1G125,AiP74LVC1G126,AiP74LVC2G04,AiP74LVC2GU04,AiP74LVC2G14,AiP74LVC2G34•编码器/译码器AiP74LVC138,AiP74LVC1G18•数字复用器AiP74LVC157,AiP74LVC1G157•触发器AiP74LVC74,AiP74LVC1G74>> 可接受提前一个月订货产品如下:•门电路AiP74LVC02,AiP74LVC03,AiP74LVC10,AiP74LVC11,AiP74LVC20,AiP74LVC27,AiP74LVC30,AiP74LVC86,AiP74LVC132,AiP74LVC1G02,AiP74LVC1G10,AiP74LVC1G11,AiP74LVC1G57,AiP74LVC1G58,AiP74LVC1G97,AiP74LVC1G98,AiP74LVC1G99,AiP74LVC1G332,AiP74LVC1G386,AiPLVC2G00,AiPLVC2G02,AiPLVC2G32,AiPLVC2G38,AiPLVC2G86•反相器/缓冲器/驱动器/收发器AiP74LVCU04,AiP74LVC05,AiP74LVC06,AiP74LVC07,AiP74LVC14,AiP74LVC17,AiP74LVC125,AiP74LVC126,AiP74LVC240,AiP74LVC244,AiP74LVC245,AiP74LVC365,AiP74LVC367,AiP74LVC541,AiP74LVC623,AiP74LVC1GU04,AiP74LVC1G06,AiP74LVC1G34,AiP74LVC2G06,AiP74LVC2G07,AiP74LVC2G16,AiP74LVC2G17,AiPLVC2G125,AiPLVC2G126,AiPLVC2G240,AiPLVC2G241•编码器/译码器AiP74LVC139,AiP74LVC1G16,AiPLVC1G19•数字复用器AiP74LVC153,AiP74LVC251,AiP74LVC257•触发器AiP74LVC273,AiP74LVC374,AiP74LVC377,AiP74LVC574AiPLVC1G79,AiPLVC1G80,AiPLVC1G175•锁存器AiP74LVC373,AiP74LVC573•移位寄存器AiP74LVC594,AiP74LVC595以上是“奥伟斯科技”分享的产品信息,如果您需要订购此款物料,请查看我们的官网与我们联系,非常感谢您的关注与支持!奥伟斯科技提供专业的智能电子锁触摸解决方案,并提供电子锁整套的芯片配套:低功耗触摸芯片、低功耗单片机、马达驱动芯片、显示驱动芯片、刷卡芯片、时针芯片、存储芯片、语音芯片、低压MOS管、TVS二极管;中微爱芯LCD显示驱动IC:AiP31107 AiP31107E AiP31108、AiP31108U、AiP31108E、AiP31066 AiP31066LC AiP31068 AiP31065 AiP31065L AiP31063 AiP31086U AiP31020 AiP31021 AiP31520 CS1621 AIP31621D AIP31621E CS1622 CS75823优势产品未尽详细,欢迎查询!。

HD74LV573A资料

Storage temperature

Tstg

–65 to 150

°C

Notes: The absolute maximum ratings are values which must not individually be exceeded, and furthermore, no two of which may be realized at the same time. 1. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed. 2. This value is limited to 5.5 V maximum. 3. The maximum package power dissipation was calculated using a junction temperature of 150°C.

Function Table

Inputs

OE

LE

D

Output Q

L

H

H

H

L

H

L

L

L

L

X

Q0

H

X

X

Z

Note: H: High level L: Low level X: Immaterial Z: High impedance Q0: Output level before the indicated steady state input conditions were established

IOZ

output current

2.3

74ls573中文资料

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

74LV573A中文资料

74LV573A中⽂资料PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74LV573ADBR ACTIVE SSOP DB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADBRE4ACTIVE SSOPDB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVR ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVRE4ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADW ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWE4ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWR ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWRE4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573AGQNRACTIVEBGA MI CROSTA R JUNI ORGQN201000TBDSNPBLevel-1-240C-UNLIMSN74LV573ANSR ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ANSRE4ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APW ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWE4ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWR ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRE4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRG4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWT ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWTE4ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ARGYR ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573ARGYRG4ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573AZQNRACTIVEBGA MI CROSTA R JUNI ORZQN201000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part ina new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /doc/c811093619.html/productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)andAntimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.。

74573引脚图

8D数据锁存器和373一样

74573引脚图

三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

真值表:

输出enable

Latch

ENABLE启

用

D

输出

O

L H H H L H L L L L X QO H X X Z

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平

引脚功能表:

Operating Conditions 操作条件。

常用数字元件

SN74AHC02DR:四2输入正或非门

SN74AHC02N:四2输入正或非门

SN74AHC1G02DBVR:单2输入正或非门

SN74AHC1G02DCKT:单2输入正或非门

SN74AHCT02D:四2输入正或非门

SN74AHCT02DR:四2输入正或非门

SN74AHC00DR:四2输入正与非门

SN74AHC00N:四2输入正与非门

SN74AHC132PW:四2输入施密特触发正与非门

SN74AHC1G00DBVR:单2输入正与非门

SN74AHC1G00DCKR:单2输入正与非门

SN74AHC1G00DCKT:单2输入正与非门

SN74AHCT00D:四2输入正与非门

数字逻辑器件 异或门

CD4070BE:四异或门

SN74AC86D:四2输入异或门

SN74ACT86N:四2输入异或门

SN74AHC1G86DBVR:单2输入异或门

SN74AHC1G86DCKT:单2输入异或门

SN74AHC86D:四2输入异或门

SN74AHC86N:四2输入异或门

SN74HC00N:四2输入正与非门

SN74HC132D:四2输入施密特触发正与非门

SN74HC20N:双4输入正与非门

SN74HCT00D:四2输入正与非门

SN74HCT00N:四2输入正与非门

SN74LVC10AD:三3输入正与非门

SN74LVC1G00DBVR:单2输入正与非门

SN74LVC1G02DCKR:单2输入正或非门

SN74LVC1G02DCKT:单2输入正或非门

74LV573A中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74LV573ADBR ACTIVE SSOP DB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADBRE4ACTIVE SSOPDB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVR ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVRE4ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADW ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWE4ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWR ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWRE4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573AGQNRACTIVEBGA MI CROSTA R JUNI ORGQN201000TBDSNPBLevel-1-240C-UNLIMSN74LV573ANSR ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ANSRE4ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APW ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWE4ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWR ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRE4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRG4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWT ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWTE4ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ARGYR ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573ARGYRG4ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573AZQNRACTIVEBGA MI CROSTA R JUNI ORZQN201000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part ina new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and todiscontinue any product or service without notice. Customers should obtain the latest relevant informationbefore placing orders and should verify that such information is current and complete. All products are soldsubject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extentTI deems necessary to support this warranty. Except where mandated by government requirements, testingof all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsiblefor their products and applications using TI components. To minimize the risks associated with customerproducts and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patentright, copyright, mask work right, or other TI intellectual property right relating to any combination, machine,or process in which TI products or services are used. Information published by TI regarding third-partyproducts or services does not constitute a license from TI to use such products or services or a warranty orendorsement thereof. Use of such information may require a license from a third party under the patents orother intellectual property of the third party, or a license from TI under the patents or other intellectualproperty of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices.Reproduction of this information with alteration is an unfair and deceptive business practice. TI is notresponsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI forthat product or service voids all express and any implied warranties for the associated TI product or serviceand is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotive/broadband DSP BroadbandControl /digitalcontrolDigitalInterface Logic Military /military Power Mgmt Optical Networking /opticalnetworkSecurity /securityMicrocontrollers Low Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless/wirelessMailing Address: Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright © 2007, Texas Instruments Incorporated。

74LVX573MTR,74LVX573TTR, 规格书,Datasheet 资料

1/13August 2004sHIGH SPEED:t PD =6.4ns (TYP.) at V CC = 3.3V s 5V TOLERANT INPUTSs POWER-DOWN PROTECTION ON INPUTS sINPUT VOLTAGE LEVEL:V IL = 0.8V, V IH = 2V at V CC =3V sLOW POWER DISSIPATION:I CC = 4 µA (MAX.) at T A =25°C sLOW NOISE:V OLP = 0.3V (TYP .) at V CC =3.3VsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4 mA (MIN) at V CC = 3V sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 3.6V (1.2V Data Retention)sPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 573sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe 74LVX573 is a low voltage CMOS OCTAL D-TYPE LATCH with 3 STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology. It is ideal for low power, battery operated and low noise 3.3V applications.This 8 bit D-Type latch is controlled by a latch enable input (LE) and an output enable input (OE).While the LE input is held at a high level, the Q outputs will follow the data input precisely.When the LE is taken low, the Q outputs will be latched precisely at the logic level of D input data.While the (OE) input is low, the 8 outputs will be in a normal logic state (high or low logic level) and while high level the outputs will be in a high impedance state.Power down protection is provided on all inputs and 0 to 7V can be accepted on inputs with no regard to the supply voltage.This device can be used to interface 5V to 3V. It combines high speed performance with the true CMOS low power consumption.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74LVX573LOW VOLTAGE CMOS OCTAL D-TYPE LATCH (3-STATE NON INV.) WITH 5V TOLERANT INPUTSTable 1: Order CodesPACKAGE T & R SOP 74LVX573MTR TSSOP74LVX573TTR74LVX5732/13Figure 2: Input Equivalent CircuitTable 2: Pin DescriptionTable 3: Truth TableX : Don’t CareZ : High Impedance* : Q Outputs are Latched at the time when the LE INPUT is taken low logic levelFigure 3: Logic DiagramThis logic diagram has not be used to estimate propagation delaysPIN N°SYMBOL NAME AND FUNCTION 1OE 3 State Output Enable Input (Active LOW)2, 3, 4, 5, 6, 7, 8, 9D0 to D7 Data Inputs12, 13, 14, 15, 16, 17, 18, 19Q0 to Q73-State Latch Outputs11LE Latch Enable Input 10GND Ground (0V)20V CCPositive Supply VoltageINPUTSOUTPUTOE LE DQH X X Z L L X NOCHANGE*L H L L LHHH74LVX5733/13Table 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not impliedTable 5: Recommended Operating Conditions1) Truth Table guaranteed: 1.2V to 3.6V 2) V IN from 0.8V to 2.0VTable 6: DC SpecificationsSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage -0.5 to +7.0V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current - 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 25mA I CC or I GND DC V CC or Ground Current± 50mA T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage (note 1) 2 to 3.6V V I Input Voltage 0 to 5.5V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time (note 2) (V CC = 3V)0 to 100ns/VSymbolParameterTest ConditionValue Unit V CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V3.0 2.0 2.0 2.03.6 2.42.42.4V ILLow Level Input Voltage2.00.50.50.5V3.00.80.80.83.60.80.80.8V OHHigh Level Output Voltage2.0I O =-50 µA 1.9 2.0 1.9 1.9V3.0I O =-50 µA 2.9 3.02.9 2.93.0I O =-4 mA 2.582.482.4V OLLow Level Output Voltage2.0I O =50 µA 0.00.10.10.1V3.0I O =50 µA 0.00.10.10.13.0I O =4 mA 0.360.440.55I OZ High Impedance Output Leakage Current3.6V I = V IH or V IL V O = V CC or GND ±0.25± 2.5± 2.5µA I I Input Leakage Current 3.6V I = 5V or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current3.6V I = V CC or GND44040µA74LVX5734/13Table 7: Dynamic Switching Characteristics1) Worst case package.2) Max number of outputs defined as (n). Data inputs are driven 0V to 3.3V, (n-1) outputs switching and one output at GND.3) Max number of data inputs (n) switching. (n-1) switching 0V to 3.3V. Inputs under test switching: 3.3V to threshold (V ILD ), 0V to threshold (V IHD ), f=1MHz.Table 8: AC Electrical Characteristics (Input t r = t f = 3ns)1) Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switch-ing in the same direction, either HIGH or LOW 2) Parameter guaranteed by design (*) Voltage range is 3.3V ± 0.3VSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V OLP Dynamic Low Voltage Quiet Output (note 1, 2) 3.3C L = 50 pF0.30.8VV OLV -0.8-0.3V IHD Dynamic High Voltage Input (note 1, 3) 3.32.0V ILDDynamic Low Voltage Input (note 1, 3)3.30.8SymbolParameterTest ConditionValue UnitV CC (V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHLPropagation Delay Time LE to Q2.7158.215.6 1.018.5 1.018.5ns2.75010.719.1 1.022.0 1.022.03.3(*)15 6.410.1 1.012.0 1.012.03.3(*)508.913.6 1.015.5 1.015.5t PLH t PHLPropagation Delay Time D to Q2.7157.614.5 1.017.5 1.017.5ns2.75010.118.0 1.021.0 1.021.03.3(*)15 5.99.3 1.011.0 1.011.03.3(*)508.412.8 1.014.5 1.014.5t PZL t PZHOutput Enable Time2.7157.815.0 1.018.5 1.018.5ns2.75010.318.5 1.022.0 1.022.03.3(*)15 6.19.7 1.012.0 1.012.03.3(*)508.613.2 1.015.5 1.015.5t PLZ t PHZ Output Disable Time2.75012.119.1 1.022.0 1.022.0ns3.3(*)5010.113.6 1.015.5 1.015.5t W LE pulse Width, HIGH2.750 6.57.57.5ns 3.3(*)50 5.0 5.0 5.0t S Setup Time D to LE HIGH or LOW 2.750 5.0 5.0 5.0ns 3.3(*)50 3.5 3.5 3.5t hHold Time D to LEHIGH or LOW 2.750 1.5 1.5 1.5ns 3.3(*)50 1.5 1.5 1.5t OSLH t OSHLOutput to Output Skew Time (note1,2)2.7500.5 1.0 1.5 1.5ns3.3(*)500.5 1.01.51.574LVX5735/13Table 9: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /8 (per circuit)Figure 4: Test CircuitC L =15/50pF or equivalent (includes jig and probe capacitance)R L = R1 = 1K Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 3.34101010pF C OUT OutputCapacitance3.36pF C PDPower Dissipation Capacitance (note 1)3.3f IN = 10MHz29pF TESTSWITCH t PLH , t PHL Opent PZL , t PLZ V CC t PZH , t PHZGND74LVX573Figure 5: Waveform - LE To Qn Propagation Delays, Le Minimun Pulse Width, Dn To LE Setup And Hold Times (f=1MHz; 50% duty cycle)Figure 6: Waveform - Output Enable And Disable Times (f=1MHz; 50% duty cycle)74LVX573 Figure 7: Waveform - Propagation Delay Time (f=1MHz; 50% duty cycle)7/1374LVX5738/13DIM.mm.inchMIN.TYP MAX.MIN.TYP.MAX.A 2.35 2.650.0930.104 A10.10.300.0040.012 B0.330.510.0130.020 C0.230.320.0090.013 D12.6013.000.4960.512 E7.47.60.2910.299 e 1.270.050H10.0010.650.3940.419 h0.250.750.0100.030 L0.4 1.270.0160.050 k0°8°0°8°ddd0.1000.004SO-20 MECHANICAL DATA0016022D74LVX5739/13DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c 0.090.200.0040.0079D 6.4 6.5 6.60.2520.2560.260E 6.2 6.4 6.60.2440.2520.260E1 4.34.4 4.480.1690.1730.176e 0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP20 MECHANICAL DATAcEbA2AE1D1PIN 1 IDENTIFICATIONA1LK e0087225C74LVX573Tape & Reel SO-20 MECHANICAL DATAmm.inch DIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T30.4 1.197 Ao10.8110.4250.433 Bo13.213.40.5200.528 Ko 3.1 3.30.1220.130 Po 3.9 4.10.1530.161 P11.912.10.4680.47610/1374LVX573 Tape & Reel TSSOP20 MECHANICAL DATAmm.inchDIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992C12.813.20.5040.519D20.20.795N60 2.362T22.40.882Ao 6.870.2680.276Bo 6.97.10.2720.280Ko 1.7 1.90.0670.075Po 3.9 4.10.1530.161P11.912.10.4680.47611/1374LVX573Table 10: Revision HistoryDate Revision Description of Changes 27-Aug-20044Ordering Codes Revision - pag. 1.12/1374LVX573 Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is grantedby implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are notauthorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronicsAll other names are the property of their respective owners© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America13/13。

74H573规格书

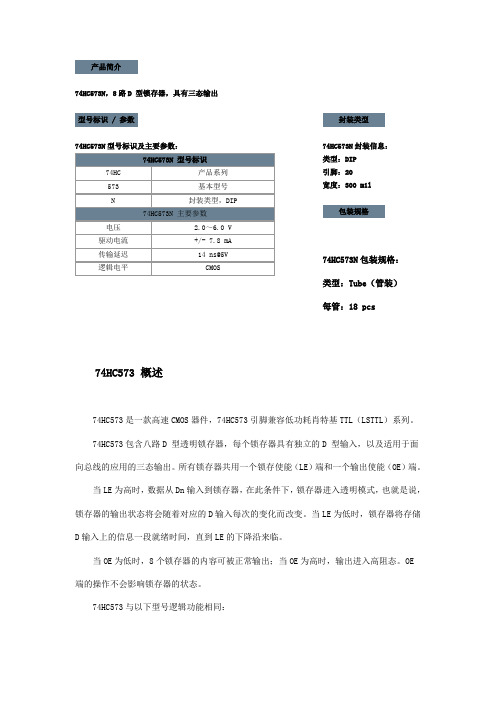

74HC573N,8路D 型锁存器,具有三态输出74HC573N型号标识及主要参数:74HC573N封装信息:类型:DIP引脚:20宽度:300 mil74HC573N包装规格:类型:Tube(管装)每管:18 pcs74HC573 概述74HC573是一款高速CMOS器件,74HC573引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC573包含八路D 型透明锁存器,每个锁存器具有独立的D 型输入,以及适用于面向总线的应用的三态输出。

所有锁存器共用一个锁存使能(LE)端和一个输出使能(OE)端。

当LE为高时,数据从Dn输入到锁存器,在此条件下,锁存器进入透明模式,也就是说,锁存器的输出状态将会随着对应的D输入每次的变化而改变。

当LE为低时,锁存器将存储D输入上的信息一段就绪时间,直到LE的下降沿来临。

当OE为低时,8个锁存器的内容可被正常输出;当OE为高时,输出进入高阻态。

OE端的操作不会影响锁存器的状态。

74HC573与以下型号逻辑功能相同:74HC563,但输出为反相74HC373,但引脚布局不同74HC573 特性∙输入输出分布在芯片封装的两侧,为微处理器提供简便的接口∙用于微控制器和微型计算机的输入输出口∙三态正相输出,用于面向总线的应用∙共用三态输出使能端∙逻辑功能与74HC563、74HC373相同∙遵循JEDEC标准no.7A∙ESD保护o HBM EIA/JESD22-A114-C超过2000 Vo MM EIA/JESD22-A115-A超过200 V∙温度范围o-40~+85 ℃o-40~+125。

74LV574N,112,74LV574DB,118,74LV574D,118,74LV574D,112,74LV574DB,112, 规格书,Datasheet 资料

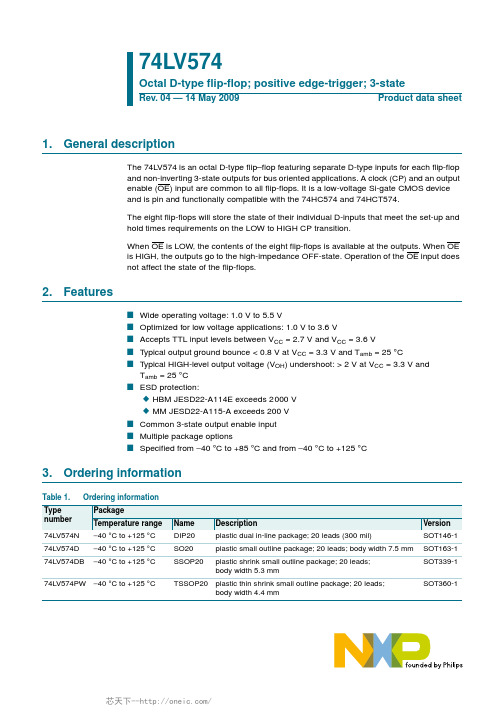

1.General descriptionThe 74LV574is an octal D-type flip–flop featuring separate D-type inputs for each flip-flop and non-inverting 3-state outputs for bus oriented applications.A clock (CP)and an output enable (OE) input are common to all flip-flops. It is a low-voltage Si-gate CMOS device and is pin and functionally compatible with the 74HC574 and 74HCT574.The eight flip-flops will store the state of their individual D-inputs that meet the set-up and hold times requirements on the LOW to HIGH CP transition.When OE is LOW,the contents of the eight flip-flops is available at the outputs.When OE is HIGH,the outputs go to the high-impedance OFF-state.Operation of the OE input does not affect the state of the flip-flops.2.FeaturesI Wide operating voltage: 1.0 V to 5.5 VI Optimized for low voltage applications: 1.0 V to 3.6 VI Accepts TTL input levels between V CC = 2.7 V and V CC = 3.6 VI Typical output ground bounce < 0.8 V at V CC = 3.3 V and T amb = 25°CI Typical HIGH-level output voltage (V OH ) undershoot: > 2 V at V CC = 3.3 V and T amb =25°C IESD protection:N HBM JESD22-A114E exceeds 2000V N MM JESD22-A115-A exceeds 200V I Common 3-state output enable input I Multiple package optionsISpecified from −40°C to +85°C and from −40°C to +125°C3.Ordering information74LV574Octal D-type flip-flop; positive edge-trigger; 3-stateRev. 04 — 14 May 2009Product data sheetTable 1.Ordering information Type number PackageTemperature range Name DescriptionVersion 74LV574N −40°C to +125°C DIP20plastic dual in-line package; 20 leads (300 mil)SOT146-174LV574D −40°C to +125°C SO20plastic small outline package; 20 leads; body width 7.5 mm SOT163-174LV574DB−40°C to +125°CSSOP20plastic shrink small outline package; 20 leads;body width 5.3 mmSOT339-174LV574PW −40°C to +125°CTSSOP20plastic thin shrink small outline package; 20 leads;body width 4.4 mmSOT360-14.Functional diagramFig 1.Logic symbol Fig 2.IEC logic symbolmna798D0D1D2D3D4D5D6D7OE CP Q0Q1Q2Q3Q4Q5Q6Q7111121314151617181998765432mna4461213141516171811C11EN1D1998765432Fig 3.Functional diagrammna8003-STATE OUTPUTSFF1to FF8Q0Q1Q2Q3Q4Q5Q6Q71213141516171819D0D1D2D3D4D5D6D7CP OE911187654325.Pinning information5.1Pinning5.2Pin descriptionFig 4.Logic diagrammna801Q4D4Q3D3Q2D2Q1D1Q0D0D FF1Q CP CPD FF2Q CPD FF3Q CPD FF4Q CPD FF5Q CPD FF6Q CPD FF7Q CPD FF8QCPOEQ5D5Q6D6Q 7D7Fig 5.Pin configuration DIP20, SO20Fig 6.Pin configuration SSOP20, TSSOP2074LV574OE V CC D0Q0D1Q1D2Q2D3Q3D4Q4D5Q5D6Q6D7Q7GND CP001aaj968123456789101211141316151817201974LV574OE V CC D0Q0D1Q1D2Q2D3Q3D4Q4D5Q5D6Q6D7Q7GND CP001aaj9691234567891012111413161518172019Table 2.Pin descriptionSymbol Pin DescriptionOE 1output enable input (active LOW)D0 to D72, 3, 4, 5, 6, 7, 8, 9data input GND 10ground (0 V)CP 11clock input (LOW to HIGH; edge triggered)Q0 to Q719, 18, 17, 16, 15, 14, 13, 12data output V CC20supply voltage6.Functional description[1]H =HIGH voltage levelh =HIGH voltage level one set-up time prior to the LOW to HIGH CP transition L =LOW voltage levell =LOW voltage level one set-up time prior to the LOW to HIGH CP transition Z =high-impedance OFF-state ↑=LOW to HIGH clock transition7.Limiting values[1]The input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]For DIP20 packages: above 70°C the value of P tot derates linearly with 12 mW/K.For SO20 packages: above 70°C the value of P tot derates linearly with 8 mW/K.For (T)SSOP20 packages: above 60°C the value of P tot derates linearly with 5.5 mW/K.Table 3.Function table [1]Operating mode Input Internal flip-flop OutputOECP Dn Qn Load and read register L ↑l L L L ↑h H H Load register and disable outputsH ↑l L Z H↑hHZTable 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Voltages are referenced to GND (ground = 0V).Symbol Parameter ConditionsMin Max Unit V CC supply voltage −0.5+7.0V I IK input clamping current V I <−0.5V or V I >V CC +0.5V [1]-±20mA I OK output clamping current V O <−0.5V or V O >V CC +0.5V [1]-±50mA I O output current V O =−0.5V to (V CC +0.5V)-±35mA I CC supply current -70mA I GND ground current −70-mA T stg storage temperature −65+150°C P tottotal power dissipationT amb =−40°C to +125°C [2]DIP20-750mW SO20, SSOP20 and TSSOP20-500mW8.Recommended operating conditionsTable 5.Recommended operating conditionsVoltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions Min Typ Max UnitV CC supply voltage[1] 1.0 3.3 5.5VV I input voltage0-V CC VV O output voltage0-V CC VT amb ambient temperature−40+25+125°C∆t/∆V input transition rise and fall rate V CC = 1.0 V to 2.0 V--500ns/VV CC = 2.0 V to 2.7 V--200ns/VV CC = 2.7 V to 3.6 V--100ns/VV CC = 3.6 V to 5.5 V--50ns/V [1]The static characteristics are guaranteed from V CC = 1.2V to V CC = 5.5V, but LV devices are guaranteed to function down toV CC=1.0V (with input levels GND or V CC).9.Static characteristicsTable 6.Static characteristicsAt recommended operating conditions. Voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions−40°C to+85°C−40°C to+125°C UnitMin Typ[1]Max Min MaxV IH HIGH-level input voltage V CC= 1.2 V0.9--0.9-VV CC= 2.0 V 1.4-- 1.4-VV CC = 2.7 V to 3.6 V 2.0-- 2.0-VV CC = 4.5 V to 5.5 V0.7V CC--0.7V CC-VV IL LOW-level input voltage V CC= 1.2 V--0.3-0.3VV CC= 2.0 V--0.6-0.6VV CC = 2.7 V to 3.6 V--0.8-0.8VV CC = 4.5 V to 5.5 V--0.3V CC-0.3V CC VV OH HIGH-level output voltage V I = V IH or V ILI O =−100µA; V CC = 1.2V- 1.2---VI O =−100µA; V CC = 2.0V 1.8 2.0- 1.8-VI O =−100µA; V CC = 2.7V 2.5 2.7- 2.5-VI O =−100µA; V CC = 3.0V 2.8 3.0- 2.8-VI O =−100µA; V CC = 4.5V 4.3 4.5- 4.3-VI O =−8 mA; V CC = 3.0V 2.4 2.82- 2.2-VI O =−16 mA; V CC = 4.5V 3.6 4.2- 3.5-V[1]Typical values are measured at T amb = 25°C.10.Dynamic characteristicsV OLLOW-level output voltageV I = V IH or V ILI O = 100µA; V CC = 1.2V -0---V I O = 100µA; V CC = 2.0V -00.2-0.2V I O = 100µA; V CC = 2.7V -00.2-0.2V I O = 100µA; V CC = 3.0V -00.2-0.2V I O = 100µA; V CC = 4.5V -00.2-0.2V I O = 8 mA; V CC = 3.0V -0.250.40-0.50V I O = 16 mA; V CC = 4.5V-0.350.55-0.65V I I input leakage current V I =V CC or GND;V CC =5.5V -- 1.0- 1.0µA I OZOFF-state output currentV I =V IH or V IL ;V O =V CC or GND;V CC =5.5V--5-10µAI CC supply currentV I = V CC or GND; I O = 0A;V CC =5.5V--20-160µA ∆I CC additional supply current per input; V I = V CC − 0.6V;V CC =2.7V to 3.6V--500-850µA C Iinput capacitance-3.5---pFTable 6.Static characteristics …continuedAt recommended operating conditions. Voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions −40°C to +85°C −40°C to +125°C Unit MinTyp [1]MaxMinMaxTable 7.Dynamic characteristicsVoltages are referenced to GND (ground =0V). For test circuit see Figure 10.Symbol Parameter Conditions−40°C to +85°C −40°C to +125°C UnitMinTyp [1]Max Min Max t pdpropagation delay CP to Qn; see Figure 7[2]V CC = 1.2 V -80---ns V CC = 2.0 V -2734-43ns V CC = 2.7 V-2025-31ns V CC = 3.0 V to 3.6 V; C L =15pF [3]-13---ns V CC = 3.0 V to 3.6 V [3]-1520-25ns V CC = 4.5 V to 5.5 V--17-21ns t enenable time OE to Qn; see Figure 8[4]V CC = 1.2 V -70---ns V CC = 2.0 V -2434-43ns V CC = 2.7 V -1825-31ns V CC = 3.0 V to 3.6 V [3]-1320-25ns V CC = 4.5 V to 5.5 V--17-21ns[1]Typical values are measured at T amb =25°C.[2]t pd is the same as t PLH and t PHL .[3]Typical value measured at V CC = 3.3 V .[4]t en is the same as t PZH and t PZL .[5]t dis is the same as t PHZ and t PLZ .[6]C PD is used to determine the dynamic power dissipation (P D in µW).P D =C PD ×V CC 2×f i ×N +∑(C L ×V CC 2×f o )where:f i =input frequency in MHz;f o =output frequency in MHz;C L =output load capacitance in pF;V CC =supply voltage in V;N =number of inputs switching;∑(C L ×V CC 2×f o )=sum of outputs.t disdisable timeOE to Qn;Figure 8[5]V CC = 1.2 V -75---ns V CC = 2.0 V -2727-34ns V CC = 2.7 V -2121-26ns V CC = 3.0 V to 3.6 V [3]-1617-21ns V CC = 4.5 V to 5.5 V[3]--15-18ns t Wpulse widthCP , HIGH or LOW; see Figure 7V CC = 2.0 V 349-41-ns V CC = 2.7 V 256-30-ns V CC = 3.0 V to 3.6 V[3]205-24-ns t suset-up timeDn to CP; see Figure 9V CC = 1.2 V -10---ns V CC = 2.0 V 224-26-ns V CC = 2.7 V 163-19-ns V CC = 3.0 V to 3.6 V[3]132-15-ns t hhold timeDn to CP; see Figure 9V CC = 1.2 V -−10---ns V CC = 2.0 V 5−4-5-ns V CC = 2.7 V 5−3-5-ns V CC = 3.0 V to 3.6 V[3]5−2-5-ns f maxmaximum frequencysee Figure 7V CC =2.0 V 1540-12-MHz V CC =2.7V 1958-16-MHz V CC =3.0V to 3.6V[3]2470-20-MHz C PDpower dissipation capacitanceC L =50pF; f i = 1 MHz;V I =GND to V CC[6]25pFTable 7.Dynamic characteristics …continuedVoltages are referenced to GND (ground =0V). For test circuit see Figure 10.Symbol Parameter Conditions −40°C to +85°C −40°C to +125°C UnitMin Typ [1]Max Min Max11.WaveformsMeasurement points are given in Table 8.V OL and V OH are typical output voltage levels that occur with the output load.Fig 7.The clock (CP) to output (Qn) propagation delays, the clock pulse (CP) and the maximum clock pulse frequencymna894CP inputQn outputt PHLt PLHt W 1/f maxV MV OHV IGNDV OLV MMeasurement points are given in Table 8.V OL and V OH are typical output voltage levels that occur with the output load.Fig 8.Enable and disable timesmna644t PLZt PHZoutputs disabledoutputs enabledV YV Xoutputs enabledoutput LOW-to-OFF OFF-to-LOWoutput HIGH-to-OFF OFF-to-HIGHOE inputV IV OLV OHV CCV MGNDGNDt PZLt PZHV MV MMeasurement points are given in Table 8.The shaded areas indicate when the input is permitted to change for predictable output performance.V OL and V OH are typical output voltage levels that occur with the output load.Fig 9.The data set-up and hold times for the Dn input to the CP input)mna202GNDGNDt ht ht sut suV MV MV MV IV OHV OLV IQn outputCP inputDn inputTable 8.Measurement pointsSupply voltageInput Output V CC V M V M V xV y< 2.7 V0.5V CC 0.5V CC V OL + 0.3V V OH − 0.3V 2.7V to 3.6V 1.5 V 1.5 V V OL + 0.3V V OH − 0.3V ≥ 4.5 V0.5V CC0.5V CCV OL + 0.3VV OH − 0.3VTest data is given in T able 9.Definitions for test circuit:R L = Load resistance.C L = Load capacitance including jig and probe capacitance.R T = Termination resistance should be equal to output impedance Z o of the pulse generator.V EXT = External voltage for measuring switching times.Fig 10.Test circuit for measuring switching times V M V Mt Wt W10 %90 %0 VV IV I negative pulsepositive pulse0 VV MV M90 %10 %t ft r t rt f 001aae331V EXTV CCV I V ODUTC LR TR LR LGTable 9.Test dataSupply voltageInput Load V EXT V CC V I t r , t f C L R L t PHL , t PLH t PZH , t PHZ t PZL , t PLZ < 2.7 V V CC ≤ 2.5 ns 50 pF 1k Ωopen GND 2V CC 2.7V to 3.6V 2.7 V ≤ 2.5 ns 15 pF , 50 pF 1k Ωopen GND 2V CC ≥ 4.5 VV CC≤ 2.5 ns50 pF1k ΩopenGND2V CC12.Package outlineFig 11.Package outline SOT146-1 (DIP20)UNIT Amax.12b 1c DEe M H L REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITA mm inchesDIMENSIONS (inch dimensions are derived from the original mm dimensions)SOT146-199-12-2703-02-13A min. A max.b Z max.w M E e 11.731.300.530.380.360.2326.9226.54 6.406.22 3.603.050.2542.547.628.257.8010.0 8.324.20.51 3.20.0680.0510.0210.0150.0140.0091.0601.0450.250.240.140.120.010.10.30.320.310.390.330.0780.170.020.13SC-603MS-001M Hc(e )1M EALs e a t i n g p l a n eA 1w Mb 1eDA 2Z2011110bEpin 1 index0510 mmscaleNote1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.(1)(1)(1)DIP20: plastic dual in-line package; 20 leads (300 mil)SOT146-1UNITAmax.A1A2A3b p c D(1)E(1)(1)e H E L L p Q ZywvθREFERENCESOUTLINE VERSIONEUROPEANPROJECTIONISSUE DATE IEC JEDEC JEITAmm inches 2.650.30.12.452.250.490.360.320.2313.012.67.67.41.2710.6510.001.11.00.90.48oo0.250.1DIMENSIONS (inch dimensions are derived from the original mm dimensions)Note1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included. 1.1 0.4SOT163-11020w M b p detail XZe 111Dy0.25075E04 MS-013 pin 1 index0.10.0120.0040.0960.0890.0190.0140.0130.0090.510.490.300.290.051.40.0550.4190.3940.0430.0390.0350.0160.010.250.010.0040.0430.0160.010510 mmscaleXθAA1A2H EL pQEcLv M A(A )3ASO20: plastic small outline package; 20 leads; body width 7.5 mm SOT163-199-12-2703-02-19Fig 12.Package outline SOT163-1 (SO20)Fig 13.Package outline SOT339-1 (SSOP20)UNIT A 1A 2A 3b p c D (1)E (1)e H E L L p Q (1)Z y w v θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITAmm0.210.051.801.650.380.250.200.097.47.05.45.20.657.97.60.90.70.90.580oo 0.131.250.20.1DIMENSIONS (mm are the original dimensions)Note1. Plastic or metal protrusions of 0.2 mm maximum per side are not included.1.030.63SOT339-1MO-15099-12-2703-02-19Xw MθAA 1A 2b pD H EL p Qdetail XE Z ecLv M A(A )3A1102011y0.25pin 1 index0 2.5 5 mmscaleSSOP20: plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1Amax.2Fig 14.Package outline SOT360-1 (TSSOP20)UNIT A 1A 2A 3b p c D (1)E (2)(1)e H E L L p Q Z y w v θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITAmm0.150.050.950.800.300.190.20.16.66.44.54.30.656.66.20.40.30.50.280oo 0.130.10.21DIMENSIONS (mm are the original dimensions)Notes1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.0.750.50SOT360-1MO-15399-12-2703-02-19w Mb pD Ze0.251102011pin 1 indexθAA 1A 2L p Qdetail XL(A )3H EE cv M AXAy0 2.5 5 mmscaleTSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1Amax.1.113.AbbreviationsTable 10.AbbreviationsAcronym DescriptionCMOS Complementary Metal Oxide SemiconductorDUT Device Under TestESD ElectroStatic DischargeHBM Human Body ModelMM Machine ModelTTL T ransistor-Transistor Logic14.Revision historyTable 11.Revision historyDocument ID Release date Data sheet status Change notice Supersedes 74LV574_420090514Product data sheet-74LV574_3 Modifications:•T ypo removed from Figure8 and Table8 adapted accordingly74LV574_320090416Product data sheet-74LV574_2 74LV574_219970203Product specification-74LV574_1 74LV574_119980610Product specification--15.Legal information15.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s)described in this document may have changed since this document was published and may differ in case of multiple devices.The latest product status information is available on the Internet at URL .15.2DefinitionsDraft —The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet —A short data sheet is an extract from a full data sheet with the same product type number(s)and title.A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.15.3DisclaimersGeneral —Information in this document is believed to be accurate andreliable.However,NXP Semiconductors does not give any representations or warranties,expressed or implied,as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes —NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice.This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use —NXP Semiconductors products are not designed,authorized or warranted to be suitable for use in medical, military, aircraft,space or life support equipment, nor in applications where failure ormalfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmentaldamage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications —Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values —Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134)may cause permanent damage to the device.Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in theCharacteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale —NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale,as published at /profile/terms , including those pertaining to warranty,intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license —Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant,conveyance or implication of any license under any copyrights,patents or other industrial or intellectual property rights.Export control —This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.15.4TrademarksNotice:All referenced brands,product names,service names and trademarks are the property of their respective owners.16.Contact informationFor more information, please visit:For sales office addresses, please send an email to:salesaddresses@Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development.Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheetProductionThis document contains the product specification.17.Contents1General description. . . . . . . . . . . . . . . . . . . . . . 12Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Ordering information. . . . . . . . . . . . . . . . . . . . . 14Functional diagram . . . . . . . . . . . . . . . . . . . . . . 25Pinning information. . . . . . . . . . . . . . . . . . . . . . 35.1Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 36Functional description . . . . . . . . . . . . . . . . . . . 47Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 48Recommended operating conditions. . . . . . . . 59Static characteristics. . . . . . . . . . . . . . . . . . . . . 510Dynamic characteristics . . . . . . . . . . . . . . . . . . 611Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 812Package outline . . . . . . . . . . . . . . . . . . . . . . . . 1113Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 1514Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1515Legal information. . . . . . . . . . . . . . . . . . . . . . . 1615.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . 1615.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1615.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 1615.4T rademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 1616Contact information. . . . . . . . . . . . . . . . . . . . . 1617Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2009.All rights reserved.For more information, please visit: For sales office addresses, please send an email to: salesaddresses@Date of release: 14 May 2009。

KK74LV573DW中文资料

RECOMMENDED OPERATING CONDITIONS

Symbol VCC VI VO TA tr, tf DC Supply Voltage DC Input Voltage DC Output Voltage Operating Temperature, All Package Types Input Rise and Fall Time (Figure 1) 0 V ≤ VCC ≤ 2.0 V 2.0 V ≤ VCC ≤ 2.7 V 2.7 V ≤ VCC ≤ 3.6 V 3.6 V ≤ VCC ≤ 5.5 V Parameter Min 1.2 0 0 -40 0 0 0 0 Max 5.5 VCC VCC +125 500 200 100 50 Unit V V V °C ns

V V µА µА mA

IOZ

3-state output VI (11) = VIH VO =VCC or 0 V

5.5

-

±0.5

-

±0.5

-

±5

-

±10

µА

3

元器件交易网

KK74LV573

AC ELECTRICAL CHARACTERISTICS (CL=50 pF, tr=tf=2.5 ns)

VIL

LOW level output voltage

V

VOH

HIGH level VI = VIH or VIL output IO = -100 µА voltage

V

VI = VIH or VIL IO = -8 mА VI = VIH or VIL IO = -16 mА VOL LOW level output voltage VI = VIH or VIL IO = 100 µА

74ls573工作原理

74ls573工作原理Title: Understanding the Working Principle of 74LS573The 74LS573 is a 3-state octal D-type latch with three-state outputs. It is designed to operate with low power consumption and high speed, making it a popular choice in various digital circuits.74LS573是一个具有三态输出的3态8位D型锁存器。

它设计用于低功耗和高速操作,因此在各种数字电路中备受欢迎。

The latch function of the 74LS573 allows it to store and retain data even when the input signals change. This is achieved through the use of internal latches that capture the data on the rising edge of the latch enable (LE) input.74LS573的锁存功能使其能够在输入信号改变时存储和保留数据。

这是通过内部锁存器实现的,这些锁存器在锁存使能(LE)输入的上升沿捕获数据。

When the LE input is high, the data present on the D inputs is latched and appears on the Q outputs. Conversely, when LE is low, the Q outputs are in a high-impedance state, effectively disconnecting them from the internal circuitry.当LE输入为高电平时,D输入上的数据被锁存并出现在Q输出上。

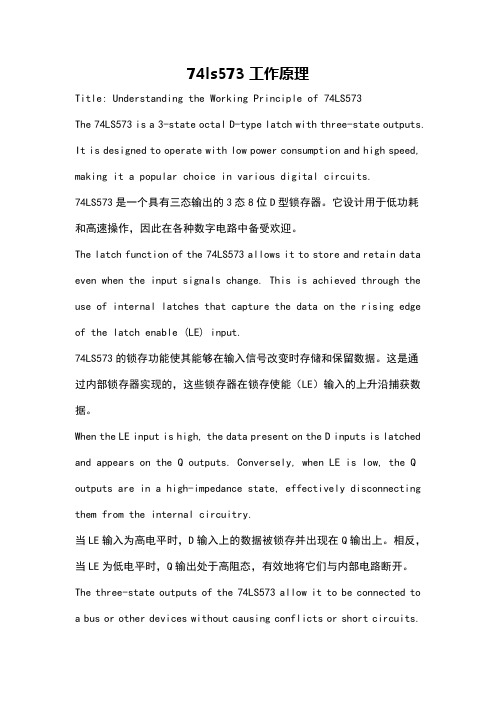

74CH573锁存器的功能

174CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制。

74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低电压激活:1是低电压激活芯片2~9脚是数据的输入脚从D0到D710脚是接地11脚是高电压激活芯片12~19脚是数据的输出脚1.真值表74HC573真值表,意思如下:第一行/第二行:当OE=0、LE=1时,输出端数据等于输入端数据; 第三行:当OE=0、LE=0时,输出端保持不变;第四行:当OE=1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,atch是锁存的意思; Dn:第n路输入数据; On:第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:a. OE=0;b.先将数据从单片机的口线上输出到Dn; c.再将LE从0->1->0 ;d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns 级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A //将数据输出到并行数据端口 CLR LESETB LECLR LE ; //上面三条指令完成LE的波形从0->1->0的变化74LS573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端.。

74LS573

© 2000 Fairchild Semiconductor Corporation DS009814October 1988Revised March 2000DM74LS573 Octal D-Type Latch with 3-STATE OutputsDM74LS573Octal D-Type Latch with 3-STATE OutputsGeneral DescriptionThe DM74LS573 is a high speed octal latch with buffered common Latch Enable (LE) and buffered common Output Enable (OE) inputs.This device is functionally identical to the DM74LS373, but has different pinouts.Featuress Inputs and outputs on opposite sides of package allow-ing easy interface with microprocessors s Useful as input or output port for microprocessors s Functionally identical to DM74LS373s Input clamp diodes limit high speed termination effects s Fully TTL and CMOS compatibleOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Logic Symbol V CC = Pin 20GND = Pin 10Connection DiagramPin DescriptionsFunction TablesL = LOW State H = HIGH State X = Don't CareZ = High Impedance State Q O = Previous Condition of OOrder Number Package NumberPackage DescriptionDM74LS573WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide DM74LS573NN20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePin Names DescriptionD0–D7Data InputsLE Latch Enable Input (Active HIGH)OE 3-STATE Output Enable Input (Active LOW)O0–O73-STATE Latch OutputsOutput Latch D Output Enable Enable O L H H H L H L L L L X Q O HXXZ 2D M 74L S 573Absolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsElectrical CharacteristicsOver recommended operating free air temperature range (unless otherwise noted)Note 2: All typicals are at V CC = 5V, T A = 25°C.Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.Supply Voltage 7V Input Voltage7VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range−65°C to +150°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Input Current −2.6mA I OL LOW Level Output Current 24mA T AFree Air Operating Temperature70°CSymbol ParameterConditionsMinTyp Max Units (Note 2)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max, 2.7 3.4VOutput Voltage V IL = Max V OLLOW Level V CC = Min, I OL = Max,0.350.5Output VoltageV IH = MinV I OL = 4 mA, V CC = Min 0.250.4I I Input Current @ Max Input Voltage V CC = Max, V I = 7V 1mA I IH HIGH Level Input Current V CC = Max, V I = 2.7V 20µA I IL LOW Level Input Current V CC = Max, V I = 0.4V −0.4mA I OS Short Circuit V CC = Max −30−130mA Output Current (Note 3)I CC Supply Current V CC = Max 50mA I OZH 3-STATE Output V CC = V CCH 20µA OFF Current HIGH V OZH = 2.7V I OZL3-STATE Output V CC = V CCH −20µAOFF Current LOWV OZL = 0.4VDM74LS573 Switching Characteristicsat V CC= 5V and T A= 25°CR L= 2 kΩ,Symbol Parameter C L= 50 pF UnitsMin Maxt PLH Propagation Delay27nst PHL Data to Q18t PLH Propagation Delay36nst PHL LE to Q25t PZH3-STATE Enable Time20nst PZL OE to Q25t PHZ3-STATE Enable Time20nst PLZ OE to Q25t S(H)Setup Time (HIGH/LOW)3nst S(L)Data to LE7t H(H)Hold Time (HIGH/LOW)10nst H(L)Data to LE10t W(H)Pulse Width (HIGH)15ns Data to LE 4D M 74L S 573Physical Dimensionsinches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WidePackage Number M20B5DM74LS573 Octal D-Type Latch with 3-STATE OutputsPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N20AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.This datasheet has been downloaded from:Free DownloadDaily Updated Database100% Free Datasheet Search Site100% Free IC Replacement Search SiteConvenient Electronic DictionaryFast Search SystemAll Datasheets Cannot Be Modified Without PermissionCopyright © Each Manufacturing Company。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DIP20:plastic dual in-line package; 20 leads (300 mil)SOT146-1

SO20:plastic small outline package; 20 leads; body width 7.5 mm SOT163-1

SSOP20:plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1

TSSOP20:plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1

NOTES

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products,including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright,or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

LIFE SUPPORT APPLICATIONS Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices,or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips

Semiconductors reserves the right to make changes at any time without notice in order to improve design

and supply the best possible product.

Philips Semiconductors

811 East Arques Avenue

P .O. Box 3409

Sunnyvale, California 94088–3409

Telephone 800-234-7381DEFINITIONS

Data Sheet Identification

Product Status Definition Objective Specification Preliminary Specification Product Specification Formative or in Design Preproduction Product Full Production

This data sheet contains the design target or goal specifications for product development. Specifications

may change in any manner without notice.

This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes