基于CORDIC算法数字下变频器设计

基于改进型Cordic算法数字下变频FPGA实现

r e f d i ta a e v r e n ma l . i i b K e wo d Cod cag r h ;NCO ;r tt n drcin;FP y rs r i o t m l i oai i to o e GA

数字下变频作 为连接 中频 A D转换 器和基 带 数 / 字信号处理单 元 的桥梁 ,已成为 软件 无 线 电接 收 机

和减小精度 ,文 中重点叙述 了改进 型的 C ri 算法原理 ,并通过原理进行 了 F G odc P A设计 ,最后给 出了 Q at I ur sI仿 u

真结果,并在 Maa tb中得 到 了验证 。 l 关键词 C ri 算法 ;数字控制振荡器;旋转方向 ;F G odc PA

T 91 N 1 文 献标 识 码 A 文章 编 号 10 72 (08 0 0 3— 5 07— 80 20 )2— 6 0

ain a d s le rcso . A e in wih FP t n malrp e iin o d sg t GA s pe e td a d smu ae t u ru I Smu ain rs ls i r sn e n i ltd wi q at sI. i lt ut h o e

输 入信号分为 I ,Q分量 ,分别与 N O产 生的 C

得到最低 输 出频 率 为

=f , = JM。如果 每次 6J2r f t

的相位增量选择为 的 倍 ,则得到 =f 2r 6 '= J r

收 稿 日期 :2O .7 1 O 7 0 .8 作者 简 介 :余 捷 (9 2一) 男 ,硕 士研 究 生 。研 究 方 向 : 18 ,

进 一步可 推得

2

( 1一Ytn ) o0 1 0 c s a () 5

基于CORDIC算法通用数字调制器的FPGA设计

De i n o e r ld g t lm o ul t r b s d o sg fg ne a i ia d a o a e n CORDI a g rt m nd FPGA C l o ih a

L INe g fn E n - g a

( e ate tfP yi n l t nc n i ei , i nTah r U i ri , i t74 0 , hn ) D pr n hs s dEe r iE gn r g Wen eces n esy Wen l 100 C ia m o ca co e n a v t o

雷 能 芳

( 南 师 范 学院 物理 与 电子 工程 系 ,陕 西 渭 南 7 4 0 ) 渭 100

摘 要 :通 信 系统 的振 幅键 控 ( K) 移 频键 控 ( S 和移 相 键 控 ( S 是 数 字 调 制 的 3种 基 本 信 号 形 式 。 而数 字 调 制 AS 、 F K) P K)

器载 波 的 产 生 通 常 都 是 基 于查 找 表 的方 法 , 了达 到 高 精 度 要 求 , 为 需要 耗 费 大 量 的 R M 资 源去 建 立 庞 大 的查 找 表 。 O 文 中提 出 了一 种 基 于 流 水 线 C R I O D C算 法 通 用 数 字 调 制 器 的 F G 实现 方 案 , 以有 效地 节省 F G 的硬 件 资 源 . PA 可 PA 提 高运 算 的速 度 。文 章 最后 给 出了该 方 案 的 硬 件 测 试 结 果 , 证 了设 计 的 正 确性 。而且 整 个 系统 便 于编 程 、 改 以及 验 修

升级改进。

关 键 词 : 用调 制 器 ; O D C 算 法 :流 水 线 ; P A 通 C R I FG 中 图 分 类 号 : N 1 T 9l 文献 标 识 码 : A 文 章编 号 :1 7 — 2 6 2 1 ) 7 0 6 — 3 6 4 6 3 (0 10 — 0 8 0

基于流水线CORDIC算法的数字下变频实现

I lme t t n o mp e n a i fDDC s d o i ei e o Ba e n P p l d CORDI Al o ih n C g rt m

Z NG Jn 。 i —o g HE i GE Ln d n

w ih r q i s a h g o u fROM o a he e hg e ou in h i p p rp r o e i ei e r h tc u o mpe na in h c e ur u e v l me o e t c iv ih rs l t .T s a e o p s s a p p l d a c i t r fri l me tt o n e e o o C o P fDD n F GA,whc ih,b e n C s a d o ORDI l oi m,c n s v o sd r b e h r wa s u c sa d i r v h p e e f r C ag r h t a a e c n ie a l a d r r o r e n mp o et e s e d p r m- e e o a c sw l n e a e1 i a y u n i t n e r ra ay i a d smu ain rs l r rs ne . .F n l ,a q a t a i ro n s n i lt u t ae p e e td l z o l s o e s

( .B in i o 4 , nt , B in 0 0 3, hn ) 1 e igMa b x 7 U i7 e ig10 8 C ia j l 9 j ( .Ifr ai n ier gU iesy L Z e gh u4 0 0 ,C ia 2 nom t nE gnei nvr t,P A, h n zo 5 0 2 hn ) o n i

基于改进型CORDIC算法的数控振荡器的设计

基于改进型CORDIC算法的数控振荡器的设计摘要:数字式频率合成器广泛的应用于现代电子通信,电子对抗等重要的军事领域。

作为直接数字式频率合成技术的核心部分数控振荡器的研究,就有十分必要的意义和价值。

本论文在传统的数控振荡器(numericcontroloscillator,简称nco)的基础上,采用改进的计算机坐标旋转(coordinaterotationdigitalcomputer,简称cordic)算法,设计的nco硬核进行验证,最后生成一个0.8*0.8mm2的硬核。

关键词:cordic;数控振荡器;频率中图分类号:tn752 文献标识码:a 文章编号:1674-7712 (2013)08-0000-02频率合成技术是指将一个高密度和高精度的标准频率经过加,减,乘,除的四则运算,产生同样稳定度和精确度的大量离散频率的技术。

根据其原理组成的设备或者仪器成为频率合成器。

数控振荡器(nco)是一种全新的频率发生器的核心部分。

nco的目标是产生一个频率可变的正弦波或者是余弦波样本。

一、数控振荡器(nco)原理nco的基本结构是一个相位累加器和一个相/幅转换器。

nco的相位地址累加器根据参考时钟fclk对m位频率字进行累加,将累加的结果作为相/幅转换器中的输入,相/幅转换器的输出即为正弦值或余弦值。

每来一个时钟脉冲fclk,n位累加器将m位频率控制数据与相位寄存器输出的累加相位数据相加,相加后的结果送至相位寄存器的输入端。

相位寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到累加器的输入端,以使累加器在下一时钟的作用下继续与频率控制数据m相加;另一方面将这个值作为相/幅转换器的控制信号,进行加减和移位运算,输出相应的波形数据。

累加器在基准时钟的作用下进行线性相位累加,相位累加器加满时产生一次溢出,完成一个周期,这个周期也就是nco信号的频率周期。

只要改变频率控制字fcw,字长n,和时钟频率fclk,就可以改变输出频率和频率分辨率。

基于CORDIC算法的数字信号处理技术研究

基于CORDIC算法的数字信号处理技术研究数字信号处理技术在现代通信、音视频处理等领域中起着重要作用。

在数字信号处理过程中,算法是至关重要的一部分,而CORDIC算法作为一种具有良好性能和低复杂度的算法,被广泛应用于数字信号处理中。

本文针对基于CORDIC算法的数字信号处理技术进行了探讨。

一、CORDIC算法简介CORDIC算法全称为Coordinate Rotation Digital Computer(坐标旋转数字计算机)算法,它是一种通过坐标旋转来计算三角函数和超越函数的算法。

CORDIC算法最初是由Jack E. Volder 在1959年所发明的,它的应用范围非常广泛,可以用于各种数字信号处理、图像处理、通信、雷达等领域。

CORDIC算法通过迭代近似的方式来计算各种三角函数和超越函数,通过不断的旋转一个向量,让它的终点逼近目标点从而得到所需的结果。

二、基于CORDIC算法的数字信号处理技术基于CORDIC算法的数字信号处理技术可以分为下面几个方面:1. 数字信号处理中的三角函数计算三角函数是数字信号处理中不可避免的一部分,例如在频域中,信号的傅里叶变换、离散余弦变换等都涉及到三角函数的计算。

CORDIC算法通过对坐标轴的旋转来实现三角函数的计算,同时具有迭代次数少、计算速度快等优点。

2. 基于CORDIC算法的FFT算法FFT(快速傅里叶变换)是一种高效的频域分析算法,它是数字信号处理技术中最常用的算法之一。

基于CORDIC算法的FFT算法,相对于传统的FFT算法,具有计算速度快、复杂度低等优点。

CORDIC-FFT可以实现高速的FFT计算,为实时计算提供了可能。

3. 数字信号处理中的滤波器设计数字信号处理中的滤波器设计是指对数字信号进行滤波处理,通常包括低通滤波、高通滤波、带通滤波、带阻滤波等。

CORDIC算法在滤波器设计中的应用集中在滤波器的系数计算。

CORDIC-FFT算法可以采用线性相位滤波器替代非线性相位滤波器,并据此实现频率响应的线性化,提高了滤波器的性能。

基于MVR CORDIC算法的DDC设计与实现

1 引言

数字下变频器 ( D 的主要 功能是将输入 中频信号 D C) 的频率变换至零 中频 、滤 波得 到基带信号 的同相分量 和 正交分量 。D C由数 字混频器 、 C D N O和低通滤波器 3部 分组成 。其实现主要有 3种途径 : 采用专用芯片 , 自己制 作专用 芯片 , 于 D P或 F G 基 S P A等通 用芯片 。在 高采样 率 系统 中各有弊端 : 专用 芯片要求 MD转换 器转换 出数 据速率较 低 ,比如 A 6 2 D 6 0要求数 据速率小 于 7 z 0MH ; 而 自己制作专用芯片 ,由于成本过高和 国内技术条件 限 制, 在小规模研发生产 中几乎不可能 ; S D P是串行执行指 令, 在高速处理 中处理能 力过低 。 FG P A既有专用 芯片 的优点 , 又克服其设计周 期长 、 投 资大 、 活性差 的缺 点 , 灵 因而用 F G P A实现 D C算法 D 有很好 的前景【 但采用 F G 1 I 。 P A实现经典 的数字下变频会t 遇到两个瓶 颈 :用常用 的查表法无法 实现高速 N O, C 低 通滤波器采用传统 FR滤波器无法实现高速处理 。 I 提 出一 种采用流水 线结构 的 MV O DC算 法来 RC R I 实现 N O ̄ 采用 C D码 实现 FR滤波器[ 可实时 高速 Ct ] , S I 3 1 , 处理 。D C的性 能主要 由 N O和 FR低通滤波器决定 , D C I

・ 设・ 实 计 用

【 摘 要 】介绍 了基于 F G 的数控振荡 器( C 的实现方 案, PA N O) 基于 F G 的 FR滤波器 的实现 方案, R C R I PA I MV O D C算法 的基本

基于CORDIC算法的数字下变频器设计

基于CORDIC算法的数字下变频器设计

王晓华

【期刊名称】《舰船电子对抗》

【年(卷),期】2005(28)2

【摘要】数字下变频技术的基本功能是将宽带高速数据流信号转变成窄带低速数据流信号,以便DSP实时处理.研究了基于协调旋转数字式计算机(CORDIC)算法的数字下变频设计,这种方法能有效提高信号处理效率,减小硬件设计的代价,并且通过仿真证明该方法的高效性.

【总页数】3页(P44-46)

【作者】王晓华

【作者单位】华东船舶工业学院,镇江,212003

【正文语种】中文

【中图分类】TN773;TP312

【相关文献】

1.基于全流程并行加速的改进数字下变频器设计∗ [J], 吉炜寰;邹玉炜;黄磊

2.基于CORDIC算法的数字下变频器 [J], 王军;田忠

3.基于FPGA的数字下变频器设计 [J], 刘云龙;张伟霞

4.基于FPGA的数字下变频器的设计 [J], 张红涛;宁晋哲;慈国辉

5.基于FPGA的在线可重配置数字下变频器的设计与实现 [J], 田黎育;袁一丹;李晓阳;吕佳

因版权原因,仅展示原文概要,查看原文内容请购买。

基于改进型CORDIC算法的数控振荡器的设计

技术交流

C o n s u me r E l e c t r o n i c s Ma g a z i n e

2 0 1 3年 4月下

建立起 以行业外部监 管为主 、事务所 内部监 管为辅 的监 管体 系 。同时,中国注协还应联合各级政府财政部 门、中国证券监 督管理委员会 、 审计署等部 门, 形成稳定的政府部 门承担行 政 监管职能,注册会计师协会承担 自律监管 的监管体系 。 另外, 应 加强社会监督力度 , 通过正确的社会舆 论导向来 监督注册会计师的执业 过程 ,对于弄虚作假行为 , 社会大众应

担负起揭露和曝光的责任 , 使违法事件无处可藏,给企图违 反 规定的会计师事务所施 以无形 的压力 , 以提高注册会计师 的职 业道德形象和执业质 量。 ( 五)加强注册会计师事务所 内部管理 健 全有效 的会计 师事务所 内部 管理机制是保证 事务所执 行客观、公正审计 的前提 , 也是促使会计师 事务所及其 审计人 员按照职业道德准则 的要求执业的基础。 完善 的事务所 内部管 理应从 以下方面入手 。 第 一, 稳定而不乏灵活 的经营理念。 经营理念是知道事务 所发展的核心 , 它 引导事务所的发展方向,是内部管理机制建 立的灵魂 。 理想 的经营理念应该讲求 以人为本, 有注册会计师 注 册会计师职业道德 问题是一个长期而艰巨的工程, 我们必须 组成 强大 的合作 团队。合作 者之 间要相互融合 ,和谐相 处,真 多方努力推进注册会计师职业道德建设,从 自身做起 , 提高审 诚相待。 计服务质量 , 推动社会主义市场经济的健康有 序发 展。 在我 国 第 二, 分配和激励政策 。 在处理分配关系 时应着重注意合 注 册 会 计 师 行 业 成 长 道 路 上 , 注 册 会 计 师职 业 道 德 水 平 也 会 跃 伙人 间的分配关系 、 业务开发和执行者的关系 、 管理人员和业 上一个新 台阶 。 务部门的关系 。 在处理激励政策时,可以建立科学 的绩效考核 参考文 献: 体系 ,同时采用和重视精神鼓励和物质 奖励 的方式 。 分配和激 [ 1 1 吴 承 澜. 注 册 会 计 师 执 业 道 德 问题 浅析 【 I l l 财务会计, 2 0 1 2, 2 2. 励政策是制定其他具体制度政策和前提 。 第三 ,贯彻落实有 关制度 。管理层要身体力行,对制度要 『 2 l 李梅 . 浅谈 注册会计师职业道德 困境的原 因 及 对策[ I 1 _ 行 严格遵 守。 要将奖励与惩戒落到实处。 加强员工对于制度理解 政 事业 资产与财务, 2 0 1 2 , 1 6 . 的培 训和教育 。认真研究执行效果并采取行动 改善 。 『 3 ] 刘福 清. 浅析 注册会计师职业道德【 I 1 _ 财会通讯, 2 0 1 1 , 2 5 . ( 六 )规范注册会计师行业收费制度 f 4 1 王桂 梅. 注册会计 师职业道德缺失的制度思考U ] . 商业会

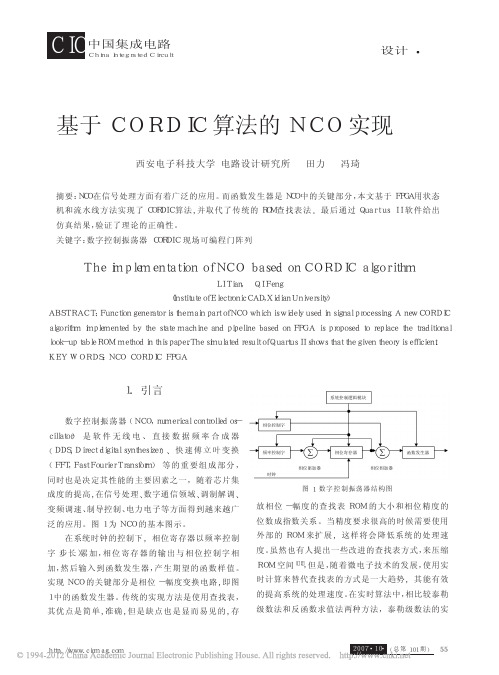

基于CORDIC算法的NCO实现

ChinalntegratedCircult1.引言数字控制振荡器(NCO,numericalcontrolledos-cillator)是软件无线电、直接数据频率合成器(DDS,Directdigitalsynthesizer)、快速傅立叶变换(FFT,FastFourierTransform)等的重要组成部分,同时也是决定其性能的主要因素之一,随着芯片集成度的提高,在信号处理、数字通信领域、调制解调、变频调速、制导控制、电力电子等方面得到越来越广泛的应用。

图1为NCO的基本图示。

在系统时钟的控制下,相位寄存器以频率控制字(步长)累加,相位寄存器的输出与相位控制字相加,然后输入到函数发生器,产生期望的函数样值。

实现NCO的关键部分是相位-幅度变换电路,即图1中的函数发生器。

传统的实现方法是使用查找表,其优点是简单,准确,但是缺点也是显而易见的,存放相位-幅度的查找表ROM的大小和相位精度的位数成指数关系。

当精度要求很高的时候需要使用外部的ROM来扩展,这样将会降低系统的处理速度。

虽然也有人提出一些改进的查找表方式,来压缩ROM空间[1][2],但是,随着微电子技术的发展,使用实时计算来替代查找表的方式是一大趋势,其能有效的提高系统的处理速度。

在实时算法中,相比较泰勒级数法和反函数求值法两种方法,泰勒级数法的实西安电子科技大学电路设计研究所田力冯琦基于CORDIC算法的NCO实现摘要:NCO在信号处理方面有着广泛的应用。

而函数发生器是NCO中的关键部分,本文基于FPGA用状态机和流水线方法实现了CORDIC算法,并取代了传统的ROM查找表法。

最后通过QuartusII软件给出仿真结果,验证了理论的正确性。

关键字:数字控制振荡器CORDIC现场可编程门阵列TheimplementationofNCObasedonCORDICalgorithmLITian,QIFeng(InstituteofElectronicCAD,XidianUniversity)ABSTRACT:FunctiongeneratoristhemainpartofNCOwhichiswidelyusedinsignalprocessing.AnewCORDICalgorithmimplementedbythestatemachineandpipelinebasedonFPGAisproposedtoreplacethetraditionallook-uptableROMmethodinthispaper.ThesimulatedresultofQuartusIIshowsthatthegiventheoryisefficient.KEYWORDS:NCOCORDICFPGA图1数字控制振荡器结构图现需要乘法器,在硬件的复杂性和速度上受到一些限制;反函数求值法在速度上要比坐标旋转数字计算机(CORDIC,COordinateRotationsDIgitalComput-er)算法慢。

基于CORDIC的数字下变频器的FPGA实现

基于CORDIC的数字下变频器的FPGA实现

刘 科1,李广军2

电子科技大学通信与信息工程学院,成都 1kerryliu~81@yahoo.oom.ca 29ili@uestc.edu.cn 摘要:本文介绍了一种基于COImIC算法的数字下频器的结构以及该结构在FleA上的实现。与传统的 数字下变频结构相比,该结构具有速度快,资源省,拓展性好等优点。 关键词:数字下变频;坐标旋转数字计算机;流水结构

Abstract:This paper introduces a new structure of Digital Downconverter which is based on CORDIC algorithm and its FPGA realization.Compared to traditional Digital Downconverter,this structure has hi【sh- er fmax。COSTS less FPGA Or]一chip resource and call be extended easily.

待

图1传统的数字下变频结构

图2改进的数字下变频结构

2.算法与实现:

791

CORDIC(Coordinate Rotation Digital Computer)作为一种迭代算法,提供了计算三角函数的方法。 CORDIC算法迭代原理如下:

基于CORDIC算法的数字下变频技术设计与实现

(oria t i i t o p t, co n t r a o dga cm u 坐标 旋 转 数 值 计 算 ) 法 的 数 控 振 荡 器 的 设 计 方 法 , 且 该 算 法使 数 控 本 振 和数 d e o tn il e 算 而

图 2 C RD C算 法原 理 图 O I

Fg Prn il lc iga o i.2 i cp ebo kd arm fCORDI agrtm C loi h

[ [s-  ̄c【 一 [c y 。 s [ 。 I “ ; c I1s协 ]] o 。 1 ]i i = : O n 0

第 2 0卷 第 9期

V0 . 0 1 2

No9 .

电 子 设 计 工 程

El cr n c De in Engne rn e to i sg i eig

21 0 2年 5月

Ma .2 2 y 01

基于 C R I O D C算 法的数字下变频技术设计 与实现

侯 武威 , 安 民 , 颖辉 袁 赵

Ab t a t T e t d t n O a e n lo -p tb e meh d c n u slt fF GA’ e o r e , o v h sp o l m , hs sr c : h a i o a NC b s d o k u l t o o s me so P r i l o a o Sr s u c s t s l et i r b e o t i p p r p t o w r u rc l o t l d o clao e h i u a e n CORD C lo i m , e l o t m o i e a e u s f r a d a n me i al c n r e s i tr tc n q e b s d o y o l I ag r h t t ag r h i h c mb n s

基于CORDIC算法的通用调制器设计

余 弦函数值 的 主要方法 , 在工 程实 际 中有 着广 泛的应 用 ; 而 传统 的查找 表或差 值 法计 算 , 在精 度 、 运 算 速度 方 面不 能兼 得 ,

且 占用资源 多 。文 中提 出 了基 于 C O R D I C算 法 的通用 调制器 的实 现方法 , 使用 V H D L硬件 描述 语 言进 行 编程 实现 , 在I S E 1 2 . 4中对算 法进行 功能仿 真 , 最 后通 过 X i l i n x公 司的 F P G A S p a r t a n 一 3系列 X C 3 ¥ 5 0芯 片进行 了具体 验证 。结果 表明 , 该 实 现方 案不仅 计算 速度快 , 而且 硬件 资源 消耗少 , 显著地 提高 了算法 精度 。 关键 词 : 坐 标旋转 数字 计算机 ; 现场 可编 程 门阵列 ; 通 用调 制器 ; 查 找表 中图分 类号 : T P 3 9 1 . 9 文 献标识 码 : A 文章 编号 : 1 6 7 3 — 6 2 9 X( 2 0 1 5 ) 1 1 — 0 1 9 6 — 0 4

( C o o r d i n a t e R o at t i o n D i g i t a l C o mp u t e r )a l g o i r hm t i s he t ma i n me ho t d t O r e a l i z e t h e f a s t nd a a c c u r a t e t r i g o n o me t r i c f u n c i t o n , nd a i s w i d e —

p l e t e t h e AM , F M a n d PM f u n c t i o n . h e T s h o r t c o mi n g s u c h a s o c c u p y i n g FP GA a l o t o f r e s o u r c e s o f ROM , c a l l b e o v e r c o mi n g . CORDI C

数字下变频中基于CORDIC算法的NCO设计

数字下变频中基于CORDIC算法的NCO设计刘刚;蒋伟进;董胡;钟新跃【摘要】在数字下变频中传统数字控制振荡器(Numerically Controlled Oscillator,NCO)模块都是基于查找表结构的,该结构在FPGA内部实现需要占用大量ROM资源,针对这一问题,提出采用坐标旋转数字计算(Coordinate Rotation DigitalComputer,CORDIC)算法进行NCO设计,相比传统的NCO设计,该方法具有输出信号频谱纯度高、能够直接混频而不需要乘法器等优点.设计中采用变象限映射方法解决CORDIC算法无法全周期覆盖的问题,采用流水线技术解决串行迭代带来难以实时输出的问题.经过Modelsim仿真分析,实际输出值与理论值之间的相对误差在10-4~ 10-5数量级范围内,满足数字下变频中NCO的性能需要.【期刊名称】《无线电工程》【年(卷),期】2017(047)012【总页数】4页(P71-74)【关键词】数字下变频;坐标旋转数字计算方法;流水线;数字控制振荡器;现场可编程门阵列【作者】刘刚;蒋伟进;董胡;钟新跃【作者单位】长沙师范学院信息与工程系,湖南长沙410100;湖南商学院计算机与信息工程学院,湖南长沙410205;长沙师范学院信息与工程系,湖南长沙410100;长沙师范学院信息与工程系,湖南长沙410100【正文语种】中文【中图分类】TN911在软件无线电接收机中,数字下变频器是把ADC数字化后的高速数字中频信号变为低速的基带信号,便于后续的相关处理。

数字下变频器在这里起到前端ADC和后端通用DSP器件之间的桥梁作用,其性能的优劣会对整个软件无线电系统的性能产生直接的影响[1]。

因此,数字下变频技术成为软件无线电接收机的关键技术之一,成为制约软件无线电性能的重要器件之一[1]。

文献[2-3]中采用基于多相滤波结构来设计实现数字下变频器,虽然在一定程度上能够节省FPGA内部资源和实现高速数据流下数字下变频,但在性能上还有较大的提升空间,因为只有改进和优化数字下变频中NCO这一核心模块才能大幅度提高数字下变频的性能。

基于cordic算法的数字下变频实现笔记

基于cordic算法的数字下变频的实现---------孙月2014/12/11Matlab实现的参数采样频率 fs=62e6;调制频率 f1=15.5e6;采样点数 N=1024*32;n=1:N;时域时间“t” t=n/fs;频域里的频率参考 freq=(-N/2:N/2-1)/N*fs;在一个matlab脚本中,时域到频域转换之后。

它们的点数是一一对应的,均为N个点。

在时域中N个点,只是离散的点与时间“t”没有关系,作图时plot(t,x)才建立的关系,可以理解为把N个点放在了时间t上。

频域上也是如此(一定要真正理解)。

主要步骤1、用wgn函数产生N点的白噪声x;2、再将白噪声信号x,用2M的低通滤波器,产生零中频的带宽信号x_0;3、用调制信号cos(2*pi*fi.*t)与信号x_0相乘,变频到15.48M为中心的带宽信号sig。

将信号sig扩大2^14倍后,以2进制补码的形式存入到txt文本中,作为硬件实现时的测试激励信号;4、在matlab中,用cordic算法实现将信号分为I,Q两路,并作时域,和频域分析。

5、同时在matlab中直接调用cos,sin函数,产生NCO算法,验证4中的cordic算法是否正确。

6、基于ise平台,实现cordic算法,并将I,Q两路输出存在txt文本中,再导入到matlab中,做频谱分析,与(4)中matlab实现的cordic算法结果比对,验证硬件实现是否正确。

下面是具体实现,以及遇到的问题Wgn(1,N,1)是产生一维的N个点,平均功率为1.低通滤波器的实现有两种方式一、直接调用fdatool工具,设置参数,低通滤波时采样频率fs>2fp。

带通时,fs>2(fh-fl),将fs设置的稍大一点性能更好。

生成的系数,通过“file”—>”export”导出,在matlab中保存以num_1.mat格式保存在该件夹中。

在本脚本中使用时,fir_1=load('Num_1.mat'),fir_1.Num_1即为各系数。

数字下变频器中坐标变换模块的ASIC实现

数字下变频器中坐标变换模块的ASIC实现1.引言数字下变频(DDC)技术是软件无线电接收机的核心技术。

其基本功能是从输人的宽带高速数字信号中提取所需的窄带信号,将其下变频为数字基带信号,并转换成较低的数据率,以供后续的DSP 作进一步的处理。

目前许多型号的DDC 芯片事实上其功能己远远不只是下变频,还包括了成形滤波器、定时同步内插滤波器、重采样NCO、坐标变换、数字ACC 等功能,其结构如图1所示。

CORDIC(Coordinate Rotation Digital Computer)是一种迭代算法,它提供了计算三角函数和欠量求模的方法。

该算法仅利用加法和移位两种运算通过迭代方式进行矢量旋转,因此,它非常适合于硬件A-SIC 实现。

本文所要阐述的就是基于CORDIC 算法的数字下变频器中坐标变换模块的ASIC 实现结构,该模块的主要功能是实现直角坐标系到极坐标系的变换,从而求得由I 路信号和Q 路信号构成的向量的幅度值和相位值,将得到的幅度信息返回给前级的数字AGC 进行增益控制,还可以实现对FM 信号的解调。

2.CORDIC 算法与实现2.1 CORDIC 算法原理CORDIC 是一种迭代算法,它可以用来计算sin,cos 等三角函数,计算幅值和相位等到所需的精度,CORDIC 算法计算幅值和相位的原理如下:假设直角坐标系内有向量A(Xn,Yn),向量A 顺时针旋转θn后得到向量B(Xn,Yn),如图2 所示。

向量A 和向量B 之间存在以下关系,用矩阵表示为将cosθn提出以后得到在这里我们取0i=arctan(1/2i),所有迭代的总和为,其中Si={-1,+1},则tanθi=Si2-i,可得上式Si 中的符号决定了向量的旋转方向,当时Yi≥0,Si=1,顺时针旋转;当Yi<0 时,Si=-1,逆时针旋转,式中的cosθi=cos(arctan(1/2i),随着迭代次数的增加它收敛于一个常数,我们暂不考虑这个常数增益,这样式(2-3)就变为设总共旋转的角度为,初值为0,则,给定向量一组初值如下从上面的式子可以看出,当向量A 旋转到X 轴时,可以得到迭代的结果为,即可求得向量A 的幅值和相位。

cordic下变频原理

cordic下变频原理Cordic下变频原理引言:在现代通信系统中,频率的变换和调整是非常常见的操作。

而Cordic(Coordinate Rotation Digital Computer)算法是一种经典的数字信号处理算法,广泛应用于各种数学运算中,特别是在频率变换中。

本文将介绍Cordic下变频的原理及其应用。

一、Cordic算法简介:Cordic算法是一种通过迭代旋转坐标系的方法来进行各种数学运算的算法。

其基本思想是将一个复杂的运算转化为一系列简单的旋转运算。

Cordic算法的优势在于其简单性和迭代的可重复性,适用于各种数字信号处理应用。

二、Cordic下变频原理:Cordic下变频是指利用Cordic算法来实现频率的变换。

在频率变换中,我们需要将输入信号的频率在一定范围内进行调整,以满足特定的需求。

Cordic算法通过旋转坐标系来实现频率的变换。

具体来说,Cordic下变频可以分为以下几个步骤:1. 初始化:首先需要确定变频的目标频率,以及所需的精度和迭代次数。

通常,我们将目标频率表示为一个固定的角度。

2. 旋转计算:根据目标频率的角度,我们可以通过迭代的方式来计算旋转角度。

通过不断调整旋转角度,我们可以逐步逼近目标频率。

3. 旋转更新:在每一次迭代中,我们会根据计算出的旋转角度来更新坐标系。

通过旋转坐标系,我们可以实现对输入信号的频率变换。

4. 输出计算:最后,我们需要根据旋转后的坐标系来计算输出信号的频率。

通过将旋转后的坐标系投影到输出轴上,我们可以得到变频后的信号。

三、Cordic下变频的应用:Cordic下变频在数字信号处理中有着广泛的应用。

其中,最常见的应用是在通信系统中的频率调整和频谱分析中。

通过Cordic下变频,我们可以实现信号的频率调整,以满足不同的通信需求。

Cordic下变频还可以应用于正交频分复用(OFDM)系统中。

OFDM系统是一种广泛应用于无线通信的调制技术,其中频率的变换是必不可少的操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.3 ?初始化旋转单元代码

??? 输入为x_in y_in z_in 输出为 phi,eps,r 定义信号为x,y,z

基于CORDIC算法数字下变频器设计

郭勇 梅大成 邢丹

(西南石油大学 计算机科学学院,四川 成都 610000)

?

??? 摘? 要 本文以软件无线电为指导,提出基于CORDIC算法利用FPGA平台数字下变频器设计方案。首先分析下变频器的结构;然后采用模块化设计思想,将数字下变频的功能模块包括数字控制振荡器、CIC抽取滤波、HBF抽取滤波器、FIR低通滤波器进行分析和FPGA的设计;最后在MATLAB/DSPBuilder下硬件仿真模块进行仿真并给出仿真结果。

3.1? CORDIC算法

??? CORDIC算法基本原理是:设初始向量x0+jy0经旋转 角度后得到的向量 xn+jyn即 INCLUDEPICTURE "/back/200712416017990.jpg" \* MERGEFORMATINET , INCLUDEPICTURE "/back/200712416024777.jpg" \* MERGEFORMATINET ,设旋转基本角度 θi,令 INCLUDEPICTURE "/back/200712416136978.jpg" \* MERGEFORMATINET ,那么初始向量可通过一系列的基本角度 θi的旋转,逐渐逼近目标向量。在旋转模式下,如果设Z0=θ ,根据J,S,WALTER的推导有:

INCLUDEPICTURE "/back/2007124162623146.jpg" \* MERGEFORMATINET

INCLUDEPICTURE "/back/2007124162629385.jpg" \* MERGEFORMATINET

6 ?使用Dspbuilder低通滤波器的设计

??? 使用Dspbuilder可以方便地在图形化环境中设计FIR数字滤波器,而且系数的计算可以借助MATLAB强大的计算能力和现成的滤波器设计工具来完成。

??? 采用了流水线型实现结构,它用n级相似的算法单元在同一个时钟周期内并行工作,每级算法单元的具体实现结构如图3所示。图中的三个累加器分别完成了该级中xi,yi,zi的迭代,累加器的加/减控制信号为上一级算法单元中的di信号,两个i位的右移寄存器(注:图中的>>i表示右移i位)完成了迭代等式中的乘2-i运算,而该级的基本旋转角度值(2-i)可以采用直接硬连接。

3.2??基于CORDIC算法实现NCO

INCLUDEPICTURE "/back/2007124161511160.jpg" \* MERGEFORMATINET

??? 我们设计的NCO顶层结构为图2所示。我们可以看到,频率控制字寄存器将接收到的频率控制字K送入相位累加器,累加器对系统时钟进行累加计数,当到达输入频率控制字的值时对相位进行累加,随后将累加值送入相位相加器,与相位控制字寄存器接收到的初始相位相加,得到当前的相位值。经过上述相位处理之后,即可获得相位的正/余弦相位序列,将此序列送入基于CORDIC算法的波形发生器,最终获得两路正交的正/余弦输出序列。

的实现结构虚线框中部分是个初始化旋转单元,是因为 INCLUDEPICTURE "/back/2007124161740904.jpg" \* MERGEFORMATINET 。由此可见,当迭代的次数n趋近于无穷大时,所被 覆盖的角度只能是在-99.9度~99.9度之间,若想让 的覆盖范围扩展到 INCLUDEPICTURE "/back/2007124161832777.jpg" \* MERGEFORMATINET ,必须在迭代之前再增加一个初始化旋转,将输入向量先旋转 INCLUDEPICTURE "/back/2007124161925779.jpg" \* MERGEFORMATINET ,之后是16级流水线算法单元,最右边的是级的基本旋转角度值(2-i),di为各级累加器加/减控制信号"X0,Y0,Z0为下变频模块的数据输端口,Xn,Yn,Zn是三个输出端口"。

INCLUDEPICTURE "/back/2007124161613539.jpg" \* MERGEFORMATINET

??? 流水线结构的最大优点在于它的运算速度很快在任何一个时钟周期,n级算法单元都同时工作,如在输入端连续不断地送入数据,那么在n个时钟周期的延迟之后,输出端将连续得到相应的下变频后的数据与传统的串行结构相比,流水线结构的运算速提高了n倍。图4给出了16级流水线算法

??? δi代表向量旋转方向

??? 经过n 次旋转迭代后的结果为:

INCLUDEPICTURE "/back/200712416413662.jpg" \* MERGEFORMATINET

??? 其中, INCLUDEPICTURE "/back/200712416746837.jpg" \* MERGEFORMATINET ,称为模校正因子。如果令 INCLUDEPICTURE "/back/200712416850237.jpg" \* MERGEFORMATINET , y0=0,则? INCLUDEPICTURE "/back/200712416111774.jpg" \* MERGEFORMATINET ,由上述推导可知:若已知角度Z0 和初始向量的 x0,y0 可由式(1)迭代运算得到角度 Z0的正余弦值,而式(3)中的迭代运算用硬件实现时非常方便,只有加(减)和移位操作。

??? 关键字 数字下变频;CORDIC;FPGA

?

1? 引言

??? 软件无线电的设计思想之一是将A/D 转换器尽可能靠近天线,即把A/D从基带移到中频甚至射频,把接收到的模拟信号尽早数字化。由于数字信号处理器(DSP)的处理速度有限,往往难以对 A/D采样得到的高速率数字信号直接进行各种类别的实时处理。为了解决这一矛盾,需要采用数字下变频(DDC)技术,将采样得到的高速率信号变成低速率基带信号,以便进行下一步的信号处理。数字下变频技术在软件无线电和各类数字化接收机中得到了广泛应用。因此建立软件无线电的通用数字下变频器是非常必要的。

---Test for x_in<0 rotate 0,+90,or -90 degrees

IF x_in>o THEN

?????? x <=x_in;

?????? y<=y_in;

?????? z<=z_in;

ELSEIF y_in>0 THEN

?????? x<=y_in;

?????? y<=-x_in;

INCLUDEPICTURE "/back/2007124162356553.jpg" \* MERGEFORMATINET

5? 半带抽取滤波器(HBF)的FPGA设计

??? HBF滤波器特别适合于实现2的幂次方倍的抽取,且计算效率高、实时性强。其频谱如图7所示。半带滤波器是频率响应满足阻带宽度与通带宽度相等,当抽取率为2的幂次方时实现如图8所示。

??? 图5显示的是它的频谱图。CIC所有系数都为1,实现起来极其简单,它不需要任何乘法运算,不需要存储滤波器系数。为了加大阻带衰减,通常采用N级CIC滤波器如图6所示。

INCLUDEPICTURE "/back/2007124162219711.jpg" \* MERGEFORMATINET

2? 下变器如图1所示。

INCLUDEPICTURE "/back/2007124155152633.jpg" \* MERGEFORMATINET ??? 量化的中频数字信号进入数字下变频器后,先与数字控制振荡器产生的本地数字载波混频,经过CIC抽取滤波器,HBF抽取滤波器,FIR低通滤波对信号进行D倍抽取后得到正交基带信号,这是下变频过程。虚线框内为数字下变频部分是我们设计和讨论的重点。

?????? z<=z_in+90;

ELSE

?????? x<=-y_in;

?????? y<=x_in;

?????? z<=z_in-90;

END IF;

4? 积分梳状(CIC)滤波器的FPGA设计

?? CIC滤波器由两部分组成,积分器和梳状滤波器的级联其冲击响应为

INCLUDEPICTURE "/back/2007124162137946.jpg" \* MERGEFORMATINET ?????????????????? (4)?

INCLUDEPICTURE "/back/20071241633989.jpg" \* MERGEFORMATINET ??????????????????(1) ??? 其中????

INCLUDEPICTURE "/back/200712416334253.jpg" \* MERGEFORMATINET

3? 数字控制振荡器振荡器

??? 如图1所示。正交数字下变频器前端包括两部分一是乘法器;一是NCO。乘法器设计很简单,NCO的目标是产生一个理想的正弦和余弦波。更确切地说是产生一个可变频率的正弦波样本如公式: INCLUDEPICTURE "/back/2007124155245189.jpg" \* MERGEFORMATINET 其中 INCLUDEPICTURE "/back/2007124155328191.jpg" \* MERGEFORMATINET 为本地振荡频率; INCLUDEPICTURE "/back/2007124155333182.jpg" \* MERGEFORMATINET 为DDC输入信号的采样频率。正弦波样木可以用实时计算的方法产生,但这只适用信号采样频率很低的情况。在软件无线电高速信号采样频率的情况下,NCO实时计算的方法是不可取的。NCO产生正弦波样本通常采用查表法,通过输入的相位数据来寻址查表输出相应的正弦波幅值。对于一个相位位数为n,输出信号幅度位数为M的数控振荡器,这就需要耗费大量的ROM资源(2nX Mbit)。为了避免使用大容量的存储器。可采用了一种基于CORDIC( Coordinate Rotation Digital Computer)算法来产生正/余弦样本。该算法有线性的收敛域和序列特性。只要迭代次数足够,即可保证结果有足够的精度。并且用于混频的乘法器也可以省掉。从而还节省了大量的逻辑硬件资源。使得数字下变频更易于用FPGA来实现。