SDRAM的布线规则 基于Allegro嵌入式高速电路布线设计

SDRAM布线规则及技巧

SDRAM布线规则及技巧SDRAM(Synchronous Dynamic Random Access Memory)是一种同步动态随机存取存储器,广泛应用于计算机系统中。

SDRAM的性能受到布线的影响,因此在设计SDRAM布线时需要遵守一些规则和技巧,以保证其性能和稳定性。

首先,布线规则是确保时序要求满足的基础。

时序要求是指控制信号在SDRAM上正确传输和演变的时间约束。

布线规则的主要目标是减少时序延迟和时序失真,确保信号的准确到达。

一些常见的布线规则包括:1.长度匹配:确保信号线的长度尽量相等,可以通过差分对和匹配长度来实现。

2.延迟匹配:保证信号线的延迟尽量相等,可以通过使用等长路径和准确的电缆长度来实现。

3.信号间隔:确保信号线之间的间隔足够,避免相互干扰。

4.层间切换:尽量减少信号线在不同层之间的切换,减少反射和串扰。

其次,布线技巧可以帮助优化布线效果和避免一些常见的布线问题。

1.差分对布线:差分对布线是一种常见的布线技巧,用于减少信号线之间的串扰和提高抗干扰能力。

差分对布线需要保持差分对的长度和延迟匹配。

2.绕行规则:在布线时需要避免绕行,尽量使用直线布线路径,减少信号线的长度和延迟。

3.层交叉规则:避免信号线在不同层之间频繁切换,减少反射和串扰。

如果需要交叉布线,应尽量避免延迟不匹配。

4.电源和地线:为SDRAM提供稳定的电源和地线是非常重要的。

布线时需要确保电源和地线的可靠连接、低噪声和低电阻。

最后,还有一些其他的技巧可以帮助优化SDRAM布线:1.参考设计:可以参考已有的成熟设计和布局规则,避免重复工作和一些常见的布线问题。

2.仿真与验证:使用电磁仿真工具和布线验证工具进行仿真和验证,确保布线符合设计要求并满足性能要求。

3.信号完整性分析:通过信号完整性分析工具,检测和分析信号线中的时序失真和耦合问题,从而优化布线布局。

总结起来,SDRAM布线规则和技巧可以帮助优化布线效果、提高信号完整性,确保SDRAM的性能和稳定性。

sdram pcb 设计规则

sdram pcb 设计规则SDRAM PCB设计规则SDRAM(Synchronous Dynamic Random Access Memory)是一种常见的内存芯片,它在计算机系统和其他电子设备中广泛使用。

为了确保SDRAM能够稳定、高效地工作,PCB(Printed Circuit Board)的设计需要遵循一些特定的规则。

1. 电源和地线规则:SDRAM需要稳定的供电和有效的接地。

为了实现这一点,在设计过程中应遵循以下规则:- 为SDRAM芯片提供一组独立的电源和地线,以减少电源噪声。

- 在布局过程中,将电源和地线尽可能靠近SDRAM芯片,并使用足够宽度的铜层来降低电阻和电感。

2. 布局规则:好的布局是确保SDRAM性能的重要因素。

以下是一些建议的布局规则:- 将SDRAM芯片放置在离CPU和其他重要器件尽可能近的位置,以缩短信号路径。

- 尽量避免将SDRAM芯片放置在热源附近,以防止温度升高而导致性能下降。

- 在布局过程中,遵循良好的信号完整性原则,如避免过长的导线或者过多的弯曲。

3. 信号完整性规则:为了保证信号在PCB上的传输完整性,应遵循以下规则:- 确保时钟和数据线的匹配长度,以防止时序偏差。

- 使用适当的信号层和层间间距来隔离敏感的时序信号,以减少噪声干扰。

- 使用合适的阻抗匹配来提高信号传输的质量,防止反射和信号衰减。

4. 热管理规则:SDRAM在高频运行时会产生热量,因此在设计过程中需要考虑热管理问题:- 在PCB中加入散热孔或金属散热片,以增加散热表面积并提高散热效果。

- 确保周围环境的通风良好,避免过热影响SDRAM的性能。

综上所述,设计符合SDRAM的PCB需要遵循电源和地线规则,布局规则,信号完整性规则以及热管理规则。

这些规则旨在最大程度地提高SDRAM的性能、稳定性和可靠性。

在设计过程中,请确保严格遵守相关规范和标准,以确保SDRAM的最佳工作状态。

DDRSDRAM布线规则

DDRSDRAM布线规则DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)是一种双倍数据速率同步动态随机访问存储器。

DDR SDRAM的主频和前面的SDRAM相比,提供了更高的数据传输速率,更高的带宽和更低的功耗。

正确的DDR SDRAM布线规则是确保内存子系统的最佳性能和稳定性。

以下是DDRSDRAM布线规则的一些重要要点:1.信号布线:-时钟信号(CK)和数据线(DQ)应该以相同的长度布线,以避免时钟偏移引起的数据损失。

-时钟信号和数据线应该尽量平行布线,以降低信号之间的干扰。

-时钟和地址信号应该有足够的地线引脚(GND)相邻布线,以确保信号的良好传输。

-数据线之间,特别是相邻的数据线,应保持足够的间距,以降低信号交叉干扰。

-数据线和驱动器之间应该有适当的电阻匹配,以提高信号完整性。

-控制信号(CS,RAS,CAS,WE)和地址信号(A)应尽可能与时钟信号平行布线。

2.电源和地线布线:-电源线和地线应足够宽,以提供稳定的电流和地引。

-电源和地线应平行布线,以降低信号之间的干扰。

-地线应尽可能接近信号线,以降低信号的回流路径。

-电源线和地线之间应有适当的距离,以避免互相干扰。

3.终端布线:-终端布线应尽量接近DDRSDRAM芯片,以减小传输延迟和信号损失。

-终端布线应遵循DDRSDRAM供应商提供的布线指南,以确保符合DDRSDRAM标准。

4.长度匹配:-时钟信号和数据线应尽量匹配相同的长度,以避免时钟偏移引起的数据损失。

-地线和电源线也应尽量匹配相同的长度,以避免功率噪声干扰。

5.建模和仿真:-使用建模和仿真工具来验证DDRSDRAM布线的正确性和稳定性。

-进行时序分析和电气分析,以确保数据在DDRSDRAM子系统中的正确传输。

总之,DDRSDRAM布线规则是一个复杂的过程,需要考虑时钟信号、数据线、电源和地线的布线方式。

DDRSDRAM布线规则

DDRSDRAM布线规则DDRSDRAM布线规则是指在电路板上设计和布置DDRSDRAM的电路和连线时需要遵循的一些规则和原则。

DDRSDRAM是一种双倍速率同步动态随机存储器,用于高速数据存储和访问,因此布线规则尤为重要,可以确保信号的完整性和稳定性,提高系统的性能和可靠性。

以下是DDRSDRAM布线规则的一些重要方面:1.线长匹配:DDRSDRAM的布线中,所有的时钟、地址、数据和控制信号必须尽量保持相等的线长。

由于DDRSDRAM使用双倍速率,信号频率较高,线长差异可能导致信号到达时间不一致,影响系统的稳定性。

通过保持线长相等,可以降低信号的传输延迟,减少时钟失真和时序错误。

2.地与电源平面:DDRSDRAM的布线中,要为信号线和电源线提供良好的地和电源环境。

通过使用地和电源平面,可以降低信号线上的互损耗和串扰,提高信号的信噪比和阻抗匹配。

电源平面还可以提供稳定的电源供应,减少功率噪声和波动对信号传输的影响。

3.信号隔离:DDRSDRAM的布线中,需要将不同类型的信号线进行隔离,避免互相干扰。

例如,时钟信号和数据信号应尽量分开布线,以减少互相之间的串扰。

同时,还应将高速信号线和低速信号线进行分离,避免高速信号对低速信号的影响。

4.差分信号:DDRSDRAM的部分信号采用差分传输方式,例如,地址和数据线。

在布线时,要确保差分线对称和匹配。

差分线对称性可以减少共模噪声的影响,而差分线匹配可以提高差分信号的传输效率和抗干扰能力。

5.终端电阻:DDRSDRAM的布线中,需要正确设置终端电阻来匹配信号线的特性阻抗。

终端电阻的作用是反射信号的能量,减少信号反射和回波干扰。

正确设置终端电阻可以提高信号的传输质量,减少时序错误和噪声。

6.时序调整:DDRSDRAM的布线中,需根据具体的DDRSDRAM芯片和系统要求进行时序调整。

时序调整包括延迟设置、预充电设置和时钟节拍调整等。

通过合理设置时序参数,可以确保DDRSDRAM正常工作,提高数据传输的稳定性和速度。

sdram pcb 设计规则

sdram pcb 设计规则SDRAM (Synchronous Dynamic Random Access Memory)是一种同步动态随机存取存储器,被广泛应用于计算机和其他电子设备中。

SDRAM PCB (Printed Circuit Board)设计规则是在设计SDRAM模块时需要遵循的一些准则和规范,以确保模块的性能、稳定性和可靠性。

下面是一些与SDRAM PCB设计相关的参考内容:1. PCB布局:- 确保SDRAM芯片和相关元件之间的连接尽可能短,以减少信号传输的延迟。

- 高速信号线应避免过长的走线,并尽量采用直线走线方式,以减少信号的反射和干扰。

- 将SDRAM芯片和电源引脚放置在接近功耗滤波电容的位置,以最大程度地降低功耗线的阻抗。

- 合理规划地面和电源平面,确保它们之间有足够的距离,以减少地平面与电源平面之间的串扰。

2. 信号完整性:- 为时钟信号、地址信号和控制信号提供低阻抗、低噪声的电源电压。

这可以通过增加电源滤波电容和合理布局电源和地线来实现。

- 使用阻抗匹配技术,保持信号走线的阻抗与适配SDRAM的驱动器和终端之间的要求一致。

- 通过添加补偿差分走线、增加差分走线间距、使用扇出缓冲器等措施,减少信号串扰和互相干扰。

3. 电源和地线:- 提供足够的地平面和电源平面,以减少信号回流路径的长度和电磁干扰。

- 采用较大的电源与地引脚走线,以增加电源回流的路径,减小引脚区距离,提高电源稳定性。

- 使用分区式供电和分离式地线布局,以降低供电噪声和信号引起的传导和射频辐射干扰。

4. DDR引脚布局和输形:- DDR (Double Data Rate)是SDRAM的一种改进版本,它有更高的数据传输速率和更复杂的信号分布。

在布局和输形过程中,应遵循DDR的特殊要求,如匹配长度差异、避免信号回流突变等。

5. 噪声控制:- 在PCB设计中使用分离式地线和电源布局可减少地线回流并降低供电噪声。

SDRAM布线规则

SDRAM布线规则一:SDRAM 类高速器件布线规则通用基本法则:(1)DDR和主控芯片尽量靠近(2)高速约束中设置所有信号、时钟线等长(最多允许50mil的冗余),所有信号、时钟线长度不超过1000mil (3)尽量0过孔,元件层下面一定要有一个接地良好的地层,所有走线不能跨过地的分割槽,即从元件层透视地层看不到与信号线交叉的地层分割线。

这样的话200M的DDR基本上是没有太大问题。

其它的一些3W 20H法则能做到就尽量做到吧时钟信号:以地平面为参考,给整个时钟回路的走线提供一个完整的地平面,给回路电流提供一个低阻抗的路径。

由于是差分时钟信号,在走线前应预先设计好线宽线距,计算好差分阻抗,再按照这种约束来进行布线。

所有的DDR差分时钟信号都必须在关键平面上走线,尽量避免层到层的转换。

线宽和差分间距需要参考DDR控制器的实施细则,信号线的单线阻抗应控制在50~60 Ω,差分阻抗控制在100~120 Ω。

时钟信号到其他信号应保持在20mil以上的距离来防止对其他信号的干扰。

蛇形走线的间距不应小于20 mil。

串联终端电阻RS值在15~33Ω,可选的并联终端电阻RT 值在25~68 Ω,具体设定的阻值还是应该依据信号完整性仿真的结果。

数据信号组:以地平面为参考,给信号回路提供完整的地平面。

特征阻抗控制在50~60 Ω。

线宽要求参考实施细则。

与其他非DDR 信号间距至少隔离20 mil。

长度匹配按字节通道为单位进行设置,每字节通道内数据信号DQ、数据选通DQS和数据屏蔽信号DM长度差应控制在±25 mil内(非常重要),不同字节通道的信号长度差应控制在1 000 mil内。

与相匹配的DM和DQS串联匹配电阻RS值为0~33 Ω,并联匹配终端电阻RT值为25~68Ω。

如果使用电阻排的方式匹配,则数据电阻排内不应有其他DDR信号。

地址和命令信号组:保持完整的地和电源平面。

特征阻抗控制在50~60 Ω。

pads高速布线规则

高速布线规则SDRAM的布线规则该嵌入式系统使用64M字节的SDRAM扩展数据存储区,由两片K4S561632组成工作在32位模式下。

最高频率可达100M以上,对于SDRAM的数据线、时钟线、片选及其它控制信号需要进行线长匹配,由此提出以下布线要求:1. SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰。

走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线。

误差允许在20mil以内。

2. 地址,片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil。

尽量走成菊花链拓补。

可有效控制高次谐波干扰,可比时钟线长,但不能短。

3. SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

根据布线要求,在Allegro中设置不同的约束:针对线宽设置3 个约束SDRAM_CLK,SDRAM_ADDDR,SDRAM_DATA,设置完约束后将约束添加到对应的net上。

使得各个net都具有线宽、线距约束属性。

最后为不同的信号组选择合适的约束即可。

但是设置的约束在系统CPU内部是无法达到的。

因为EP9315为BGA封装。

pin间距1.27毫米,显然在CPU内部,线宽线距无法达到上述要求,利用Allegro设置CPU特殊走线区域cpu_area。

并加上area属性,在此区域中另设置适合BGA内部走线的约束。

Xnet在IDE总线等长布线中的应用系统中的IDE接口设计EP9315强大的外设接口能力能够直接驱动IDE硬盘,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。

如图2所示其中的排阻起到了端接匹配的作用,但使得整个走线被分为好几个NET,而Allegro中常用的走线长度设置propagation_delay和relative_propagation_delay只能针对同一NET设置.IDE总线信号由EP9315扇出,要求EP9315到IDE接口走线DD*+UBDD*(如图2中NET)等长,误差为+/-20mil,最简单的方法是分别设置DD*等长和UBDD*等长,误差各位+/-10mil,就可以达到要求,但是增加了布线难度,特别当DD*有较大绕线空间。

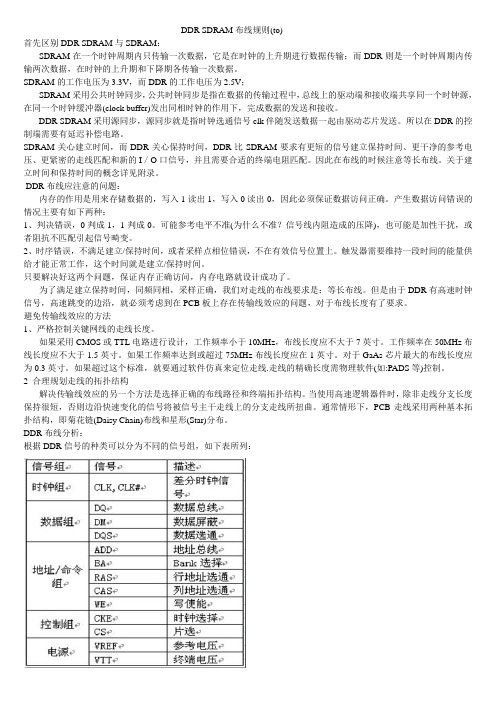

DDR SDRAM布线规则

跳至文章首页芯片设计EMSYM 昂信科技苏州市嵌入式系统重点实验室搜索 搜索BOM 管理System On Module 高清 VODDDR SDRAM布线规则2009-11-12 / 3:06 pm tzhiwen 抢沙发首先区别DDR SDRAM与SDRAM:SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR则是一个时钟周期内传输两次数据,在时钟的上升期和下降期各传输一次数据。

SDRAM的工作电压为3.3V,而DDR的工作电压为2.5V;SDRAM采用公共时钟同步,公共时钟同步是指在数据的传输过程中,总线上的驱动端和接收端共享同一个时钟源,在同一个时钟缓冲器(clock buffer)发出同相时钟的作用下,完成数据的发送和接收。

DDR SDRAM采用源同步,源同步就是指时钟选通信号clk伴随发送数据一起由驱动芯片发送。

所以在DDR的控制端需要有延迟补偿电路。

SDRAM关心建立时间,而DDR关心保持时间,DDR比SDRAM要求有更短的信号建立保持时间、更干净的参考电压、更紧密的走线匹配和新的I/O口信号,并且需要合适的终端电阻匹配。

因此在布线的时候注意等长布线。

关于建立时间和保持时间的概念详见附录。

DDR布线应注意的问题:内存的作用是用来存储数据的,写入1读出1,写入0读出0,因此必须保证数据访问正确。

产生数据访问错误的情况主要有如下两种:1、判决错误,0判成1,1判成0。

可能参考电平不准(为什么不准?信号线内阻造成的压降),也可能是加性干扰,或者阻抗不匹配引起信号畸变。

2、时序错误,不满足建立/保持时间,或者采样点相位错误,不在有效信号位置上。

触发器需要维持一段时间的能量供给才能正常工作,这个时间就是建立/保持时间。

只要解决好这两个问题,保证内存正确访问,内存电路就设计成功了。

为了满足建立保持时间,同频同相,采样正确,我们对走线的布线要求是:等长布线。

但是由于DDR有高速时钟信号,高速跳变的边沿,就必须考虑到在PCB板上存在传输线Un Re gi st er ed效应的问题,对于布线长度有了要求。

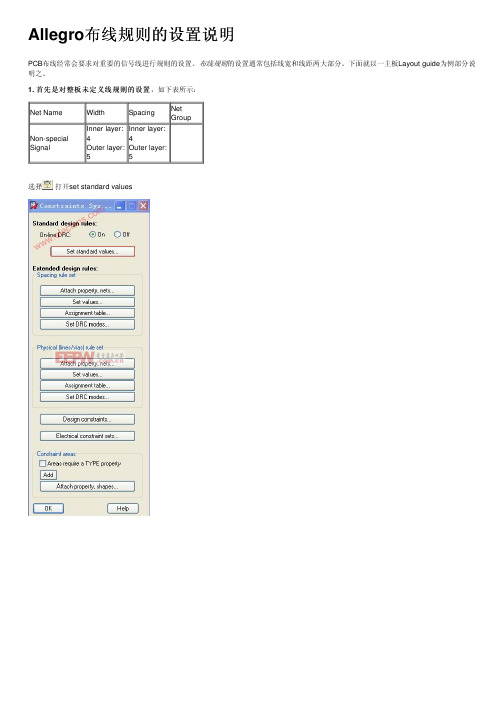

Allegro布线规则设置说明说明书

Allegro布线规则的设置说明PCB布线经常会要求对重要的信号线进行规则的设置。

布线规则的设置通常包括线宽和线距两大部分。

下面就以一主板Layout guide为例部分说明之。

1. 首先是对整板未定义线规则的设置首先是对整板未定义线规则的设置,如下表所示:Net Name Width Spacing Net GroupNon-special Signal Inner layer:4Outer layer:5Inner layer:4Outer layer:5选择打开set standard values这里规定了Default line 在outer layer(TOP)和inner layer(INT1)中的line width 和pad to pad 的间距。

2. 接下来设置HOST 部分,部分,见下表要求:Net Name Width Spacing Space withothersignalNetGroupFSB Signals Inner layer:4Outer layer:58/1020HOST首先将属于此网络的所有net 定义为同一组,即BUS NAME=HOST选择Edit-Properties 并在右侧的当前命令栏中点击More 打开Find by name or property 窗口,ok这样就可以得到下面的窗口:至此一组HOST 线设置完毕,用同样的方法我们可以继续将DDR 等部分的线设置完3. 重新打开,选择spacing rule set-set value,点击ADD 添加HOST 8:10然后在Subclass 中,顶底层Line To Line 的间距为10,内层为8.4. 选择physical rule set-set value,点击ADD 添加HOST 4/5然后在Subclass 中,顶底层的线宽为5,内层为4.5. 无论是线宽还是线距都需要在assignment table 中进行和其他NET 的匹配。

SDRAM布线规则

SDRAM布线规则SDRAM (Synchronous Dynamic Random Access Memory)是一种常用于计算机主板上的随机访问存储器。

在设计SDRAM布线时,需要遵循一些规则,以确保信号传输的可靠性和稳定性。

以下是SDRAM布线的一些建议和规则:1.路线长度匹配:SDRAM使用同步时钟来同步数据传输,因此,所有的信号线应具有相似的长度,以保持同步。

如果存在长度差异,则可能产生信号延迟或抖动,导致数据错误。

为了匹配长度,可以使用不同的连线层或添加等长的延迟。

布线工程师应考虑敏感信号的传输时间,并相应地调整线路长度。

2.信号分组:将相似的信号分组放置在一起,以最小化相互干扰的概率。

将地址线,控制线和数据线组织成几个独立的组,每个组内的信号彼此相邻。

同时,应尽量将信号组放置在板上物理位置上,以最小化信号传输路径的长度。

3.地线和电源线分离:将地线和电源线分开布线,以避免互相干扰。

这样可以减少地线引起的共模噪声对信号的影响。

此外,还应确保地线和电源线的足够宽度,以降低电阻和电感,从而提供稳定的电源和地线连接。

4.控制线布线:控制线的布局应设计为最小化对数据线和地址线的交叉干扰。

这可以通过在控制线周围放置地线和电源线来实现。

同时,控制线应尽量与其他线路相垂直,以减少信号耦合。

5.地线引脚:SDRAM芯片有许多地线引脚,这些引脚应尽可能地靠近芯片。

这样可以减少引脚之间的电阻和电感,提供稳定的地线连接。

6.数据线布线:数据线应尽量短,并且按照组织进行布线。

布线长度的不匹配会导致时序问题,因此需要在布线过程中考虑数据线的长度。

7.阻抗匹配:为了防止信号反射和串扰,应将信号线和所用电阻之间的阻抗进行匹配。

在布线过程中,需确保选择正确的电阻值和线宽。

8.PCB层数:信号线数目较多的SDRAM布线可能需要使用多层PCB以提供足够的空间和良好的信号隔离。

在布线时,应尽量将耦合效应减到最小。

9.PCB排布:在整个主板设计中,需要设定SDRAM芯片的位置和布局,以尽量缩短信号线的长度,减少信号传输的时延和损耗。

allegro中 Xnet概念和Xnet等长设置

allegro中 Xnet概念和Xnet等长设置SDRAM的布线规则该嵌入式系统使用64M字节的SDRAM扩展数据存储区,由两片K4S561632组成工作在3 2位模式下。

最高频率可达100M以上,对于SDRAM的数据线、时钟线、片选及其它控制信号需要进行线长匹配,由此提出以下布线要求:1.SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰。

走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线。

误差允许在20mil以内。

2.地址,片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil。

尽量走成菊花链拓补。

可有效控制高次谐波干扰,可比时钟线长,但不能短。

3.SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

根据布线要求,在Allegro中设置不同的约束:针对线宽设置3 个约束SDRAM _CLK,SDRAM_ADDDR,SDRAM_DATA,设置完约束后将约束添加到对应的net上。

使得各个net都具有线宽、线距约束属性。

最后为不同的信号组选择合适的约束即可。

但是设置的约束在系统CPU内部是无法达到的。

因为EP9315为BGA封装。

pin间距1.27毫米,显然在CPU内部,线宽线距无法达到上述要求,利用Allegro设置CPU特殊走线区域cpu_area。

并加上area属性,在此区域中另设置适合BGA内部走线的约束。

Xnet在IDE总线等长布线中的应用系统中的IDE接口设计EP9315强大的外设接口能力能够直接驱动IDE硬盘,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。

如图2所示其中的排阻起到了端接匹配的作用,但使得整个走线被分为好几个NET,而Allegro中常用的走线长度设置propagation_delay和relative_propagation_delay只能针对同一NET设置.I DE总线信号由EP9315扇出,要求EP9315到IDE接口走线DD*+UBDD*(如图2中NET)等长,误差为+/-20mil,最简单的方法是分别设置DD*等长和UBDD*等长,误差各位+/-10mil,就可以达到要求,但是增加了布线难度,特别当DD*有较大绕线空间。

SDRAM布线规则

SDRAM布线规则SDRAM布线规则SDRAM接口电路和PCB布线很多人对内存布线感到迷茫,找不到切入点,不知如何下手,其实高速硬件设计的主要任务就是与干扰做斗争,内存布线也不例外。

可以这样考虑:内存是做什么用的呢?是用来存储数据的,写入1读出1,写入0读出0,即保证数据访问正确。

那么,在什么情况会导致数据访问错误呢?"1、判决错误,0判成1,1判成0。

可能参考电平不准(为什么不准?信号线内阻造成的压降),也可能是加性干扰,或者阻抗不匹配引起信号畸变。

2、时序错误,不满足建立/保持时间,或者采样点相位错误,不在有效信号位置上。

触发器需要维持一段时间的能量供给才能正常工作,这个时间就是建立/保持时间。

那么只要解决好这两个问题,保证内存正确访问,你的内存电路就设计成功了。

有了这个指导思想,内存布线就可以按部就班地完成。

不过,不同的RAM类型,虽然目标都是避免判决和时序错误,但实现方法因工作模式不同而有较大差异。

高速系统一般采用低压信号,电压低,摆幅小,容易提高速度,降低功耗,但这给布线带来了困难,因为低压信号功率受信号线内阻影响大,是电压平方关系,所以要尽量减少内阻,比如使用电平面,多打孔,缩短走线距离,高压传输在终点用电阻分压出较低电压的信号等。

SDRAM、DDR-I、DDR-II、DDR-III信号电压一个比一个低,越来越不容易做稳定。

电源供给也要注意,如果能量供给不足,内存不会稳定工作。

下面先介绍一下时钟同步电路的类型,然后分析具体芯片的类型。

源同步就是指时钟选通信号clk伴随发送数据一起由驱动芯片发送。

公共时钟同步是指在数据的传输过程中,总线上的驱动端和接收端共享同一个时钟源,在同一个时钟缓冲器(clock buffer)发出同相时钟的作用下,完成数据的发送和接收。

公共时钟同步,将同一个时钟信号用时钟分配器分成2路,一路接发送器,一路接接收器。

在时钟上升沿发送数据,在下一个周期的上升沿采样接收。

常用存储器设计常用电路模块的布局布线原则

差分对误差严格控制在5mil 数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

DDRx1片的等长布线

v Class规则:

将数据类设为2组Class(D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS);

v 误差范围:

差分对误差严格控制在5mil 数据线误差范围控制在+/- 15mil 地址线误差范围控制在+/- 100mil

DDR2芯片时序设计

v SDRAM v FLASH v DDR v DDR2

vDDR3

v QDR

课程内容

DDR3的设计

v DDR3的新特性

DDR3与DDR2的比较

DDR3的拓扑结构

严格差分等长设计

严格差分等长设计 严格差分等长设计

严格等长设计,控制 在±10mil

严格差分等长设计

严格等长设计, 控制在±10mil

尽量控制等长

尽量控制等长,控制 在±100mil如果是菊 花链拓扑则走线越短

越好

尽量控制等长

v SDRAM v FLASH v DDR v DDR2 v DDR3

vQDR

SDRAM的布局

v 布局原则是:靠近CPU摆放 v SDRAMx1片时,点对点的布局方式

SDRAM到CPU推荐的中心距离: 当中间无排阻时:900-1000mil 当中间有排阻时:1000-1300mil

SDRAM的布局

v SDRAMx2片时,相对于CPU严格对称

v 方案一:空间足够时,与CPU放在同一面

方案二: SDRAM顶底对贴

SDRAM布线方法

SDRAM布线方法1、无所谓在外面还是在内部,都可以,内外走线都要打孔。

表层信号紧临地平面就不怕干扰,但要注意外表面空气介电常数不如隔绝空气的内部稳定,在一些湿度,温差大的地方的设备最好走内部,外部走地层,不过这样成本高。

2、等长不是目的,目的是满足建立保持时间,同频同相,采样正确。

SDRAM是公共时钟模式,只关心建立时间,不关心保持时间。

这些时间和各段飞行时间,经过个门电路延时,clock skew,jitter,cycle等有关,需要按照公式精确计算。

算出各种参数后下规则,让EDA软件辅助设计。

选出最长的一根线,不需要计算什么,只要与之等长即可。

有些软件能自己算,有些只能自己一段段计算,可以编程让EXCEL表格对某种格式的报告文件自动求和,也算半自动了。

目测不准吧。

3、有些软件有自动推济功能,DXP好像有吧,不清楚。

其实布线就是和干扰做斗争,可以这样考虑:SDRAM是内存,用来存储数据,写入1读出1,写入0读出0,即保证数据访问正确。

那么,什么情况会导致数据访问错误呢?1、判决错误,0判成1,1判成0。

可能参考电平不准(为什么不准:电源压降),也可能是加性干扰,阻抗不匹配。

2、时序错误,不满足建立保持时间,采样点相位错误。

那么只要解决好这两个问题,保证内存正确访问,你的SDRAM电路就设计成功了。

SDRAM对布线有什么要求?首先必须明白SDRAM是一种什么样的存储器,搞清其接口工作的逻辑时序。

SDRAM是一种同步动态存储器,所有接口信号都是通过时钟同步和采样的。

这就对SDRAM的布线提出了要求——保证采样的正确性。

于是,应用高速数字电路的知识结合某种具体SDRAM 器件和你的PCB进行分析,发现在正常工作频率(如100MHz)下,在PCB走线上的信号传输时间大于其上升时间1/10。

于是,接下来考虑高速数字电路两大问题反射和延迟:反射造成 SDRAM时钟线信号出现振铃,多次穿越门限造成误触发;数据线和时钟线的传输延迟不相同,造成时钟上升沿采样不到所需要的数据。

ALLEGRO DDR布线规则

ALLEGRO约束规则设置步骤(以DDR为例)Dyyxh@pcbtechtzyhust@本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助.由于本人水平有限,错误之处难免,希望大家不吝赐教!在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好constraint规则,并将这些规则分配到各类net group上.下面以ddr为例,具体说明这些约束设置的具体步骤.1. 布线要求DDR时钟: 线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,必需精确匹配差分对走线误差,允许在+20mil以内DDR地址,片选及其他控制线:线宽5mil,内部间距15mil,外部间距20mil,应走成菊花链状拓扑,可比ddrclk线长1000-2500mil,绝对不能短DDR数据线,ddrdqs,ddrdm线:线宽5mil,内部间距15mil,外部间距20mil,最好在同一层布线.数据线与时钟线的线长差控制在50mil内.2. 根据上述要求,我们在allegro中设置不同的约束针对线宽(physical),我们只需要设置3个约束:DDR_CLK, DDR_ADDR,DDR_DATA设置好了上述约束之后,我们就可以将这些约束添加到net上了.点击physical rule set中的attach……,再点击右边控制面板中的more,弹出对话框如上图所示,找到ckn0和ckp0,点击apply,则弹出选中左边列表中的NET_PHYSICAL_TYPE, 在右边空格内输入DDR_CLK, 点击apply,弹出即这两个net已经添加上了NET_PHYSICAL_TYPE属性,且值为DDR_CLK. 类似的,可以将DDR数据线,数据选通线和数据屏蔽线的NET_PHYSICAL_TYPE设为DDR_DATA, DDR地址线,片选线,和其他控制线的NET_PHYSICAL_TYPE设为DDR_ADDR.上述步骤完成后,我们就要将已经设好的约束分配到这些net group上. 如下图点击assignment table……弹出对话框如下图所示,我们对不同的信号组选择各自的physical约束有人可能会问,为什么你这还有area0,area1啊这是因为你的这些约束有的地方不可能达到的,比如在bga封装的cpu内,你引线出来,线间距不可能达到30,20甚至10个mil.在这些地方,如果你也按照这个约束那么你的pcb中的drc就不可能消的掉.这时一个解决办法就是把这些地方划为一个room,然后给他加上room 属性(即为room的名字area0,1等等).针对这些room内,设定合适的约束(同上).针对线间距,由于每个都分为组内间距和组外间距,所以共有6个约束: DDR_CLK_INNER,DDR_CLK_OUTER,…………………………我们只要对这六个约束设置line to line 和line to shape就可以,分别按上述要求设置就可以了.剩下的步骤和physical中设置是一样的.不过这时assignment table变成了下面这样.下面就是设置线的等长.这个需要我们到Ecset中设置.这些高速线一般都需要端接匹配(数据线由于是双向的,两端都有匹配电阻),所以你的整个etch被分成了好几个net,这时候这些net的长度计算就比较麻烦.一种情况就是你设置XNET,然后对Xnet计算长度,我认为这是最省事也是最好的一种办法,还有就是你不管什么Xnet,分别将各段的长度加起来,算等长.注: 这个时候有个很矛盾的事情,就是你的时钟线如果想定义为来走,即让allegro自己等间距的一次拉,你就不能将之定义为Xnet,我自己用的时候是这样的,我在将时钟线对应的xnet删除后,时钟线就可以成对的拉,而之前尽管设置好了差分属性,系统也是不认的.不知道大家有没有这个经验.下面我就讲讲如何设置这些约束,并将这些约束加到对应的xnet上. 点击或setup》electrical constraint spreadsheet,弹出点击electrical constraint set》routing》total etch length,右边如上图所示出现brd名字,右键点击brd名字,弹出如下右键菜单如上图点击create ECset,则弹出输入DDR_ADDR, 点击ok,则brd名字前出现+号,打开之,可以见到设置好的DDR_ADDR.现在针对DDR_ADDR,就可以设定具体的参数了.比如,你可以将最小长度设定为1600mils, 最大长度设为2500mils.这个参数的取得其实取决于你的时钟走线拓扑,因为按照走线要求,数据线,地址线等等都是以时钟线为基准的,所以,你必须先把时钟线布好,至少以后不能做大的改动,除非你能保证时钟线走线长度不变.这里我们假设你的时钟线长为1550mil+10mils,则显然你的地址线不能短于1560mils,我们取为1600mils.同时我们也可以得到数据线的走线范围为1525+25mils.类似我们设置好时钟和数据线的约束.至此,我们设置好了线长约束规则.下面的问题就是如何应用这些规则到net上去.设定好了Xnet以后,我们就可以在约束管理器中给这些Xnet添加约束. 这时,打开net》routing》total etch length,将右边brd名前+打开,下面则是所有的net名,拖动鼠标选中需要设置约束的那组信号,点击右键,弹出邮件菜单,选中菜单中的ECset Reference ,见下图.弹出对话框选中下拉列表中的DDR_ADDR,则对刚才选中的哪些xnet添加上了DDR_ADDR约束.类似的可以添加DDR_DATA,DDR_CLK约束.设置Xnet主要就是给相关的电阻加上model就可以了.。

利用Allegro实现嵌入式系统高速电路设计

利用Allegro实现嵌入式系统高速电路设计

张艺凡;张艺夕;李琪

【期刊名称】《微计算机信息》

【年(卷),期】2006(022)011

【摘要】本文首先简述了高性能ARM9微处理器EP9315集成的外设接口及硬件结构框架,提出了当前高速电路设计中的问题;然后,详细介绍了利用Allegro实现嵌入式系统中SDRAM和IDE总线接口的电路设计;最后以Cirrus Logic公司的

CS8952为例,阐述了物理层接口芯片的布线准则及其在Allegro中的实现.

【总页数】4页(P101-103,16)

【作者】张艺凡;张艺夕;李琪

【作者单位】430071,湖北武汉中国科学院武汉岩土力学所;430074,湖北武汉华中科技大学电信系;430071,湖北武汉中国科学院武汉岩土力学所

【正文语种】中文

【中图分类】TP273+.5

【相关文献】

1.利用Allegro实现万兆子卡的高速电路设计 [J], 詹萌;胡春晖

2.100MHz高速计数器在STM32F103系列嵌入式系统中的设计与实现 [J], 杨卫东;班崟峰;杨红天

3.利用Allegro实现嵌入式系统高速电路设计 [J], 张艺凡;张艺夕;李琪

4.基于嵌入式系统的串口高速采集DMA方式的实现 [J], 范娟;张伯珩;边川平;李爱玲

5.基于CPLD和嵌入式系统的高速数据采集系统的设计与实现 [J], 林德辉;道克刚;邓永刚;陈森

因版权原因,仅展示原文概要,查看原文内容请购买。

pads高速布线规则

pads高速布线规则高速布线规则SDRAM的布线规则该嵌入式系统使用64M字节的SDRAM扩展数据存储区,由两片K4S561632组成工作在32位模式下。

最高频率可达100M以上,对于SDRAM的数据线、时钟线、片选及其它控制信号需要进行线长匹配,由此提出以下布线要求:1. SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰。

走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线。

误差允许在20mil以内。

2. 地址,片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil。

尽量走成菊花链拓补。

可有效控制高次谐波干扰,可比时钟线长,但不能短。

3. SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

根据布线要求,在Allegro中设置不同的约束:针对线宽设置3 个约束SDRAM_CLK,SDRAM_ADDDR,SDRAM_DATA,设置完约束后将约束添加到对应的net上。

使得各个net都具有线宽、线距约束属性。

最后为不同的信号组选择合适的约束即可。

但是设置的约束在系统CPU内部是无法达到的。

因为EP9315为BGA封装。

pin间距1.27毫米,显然在CPU内部,线宽线距无法达到上述要求,利用Allegro设置CPU 特殊走线区域cpu_area。

并加上area属性,在此区域中另设置适合BGA内部走线的约束。

Xnet在IDE总线等长布线中的应用系统中的IDE接口设计EP9315强大的外设接口能力能够直接驱动IDE硬盘,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。

如图2所示其中的排阻起到了端接匹配的作用,但使得整个走线被分为好几个NET,而Allegro中常用的走线长度设置propagation_delay和relative_propagation_delay只能针对同一NET设置.IDE总线信号由EP9315扇出,要求EP9315到IDE 接口走线DD*+UBDD*(如图2中NET)等长,误差为+/-20mil,最简单的方法是分别设置DD*等长和UBDD*等长,误差各位+/-10mil,就可以达到要求,但是增加了布线难度,特别当DD*有较大绕线空间。

Allegro 教程之 基本规则设置 布线规则设置 线宽及线间距的设置

在PCB设计过程中,需要通过设置各种规则,以满足各种信号的阻抗。

比如,常用的高速差分线,我们常控的100欧姆,那么到底走多宽的线以及差分线之间的间距到底是多少,才能满足设计要求的100欧姆阻抗呢本文就对Allegro 种的基本规则设置做一个详细的讲解。

注:本文是基于Allegro 15 版本的。

对于16版本不适用。

首先需要打开规则管理器,可通过以下三种方式打开:一、点击工具栏上的图标。

二、点击菜单Setup->Constraints三、在命令栏内输入"cns" 并回车打开的规则管理器如下:在最上面一栏有一个On-line DRC,这是对画板过程中不停检测是否违反规则,并可产生DRC。

一般我们都默认开启。

可以实时查看产生的DRC 错误,并加以修正。

接下来的Spacing rule set 是对走线的线间距设置。

比如对于时钟线、复位线、及高速查分线。

我们可以再这里面加一规则,使其离其它信号线尽可能的远。

Physical(lines/vias)rule set 是针对各种物理规则设置,比如线宽,不同信号线的过孔等。

例如我们可通过电源网络的设置,使其默认线宽比普通信号走线更粗,已满足走线的载流能力。

现针对一个时钟及电源,分别设置间距规则和物理规则。

首先筛选网络,对于需要设置线间距规则的网络赋上Net_Spacing_Type 属性、而对于需要设置线宽规则的网络赋上Net_Physical_type 。

而对于即要线间距和线宽规则约束的网络,可将Net_Spacing_Type 及Net_Physical_type 属性同时赋上。

本例针对的时钟网络,只需要对其赋上Net_Spacing_Type ,方法如下:点击菜单Edit->Properties然后在右侧Find 一栏中选择Nets 。

如下图所示:如果你知道PCB上网络名,那么你可以直接在PCB上选择一个网络。

假如你并不知道到底哪个网络是时钟,那么你可以选择Find下面的More然后在弹出的对话框中筛选出时钟网络。

DDR SDRAM布线规则(pan)

DDR SDRAM布线规则(to)首先区别DDR SDRAM与SDRAM:SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR则是一个时钟周期内传输两次数据,在时钟的上升期和下降期各传输一次数据。

SDRAM的工作电压为3.3V,而DDR的工作电压为2.5V;SDRAM采用公共时钟同步,公共时钟同步是指在数据的传输过程中,总线上的驱动端和接收端共享同一个时钟源,在同一个时钟缓冲器(clock buffer)发出同相时钟的作用下,完成数据的发送和接收。

DDR SDRAM采用源同步,源同步就是指时钟选通信号clk伴随发送数据一起由驱动芯片发送。

所以在DDR的控制端需要有延迟补偿电路。

SDRAM关心建立时间,而DDR关心保持时间,DDR比SDRAM要求有更短的信号建立保持时间、更干净的参考电压、更紧密的走线匹配和新的I/O口信号,并且需要合适的终端电阻匹配。

因此在布线的时候注意等长布线。

关于建立时间和保持时间的概念详见附录。

DDR布线应注意的问题:内存的作用是用来存储数据的,写入1读出1,写入0读出0,因此必须保证数据访问正确。

产生数据访问错误的情况主要有如下两种:1、判决错误,0判成1,1判成0。

可能参考电平不准(为什么不准?信号线内阻造成的压降),也可能是加性干扰,或者阻抗不匹配引起信号畸变。

2、时序错误,不满足建立/保持时间,或者采样点相位错误,不在有效信号位置上。

触发器需要维持一段时间的能量供给才能正常工作,这个时间就是建立/保持时间。

只要解决好这两个问题,保证内存正确访问,内存电路就设计成功了。

为了满足建立保持时间,同频同相,采样正确,我们对走线的布线要求是:等长布线。

但是由于DDR有高速时钟信号,高速跳变的边沿,就必须考虑到在PCB板上存在传输线效应的问题,对于布线长度有了要求。

避免传输线效应的方法1、严格控制关键网线的走线长度。

如果采用CMOS或TTL电路进行设计,工作频率小于10MHz,布线长度应不大于7英寸。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SDRAM的布线规则基于Allegro嵌入式高速电路布线设计

1 引言随着嵌入式微处理器主频的不断提高,信号的传输处理速度越来越快,当系统时钟频率达到100MHZ以上,传统的电路设计方法和软件已无法满足高速电路设计的要求。

在高速电路设计中,走线的等长、关键信号的阻抗控制、差分走线的设置等越来越重要。

笔者所在的武汉华中科技大学与武汉中科院岩土力学所智能仪器室合作.以ARM9微处理器EP9315为核心的嵌入式系统完成工程检测仪的开发。

其中在该嵌入式系统硬件电路设计中的SDRAM和IDE等长走线、关键信号的阻抗控制和差分走线是本文的重点,同时以cirrus logic公司的网络物理层接13芯片cs8952为例详细介绍了网络部分的硬件电路设计,为同类高速硬件电路设计提供了一种可借鉴的方法。

2 硬件平台 2.1 主要芯片本设计采用的嵌入式微处理器是Cirrus Logic公司2004年7月推出的EP93XX系列中的高端产品EP9315。

该微处理器是高度集成的片上系统处理器,拥有200兆赫工作频率的ARM920T内核,它具有ARM920T内核所有的优异性能,其中丰富的集成外设接口包括PCMCIA、接口图形加速器、可接两组设备的EIDE、1/10/100Mbps以太网MAC、3个2.0全速HOST USB、专用SDRAM通道的LCD接口、触摸屏接口、SPI串行外设接口、AC97接口、6通道I2S接口和8*8键盘扫描接口.并且支持4组32位SDRAM的无缝连接等。

主芯片丰富的外设接口大大简化了系统硬件电路.除了网络控制部分配合使用Cirrus Logic公司的100Base—X/10Base-T物理层(PHY)接口芯片CS8952外,其他功能模块无需增加额外的控制芯片。

2.2 系统主体结构由图1可见.系统以微处理器EP9315为核心,具有完备的外设接口功能,同时控制工程检测仪。

IDE/CF卡接口为工程检测数据提供大容量移动存储设备;扩展32M的SDRAM作为外部数据存储空间;3个主动USB 接口支持USB键盘鼠标;LCD接口支持STN/TFT液晶和触摸屏.为用户提供友好的交互界面;1/10/100 Mbps以太网为调试操作系统时下载内核及工程检测时远程监控提供途径;面板按键为工程人员野外作业无法使用键盘鼠标时提供人机交互接口。

EP9315在操作系统下主频达到200M,总线频率100M,外设时钟为50M,数据线和地址。