实验八 计数器

数字电路实验指导书

实验一集成逻辑门电路逻辑功能的测试一、实验目的1.熟悉数字逻辑实验箱的结构、基本功能和使用方法。

2.掌握常用非门、与非门、或非门、与或非门、异或门的逻辑功能及其测试方法。

二、实验器材1.数字逻辑实验箱DSB-3 1台2. 万用表 1只3.元器件: 74LS00(T065) 74LS04 74LS55 74LS86 各一块导线若干三、实验说明1.数字逻辑实验箱提供5 V + 0.2 V的直流电源供用户使用。

2.连接导线时,为了便于区别,最好用不同颜色导线区分电源和地线,一般用红色导线接电源,用黑色导线接地。

3.实验箱操作板部分K0~K7提供8位逻辑电平开关,由8个钮子开关组成,开关往上拨时,对应的输出插孔输出高电平“1”,开关往下拨时,输出低电平“0”。

4.实验箱操作板部分L0~L7提供8位逻辑电平LED显示器,可用于测试门电路逻辑电平的高低,LED亮表示“1”,灭表示“0”。

四、实验内容和步骤1.测试74LS04六非门的逻辑功能将74LS04正确接入面包板,注意识别1脚位置,按表1-1要求输入高、低电平信号,测出相应的输出逻辑电平。

表1-1 74LS04逻辑功能测试表2.测试74LS00四2输入端与非门逻辑功能将74LS00正确接入面包板,注意识别1脚位置,按表1-2要求输入高、低电平信号,测出相应的输出逻辑电平。

3.测试74LS55 二路四输入与或非门逻辑功能将74LS55正确接入面包板,注意识别1脚位置,按表1-3要求输入信号,测出相应的输出逻辑电平,填入表中。

(表中仅列出供抽验逻辑功能用的部分数据)4.测试74LS86四异或门逻辑功能将74LS86正确接入面包板,注意识别1脚位置,按表1-4要求输入信号,测出相应的输出逻辑电平。

五、实验报告要求1.整理实验结果,填入相应表格中,并写出逻辑表达式。

2.小结实验心得体会。

3.回答思考题若测试74LS55的全部数据,所列测试表应有多少种输入取值组合?实验二集成逻辑门电路的参数测试一、实验目的1.掌握TTL和CMOS与非门主要参数的意义及测试方法。

实验八程序计数器PC 实验

实验八程序计数器PC 实验【实验要求】利用CP226实验箱上的K16…K23 开关做为DBUS 数据的输入端,其它开关做为控制信号的输入端,实现程序计数器PC预置与加1功能。

【实验目的】掌握模型机中程序计数器PC的功能及其功能实现的工作原理与控制方法,程序执行过程中顺序和跳转的实现。

【主要集成电路芯片及其逻辑功能】1. 计数器74HC161本实验所涉及的主要集成电路芯片之一为74HC161,用于实现程序计数器PC预置与加1功能。

74HC161是四位二进制可预置同步加法计数器,芯片包含一条时钟输入线CP、四条数据输入线(P0~P3)、一条清零信号线MR、二条使能信号线CEP和CET、一条预置信号线PE、四条数据输出线(Q0~Q3)、一条进位输出TC(TC= Q0·Q1·Q2·Q3·CET)。

74HC161引脚结构如下图所示,其功能逻辑如下表所示。

2. 数据选择器74HC151本实验所涉及的主要集成电路芯片之二为74HC151,用于指令执行过程中形成跳转条件。

74HC151为互补输出的8选1数据选择器,芯片包含三条选择控制线(地址端,S0、S1、S2)、8条数据输入线(I0~I7)、二条互反输出线(Z 、~Z)、二条使能信号线E 。

74HC161引脚结构如下图所示,其功能逻辑如下表所示。

【实验涉及的逻辑电路及原理】 1. 程序计数器PC程序计数器PC 是由两片74HC161构成的八位带预置计数器,预置数据来自于数据总线。

PC 输出可以通过由PCOE(低电平有效)控制的74HC245送到地址总线,还可以通过由PCOE_D (低电平有效)控制的另一片74HC245送回到数据总线。

程序计数器PC 实验原理逻辑电路如下图所示,其中PC+1、LDPC 、RST 、PCOE_D 、PCOE 分别为计数器使能、计数器预置、计数器清0、数据总线收发器使能、地址总线收发器使能控制信号,CK 为脉冲信号。

实验八M序列发生及眼图观测实验

实验八 M序列发生及眼图观测实验

四、实验原理

1、M序列

移位时 钟节拍

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

表1 m序列发生器状态转移流程图

第1级 a n1

0 1 0 0 1 1 0 1 0 1 1 1 1 0 0 0 1

第2级

an2

0 0 1 0 0 1 1 0 1 0 1 1 1 1 0 0 0

二、实验预习要求

认真预习《通信原理》中关于M序列及 眼图有关章节的内容。

通信工程专业实验室

实验八 M序列发生及眼图观测实验

三、实验仪器仪表

1、70MHz双踪数字存储示波器一台 2、实验模块:

数字编码模块——M序列输出 数字时钟信号源模块 眼图观测及白噪声输出模块

通信工程专业实验室

实验八 M序列发生及眼图观测实验

通信工程专业实验室

实验八 M序列发生及眼图观测实验

四、实验原理

2、眼图

所谓“眼图”,就是由解调后经过低通 滤波器输出的基带信号,以码元定时作为同 步信号在示波器屏幕上显示的波形。干扰和 失真所产生的传输畸变,可以在眼图上清楚 地显示出来。因为对于二进制信号波形,它 很像一只人的眼睛。

眼图是指利用实验的方法估计和改善(通

实验八 M序列发生及眼图观测实验

实验八 M序列发生及 眼图观测实验

【实验性质】:验证性实验

通信工程专业实验室

实验八 M序列发生及眼图观测实验

一、实验目的

1、掌握M序列等伪随机码的发生原理。 2、了解伪随机码在通信电路中的作用。 3、掌握眼图的观测。

通信工程专业实验室

实验八 M序列发生及眼图观测实验

t

实验八 可编程定时计数器8253的Proteus仿真实验

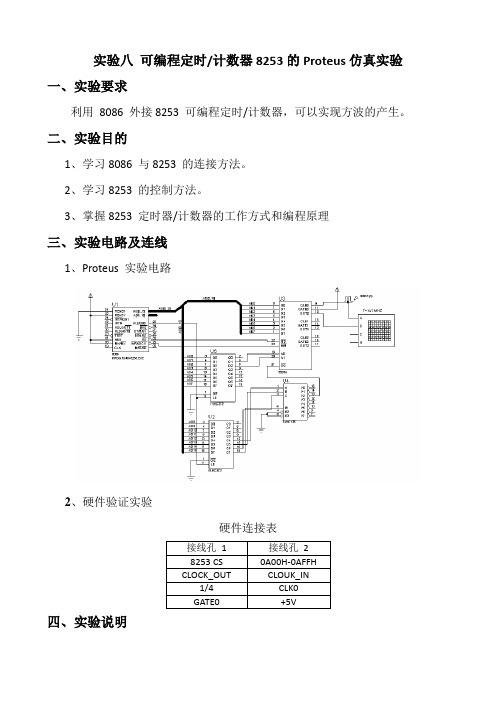

实验八可编程定时/计数器8253的Proteus仿真实验一、实验要求利用8086 外接8253 可编程定时/计数器,可以实现方波的产生。

二、实验目的1、学习8086 与8253 的连接方法。

2、学习8253 的控制方法。

3、掌握8253 定时器/计数器的工作方式和编程原理三、实验电路及连线1、Proteus 实验电路2、硬件验证实验硬件连接表四、实验说明1、8253 芯片介绍8253 是一种可编程定时/计数器,有三个十六位计数器,其计数频率范围为0-2MHz,用+5V 单电源供电。

2、8253的功能用途:(1)延时中断(2)可编程频率发生器(3)事件计数器(4)二进制倍频器(5)实时时钟(6)数字单稳(7)复杂的电机控制器3、8253 的六种工作方式:(1)方式0:计数结束中断(2)方式l:可编程频率发生(3)方式2:频率发生器(4)方式3:方波频率发生器(5)方式4:软件触发的选通信号(6)方式5:硬件触发的选通信号五、实验程序流程图六、实验步骤1、Proteus 仿真a.在 Proteus 中打开设计文档“8253_STM.DSN”;b.建立实验程序并编译,仿真;c.如不能正常工作,打开调试窗口进行调试。

参考程序:CODE SEGMENT;H8253.ASMASSUME CS:CODESTART:JMP TCONTTCONTROEQU0A06HTCON0 EQU0A00HTCON1 EQU0A02HTCON2 EQU0A04HTCONT:MOV DX,TCONTROMOV AL,16H ;计数器0,只写计算值低8 位,方式3,二进制计数OUT DX,ALMOV DX,TCON0MOV AX,20 ;时钟为1MHZ,计数时间=1us*20=20us,输出频率50KHZOUT DX,ALJMP $CODE ENDSEND START2、实验板验证a.通过USB 线连接实验箱b.按连接表连接电路c.运行PROTEUS 仿真,检查验证结果。

显微镜直接计数和平板菌落计数

测定结果误差较大、操作比较烦琐、需要的时间较长。

三、主要器材

1. 活材料:啤酒酵母(S6) 、 解脂假丝酵 母(S5)

2. 染色液:复红染色液(或结晶紫,美兰) 3. 器材:显微镜、血球计数板、载玻片、 盖玻片 、擦镜纸、吸水纸、计数器、滴管、 无菌吸管、无菌培养皿、马铃薯葡萄糖培养 基。

实验八 微生物显微镜直接计数

和平板菌落计数

一. 实验目的

1. 学习、掌握显微镜直接计数法和平板菌 落计数法; 2. 了解血球计数板的构造、计数原理和计 数方法,掌握显微镜下直接计数的技能。

二、实验原理

测定微生物细胞数量的方法很多,通 常采用的有显微镜直接计数法和平板菌落 计数法。

(一)显微镜直接计数法

后要尽快倒入冷至45℃左右的培养基15 ml ,并迅速旋转混匀。否则,菌体会 吸附在皿底,不易分散形成单菌落。

(二)平板菌落计数法 1. 编号 将平皿和试管分别标记浓度。 2. 稀释样品 将酵母菌样品进行适当稀释。 3. 取样 用无菌吸管准确吸取10-4、 10-5、 10-6稀释菌液各1 ml,放0.2 ml 于无菌平皿。 4. 倒平板 于上述平皿中尽快倒入融化并 冷却到45℃左右的培养基15 ml ,旋转混匀。 5. 计数 培养48 h后取出培养皿,算出同一 稀释度的三个平皿中平均菌落数,再按公 式计算每毫升样品中活菌数。

平板菌落计数法示意图

五、实验报告

(一)实验结果 1. 将直接计数结果记录于表中。 2. 将平板菌落计数结果记录于表中。

(二)思考题 某单位要求知道一种干酵母粉中的活菌

存活率,请设计1-2种可行的检测方法。

六.注意事项

1.计数器必须洗干净,勿刷 ; 2. 千万注意勿损坏计数器 。 3. 平板菌落计数时,测定样品移入培养皿

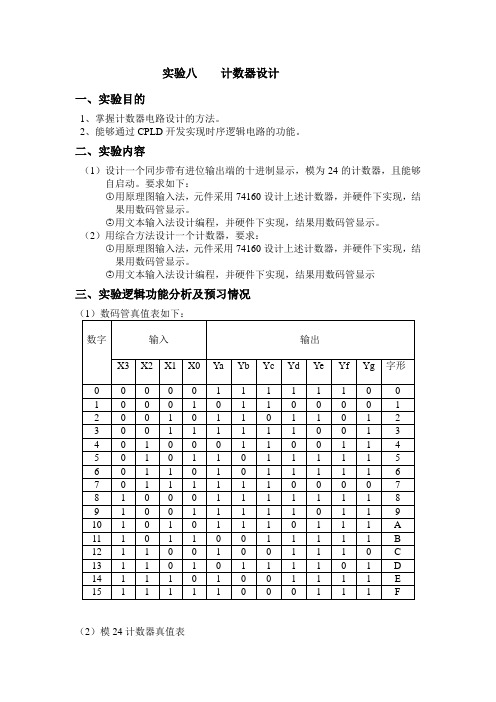

实验八计数器设计(可编程实验)

实验八计数器设计一、实验目的1、掌握计数器电路设计的方法。

2、能够通过CPLD开发实现时序逻辑电路的功能。

二、实验内容(1)设计一个同步带有进位输出端的十进制显示,模为24的计数器,且能够自启动。

要求如下:○1用原理图输入法,元件采用74160设计上述计数器,并硬件下实现,结果用数码管显示。

○2用文本输入法设计编程,并硬件下实现,结果用数码管显示。

(2)用综合方法设计一个计数器,要求:○1用原理图输入法,元件采用74160设计上述计数器,并硬件下实现,结果用数码管显示。

○2用文本输入法设计编程,并硬件下实现,结果用数码管显示三、实验逻辑功能分析及预习情况(2)模24计数器真值表四、实验过程模为24的计数器(一)采用原理图设计模为24的计数器(1)启动MAX+plusII软件;(2)创建一个新工程;(3)原理图编辑;编辑原理图,如下(4)保存、编译原理图;(5)启动波形图编译器;设计End time为1.0us,Grid Size为50.0ns。

结果如下:(6)时间分析图(7)利用真值表验证所设电路的逻辑功能;(8)经过验证保存仿真原理图。

(二)采用文本文档设计模为24的计数器(1)启动MAX+plusII软件;(2)创建一个新工程;○1启动文本编译器;○2编译VHDL语言程序为Library ieee;Use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity mo24cx isPort(CLK:in std_logic;ohigh,olow:out std_logic_vector(6 downto 0);CO :out std_logic);End;Architecture rtl of mo24cx issignal h_temp,l_temp:std_logic_vector(3 downto 0):="0000";signal CO_temp : std_logic;beginprocess(CLK)beginCO_temp <= h_temp(1) and l_temp(1) and l_temp(0);if(CLK'event and CLK = '1')thenif(h_temp = "0010" and l_temp = "0011" )thenh_temp <= "0000";l_temp <= "0000";elsif(l_temp = "1001")thenh_temp <= h_temp+1;l_temp <= "0000";elsel_temp <= l_temp+1;end if;end if;end process;process(l_temp)begincase l_temp iswhen "0000" => olow <= "1111110";when "0001" => olow <= "0110000";when "0010" => olow <= "1101101";when "0011" => olow <= "1111001";when "0100" => olow <= "0110011";when "0101" => olow <= "1011011";when "0110" => olow <= "1011111";when "0111" => olow <= "1110000";when "1000" => olow <= "1111111";when "1001" => olow <= "1111011";when others => olow <= "ZZZZZZZ";end case;end process;process(h_temp)begincase h_temp iswhen "0000" => ohigh <= "1111110";when "0001" => ohigh <= "0110000";when "0010" => ohigh <= "1101101";when "0011" => ohigh <= "1111001";when "0100" => ohigh <= "0110011";when "0101" => ohigh <= "1011011";when "0110" => ohigh <= "1011111";when "0111" => ohigh <= "1110000";when "1000" => ohigh <= "1111111";when "1001" => ohigh <= "1111011";when others => ohigh <= "ZZZZZZZ";end case;end process;CO <= CO_temp;end;○3启动波形图编译器;○4时间分析图○5利用真值表验证所设电路的逻辑功能;○6经过验证保存仿真原理图。

实验八-环境因素对微生物的影响

实验八-环境因素对微生物的影响微生物是地球上最早出现的生物之一,其生存、繁殖和活动受到许多环境因素的影响。

本实验将研究不同环境因素对微生物的影响,了解微生物的适应能力和抗逆能力。

1.实验目的通过本实验,可以了解下列内容:(1)了解微生物生长和繁殖所需的环境条件;(3)了解微生物的适应能力和抗逆能力。

2.实验器材大肠杆菌、葡萄球菌、石蜡培养皿、菌落计数器、培养基、平板、灭菌器、恒温箱、植物保温箱、紫外灯等。

3.实验方法(1)不同温度下对微生物的影响将大肠杆菌、葡萄球菌分别接种在含有培养基的石蜡培养皿上,分别放置在20℃、37℃、45℃恒温箱中孵育24小时。

观察不同温度下两种微生物的生长情况。

(5)紫外线辐射对微生物的影响4.实验结果大肠杆菌在20℃下生长缓慢,呈现线形生长,37℃时生长最佳,生长形态为圆形或不规则形;45℃时生长受到抑制,只有极少数生长。

葡萄球菌在20℃下无生长,37℃时表现最佳生长形态,45℃时生长受到抑制,只有极少数生长。

大肠杆菌在室内光照充足的条件下生长最快,黑暗中生长受到一定抑制;葡萄球菌在室内和黑暗条件下均较慢,没有明显差别。

大肠杆菌在pH为5、9的条件下不能生长,只有在pH为7的中性条件下生长正常;葡萄球菌在pH为5、7、9的条件下均有较好的生长,生长与pH无明显相关。

大肠杆菌在0.2%~1%的NaCl浓度范围内有较好的生长,1.2%时生长受到抑制,但仍有部分生长;葡萄球菌在0.2%~0.6%间有良好的生长,0.8%~1.2%时生长明显受到抑制。

两种微生物在不同时间的辐射处理下,生长都出现受损状况,但大肠杆菌受损情况更明显。

5.实验分析微生物生存条件受到温度、光照、pH、盐度等多个环境因素的影响。

大肠杆菌在较宽的温度范围内生长正常;在光照条件下,适度的光照有利于其生长,黑暗环境有一定抑制作用;在pH条件下,中性条件为最适宜的生存环境;在盐度范围内,0.2%~1%的浓度范围内生长良好;对紫外线的抵抗力相对较弱,会对其生长造成较明显的损害。

4位二进制计数器

实验八 4位二进制计数器74x163的设计一、实验目的熟悉QuartusⅡ仿真软件的基本操作,并用VHDL/Verilog语言或者逻辑图完成4位二进制计数器74x163的设计。

二、实验内容用VHDL语言设计由边沿触发式D触发器构成的74x163四位二进制计数器,并进行仿真分析;(参看新、老教材中器件74x163的逻辑功能及其VHDL源代码)三、实验原理1.计数器是数字系统中用得较多的基本逻辑器件。

2.计数器的种类很多。

按时钟脉冲输入方式的不同,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器和非二进制计数器;按计数过程中数字增减趋势的不同,可分为加计数器、减计数器和可逆计数器。

四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII(或MaxplusⅡ)软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱(由于实验室条件有限,无法实现)。

实验步骤:1)编写源代码。

打开QuartusII软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件(画逻辑图实现则新建block文件)。

2)按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”。

3)编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

编译结果有错误或警告,则将要调试修改直至文件编译成功。

4)波形仿真及验证。

在编译成功后,点击Waveform开始设计波形。

点击“insert the node”,按照程序所述插入节点。

任意设置输入节点的输入波形…点击保存按钮保存。

5)时序仿真。

将波形区域分段显示,如每个10.0ns重复一次步骤四,分别设置不同的a,b的输入波形,点击保存按钮保存,从而得出相应的结果,最后形成完整的连续的时序仿真图。

数字电路实验3计数器

实验八计数器一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理。

2.熟悉掌握常用中规模集成电路计数器及其应用方法。

二、实验原理和电路所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。

根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。

根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的。

根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器异步二进制加法计数器是比较简单的。

图1.8.1(a)是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图1.8.1(b)和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FFO(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的C P端接FF0的Q0端,因而当FFO(Q O)由1→ 0时,FF1翻转。

类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

从波形图可看到,Q0 的周期是CP周期的二倍;Q1是Q0的二倍,CP的四倍;Q2是Q1 的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0的八倍,CP的十六倍。

实验八定时器计数器8253实验

8253是Intel公司生产的一款可 编程定时器计数器。

它具有3个独立的16位计数器, 每个计数器都可以独立编程和控

制。

8253的计数器可以用于产生时 间间隔、脉冲信号、PWM(脉

宽调制)等。

8253的工作原理

825ቤተ መጻሕፍቲ ባይዱ的每个计数器都有一个预置 值,当计数达到预置值时,计数 器会自动回置并触发一个中断或

实验八:定时器计数器8253实验

contents

目录

• 实验简介 • 8253定时器计数器概述 • 实验步骤与操作 • 实验结果与分析 • 实验总结与思考

01 实验简介

实验目的

掌握8253定时器计 数器的工作原理。

了解定时器在计算机 系统中的应用。

学习如何编程控制 8253定时器计数器。

实验设备

01

微机实验箱

02

8253定时器计数器芯片

03

示波器

04

信号发生器

02 8253定时器计数器概述

定时器计数器的基本概念

定时器计数器是一种用于产生 时间间隔或计数的电子设备。

它通常由石英晶体振荡器驱动, 以提供稳定的计时基准。

定时器计数器广泛应用于计算 机、通信、自动化等领域。

8253的特性和功能

配置8253定时器计数器

设置工作模式

根据实验要求,选择适当的定时/计数 模式,如计数模式、定时模式或门控 模式等。

设置定时/计数初值

启动定时/计数

通过微处理器发送控制信号,启动 8253定时器计数器的定时/计数操作。

根据实验要求,设置适当的定时/计数 初值,以满足实验条件。

启动和观察实验结果

启动实验

加强实践环节

为了更好地理解和掌握相关知识,建议增加更多的实践环节,例 如组织小组讨论、分享经验等。

实验八 血球计数板的使用

四、实验内容与操作步骤

(一)血球计数板的使用 一

1. 计数样品制备:按无菌操作要求,用1mL无菌吸管自稀释 倍的酵母菌 计数样品制备:按无菌操作要求, 无菌吸管自稀释10倍的酵母菌 无菌吸管自稀释 培养液试管中吸取菌液1mL移人 移人9mL无菌水中,充分混匀,即得稀释 无菌水中, 培养液试管中吸取菌液 移人 无菌水中 充分混匀, 100倍的计数样品。原则以每个小格菌数为 倍的计数样品。 个为宜来记数进行稀释。 倍的计数样品 原则以每个小格菌数为5-10个为宜来记数进行稀释。 个为宜来记数进行稀释 2. 清洗计数板:将血球计数板及专用的厚盖玻片用药棉沾取 %酒精轻轻 清洗计数板:将血球计数板及专用的厚盖玻片用药棉沾取95% 擦洗,然后用自来水冲洗,再让其自然晾干或吸水纸吸干。 擦洗,然后用自来水冲洗,再让其自然晾干或吸水纸吸干。 3. 滴加菌液:将盖玻片盖在计数板的方格网上,用无菌吸管 或无菌玻棒 滴加菌液:将盖玻片盖在计数板的方格网上,用无菌吸管(或无菌玻棒 或无菌玻棒) 吸取少许稀释100倍的酵母菌液,从盖玻片的一端注入,使菌液沿二玻 倍的酵母菌液, 吸取少许稀释 倍的酵母菌液 从盖玻片的一端注入, 片间渗入,勿使菌液流到盖玻片或两边平台上, 片间渗入,勿使菌液流到盖玻片或两边平台上,多余的菌液则用吸水纸 吸去。 吸去。

ቤተ መጻሕፍቲ ባይዱ

五、思考题

1.计算每毫升(每克 所测样品的含菌数 .计算每毫升 每克 所测样品的含菌数? 每克)所测样品的含菌数 2.用血球计数板测定微生物细胞数量有何 . 优缺点?

中格

25X16规格 规格

一个中格的小格

在进行观察计数 时,由于菌体在血球 计数板上处于不同的 空间位置, 空间位置,要在不同 的焦距下才能看到。 的焦距下才能看到。 所以观察时必须不断 调节微调螺旋方能数 到全部菌体, 到全部菌体,防止遗 漏。如菌体位于小格 的线上, 的线上,计数时则数 上线不数下线, 上线不数下线,数左 线不数右线,这样做, 线不数右线,这样做, 即可减少误差。 即可减少误差。酵母 菌的芽体细胞达到母 细胞大小一半时, 细胞大小一半时,即 可作为两个菌体计算, 可作为两个菌体计算, 每个样品应重复计数2每个样品应重复计数 3次(每次数值差数不应 次 每次数值差数不应 过大,否则应重测)再 过大,否则应重测 再 取其平均值。 取其平均值。

实验8 数字系统测试

实验八数字系统测试一、实验目的1熟悉逻辑分析仪的主要应用;2掌握用逻辑分析仪测试数字系统的方法。

二、实验内容1 测试74LS160/74LS161的功能;2 观察60进制计数器的输出数据流;3 检测毛刺脉冲。

三、实验器材1 DSO-2902/512K型测试仪 1台2 标准信号发生器 1台3 数字实验箱 1台4 数字电路实验板 1块5 74LS160/74LS161 2片6 3线-8线译码器74LS138 1片7 双下降沿JK触发器74LS112 2片8 74LS00 1片四、实验要求1 学生实验前要查阅有关计数器、竞争冒险等的参考书;2 学生实验中要独立操作每一个步骤,并根据相关原理分析问题和解决问题。

五、实验步骤1 测试74LS160/74LS161(1)把74LS160/74LS161插入数字电路实验板,连接电源Vcc、GND,预置数端、复位端、使能端EP和ET 都接高电平,CLK端接100Hz脉冲。

(2)把CLK端同时接到“逻辑POD盒”的D0通道,把74LS160/74LS161的Q3Q2Q1Q0依次接到“逻辑POD盒”的D4D3D2D1通道。

注意小心接线,避免损坏测试钩和测试钩连线。

(3)设置通道名称:“Chan D 0”→“CLK”,“Chan D 1”→“Q0”,“Chan D 2”→“Q1”,“Chan D 3”→“Q2”,“Chan D 4”→“Q3”。

(4)设置采样速率为“10kSa(100μs)”,设置触发字(Word)为“00000000”。

(5)打开实验箱电源。

(6)点“”按钮,捕捉到数据后点“”按钮停止捕捉,观察逻辑分析仪波形显示区和数据显示区,画出74LS160/74LS161的计数工作波形图和状态转换图。

试分析74LS160/74LS161功能是否正常。

(7)如果把触发字设置为“00001000”, 观察逻辑分析仪波形显示区和数据显示区有何变化?为什么? 2 观察60进制计数器的输出数据流(1)用两片74LS160/74LS161设计一个同步60进制计数器,要求所用状态对应十进制数“00”~“59”。

(整理)实验八用气垫导轨验证动量守恒定律.

实验八 用气垫导轨验证动量守恒定律[实验目的]1.观察弹性碰撞和完全非弹性碰撞现象。

2.验证碰撞过程中动量守恒和机械能守恒定律。

[实验仪器]气垫导轨全套,MUJ-5C/5B 计时计数测速仪,物理天平。

[实验原理]设两滑块的质量分别为m 1和m 2,碰撞前的速度为10v 和20v ,相碰后的速度为1v 和2v 。

根据动量守恒定律,有2211202101v m v m v m v m +=+ (1) 测出两滑块的质量和碰撞前后的速度,就可验证碰撞过程中动量是否守恒。

其中10v 和20v 是在两个光电门处的瞬时速度,即∆x /∆t ,∆t 越小此瞬时速度越准确。

在实验里我们以挡光片的宽度为∆x ,挡光片通过光电门的时间为∆t ,即有220110/,/t x v t x v ∆∆=∆∆=。

实验分两种情况进行:1. 弹性碰撞两滑块的相碰端装有缓冲弹簧,它们的碰撞可以看成是弹性碰撞。

在碰撞过程中除了动量守恒外,它们的动能完全没有损失,也遵守机械能守恒定律,有2222112202210121212121v m v m v m v m +=+ (2) (1)若两个滑块质量相等,m 1=m 2=m ,且令m 2碰撞前静止,即20v =0。

则由(1)、 (2)得到1v =0, 2v =10v 即两个滑块将彼此交换速度。

(2)若两个滑块质量不相等,21m m ≠,仍令20v =0,则有 2211101v m v m v m += 及2222112101212121v m v m v m += 可得1021211v m m m m v +-=, 1021122v m m m v +=当m 1>m 2时,两滑块相碰后,二者沿相同的速度方向(与10v 相同)运动;当m 1< m 2时,二者相碰后运动的速度方向相反,m 1将反向,速度应为负值。

2. 完全非弹性碰撞将两滑块上的缓冲弹簧取去。

在滑块的相碰端装上尼龙扣。

计数器实验原理

计数器实验原理

计数器实验的原理是基于电子数字技术实现的。

它通过将输入的电信号进行计数,并根据给定的规则输出相应的计数结果。

计数器的工作原理通常利用触发器和逻辑门电路来实现。

触发器是一种能够存储和传递信息的电子器件。

计数器中使用的触发器被称为“触发型计数器”,它能够周期性地切换输出状态,从而实现计数功能。

计数器通常有一个输入端,称为时钟输入。

时钟输入接收外部的时钟信号,根据时钟信号的变化来切换触发器的状态。

当时钟信号的边沿(上升沿或下降沿)到来时,触发器的状态会发生变化。

计数器一般有几个输出端,每个输出端对应一个计数值。

当时钟信号到来时,计数器根据规定的计数规则改变输出的计数值。

不同类型的计数器有不同的计数规则,常见的有二进制计数器、十进制计数器和BCD码计数器等。

计数器可以实现多种功能,如正向计数、负向计数、加法计数、减法计数、循环计数等。

通过不同的触发器和逻辑门的组合,可以实现各种复杂的计数功能。

计数器广泛应用于各个领域,如计算机、通信、测量等。

它们能够对事件、信号、数据等进行计数和统计,提供了有效的计数和计量手段。

微机实验八-8253方波实验实验报告

计算机科学与技术系实验报告专业名称计算机科学与技术课程名称微机原理与接口技术项目名称 8253方波实验班级学号姓名同组人员无实验日期 2016/06/28一、实验目的与要求1、了解8253的内部结构,工作原理;了解8253与8088的接口逻辑;熟悉8253的控制寄存器和初始化编程方法,熟悉8253的6中工作方式 二、实验逻辑原理图与分析(汇编—流程图) 2.1 画实验逻辑原理图AD15~AD0ALE A16/s3~A19/s6BHEDT/R DEN RD WR M/IOINTA INTRMN/MXClK READY RESET82828288收发器STB D7~D0RD WR A0A1CLK0GATE0OUT CLK GATE1OUT OUT2GATE2CLK22M+5V 发光管或蜂鸣器译码器CS2.2 逻辑原理图分析实验原理与分析:由于实验是使用8253的计数器0和计数器1实现对输入时钟频率的两级分频,得到一个周期为1S 的方波。

故8253通信实验需要8253A 芯片,8282地址锁存器,用于8086CPU 与8253A 芯片地址线的连接,8286收发器用于8086CPU 与8253A 芯片数据线的连接,通过地址译码器实现片选信号(CS )的选通。

8253的内部结构,读/写控制逻辑 :决定三个计数器和控制字寄存器中哪一个能进行工作,并控制内部总线上数据传送的方向;控制寄存器:接收从CPU 来的控制字,并由控制字的D7、D6位的编码决定该控制字写入哪个计数器的控制寄存器,控制寄存器只能写入,不能读出;计数器: 当8253用作计数器时,加在CLK 引脚上脉冲的间隔可以是不相等的;当它用作定时器时,则在CLK 引脚应输入精确的时钟脉冲,8253所能实现的定时时间,取决于计数脉冲的频率和计数器的初值,即:定时时间=时钟脉冲周期Tc ×预置的计数初值n 。

三、 程序分析3.1、程序功能使用8253的计数器0和计数器1实现对输入时钟频率的两级分频,得到一个周期为1秒的方波,用此方波控制蜂鸣器,发出报警信号,也可以将输入脚接到逻辑笔上来检验程序是否正确3.2程序代码分析写8253控制字:选择计数器0,计数器的写格式为:先写低地址在写高地址,计数器0的工作在方式2(分频)BCD 码计数 端口地址为:0B003HD 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 1 0 1 0 1 1 0 0BCD 计数MOV DX,COM_ADDR MOV AL,35HOUT DX,AL ;计数器T0设置在模式2状态,BCD 计数 写入计数器0的初始值(10000H )端口地址0B000H MOV DX,T0_ADDR MOV AL,00H OUT DX,ALMOV AL,10H ;CLK0/1000 OUT DX,AL写8253控制字:选择计数器1,计数器的写格式为:先写低地址在写高地址,计数器0的工作在方式3(方波)BCD 码计数 端口地址为:0B003HD 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 1 1 1 0 1 1 1 0BCD 计数MOV DX,COM_ADDRMOV AL,77HOUT DX,AL ;计数器T1为模式3状态,输出方波,BCD 码计数 写入计数器0的初始值(20000H )端口地址0B001H MOV DX,T1_ADDR MOV AL,00H OUT DX,AL MOV AL,20HOUT DX,AL ;CLK1/1000 JMP $ ;OUT1输出1s 的方波 END START四、实验数据和结果分析先写低8位后写高8位 方式2计数器0 先写低8位后写高8位 方式3计数器14.1 实验结果数据实验结果:二极管的关断和导通的频率每隔0.5秒亮一次,0.5秒灭4.2 结果数据分析根据定时器/计数器8253的工作原理:8253具有3个独立的计数通道,采用减1计数方式。

实验八 时序逻辑电路设计实验

实验八时序逻辑电路设计实验一、实验概述本实验是使用74LS74双D触发器构成一个扭环形计数器,以及使用74LS112双JK触发器构成三进制加法计数器。

二、实验目的1、掌握简单的时序电路的设计方法2、掌握简单时序电路的调试方法三、实验预习要求1、查找74LS74、74LS112、74LS00芯片引脚图,并熟悉引脚功能2、复习教材中异步2n进制计数器构成方法及同步2n进制计数器构成方法的内容3、复习同步时序电路和异步时序电路的设计方法4、设计画出用74LS74构成异步四进制减法计数器的逻辑电路图5、设计画出用74LS112构成同步四进制加法计数器的逻辑电路图四、实验原理时序逻辑电路是数字逻辑电路的重要组成部分,时序逻辑电路又称时序电路,主要由存储电路和组合逻辑电路两部分组成。

它和我们熟悉的其他电路不同,其在任何一个时刻的输出状态由当时的输入信号和电路原来的状态共同决定,而它的状态主要是由存储电路来记忆和表示的。

同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路而言,往往具有难度大、电路复杂并且应用范围广的特点。

时序逻辑电路通常可以分为同步时序逻辑电路和异步时序逻辑电路两大类。

同步时序逻辑电路从构成方式来讲,同步时序电路所有操作都是在同一时钟严格的控制下步调一致地完成的。

从电路行为上,同步电路的时序电路公用同一个时钟,而所有的时钟变化都是在时钟的上升沿(或下降沿)完成的。

同步逻辑是时钟之间存在固定因果关系的逻辑,所有时序逻辑都是在同源时钟控制下运行。

注意,在用Verilog HDL实现时,并不要求是同一时钟,而是同源时钟。

所谓的同源时钟是指同一个时钟源衍生频率比值为2的幂次方,且初相位相同的时钟。

异步时序逻辑电路异步时序逻辑电路,顾名思义就是电路的工作节奏不一致,不存在单一的主控时钟,主要是用于产生地址译码七、FIFO和异步RAM的读写控制信号脉冲。

除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路状态改变完全有外部输入的变化直接引起。

注意广度和划消试验[整理版]

![注意广度和划消试验[整理版]](https://img.taocdn.com/s3/m/79242ca9f021dd36a32d7375a417866fb84ac046.png)

实验八注意广度和划消实验一注意广度一.实验目的:通过测试视觉的注意广度,学习用速度测量注意广度的程序,并了解影响注意广度的条件。

二.器材1.JGW—B心理实验台速示器单元,记录用纸。

2.点子图卡片2组,每组13张,每张卡片上有点子3—15个不等:其中第一组卡片上的点子为规则排列,第二组卡片上的点子为不规则排列。

3.背景卡片一张,练习卡片一张。

三.步骤1.主试将每组卡片随机排列好,在记录纸上标明卡片的排列顺序及点子的个数。

2.接上电源:速示器电源选择“ON”,灯亮表示接通。

用明度测试卡调节A、B视场的明度达到基本一致;在“工作方式选择”栏,将A选“定时”,B选“背景”,选“A—B”顺序方式;在“时间选择”栏,将A定位“0100”。

3.将背景卡片输入B现场。

被试坐在桌前,面部贴紧速示器观察窗,两眼注视屏幕中心红点。

4.指导语:“请你注视眼前的注视点(红点),当我发出‘预备’口令后,将出现一些黑色圆点,这些黑点呈现时间很短,你要注意看,并迅速报告有几个黑色圆点。

下面我们练习两次。

”5.练习卡片输入A视场。

主试发出“预备”口令1—2秒后按速示器“触发”键,启动速示器,呈现时间为100毫秒。

6.正式实验,,将第一组的13张点子图卡片按记录纸上的排列顺序逐张放入A视场。

依照上述步骤进行第一组的实验。

主试则在记录表上记下反应结果。

7.休息一分钟,依照上述步骤继续进行第二组材料的实验。

8.两组实验完毕后,要求被试写出其判断点子数量策略。

四.结果被试种类百分数%被试一规则图形100 不规则图形69.2被试二规则图形100 不规则图形53.8被试三规则图形92.3 不规则图形46.2五.讨论1.注意的广度因注意对象的特点的变化而有所不同。

一般说来,注意对象的组合越集中,排列越有规律,相互之间能成为有机联系的整体,注意的范围就越大。

2. 活动任务越多、复杂,越需要关注细节的注意过程,注意的广度就越小,活动任务越少,注意范围就越大。

实验八 鸡血细胞计数

鸡红血细胞计数一实验目的和内容目的:掌握利用血球计数板计数动物红血细胞的方法内容:认识血球计数板的构造,测定鸡血样本单位体积红细胞的数量。

二实验原理应用显微镜的成像原理,并借助血细胞计数板,计算单位体积的细胞或微小生物的数量。

三实验材料、用品材料:鸡血红细胞悬液(1份鸡血+100份0.17mol/L氯化钠溶液),无菌水,显微镜,擦镜纸,吸水纸药品:0.17mol/L氯化钠溶液仪器:吸管及胶头、细胞计数板及计数器、显微镜四操作步骤1 血球计数板的构造血球计数板由四条平行槽构成3个平台,中间的平台较宽,其中间又被一短槽隔成两半,每边平台面又各有一个含9个大格的方格网,中间大格为计数室,计数室长和宽各为1mm,中间平台下陷0.1mm ,故盖上盖玻片后,计数室的容积为0.1立方毫米,常见的计数室有两种规格,一种是16×25型,称为麦氏血球计数板,共有16个中格,每个中格分成25个小格。

另一种是25×16型,称为希里格式血球计数板,共有25个中格,每个中格分为16个小格,但两种规格的其计数室的小格均有400个小方格组成。

应用时直接计算细胞数量,方法是先测定若干个方格中的细胞,再换算成每1ml细胞液(或每克样品)中细胞数量。

2 细胞数量的测定⑴用乙醇清洁计数板及专用盖玻片,然后用绸布轻轻拭干。

⑵稀释加样:先将盖玻片放在计数室上,用吸管轻吸已稀释好的少许细胞悬液滴加微量于盖玻片的边缘,让细胞液自行渗入,多余的用吸水纸吸去,片刻后计数。

⑶找计数室:先在低倍镜下寻找大方格的位置,再换高倍镜调节光亮度至细胞液和计数室线条清晰为止,再将计数室一角的小格移至视野中,调节使计数室位于视野中间。

3 计数用16×25型:取左上、右上、左下、右下4个中格(100个小格)25×16型:取左上、右上、左下、右下及中央一中格共5个中格(80个小格)将计得的细胞数填入结果表中,重复3次取平均值,按下列公式计算每ml细胞液中所含的细胞数。

实验八M序列发生及眼图观测实验

编译码模块的M序列生成部分的时钟输入端

CLK_IN;

(2)连接数字编译码模块的M序列生成部

分的数据输出端D-OUT至眼图观测模块的SD-

IN;

2 1

3:无噪声 4:有噪声

通信工程专业实验室

实验八 M序列发生及眼图观测实验

六、实验步骤及注意事项

2、依次打开各模块的电源开关和系统电源开关; 3、用示波器观测M序列输出端的波形,调节示波 器达到最佳观测效果,并记录下DOUT波形; 4、用示波器观测眼图模块的眼图输出端口的波形 ,调节示波器,使一个眼图刚好充满示波器整个屏 幕,记录下EYE-OUT波形; 5、调节噪声电位器,观察噪声对眼图的影响,并 记录下EYE-OUT波形;

通信工程专业实验室

实验八 M序列发生及眼图观测实验

二、实验预习要求

认真预习《通信原理》中关于M序列及 眼图有关章节的内容。

通信工程专业实验室

实验八 M序列发生及眼图观测实验

三、实验仪器仪表

1、70MHz双踪数字存储示波器一 台 2、实验模块:

数字编码模块——M序列输出 数字时钟信号源模块 眼图观测及白噪声输出模块

n

本原多项式的八进制表示

代数式

2

7

x2+x+1 111

3

13

x3+x|+1 1 011

4

23

x4+x+1 10 011

5

45

x5+x2+1 100 101

6

103

x6+x+1 1 000 011

7

211

x7+x3+1 10 001 001

8

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验八计数器一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理。

2.熟悉掌握常用中规模集成电路计数器及其应用方法。

二、实验原理和电路所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。

根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。

根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的。

根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器异步二进制加法计数器是比较简单的。

图 1.8.1(a)是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图1.8.1(b)和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FF O(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的CP端接FF0的Q0端,因而当FF O(Q O)由1→ 0时,FF1翻转。

类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

从波形图可看到,Q0 的周期是CP周期的二倍;Q1 是Q0的二倍,CP的四倍;Q2是Q1 的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0的八倍,CP的十六倍。

所以Q0 、Q1、Q2、Q3分别实现了二、四、八、十六分频,这就是计数器的分频作用。

2.异步二进制减法计数器异步二进制减法计数器原理同加法计数器,只要在图 1.8.1(a)所示加法计数器逻辑电路中将低位触发器Q端接高位触发器CP端换成低位触发器Q端接高位触发器CP端即可。

图1.8.2为异步二进制减法计数器。

如果有D触发器,则可把D触发器光转换成T’触发器,然后根据74LS74 D 触发器是上升沿触发,画出逻辑电路图。

用74LS74构成的4位二进制计数器逻辑电路如图1.8.3所示,3.其它进制计数器在很多实际应用中,往往需要不同的计数进制满足各种不同的要求。

如电子钟里需要六十进制、二十四进制,日常生活中的十进制,等等。

在图1.8.3中虚线所示,我们只要把Q3和Q1通过与非门接到FF0、FF1、FF2、R-,即可实现从十六进制转换为十进制计数器。

如FF3四个触发器的清零端d要实现十四进制计数器,可以把Q3、Q2、Q1 相“与非”后,接触发器FF3~FF0 R-。

同理可实现其它进制的异步计数器。

的清零端d“8421码”十进制计数器是常用的,图1.8.4为下降沿触发的JK触发器构成的异步十进制计数器(8421码)。

要组成100进制(8421码)计数器可以把两个8421计数器级联起来即可实现。

4.集成计数器在实际工程应用中,我们一般很少使用小规模的触发器去拼接而成各种计数器,而是直接选用集成计数器产品。

例如74LS161是具有异步清零功能的可预置数4位二进制同步计数器。

74LS193是具有带清除双时钟功能的可预置数4位二进制同步可逆计数器。

图1.8.5为74LS161惯用逻辑符号和外引脚排列图。

表1.8.1为74LS161的功能表。

由表1.8.1可知,74LS161具有下列功能:①CR-=0,不管其它输入端为何状态,输出均为0。

②CR-=1,LD-=0,在CP上升沿时,将d0~d3置入Q0~Q3中。

③CR-= LD-=1,若CT T=CT P=1,对CP脉冲实现同步计数。

④CR-= LD-=1,若CT P. =0,计数器保持。

进位CO在平时状态为0,仅当CT T=1且Q0~Q3全为1时,才输出1(CO= CT T.Q3. Q2. Q1 .Q0)。

体现74LS193功能的波形图如图1.8.6所示,其主要功能如下:①CR=1为清零,不管其它输入如何,输出均为0。

②CR=0, LD-=0,置数,将D、C、B、A置入Q D、Q C、Q B、Q A中。

③CR=0,LD-=1,在CP D=1,CP U有上升沿脉冲输入时,实现同步二进制加法计数。

在CP U=1,CP D 有上升沿脉冲输入时,实现同步二进制减法计数。

④在计数状态下(CR=0,LD-=1时,CP D=1时)CP U输入脉冲,进行加法计数,仅当计数到Q D~Q A全1时,且CP U为低电平时,进位CO--输出为低电平;减法计数时(CP U=1,CP D为脉冲输入,CR=0,LD-=1),仅当Q D~Q A 全0时,且CP D为低电平时,借位BO--输出为低电平。

三、实验内容及步骤1.异步二进制加法计数器a.在实验箱中选四个JK触发器,(也可自行插入二片74LS112双JK触发器)按图1.8.1(a)接线。

74LS112管脚排列如实验七图1.7.14所示。

b. 其中CP接单次脉冲(或连续脉冲),R端接实验箱上的复位开关K5。

c.接通实验系统(箱)电源,先按复位开关K5(复位开关平时处于1,LED灯亮,按下为0,LED灯灭,再松开开关,恢复至原位处于1,LED灯亮),计数器清零。

d.按动单次脉冲(即输入CP脉冲),计数器按二进制工作方式工作。

这时Q3、Q2、Q1、Q0的状态应和图1.8.1(b)一致。

如不一致,则说明电路有问题或接线有误,需重新排除错误后,再进行实验论证。

2.异步二进制减法计数器a.按图1.8.2(a)接线。

实际上,只要把异步二进制加法计数器的输出脉冲引线由Q端换成Q-端,即为异步二进制减法计数器。

b.输入单次脉冲CP,观察输出Q3、Q2、Q1、Q0的状态是否和图(b)一致。

c.将CP脉冲连线接至接续脉冲输出(注意,必须先断开与单次脉冲连线,再接到连续脉冲输出上),调节连续脉冲旋钮,观察计数器的输出。

3.用D触发器构成计数器a.按图1.8.3接线,即为4位二进制(十六进制)异步加法计数器,验证方法同上,从本实验不难发现,用D触发器构成的二进制计数器与JK触发器构成的二进制计数器的接线(即电路连接)不一样,原因是74LS74双D触发器为上升沿触发,而74LS112双JK触发器为下降沿触发。

b.构成十进制异步计数器在图1.8.3中,将Q3和Q1两输出端,接至与非门的输入端,输出端接计数R--。

图中虚线所示(原来d R--接复位按钮K5的异线应断开)。

器的四个清零端d按动单次脉冲输入,就开发现其逻辑功能为十进制(8421码)计数器。

若要构成十二进制或十四进制计数器,则只需将Q3、Q2、Q1进行不同组合即可。

如图1.1.8所示分别为十进制、十二进制、十四进制计数器反馈接线图。

4.集成计数器74LS161的功能验证和应用a.将74LS161芯片插入实验箱IC空插座中,按图1.8.9接线。

16脚接电源+5V,8脚接地,D0、D1、D2、D3接四位数据开关,Q0、Q1、Q2、Q3、CO接五只LED 发光二极管,置数控制端LD-,清零端CR-,分别接逻辑开关K1、K2,CT P、CT T分别接另二只逻辑开关K3、K4,CP接单次脉冲。

接线完毕,接通电源,进行74LS161功能验证。

①清零:拨动逻辑开关K2=O(CR=0),则输出Q0~Q3全为0,即LED全灭。

②置数:设数据开关D3 D2 D1D0=1010,再拨动逻辑开关K1=0,K2=1(即LD=0,CR=1),按动单次脉冲(应在上升沿时),输出Q3 Q2 Q1Q0=1010,即D3~D0数据并行置入计数中,若数据正确,再设置D3~D0为0111,输入单次脉冲,观察输出正确否(Q3~Q0=0111)。

如不正确,则找出原因。

③保持功能:置K4=K2=1(CR=LD=1),K3或K4=0(即CT P=0或CT P=0),则计数器保持,此时若按动单次脉冲输入CP,计数器输出Q3~Q0不变(即LED状态不变)。

④计数:置K1=K2=1(CR=LD=1),K3=K4=1(CT P=CT T=1),则74LS16处于加法计数器状态。

这时,可按动单次脉冲输入CP,LED显示十六进制计数状态,即从000→0001→…111进行顺序计数,当计到计数器全为1111时,进位输出LED发光二极管亮(即CO=1,CO=G .Q3.Q2 .Q1.Q0)。

将CP接到单次脉冲的导线切断,连至连续脉冲输出端,这时可看到二进制计数器连续翻转的情况.b.十进制计数也可用74LS161方便地实现.将Q3和Q4通过与非门反馈后接到CR端,见图1.8.10(a)所示.利用此法,74LS16可以构成小于模16的任意进制计数器.此外,还可利用另一控制端LD把74LS16设计成十进制计数器,如图1.8.10(b)所示。

同步置数法,就是利用LD这一端给一个零信号,使=D3 D2 D1D0"0110"6这个数并行置入计数器中,然后以6为基值向上计数直至15(共十个状态),即0110→0111→1000→1001→1010→1011→1100→1101→1110→1111。

所以利用15="1111"状态CO为1的特点,反相后接到LD,而完成十进制计数器这一功能.同样道理,也可以从0、1、2等数值开始,再取中间十个状态为计数状态,取最终状态的“1”信号相与非后,作为LD 的控制信号,就可完成十进制计数器。

例如若D3D2D1D0=“0000”=0则计到9;D3D2D1D0=“0001”=1则计到10,等等。

c.用两片或三片74LS161完成更多位数的计数器,实验电路见图1.8.11和图1.8.12。

其中图1.8.11为两片74LS161构成174进制计数器的两种接法。

图1.8.12为三片构成4096进制计数器的两种接法。

按图1.8.11和图1.8.12分别进行实验论证。

5.集成计数器74LS193的功能验证74LS193计数器的使用方法和74LS161很相似。

图1.8.13为其实验接线图。

按图1.8.13接线,进行74LS193的功能验证。

a.清零:74LS193的CR端与74LS161不同,它是“1”信号起作用,即CR=1时,74LS193清零.实验时,将CR置1,观察输出Q D、Qc、Q B、Q A的状态,并和逻辑功能;图1、8、6、比较。

b.计算;74LS193可以加、减计数,在计数状态时,即CR=0,LD=1,CP D=1时,CP U输入脉冲,为加法计数器;CP U=1,CP D输入脉冲,计数器为减法计数器。