基于挠性覆铜箔的平面无源集成LC单元设计

微电子制造概论PCB设计和制造

2021/9/17

31

设计基本原则

● 设计时应确定使用高频低频中频三种去耦电容,中频 与低频去耦电容可根据器件与PCB功耗决定,可分别选 47-1000uF和470-3300uF;高频电容计算为: C=P/V*V*F.

酚醛和甲醛树脂板耐湿性能和高频 性能不好,但电性能和温度较好

最常用环氧树脂浸渍的玻璃布层压 板FR4

高频下,氟碳树脂浸渍的玻璃布层 压板PTFE

2021/9/17

37

2021/9/17

38

2021/9/17

39

2021/9/17

40

PCB制作工艺 单面板制作工艺

单面板制作工艺

基板:酚醛纸基、环氧纸基、 环氧玻璃布基,单面覆铜

2021/9/17

45

钻孔-数控钻铣

一、钻床选择

1.机床台面的刚性和稳定性: 2.转轴的转速和稳定度: 3.台面的移动精度和位移重复精度: 4.X、Y、Z轴的进给速率: 5.台面的移动及固定装置: 6.最大加工尺寸: 7.操作系统和控制系统: 8.刀具管理系统: 9.光尺系统的选购: 10.吸尘系统: 11.保护系统:

2021/9/17

12

印制电路板的几个概念

导线

铜膜导线 飞线

2021/9/17

13

印制电路板的几个概念

助焊膜和阻焊膜

助焊膜Solder

Mask]

阻焊膜Paste

Mask

2021/9/17

14

印制电路板的几个概念

层

半盲孔(Blind) 盲孔(Buried) 过孔(via)

Mil:【电】密耳(千分之一英寸)

挠性覆铜板用电解铜箔

C F使用 的 2 O 层挠 性覆铜 箔板 ( C L l i e F C ,Fe b xl Ca — o p r a nt)有三种 制法 。表 I l C p e mia d L e 表示 了三 种2 F C 层 C L的特征 。溅 射法 的金属 化 ( tl i ) Meain lz g

加 热 工具 侧 ,要 越 过 蚀 刻掉 铜 箔 的聚 酰 亚 胺 膜 识 别 I C器 件 。这 时 的聚 酰亚 胺 膜 表 面成 为 铜 箔 的复 制 品 ( p i a , 如 果 与 聚 酰亚 胺 膜 相 接 的铜 箔 表 面 不 Re lc )

的 F — S箔 比较 ,U— OW WZ箔聚 酰 亚胺 粘 结面 的粗糙

F C 以聚 酰亚 胺为 基本 材料 ,涂布 法 F L和 层压 CL CC

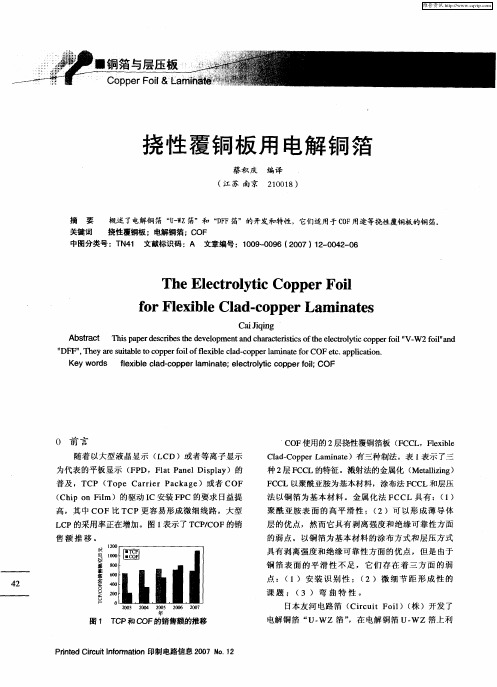

普 及 ,T P ( o e C rirP c a e C T p are a k g )或 者 CO F ( hpo i )的 驱动 I C i nFl m C安 装 F C的 要求 日益提 P

法 以铜 箔 为 基 本材 料 。金 属 化 法 F L具 有 :( ) CC 1 聚酰 亚胺表面 的高平滑 性 ;( 2)可 以形 成 薄 导 体 层 的优 点 ,然 而 它 具 有 剥 离 强度 和 绝 缘 可 靠 性方 面 的弱 点 。 以铜 箔 为 基本 材 料 的涂 布 方 式和 层 压 方 式 具有 剥离 强 度 和绝 缘可 靠 性 方 面 的优 点 ,但 是 由于 铜 箔 表 面 的 平 滑 性 不 足 , 它 们 存 在 着 三 方 面 的 弱

维普资讯

ห้องสมุดไป่ตู้

…

…

…

…

…

…

…

…

…

…

挠性覆铜板的研究进展

挠性覆铜板的研究进展徐君;田国峰;武德珍;齐胜利【摘要】综述了挠性覆铜板的研究进展,包括挠性覆铜板的发展历史、分类、组成、市场占有率及生产厂家.分别介绍了组成挠性覆铜板的基体材料——铜箔、聚合物薄膜和胶黏剂.重点介绍了聚酰亚胺(PI)薄膜挠性覆铜板的研究进展,通过对其制备工艺和所用PI薄膜的分析,指出了目前该领域存在的问题和未来的发展方向.%This paper reviewed the research progress of flexible copper clad laminates (FCCL),which covered their developmenthistory,classification,composition,market share and manufacturers.Copper foils,polymer films and adhesives as the base materials for FCCL were also introduced.Particularly,the research progress in polyimide-based FCCL was also presented.Based on the analysis of the production technology of FCCL and the polyimide films used,this paper pointed out the current existing problems and development direction in the field of FCCL.【期刊名称】《中国塑料》【年(卷),期】2017(031)009【总页数】10页(P1-10)【关键词】挠性覆铜板;聚酰亚胺;薄膜;研究进展【作者】徐君;田国峰;武德珍;齐胜利【作者单位】北京化工大学化工资源有效利用国家重点实验室,北京100029;北京化工大学化工资源有效利用国家重点实验室,北京100029;北京化工大学常州先进材料研究院,江苏常州213164;北京化工大学化工资源有效利用国家重点实验室,北京100029;北京化工大学常州先进材料研究院,江苏常州213164;北京化工大学化工资源有效利用国家重点实验室,北京100029;北京化工大学常州先进材料研究院,江苏常州213164【正文语种】中文【中图分类】TQ320.72+2近些年来,挠性印制电路板(FPC)的应用范围越来越广泛。

一种集成无源器件、其制作方法及半导体装置[发明专利]

![一种集成无源器件、其制作方法及半导体装置[发明专利]](https://img.taocdn.com/s3/m/a7cf23ec0408763231126edb6f1aff00bed570cb.png)

专利名称:一种集成无源器件、其制作方法及半导体装置专利类型:发明专利

发明人:车春城,肖月磊,李月,吴艺凡,常文博,曹雪,周毅,韩基挏,周柏君,龚林,安齐昌,冯昱霖,曲峰

申请号:CN202111265841.1

申请日:20211028

公开号:CN113990858A

公开日:

20220128

专利内容由知识产权出版社提供

摘要:本发明实施例公开了一种集成无源器件、其制作方法及半导体装置,本发明通过采用第一柔性基板+玻璃基板+第二柔性基板的三明治结构,取代相关技术中的单层玻璃基板结构,可以增加器件强度,弥补玻璃基板打孔填充导电结构后强度降低的问题;并且本发明通过设计三维电感结构、平面电容结构,可以提高电感的品质因素(即Qfactor),从而降低损耗,提高集成无源器件的可靠性。

申请人:京东方科技集团股份有限公司,北京京东方光电科技有限公司

地址:100015 北京市朝阳区酒仙桥路10号

国籍:CN

代理机构:北京同达信恒知识产权代理有限公司

代理人:刘源

更多信息请下载全文后查看。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

随着信息产业及其带来的消费类电子产品的迅速发展,为电力电子行业带来巨大的市场,在通信、计算机以及各种移动设备中,都需要大量的电力电子变流器。

大多数电力电子变换器中无源器件占据了变换器很大的体积,提高开关频率可以减小储能元件的体积。

分立型的电感电容通常体积大,元件较多,空间利用率不高,阻碍了功率密度的提高。

通过电磁作用将电感、电容、变压器集成为一个模块可以克服这些缺点。

电感器与电容器集成技术是利用电感绕组之间的寄生电容作为部分电路参数实现部分电路功能。

为了增大电感绕组之间的寄生电容,可以通过特殊结构(如平面绕组结构)或者增大介质材料的介电常数(选用具有较大介电常数的介质材料)。

电感与电容集成后为一个器件,即为LC单元。

VANWYK J D教授在磁元件与电容元件集成方面开展了大量的工作,提出电感器-电感器-电容器-变压器(L-L-C-T)集成结构,电感电容集成结构作为原边绕组,铜箔作为副边绕组。

为了增大变压器漏感作为谐振电感,在原边绕组和副边绕组之间加入一层低磁导率的磁性材料作为“漏感层”来调节漏感,整体采用平面结构,可以减小无源元件的总体积和高度,提高变流器功率密度。

这种结构采用的是EI型磁芯。

参考文献[1]中提出了基于柔性多层带材绕组的集成EMI滤波器结构,采用介电常数较低、温度和频率稳定性好的薄膜电介质材料来实现电容,克服了增大电容的困难。

但所占据空间的体积仍然比较大,不符合现代开关电源的“短、小、轻、薄”的发展趋势。

参考文献[2]中的平面PCB绕组电感电容集成结构,虽然可以减小磁芯的高度和尺寸,绕在EI型磁芯上可以实现很大的电感,但磁芯中柱也占据了很大面积。

综合参考文献[1]和参考文献[2]的思路,在现有实验条件下,本文提出了一种基于多层挠性覆铜箔交错并联的平面集成LC结构,采用CI型磁芯,实现了串联谐振、并联谐振集成,最后测试了样机的谐振点并与pspice软件的仿真结果进行了比较,得出集成的平面LC单元有效性和可行性的结论。

基于挠性覆铜箔的平面无源集成LC单元设计于宝青,杨玉岗(辽宁工程技术大学电气工程学院,辽宁葫芦岛125105)摘要:提出一种基于多层挠性覆铜箔薄膜的平面集成多个电感和电容(LC)单元的结构。

多个集成LC单元叠放到CI型磁芯里,通过不同端子的连接方式可实现串/并联谐振、低通滤波器等结构,以及不同大小的电感值和电容值。

仿真结果表明,交错并联结构可以增大集成LC单元的电容,进一步提高功率密度。

关键词:集成LC单元;CI型磁芯;谐振变换器中图分类号:TN86文献标识码:A文章编号:0258-7998(2010)08-0081-04Planar passive integration of the LC based onmulti-layer flexible copper-cladYU Bao Qing,YANG Yu Gang(Department of Eelectrical Engineering,Liaoning Technical University,Huludao125105,China)Abstract:Planar integration of multiple LC unit(inductance and capacitance)unit structure is provided based on multi-layer flexible copper-clad.When several integrated LC modules is stacked to the CI-type core,the series resonance,parallel resonance, and low-pass filter structure is available by connecting various terminals,and different inductance values and capacitance values can be obtained.Staggered parallel structure can increase the capacitance of integrated LC unit,and further more increase power density.Key words:integrated LC unit;CI cores;resonant converter图4样机的3D 结构示意图图1挠性覆铜箔聚酯薄膜铜箔粘胶剂介质材料聚酯薄膜挠性覆铜箔材料1集成结构的设计1.1多层交错并联集成单元的设计集成LC 单元材料选用挠性覆铜箔聚酯薄膜。

挠性覆铜箔薄膜[3]是一种由金属导体材料和介电基片,通过胶粘剂经热压粘结的复合材料。

这种产品可以随意卷绕,挠性覆铜箔材质比较薄,适合多层交错并联结构。

本文采用的是聚酯薄膜挠性覆铜箔材料。

如图1所示的挠性覆铜箔材质,其上层为50μm 的铜箔,中间为25μm 的粘胶剂,下层为50μm 电介质材料,该电介质材料是聚酯薄膜,介电常数为3。

图2为单层集成结构及其串/并联等效电路图,将聚酯薄膜裁剪成如图2(a)形状,两片紧压叠放。

上下两面铜箔形成电感,位于中间的介质材料与上下两面的铜箔形成电容,因此形成了电感和电容的集成结构,如图2(b)。

这样的结构可以同时得到确定的电感、电容,即通电后既有磁场储能,也有电场储能,并通过适当的连接方式与外电路相连,可以等效为串联谐振或并联谐振电路。

当把端点A 、D 与外电路连接时,B 、C 两端悬空,形成电感、电容的串联谐振形式;当端点A 、D 与外电路连接,B 、C 两端直接相连接时,即形成了电感、电容的并联谐振形式,其等效电路如图2(c)所示。

本文提出了一种基于多层挠性覆铜箔交错并联的平面集成LC 结构,实现了串/并联谐振的集成。

如同图2制作方式一样,共裁剪8片这样的形状,把它们层叠、紧压,能够实现交错并联集成的LC 单元结构,这种结构能灵活增大电容,如图3(a)所示,其等效电路如图3(b)所示。

同样也是4个端子的LC 单元结构,可以制作多个这样的集成LC 单元,按照参考文献[2]提到的多个单元连接结构还可以根据不同电感值和电容值的需要,对多个单元进行大电感大电容、大电感小电容、小电感大电容、小电感小电容的串/并联连接来实现。

进一步增加了集成电感值和电容值的灵活性。

本文先制作2个四层交错并联集成的LC 单元。

采用CI 型磁芯,节省了EI 型磁芯的磁芯中柱,增大了电容面积。

将与CI 型磁芯相应的电路板挖空,然后把每个集成LC 单元的4个引脚焊接到电路板上,2个单元之间的引线可以从电路板上走线,磁芯扣在LC 单元上,既可以节省整体无源器件所占空间体积,还可以增大磁芯的散热面积。

若想增大电感值,当给集成LC 单元通电时,所有集成LC 单元电流的方向应该是一个方向,比如每个集成LC 单元都从A 、D 端输入,从B 、C 端输出,连接方式可以在电路板上实现;而若想减小电感值,可以使若干集成LC 单元电流流向相反,即从B 、C 端输入,从A 、D 端输出。

结构示意图如图4所示。

1.2电容的计算C =ε0εr w d(1)式中,ε0为真空中的介电常数(8.854×10-12F/m),εr 为介质相对介电常数,w 为铜箔的面积(m 2),d 为介质的厚度(m)。

由式(1)可以看出,如果需要增加更大的电容C ,有3种途径:(1)增大电介质材料的相对介电常数εr ;(2)增大平面绕组的铜箔面积w ;(3)减少电介质材料的厚度d 。

图2单层集成结构及其串并联的等效电路图(a)单片挠性覆铜箔(b)单层集成结构介质材料DCB 铜箔A(c)串联谐振和并联谐振等效电路图ACB D ACB D图3四层交错并联集成结构及等效电路图(a)四层交错并联结构BCDAA BCD(b)等效电路图DA D CB BCA表2样机的计算测量及实验结果样机的计算结果样机的测量结果实验测量结果串联谐振电感L 电容C 电感L 电容C 14.3μH 0.83nF 串联谐振电感L 电容C 谐振点f 阻抗值95μH 10.2nF 160kHz 9.7Ω15μH 0.75nF并联谐振电感L 电容C 电感L 电容C 57.1μH 0.21nF 电感L 电容C 谐振点f 阻抗值61.2μH 22nF 140kHz 1.4Ω60μH 0.2nF并联谐振串联谐振并联谐振图5样机的照片表1样机的材料和参数磁芯天通公司CI14/13材质聚酯薄膜磁导率2500介电常数3A e /mm 275长/mm24长/mm24长/mm24L e /m0.033宽/mm7宽/mm7宽/mm7电容厚/μm50厚/μm25厚/μm50粘胶剂铜箔若增加更大的电容,采用交错并联方式[1]优势即可显现出来,如图2(b)所示,假如每个单元由n 片这样的结构叠加成图3(a)的结构,可以推导出电容C 的计算公式:C =(2n -1)ε0εr w(2)计算电容时,先计算一个集成LC 单元的电容量,根据参考文献[2],多个单元根据需要可通过不同的连接方式得到不同的电容值。

1.3电感的计算L =μ0A eL g +L e -L geff(3)式中,μ0为真空中的磁导率(4π×10-7N /A 2),μeff 为磁芯的有效相对磁导率,A e 为磁芯的有效截面积(mm 2),L e 为磁芯的有效磁路长度(m),L g 为磁芯的空气隙(m)。

同样在计算电感时,先计算一个集成LC 单元的电感量,根据参考文献[2],多个单元根据需要可通过不同的连接方式得到不同的电感值。

2仿真和实验本文制作了一台基于交错并联挠性覆铜箔材料的集成谐振LC 单元样机,如图5所示。

该样机选用天通公司的CI14/13磁芯;集成LC 单元的材料选用咸阳众鑫电子材料有限公司的挠性覆铜箔聚酯薄膜。

具体参数如表1所示。

集成LC 单元的制作方式如图3所示,制作的2个四层集成LC 单元,测得每个集成LC 单元的电感值为3.6μH ,电容值为0.37nF ,按照参考文献[2]中大电感大电容的串联方式连接计算得到电感为14.3μH 、电容为0.83nF 。

按照大电感大电容的并联方式连接得到电感值为57.1μH 、电容为0.21nF ,样机计算的参数如表2所示。

由于介电常数较小、集成的电容值小,但所集成的器件计算出来的谐振频率比较大,频率达到几MHz 以上。

实验用的仪器为洤华仪器有限公司的3255自动电子零件分析仪,可以测得的最高谐振频率为200kHz 。

所以在实际测量时需要额外增加辅助电感和电容使它们的谐振频率在200kHz 以下。

附加的电感和电容如图6(a)所示,串联结构的集成LC 中2个单元电感值为15μH ,电容值为0.75nF ,计算集成器件的谐振频率是1.52MHz 。