场效应器件物理14频率5cmos

传感器都有哪些种类(总结篇)

性电路消除热电势与温度的⾮线性误差,最后放⼤转换为4~20mA电流输出信号。

为防⽌热电偶测量中由于电偶断丝⽽使控温失效造成事故,传感器中还设有断电保护电路。

当热电偶断丝或接解不良时,传感器会输出最⼤值(28mA)以使仪表切断电源。

⼀体化温度传感器具有结构简单、节省引线、输出信号⼤、抗⼲扰能⼒强、线性好、显⽰仪表简单、固体模块抗震防潮、有反接保护和限流保护、⼯作可靠等优点。

⼀体化温度传感器的输出为统⼀的 4~20mA信号;可与微机系统或其它常规仪表匹配使⽤。

也可⽤户要求做成防爆型或防⽕型测量仪表。

液位1、浮球式液位传感器浮球式液位传感器由磁性浮球、测量导管、信号单元、电⼦单元、接线盒及安装件组成。

⼀般磁性浮球的⽐重⼩于0.5,可漂于液⾯之上并沿测量导管上下移动。

导管内装有测量元件,它可以在外磁作⽤下将被测液位信号转换成正⽐于液位变化的电阻信号,并将电⼦单元转换成4~20mA或其它标准信号输出。

该传感器为模块电路,具有耐酸、防潮、防震、防腐蚀等优点,电路内部含有恒流反馈电路和内保护电路,可使输出最⼤电流不超过28mA,因⽽能够可靠地保护电源并使⼆次仪表不被损坏。

2、浮简式液位传感器浮筒式液位传感器是将磁性浮球改为浮筒,它是根据阿基⽶德浮⼒原理设计的。

浮筒式液位传感器是利⽤微⼩的⾦属膜应变传感技术来测量液体的液位、界位或密度的。

它在⼯作时可以通过现场按键来进⾏常规的设定操作。

3、静压或液位传感器该传感器利⽤液体静压⼒的测量原理⼯作。

它⼀般选⽤硅压⼒测压传感器将测量到的压⼒转换成电信号,再经放⼤电路放⼤和补偿电路补偿,最后以4~20mA或0~10mA电流⽅式输出。

真空度真空度传感器,采⽤先进的硅微机械加⼯技术⽣产,以集成硅压阻⼒敏元件作为传感器的核⼼元件制成的绝对压⼒变送器,由于采⽤硅-硅直接键合或硅-派勒克斯玻璃静电键合形成的真空参考压⼒腔,及⼀系列⽆应⼒封装技术及精密温度补偿技术,因⽽具有稳定性优良、精度⾼的突出优点,适⽤于各种情况下绝对压⼒的测量与控制。

alj2302场效应管参数

alj2302场效应管参数1.引言1.1 概述概述场效应管是一种常用的电子元件,广泛应用于电子电路中。

它是一种三电极器件,由控制电极、漏极和源极组成。

通过调节控制电极的电压,可以控制漏极和源极之间的电流,从而实现电路的放大、开关等功能。

场效应管具有体积小、功耗低、频率响应高等优点,因此在各类电子设备中得到了广泛的应用。

本文将介绍场效应管的基本原理和主要参数。

首先,会详细阐述场效应管的基本工作原理,包括PN结、沟道、栅极等关键概念。

然后,会介绍场效应管的主要参数,包括漏极电流、跨导、截止频率等。

这些参数对于评估场效应管性能、设计电路和进行电路分析非常重要。

通过对场效应管参数的分析和理解,可以更好地应用场效应管进行电路设计和优化。

同时,本文也会讨论场效应管参数的重要性,并探讨如何选择合适的参数以满足具体的应用需求。

综上所述,本文旨在全面介绍场效应管的参数和原理,为读者提供了解和应用场效应管的基础知识。

对于从事电子电路设计和研发的工程师和学生来说,本文具有一定的参考价值。

在电子领域的发展中,场效应管作为一种重要的电子元件,其参数的了解和应用显得尤为重要。

1.2文章结构1.2 文章结构本文主要围绕alj2302场效应管参数展开讨论。

文章分为引言、正文和结论三个部分。

引言部分首先概述了alj2302场效应管的基本特征和应用背景,介绍了场效应管在电子器件中的重要性。

接着,文章明确了本文的结构和目的,并提出了对场效应管参数的探讨。

正文部分分为两个主要小节。

首先,2.1小节详细解释了场效应管的基本原理,包括工作原理和结构特点等方面的内容。

通过对场效应管内部结构和电流控制机制的介绍,读者可以深入理解场效应管的工作原理。

其次,2.2小节深入讨论了场效应管的主要参数,包括转导、饱和电压、截止电压、漏极电阻等。

针对每个参数,我们详细介绍其定义、计算方法和对电路性能的影响,以便读者更好地理解和应用场效应管。

结论部分首先对全文内容进行总结,再进一步探讨场效应管参数的重要性。

CMOS场效应晶体管的发展趋势

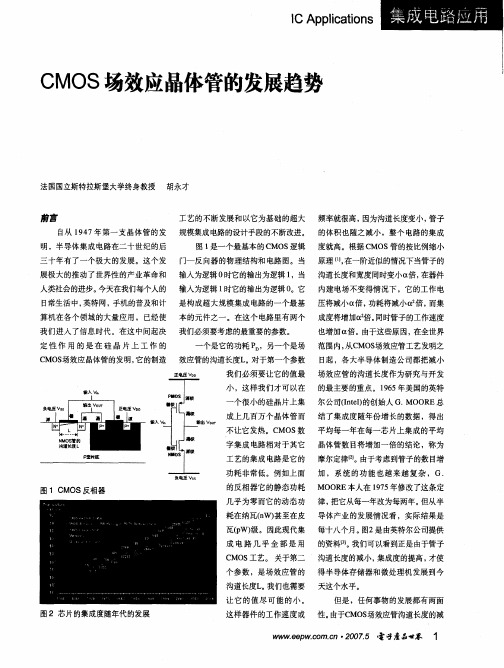

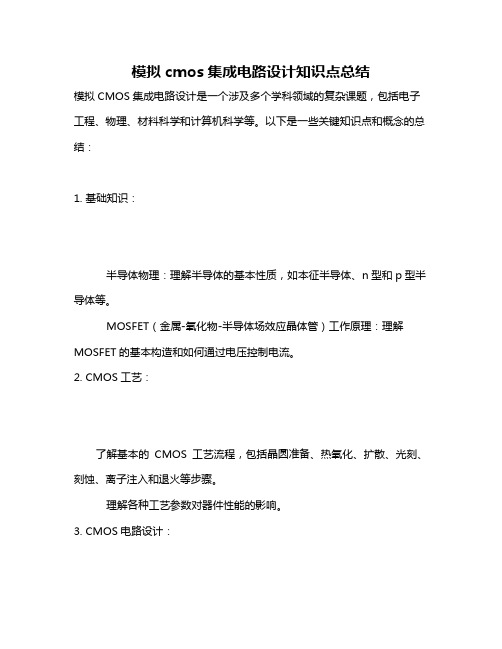

自从 1 4 9 7年第一支 晶体 管的发 规模集成 电路的设计手段的不断改进 。 的体积也 随之减小 ,整个 电路 的集成

,

图1 是一个最基本的 C S逻辑 度就高。根据 C MO MOS管的按 比例缩小

十年有了一个极大 的发展 。这个发 门一反 向器的物理结 构和 电路 图。当 原理 【, l在一阶近似的情况下当管子 的 】

8 结构 的C OS  ̄ 01 M & 效应管

图4C MOS场效应管的结构

多晶硅 多 晶硅

MO 将进入截止区域 , S 漏源 电流I 为 的沟道 掺杂 注入 结 构 , 氧 层 。 亿 一晨 曼 蔓 曼曼 豳 零就像一个开路一样 。

最小沟道 长度对于一个 C S场 S l i c n n nua r MO O ( l o s l o) Si O I t ,

赣九

小 ,这样我们才可以在 的最主要的重点。16 年美国的英特 95

一

压 v。

l 辘I 出。

正艟o 电 v 0

个很小的硅晶片上集 尔公司( t1 I e) n 的创始人 G. MOO E总 R

『 一 I 王瀛

l _ 【 ■ - _ r 一 j _

成上几百万个 晶体管而 结 了集成度随年份增 长的数据 ,得出 不让它发热。C MOS 数 平均每一年在每 一芯 片上集成的平均 字集成 电路相对于其它 晶体管数 目将增加一 倍的结论 ,称为

进入了信息时代 。在这 中间起决 我们必须要考虑的最重要的参数 。

也增加0倍。由于这些原因, 【 在全世界

洼 作 用 的 是 在 硅 晶 片 上 工 作 的

一

一

个是它的功耗 P ,另一个是场 范围内, MOS 从C 场效应管工艺发明之

简述场效应管的主要参数

简述场效应管的主要参数

场效应管(Field Effect Transistor,简称FET)是一种基于半导体物理学原理的集成电路器件,是晶体管的一种。

它是一种通过电子在半导体材料表面电场的作用下进行移动来调节电流的器件。

FET具有高输入阻抗、低噪声、低功耗、高可靠性等特点,因此在许多计算机、通信和电子设备中得到了广泛的应用。

FET的主要参数包括:

1. 栅极电压(Gate-to-Channel voltage):栅极电压是控制电流流动的关键参数,它决定了FET的导电性能。

通常,栅极电压越高,FET的导电性能越好,但也会使其功耗增加。

2. 漏极电压(Channel-to-Source voltage):漏极电压是FET的输入电压,它决定了FET的放大倍数。

FET具有输入电阻大、非线性低等特点,因此漏极电压较低时,FET的放大倍数较高。

3. 漏极电流(Channel-to-Source电流):漏极电流是FET的放大倍数和输出能力的重要参数。

当漏极电压较低时,FET的电流较小,因此输出能力较弱;当漏极电压较高时,FET的电流较大,因此输出能力增强。

4. 工作频率:FET的工作频率取决于栅极和漏极之间的电阻和栅极电压。

FET的电阻较大,因此其工作频率较高。

5. 功率:FET的功率取决于栅极和漏极之间的电流和工作频率。

FET的功率较小,因此在小型设备中应用广泛。

除了以上主要参数外,FET还有其他参数,如栅极材料、漏极材料、极化方向等。

这些参数的选择会影响到FET的性能和应用。

此外,FET还具有可编程、反向输入等特点,因此广泛应用于控制和调节电路中。

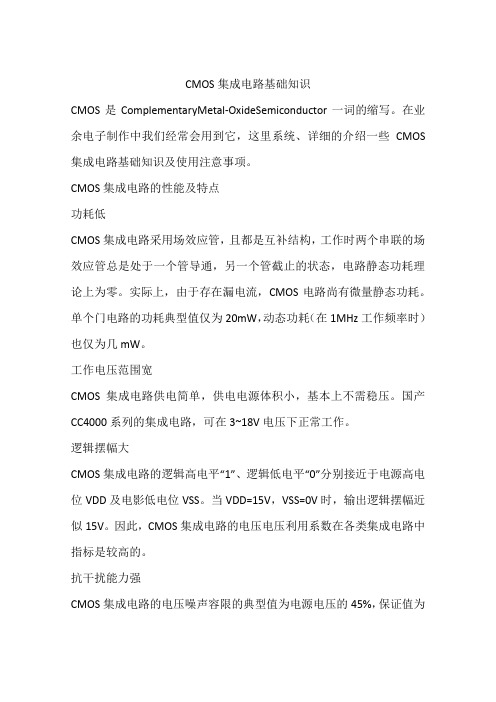

模拟cmos集成电路设计知识点总结

模拟cmos集成电路设计知识点总结模拟CMOS集成电路设计是一个涉及多个学科领域的复杂课题,包括电子工程、物理、材料科学和计算机科学等。

以下是一些关键知识点和概念的总结:1. 基础知识:半导体物理:理解半导体的基本性质,如本征半导体、n型和p型半导体等。

MOSFET(金属-氧化物-半导体场效应晶体管)工作原理:理解MOSFET的基本构造和如何通过电压控制电流。

2. CMOS工艺:了解基本的CMOS工艺流程,包括晶圆准备、热氧化、扩散、光刻、刻蚀、离子注入和退火等步骤。

理解各种工艺参数对器件性能的影响。

3. CMOS电路设计:了解基本的模拟CMOS电路,如放大器、比较器、振荡器等。

理解如何使用SPICE(Simulation Program with Integrated Circuit Emphasis)进行电路模拟。

4. 噪声:理解电子器件中的噪声来源,如热噪声、散粒噪声和闪烁噪声等。

了解如何减小这些噪声的影响。

5. 功耗:理解CMOS电路中的功耗来源,如静态功耗和动态功耗。

了解降低功耗的方法,如电源管理技术和低功耗设计技术。

6. 性能优化:理解如何优化CMOS电路的性能,如提高速度、减小失真和提高电源效率等。

7. 可靠性问题:了解CMOS电路中的可靠性问题,如闩锁效应和ESD(静电放电)等。

8. 版图设计:了解基本的版图设计规则和技巧,以及如何使用EDA(Electronic Design Automation)工具进行版图设计和验证。

9. 测试与验证:理解如何测试和验证CMOS集成电路的性能。

10. 发展趋势与挑战:随着技术的进步,模拟CMOS集成电路设计面临许多新的挑战和发展趋势,如缩小工艺尺寸、提高集成度、应对低功耗需求等。

持续关注最新的研究和技术进展是非常重要的。

以上是对模拟CMOS集成电路设计的一些关键知识点的总结,具体内容可能因实际应用需求和技术发展而有所变化。

深入学习这一领域需要广泛的知识基础和持续的研究与实践。

CMOS器件进阶版讲解(转)

CMOS器件进阶版讲解(转)本文转自芯苑, (由于芯苑会经常关闭站点,故转载存留)上一篇介绍了简单的MOS的历史和原理结构介绍,应该能够建立起比较基础的认识了,下面我们继续讲讲MOS的特性以及半导体人该关注的制程要点。

先简单回顾下MOS的重要参数开启电压,也叫阈值电压,英文叫做Threshold Voltage (Vth)。

就是在栅极加电压,通过栅极氧化层的电场耦合效应在下面的沟道表面感应出与衬底/Well反型的掺杂,使得Source/Drain能够连接起来,我们称之为反型,而这个时候的栅极电压叫做开启电压(Vth)。

所以很容易理解Vth跟GOX厚度/质量,以及衬底浓度有很大关系。

(GOX越薄自然容易感应,所以Vt越低。

而且衬底浓度越低,表面越容易反型,所以Vt也越低)。

当然Vt还跟GOX 的质量有关,也就是介电常数,所以GOX quality很重要。

随着制程越来越advance,除了尺寸要缩小,工作电压也要越来越小(shrink/scanable: 物理尺寸都等比例缩小,工作电压也要等比例缩小)。

而我们的电流密度不希望减小,所以我们要求Vt越来越低,沟道长度越来越小,这两个都是让MOS导通电流增大的原因,所以Vt 和Leff是process两个最challenge的factor。

当然缩小的一个原因是电流密度以及降低电压和功耗提高速度,另外一个原因当然是cost (我也不知道moore's law当年看重的是哪个?)当然尺寸缩小带动电压缩小,这些的好处很多比如工作频率提高了(因为节深减小了,结电容就小了,GATE与S/D的OVL减小了,所以OVL电容也小了),电压降低自然功耗降低了。

但是我们也有不好的东西,因为电压低了,所以gate delay就不得不考虑了,所以必须要降低gate电阻。

(这个可以打个比方记忆,我们的国家电网传输一定要用高压/超高压传输以减少线损,就是这个道理。

)所以,在MOS不断缩小的演进中,发展出很多一个又一个让我们这些半导体人挑战的难题,其实就是WAT参数window太小,必须enlarge window的技术革新。

模电课件 14 场效应管

学习目标 1.熟悉场效应管的结构、分类 2.了解场效应管的的工作原理、主要参数和应用

学习重点

1. 绝缘栅型场效应管的结构特点 2. 绝缘栅型场效应管的特性曲线

§1.4 场效应管

场效应管(FET)是利用输入回路的电场效应来 控制输出回路电流的一种半导体器件,由于它仅靠一 种载流子导电,又称单极型晶体管。

符号

(2)工作原理 ①当加uDS时,若 uGS=0

两个PN结背靠背,不存在导电沟道,即iD=0;

2020/1/12

模电课件

②uDS=0,uGS>0

uGS排斥SiO2附近的空穴,剩 下不能移动的离子,形成耗尽 层;

uDSuGSS源自GDN+

N+

P型衬底

随着uGS增大, 衬底的自由电子吸引到耗尽层与绝缘层之间,形成一个 N型薄层,即反型层,也是d-s之间的导电沟道;

较大

不受静电影响

几兆欧以上 漏极与源极可以互换 使用

较小

易受静电影响

2020/1/12

模电课件

参考资料:

晶体管噪声

在晶体管内,载流子的不规则运动引起不规则变化的电流起伏,因而产生不规 则变化的电压起伏,这种不规则变化的电流和电压形成晶体管的噪声。晶体管噪声 是晶体管的重要参数。

晶体管按工作原理可分为两大类,一类是双极型晶体管;另一类是单极型晶体 管,即场效应晶体管(FET)。

输出特性曲线

uDS(V)

总结:N沟道增强型

2020/1/12

导电沟道是N型,所以衬底是P型。

增强型:uGS 0,没沟道, 要 产 生 沟 道 , 必 须 加 足够 高uGS

iD 三段:表uGS 0, 沟道没,

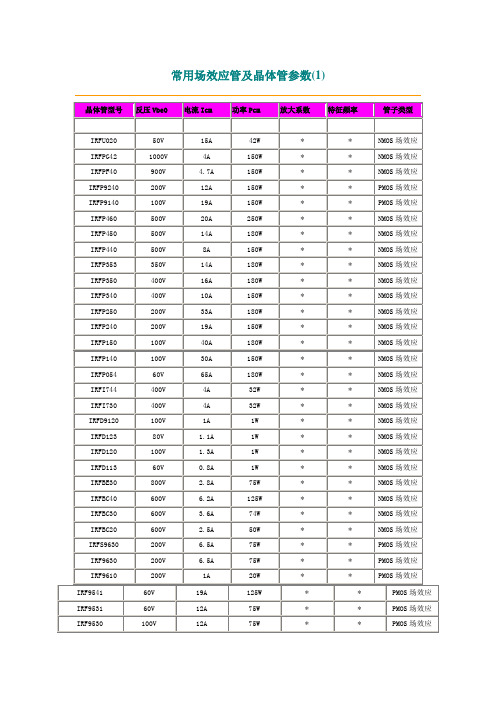

常用场效应管及晶体管参数66681

*

NMOS场效应

IRFP340

400V

10A

150W

*

*

NMOS场效应

IRFP250

200V

33A

180W

*

*

NMOS场效应

IRFP240

200V

19A

150W

*

*

NMOS场效应

IRFP150

100V

40A

180W

*

*

NMOS场效应

IRFP140

100V

30A

150W

*

*

NMOS场效应

IRFP054

IRF130

100V

14A

79W

**NMOSFra bibliotek效应BUZ20

100V

12A

75W

*

*

NMOS场效应

BUZ11A

50V

25A

75W

*

*

NMOS场效应

BS170

60V

0.3A

0.63W

*

*

NMOS场效应

常用场效应管及晶体管参数(2)

晶体管型号

反压Vbe0

电流Icm

功率Pcm

放大系数

特征频率

管子类型

2SC4582

IRF9630

200V

6.5A

75W

*

*

PMOS场效应

IRF9610

200V

1A

20W

*

*

PMOS场效应

IRF9541

60V

19A

125W

*

*

PMOS场效应

IRF9531

60V

微电子器件的多物理场场效应分析

微电子器件的多物理场场效应分析微电子器件是现代电子技术的重要组成部分,广泛应用于通信、计算机、医疗等领域。

而微电子器件的性能和可靠性往往与多种物理场效应密切相关。

本文将从多物理场效应分析的角度,探讨微电子器件的性能优化和可靠性提升的方法。

首先,我们来介绍几种常见的微电子器件中的多物理场效应。

在MOSFET(金属-氧化物-半导体场效应晶体管)中,电子在金属-氧化物-半导体界面的能带弯曲和电荷分布会受到电场效应的影响,从而影响晶体管的导通特性。

在光电二极管中,光子的能量被转换成电子能量,而电子的运动又会受到电场效应的制约。

在微电子传感器中,物理量(如温度、压力等)的变化会引起电子能带结构和电子运动的改变,从而影响传感器的灵敏度和响应特性。

针对以上多物理场效应,研究人员提出了各种模型和方法来分析和优化微电子器件的性能。

其中,有限元方法是一种常用的数值模拟方法。

通过将微电子器件划分为有限个小单元,建立物理场方程和边界条件,可以计算出电子能带结构、电子分布和电流特性等。

此外,还有基于物理方程的解析模型,例如Poisson方程、Schrodinger方程等,可以用来描述电子在微电子器件中的行为。

除了数值模拟和解析模型,实验方法也是研究微电子器件多物理场效应的重要手段。

通过设计和制备不同结构的微电子器件样品,可以通过测量电流-电压特性曲线、光电流特性曲线等来研究多物理场效应对器件性能的影响。

同时,还可以利用扫描电子显微镜、透射电子显微镜等仪器来观察器件结构和材料特性的微观变化。

在微电子器件的多物理场效应分析中,还需要考虑材料特性和工艺参数对器件性能的影响。

例如,不同材料的能带结构和载流子迁移率会影响电子能带弯曲和电子分布,从而影响器件的导通特性。

而工艺参数的变化(如氧化层厚度、掺杂浓度等)也会对器件的性能产生重要影响。

因此,在多物理场效应分析中,需要综合考虑材料特性、工艺参数和物理场效应之间的相互作用。

最后,我们来讨论如何利用多物理场效应分析来优化微电子器件的性能和提高可靠性。

第一章 CMOS电路中的器件及其模型解析

Department of Microelectronics, PKU,Xiaoyan Liu

Meyer模型

3个集总电容:

CGS

QGT VGS

,

CGD

QGT VGD

,

CGB

QGT VGB

QGT (QCT QBT ) 导通后 QGT QCT

本征电容的简单分区模型

工作区 截止区 线性区 饱和区

MOS晶体管的小信号模型

参数 • 跨导 线性区

饱和区

• 输出电导 线性区 饱和区

gm

I D VGS

VDS

gm

I D VGS

(VGS

VT )

gd

I D VDS

(VGS

VT

VDS )

gd K (VGS VT )2

• 背栅跨导 线性区 gmb I D VBS VDS VT VBS

饱和区 gmb (VGS VT ) VT VBS Department of Microelectronics, PKU,Xiaoyan Liu

Department of Microelectronics, PKU,Xiaoyan Liu

MOS 晶体管 的低频 小信号 模型

MOS晶体管的高频小信号模型

CGB CGS

CGD

WLCox 0

0

0 1/2 WLCox 1/2WLCox

0 2/3 WLCox 0

Department of Microelectronics, PKU,Xiaoyan Liu

电荷守恒模型

ix

dQ dt

Qx VG

VG t

Qx VS

VS t

Qx VD

VD t

CMOS集成电路基础知识

CMOS集成电路基础知识CMOS是ComplementaryMetal-OxideSemiconductor一词的缩写。

在业余电子制作中我们经常会用到它,这里系统、详细的介绍一些CMOS 集成电路基础知识及使用注意事项。

CMOS集成电路的性能及特点功耗低CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。

实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。

单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

工作电压范围宽CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。

国产CC4000系列的集成电路,可在3~18V电压下正常工作。

逻辑摆幅大CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。

当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。

因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

抗干扰能力强CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。

随着电源电压的增加,噪声容限电压的绝对值将成比例增加。

对于VDD=15V的供电电压(当VSS=0V时),电路将有7V 左右的噪声容限。

输入阻抗高CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

温度稳定性能好由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。

半导体器件物理II必背公式+考点摘要

半二复习笔记1.1MOS结构1.费米势:禁带中心能级(EFi)与费米能级(EF)之差的电势表示2.表面势:半导体表面电势与体内电势之差,体内EFi和表面EFi之差的电势表示3.金半功函数差4.P沟道阈值电压注意faifn是个负值1。

3 MOS原理1.MOSFET非饱和区IV公式2。

跨导定义:VDS一定时,漏电流ID随VGS变化率,反映了VGS 对ID 的控制能力3. 提高饱和区跨导途径4.衬底偏置电压VSB>0,其影响5。

背栅定义:衬底能起到栅极的作用.VSB变化,使耗尽层宽度变化,耗尽层电荷变化;若VGS不变,则反型沟道电荷变化,漏电流变化1.4 频率特性1. MOSFET频率限制因素:①沟道载流子的沟道运输时间(通常不是主要的限制因素)②栅电容充放电需要时间2。

截止频率:器件电流增益为1时的频率高频等效模型如下:栅极总电容CG看题目所给条件。

若为理想,CgdT为0,CgsT约等于Cox,即CG=Cox;非理想情况即栅源、栅漏之间有交叠,产生寄生电容:①CgdT的L为交叠部分长度②CgsT的L为L+交叠部分长度(CgsT=Cgs+Cgsp).3。

提高截止频率途径1。

5 CMOS1。

开关特性2。

闩锁效应过程2.1 非理想效应1。

MOSFET亚阈特性①亚阈值电流:弱反型态:势垒较低→电子有一定几率越过势垒→形成亚阈值电流②关系式:③注:若VDS〉4(kT/e),最后括号部分≈1,IDsub近似与VDS无关④亚阈值摆幅S:漏电流减小一个数量级所需的栅压变化量,S是量化MOS管能否随栅压快速关断的参数。

⑤快速关断:电流降低到Ioff所需VGS变化量小.因此S越小越好⑥亚阈特性的影响:开关特性变差:VGS=0时不能理想关断;静态功耗增加⑦措施:提高关断/待机状态下器件的阈值电压VT(如通过衬底和源之间加反偏压,使VT增加)、减小亚阈值摆幅2。

沟长调制效应(VDS↑⇒ID↑)①机理理想长沟:L`≈L,导电沟道区的等效电阻近似不变,饱和区电流饱和;实际器件(短沟):L` 〈L ,导电沟道区的等效电阻减小,ID增加,②夹断区长度③修正后的漏源电流④影响因素衬底掺杂浓度N 越小⇒ΔL的绝对值越大⇒沟道长度调制效应越显著;沟道长度L越小⇒ΔL的相对值越大⇒沟道长度调制效应越显著3. 迁移率变化①概念:MOSFET载流子的迁移率理想情况下:近似为常数;实际受沟道内电场的影响,迁移率非常数。

MOS 场效应晶体管

工作原理

mosfet通过在金属-氧化物-半导 体结构上施加电压,控制电子流动, 实现信号放大和开关作用。

结构

mosfet由栅极、源极、漏极和半导 体层组成,具有对称的结构。

mos 场效应晶体管的应用

集成电路

mosfet是集成电路中的基本元件, 广泛应用于数字电路和模拟电路 中。

工作原理概述

电压控制

导电通道的形成与消失

mos场效应晶体管是一种电压控制器 件,通过在栅极施加电压来控制源极 和漏极之间的电流流动。

随着栅极电压的变化,导电通道的形 成与消失,从而控制源极和漏极之间 的电流流动。

反型层

当在栅极施加正电压时,会在半导体 表面产生一个反型层,使得源极和漏 极之间形成导电通道。

电压与电流特性

转移特性曲线

描述栅极电压与漏极电流之间关 系的曲线。随着栅极电压的增加, 漏极电流先增加后减小,呈现出

非线性特性。

跨导特性

描述源极电压与漏极电流之间关 系的曲线。跨导反映了mos场效

应晶体管的放大能力。

输出特性曲线

描述漏极电压与漏极电流之间关 系的曲线。在一定的栅极电压下, 漏极电流随着漏极电压的增加而

增加,呈现出线性特性。

Part

03

mos 场效应晶体管的类型与 特性

nmos 场效应晶体管

总结词

NMOS场效应晶体管是一种单极型晶体管,其导电沟道由负电荷主导。

详细描述

NMOS场效应晶体管通常由硅制成,其导电沟道由负电荷主导,因此被称为 NMOS。在NMOS中,电子是主要的载流子,其源极和漏极通常为n型,而衬 底为p型。

制造工艺中的挑战与解决方案

1 2 3

场效应管最大工作频率

场效应管最大工作频率(原创版)目录1.场效应管的概念及特点2.场效应管的工作频率范围3.场效应管的最大工作频率取决于哪些因素4.如何计算场效应管的最大工作频率5.举例说明场效应管在不同工作频率下的应用正文一、场效应管的概念及特点场效应管(Field Effect Transistor,简称 FET)是一种半导体器件,是基于半导体材料的电子运动方式而设计的。

场效应管是三种主要的晶体管之一,另外两种是双极晶体管(Bipolar Junction Transistor,简称 BJT)和绝缘栅双极晶体管(Insulated Gate Bipolar Transistor,简称 IGBT)。

相较于其他两种晶体管,场效应管具有低噪声、高阻抗、低功耗和热稳定性等优点,在电路设计中有着广泛的应用。

二、场效应管的工作频率范围场效应管的工作频率范围取决于其类型和结构。

一般来说,场效应管的工作频率可以从几赫兹到几百兆赫兹甚至更高。

其中,N 沟道增强型场效应管(Enhancement Mode FET,简称 EMFET)和 N 沟道耗尽型场效应管(Depletion Mode FET,简称 DMFET)具有较高的工作频率,可以在高频电路中应用。

三、场效应管的最大工作频率取决于哪些因素场效应管的最大工作频率主要取决于以下几个因素:1.半导体材料的性质:不同的半导体材料具有不同的载流子迁移率,影响场效应管的工作频率。

2.结构参数:场效应管的结构参数,如栅极长度、栅极宽度、源极和漏极的距离等,也会影响其工作频率。

3.制造工艺:制造工艺决定了场效应管的物理结构和质量,对工作频率有重要影响。

4.工作电压和电流:场效应管的工作电压和电流也会影响其最大工作频率。

通常情况下,工作电压越高、工作电流越大,场效应管的最大工作频率就越低。

四、如何计算场效应管的最大工作频率要计算场效应管的最大工作频率,需要查阅其数据手册或技术规格书,获取相关参数,如最大工作电压、最大工作电流、开关速度等。

电子器件及半导体中的物理学问题

电子器件及半导体中的物理学问题电子器件和半导体是现代电子技术的重要组成部分。

它们在各种电子设备中起到着关键作用,如计算机、手机、电视、汽车和医疗设备等。

然而,在电子器件和半导体中存在许多物理学问题,这些问题影响着它们的性能和可靠性。

本文将介绍一些关键的物理学问题,并讨论目前的研究方向和解决办法。

1. PN结和二极管中的PN结PN结是一种常见的电子器件,它由p型半导体和n型半导体组成。

当p型半导体和n型半导体接触时,它们之间形成PN结。

PN结具有整流功能,即只能让电流在一个方向流动。

二极管是一种常见的PN结器件,它具有两个电极,即阳极和阴极。

当PN结的阳极为正电压时,电流可以流过它,而当阳极为负电压时,电流将被阻止。

PN结和二极管中的重要物理学问题之一是载流子注入。

当PN结中的载流子从一侧注入时,它们将遇到电荷粒子,在达到平衡后,它们将停止运动并形成电场。

这个电场将限制进一步载流子注入。

因此,了解载流子注入及其对性能的影响是很重要的。

当前的研究方向包括开发新的器件结构,以改善载流子注入,以及改进现有的技术,以克服这个问题。

2. CMOS器件中的热效应CMOS器件是一种常见的半导体器件,它由MOSFET和晶体管组成。

MOSFET是一种场效应晶体管,它可以调整通道电阻以改变电流。

在CMOS器件中,晶体管和MOSFET可以轮流控制电流。

该器件发展迅速,广泛应用于数字电路和微处理器中。

CMOS器件具有高效率、性能稳定等特点,使其在电子行业中得到广泛应用。

但该器件中存在一些物理学问题,如热效应问题。

在CMOS器件中,电流通过晶体管时会产生一定的热量,这将导致器件温度升高。

当器件温度升高时,其性能和可靠性将受到影响。

例如,当晶体管的温度达到临界点时,其场效应电流将降低。

这可能会导致器件停止工作或性能下降。

为了克服这个问题,研究人员发展出一些新的材料和结构,以提高CMOS器件的散热能力,减少热效应的影响。

3. MOSFET中的渗透效应MOSFET器件中存在一种称为渗透效应的物理学问题。

CMOS电路特性与参数

CMOS电路特性与参数CMOS(Complementary Metal-Oxide-Semiconductor,互补式金属氧化物半导体)是一种常见的集成电路技术。

它由一对互补的MOSFET (金属氧化物半导体场效应晶体管)构成,具有高集成度、低功耗和高噪声抑制等优点。

在本文中,我们将探讨CMOS电路的特性和参数。

一、CMOS电路的基本特性CMOS电路采用了互补的nMOS和pMOS晶体管,使得在非导通状态下电流基本为零,从而实现了极低的静态功耗。

此外,由于nMOS和pMOS晶体管的互补作用,CMOS电路还具有较高的抗噪声性能和较宽的工作电压范围。

这些特性使得CMOS电路成为了现代集成电路设计的重要选择。

二、CMOS电路的关键参数1. 高电平(High Level,或简称"High")和低电平(Low Level,或简称"Low")电压:这两个参数定义了CMOS电路中表示逻辑状态的电压范围。

通常情况下,高电平电压应接近于供电电压(VDD),低电平电压应接近于地(GND)。

2. 阈值电压:阈值电压(Threshold Voltage)是指晶体管切换电流的参考电压。

对于nMOS晶体管,阈值电压为正值;对于pMOS晶体管,阈值电压为负值。

阈值电压决定了晶体管的导通和截止的条件。

3. 驱动能力:驱动能力(Drive Capability)是指CMOS电路对外部负载的驱动能力。

它通常由晶体管的截止电压和饱和电压确定。

高驱动能力可以保证信号在电路中的传输质量和速度。

4. 功耗:CMOS电路的功耗主要包括静态功耗和动态功耗。

静态功耗是指电路在静止状态下的功耗,主要由漏电流引起;动态功耗是指电路在切换状态时的功耗,主要由充电和放电电流引起。

降低功耗是CMOS电路设计的一个重要目标。

5. 速度:CMOS电路的速度取决于晶体管的开关速度和电路中的延迟。

晶体管的开关速度主要由其驱动能力和晶体管的尺寸确定;电路中的延迟主要由线路长度、传输门的个数等因素决定。

现代CMOS工艺基本流程

现代CMOS工艺基本流程现代CMOS(互补金属氧化物半导体)工艺是集成电路制造中最主要的工艺之一,它是一种使用P型和N型MOSFET(金属氧化物半导体场效应晶体管)的技术,具有低功耗、低噪声和高集成度的特点。

以下是现代CMOS工艺的基本流程。

1.晶圆制备:晶圆制备是CMOS工艺的第一步。

它通常使用硅片作为基材。

首先,要选择高纯度的硅作为原料,然后通过化学方法将其制成单晶硅圆片。

随后,通过前端处理将硅片打磨成合适的尺寸和平滑度。

2.清洗和清理:接下来,需要对硅片进行清洗和清理,以去除表面的污染物和不纯物。

清洗过程包括物理和化学方法,如超声波清洗和溶剂浸泡。

这一步是很关键的,因为任何残留物都会影响后续的工艺步骤和器件性能。

3.氧化物层的生长:在CMOS工艺中,需要在硅片表面生长一层薄膜氧化物作为绝缘层。

这通常通过将硅片放入氧化炉中,使其暴露在氧气或水蒸气中进行氧化。

这层氧化物可以用于隔离电路元件和保护硅表面。

4.掩膜光刻:在这一步中,需要将光刻胶涂在硅片表面,然后使用掩膜进行光刻。

掩膜是一种具有特殊图案的透明薄膜,其使用光刻胶将这些图案转移到硅片上。

光刻胶的特性使其在紫外线照射后形成化学变化,从而在后续的腐蚀和沉积步骤中保护或提供特定区域。

5.腐蚀:腐蚀是用于去除掩膜未覆盖区域或不需要的材料的工序。

通常,使用化学物质进行湿腐蚀,以去除掩膜暴露的区域。

这使得我们可以在硅片表面形成不同的结构,例如通道区域和配线。

6.沉积:在CMOS工艺中,需要进行各种材料的沉积。

这些材料可以是金属、多晶硅、背景等,以满足不同的容器和连接要求。

沉积过程可以使用物理气相沉积(PVD)或化学气相沉积(CVD)等技术。

7.刻蚀:在一些情况下,需要从硅片或其他材料上去除特定的层。

为了实现这一点,可以使用刻蚀工艺,例如干法刻蚀或湿法刻蚀。

刻蚀可以根据硅片表面的情况和设计要求选择合适的方法。

8.金属化:金属化是CMOS工艺的一个重要步骤,用于形成晶圆上的金属线路和导线。

模拟电路中CMOS器件的频率限制因素与提高方法分析

模拟电路中CMOS器件的频率限制因素与提高方法1提高CMOS模拟集成电路频率特性的重要性在过去的十几年中,移动电话,无线网络,广播,数字电视,卫星导航,得到了迅猛发展,对重量轻,体积小,功耗低,成本低的收发器的需求也迅速增加.提高收发器的集成度无疑上满足上述需求的重要途径,在以往的收发器中,数字处理部分通常采用低成本的标准CMOS工艺,射频前端一般采用GAS,BIPOLAR或BICMOS工艺.由于数字处理部分通常占芯片面积的70%以上【1】,集成度及功耗的要求使得不可能以CMOS以外的其它工艺实现,所以只有实现COMS射频前端才能实现单片集成的收发器并最终实现CMOS射频前端,才能实现单片集成的收发器并最终实现单片集成的移动通信产品.模拟IC包含了纯模拟信号处理功能的电路和AD混合信号处理功能的电路.主要被用来对模拟信号完成采集、放大、比较、变换等功能,模拟集成电路在处理模拟信号时,除功率输出级外多数工作在小信号状态,信号频率往往从直流延伸到高频.加上模拟IC品种繁多,功能复杂,性能差异巨大,因此,模拟IC在制作工艺、器件结构、电路架构等方面都有区别于数字电路的鲜明个性,主要表现在:模拟IC在整个线性工作区内需具备良好的电流放大特性、小电流特性、频率特性等【2】.而最典型的模拟IC就是射频前端.虽然CMOS以其较低的制造成本和在同一芯片上同时包含模拟和数字电路以完善整体性能和降低封装成本而更具有吸引力,但是由于CMOS与其它工艺相比存在跨导小,频率特性差,噪声大及无源器件集成困难等不足而使它的应用受到限制【2】.因此必须想办法改善CMOS的频率特性,增益,噪声等性能,才能实现CMOS在模拟集成电路中的应用实现并最终实现单片集成的移动通信产品.而这其中我们最关心的就是提高它的频率特性.2 COMS的频率特性分析CMOS,全称Complementary Metal Oxide Semiconductor,指互补金属氧化物(PMOS 管和NMOS管)共同构成的互补型MOS集成电路制造工艺.其结构如图(其a图为P阱,b图为N阱,c图为双阱).图1采用CMOS技术可以将成对的金属氧化物半导体场效应晶体管(MOSFET)集成在一块硅片上.它的特点是低功耗.由于CMOS中一对MOS组成的门电路在瞬间要么PMOS导通、要么NMOS导通、要么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低【2】.由于CMOS由PMOS管和NMOS管共同构成,我们可心用MOSFET的小信号等效电路从数学上对电子电路进行分析,从而了解影响频率特性的因素. MOSFET的小信号等效电路包括产生频率效应的电容和电阻.我们首先说明小信号参数和等效电路,然后讨论限制CMOS频率特性的物理因素.2.1 小信号等效电路基本的MOSFET结构示意图如图2.图2为基于晶体管内部的固有电容,电阻及其它物理量的模型示意图.【3】图22.1.1小信号参数当信号加在直流偏压上时,MOS 场效应晶体管栅电荷耗尽层电荷将随信号电压发生变化,从而引起漏电压将发生变化.这里指的小信号特性是指在一定工作点上,输出端电流的微小变化与输入端电压的微小变化之间的定量关系.由于这是一种线性关系,所以可以用线性方程组描述小信号特性.我们首先讨论低频小信号参数,因为它是建立从低频到高频小信号模型的基本依据之一.以长沟道N型MOS场效应晶体管国例讨论低频小信号参数而且只考虑器件的”本征”部分,这是因为MOS晶体管的作用主要发生在这里. 2.1.1.1跨导跨导gm被定义为漏电压一定时,漏电流的微分增量与栅源电压微分增量之比,即C U U I g DS GS DSm ==αα 【4】 (1) 其中I DS 是漏源电流,U GS 是栅源电压.U DS 是漏源电压.由此可见gm反映栅源电压的变化量控制漏源电流变化量的能力,标志着MOS场效应晶体电压的放大本领,gm与电压增益K V 的关系为Rg U R I K LmGSL DS V =∆∆= 【4】(2) 其中R L 为MOS 管的负载电阻. ⅰ非饱和区跨导gml在非饱和工作区,当U DS <U Dsat (饱和漏源电压)时,由线性区电流公式⎥⎦⎤⎢⎣⎡--=U U U U I DS DS T GS DS 221)(β其中U T 为开启电压.对U GS 求导,则得器件工作在非饱和区的跨导gml=βUDS【4】 (3)从此式看上去gml似乎与U GS 无关.但实际测量表明,当U GS 增大时gml下降,这是因为当UGS增大时,电子迁移率μn下降的缘故.ⅱ饱和区跨导gms在饱和工作区,当U DS >U Dsat 时,对饱和电流公式)(221U U I T GS DS -=β对U GS求导,则得器件工作在饱和区的跨导gms=β)(U U T GS - 【4】 (4)这说明,器件工作在饱和区,其跨导与漏源电压U DS 基本无关,且随栅源电压增大而上升. ⅲ衬底跨导gmb当在MOS管的衬底上施加反向偏置电压U BS 时,表面势随着衬底偏置电压的增大而上升,表面最大耗尽层宽度也随之而展宽,表面空间电荷面密度也增大.只要将饱和电流表达式中空间电荷有关项中的U S 用()U U SBS -代之,即可得到包括衬底偏压USB后的漏电流表达式,即()()()}32_21{23232⎥⎥⎦⎤⎢⎢⎣⎡-⎥⎦⎤⎢⎣⎡---=+++U U U U U U U U U I SB S SB S DS DS S FB GS DS β]4[其中U FB 为平带电压, U S 为半导体平面上的电压降,U BS 为衬源电压, U SB 为衬底偏压,只要将上式对U SB 求导,即可得到()()⎥⎥⎦⎤⎢⎢⎣⎡--=+++U U U U U N gSB s SBS DS q LWA s nmb212102εεμ 【4】 (5)若用U sat 取代上式中的U DS ,即可得到饱和区衬底跨导表达式.显然,影响gmb的条件只包括U DS 和U SB ,而与U GS 无关. 2.1.1.2漏源输出电导gdlⅰ线性工作区的漏源输出电导gdl线性工作区的漏源输出电导gdl定义为栅源电压U GS 等于常数时微分漏电流与微分漏源电压之比,即,CUU I gGSDSDSdl=∂=α 【4】表示漏源电压对漏电流的控制能力,对线性区I DS 方程对漏源电压U DS 求导,即得非饱和工作区的漏电导()U U U g DS T GS dl--=β 【4】当U DS 很小时,是式中的U DS 可以忽略,可得器件在线性工作区的电导()U U gT GS dl-=β 【4】 (6)由上式可见输出电阻1/gdl与()U U T GS-是双曲关系,现当漏源电流较大时gdl与U GS线性关系不再维持,这是因为电子的迁移率随U GS 增大面减小的原故. ⅱ饱和区的漏-源输出电导gds理想情况下饱和区的漏电流I Dsat 与漏电压U DS 无关,gds应为零而对于实际MOS场效应晶体管,饱和区输出的特性曲线总有一定的倾斜使输出电阻不为零,其原因有二:其一,沟道长度调制效应;其二,漏极对沟道的静电反馈作用. 2.1.2 CMOS场效应晶体管交流小信号等效电路在交流工作状态下,栅源电压等于直流偏压U GS 和交流信号电压u gs 的迭加,电流也必然等于直流分量I DS 与交流分量i ds 之和.由于输入漏源电流是栅源电压U GS 和漏源电压UDS的函数,即U g Ug U U I U U I I DsdlGSmDs CDS DSGS C DS DSDS d d d U d U d GS DS +=∂∂+∂∂=== 【4】的小信号工作状态下,式中的微分增量可近似用交流信号电流和电压代替,因此交流漏电流ugug i dsdlgsmDS+=【5】 (7)MOS场效应晶体管中的电荷存储效应对MOS场效应管,MOS电路的交流及瞬态特性有决定性影响.由于栅源和栅漏之间的电容C gs 和C gd 的存在,当栅压随输入交流信号必变时,通过沟道电阻形成对等效栅电容的充电电流由此而产生输入回路中的交流栅电流dtd dtd U C U C i gd gdgs gsg += 【5】 (8)其中C gs 为栅源电容,C gd 为栅漏电容.同时,栅漏电容的充放电效应也将在漏端产生增量电流.这样以来交流漏极电流的表达式应为dtd u cu gug i gdgddsdlgsmds-+=]5[ (9)根据MOS场效应晶体管的漏端电流和i ds 和i g 的表达式,可得到器件的本征等效等效电路如下图3G图32.1.3MOS 场效应管的频率限制因素由上述交流等效电路可看出,MOS器件存在着本征电容,而且实际的MOS器件中还存在着寄生电容,由于这些电容在交流信号下充放电存在一定的延迟时间,载流子渡越沟道也需要一定的时间,这些时间延迟都会限制MOS器件的使用频率,对于模拟电路器件最关心的性能是截止频率fT和最高工作频率fM.下面分别讨论其限制因素及改进方法.2.1.3.1截止频率fT等效电路的输出端,由于C gs 的阻抗随频率增加而下降,使流过栅源电容的电流随频率增高面上升.通常把流过C gs 的电流上升到刚好等于电压控制电流源ug gsm时的频率定义为MOS场效应晶体管的截止频率.用符号ωT表示.即ug uC gsmgsgsT=ωCgsm T=ω将gm和C gs 的表示式代信上式得()L U UfT GS nT243-=μπ]5[ (10)其中μn为电子迁移率,L 为沟道长度.可见fT与MOS器件的沟道长度L平方成反比,短沟道的MOS器件fT会更高而对于长沟道的MOS器件来说沟道长度渡越时间τ是限制截止频率的主要因素,若用渡越时间τ来表示截止频率可推得τω2=T,τω5=gm ,()μτnT GS U U L -=234从上式可以看出.为提高MOS管的截止频率fT,从结构方面应当使沟道长度缩到最抵限度尽可能地增大电子在沟道表面的有效迁移率μn.2.1.3.2最高工作频率MOS管的最高工作频率fM为功率增益等于一时的频率.由于栅极沟道电容的C GC存在,使MOS场效应器件不能在任意的高频下运用,当信号频率ω增加,则流过栅沟电容的信号电流增加,即从源极流入沟道用于增加栅-沟电容充电的那部分截流子增加,直到ω足够大,以使全部沟道电流用于充电则使漏极输出信号为0.此时对应的频率ω是MOS场效应晶体管的最高信号频率ωm ,所以ug u C gsmGSGCM=ω]5[式中C GC 表示栅-沟的总电容;u gs 是信号源加到栅源之间的电压,故MOS场效应晶体管的最高工作频率Cf GCmMπ2=(11)可见,MOS管跨导愈大,最高工作频率愈高;栅-沟电容C GC 愈小,最高工作频率也愈高.因此在设计MOS场效应晶体管时,往往将CgGCm作为MOS管的高频优质去衡量它的高频特性,其比值越高,高频特性越好.由于()U u C gTgsoxnmLW-=μ, (12)则栅-沟电容C GC 为tC C OXoOXOXGC WLWL εε== (13)其中C OX 为栅氧化层单位面积电容,t OX 为二氧化硅厚度,εOX为二氧化硅介电常数,εo为真空介电常数.所以()U u LfTgs nM-=22πμ]5[ (14)从上式可以看出.为提高MOS管的最高工作频率fM,从结构方面应当使沟道长度缩到最抵限度尽可能地增大电子在沟道表面的有效迁移率μn.综上所述,限制MOS场效应管的因素主要有沟道长度和沟道电子迁移率,而根本原因则是,极间电容的存在.3 C MOS场效应管频率的提高方法针对MOS场效应管频率特性的主要限制因素,我们必须减小沟道长度,增大沟道表面的电子迁移率,减小栅电容.下面就具体讨论改进方法. 3.1缩短沟道长度减小MOS晶体管的沟道长度可以增大跨导,因而是提高频率的有效途径,这也正是MOS器件尺寸不断缩小的一个目的.缩短沟道长度主要还是根据按比例缩小理论通过改善微电子工艺技术,提高加工水平来实现.沟道长度的缩短受到光刻工艺的限制,用自对准栅工艺可以在一定程度上得到避免与克服,能其本上消除C gd,C gs对频率的影响.但CMOS器件缩小到亚011μm以后将面临着许多挑战,除了工艺技术问题还有很多器件物理问题需要解决,主要是:电源电压和阈值电压缩小问题,短沟道效应,栅氧化层可靠性,量子效应,杂质数起伏的影响,以及互连线延迟等问题.简单的等比例缩小不能解决纳米 CMOS面临的种种挑战,研究适于纳米 CMOS的新型器件结构已成为迫切的课题]6[.纳米 CMOS器件在结构和工艺设计上采取了很多措施来改善器件性能.采用浅沟槽隔离不仅有效抑制闩锁效应,而且有利于缩小面积提高集成度.为了使 NMOS和PMOS性能更对称,分别采用 n +和 p +硅栅,使 NMOS和PMOS都是表面沟器件]7[.用硅化物自对准结构(salicide)减小多晶硅线和源/漏区的寄生电阻.利用沟道工程实现优化的沟道掺杂剖面,用后退掺杂减小表面电场,消弱反型层量子化效应,还可以减小杂质随机分布对阈值电压的影响.中等掺杂的极浅的源/漏延伸区和环绕掺杂可以有效地抑制短沟效应.优化的沟道掺杂也可以防止热电子效应,保证器件的可靠性.在改进常规的体硅CMOS器件结构设计的同时,近年来发展了若干富有新意的器件结构.主要是:SOI CMOS,双栅 MOSFET,环栅 MOSFET,凹陷沟道 MOS2FET,DTMOSFET和低温 CMOS,他们在性能、功耗诸方面让CMOS的发展日新月异.SOIMOSFET可以解决一些缩小器件尺寸带来的器件和工艺问题,如浅结、软失效和体硅CMOS的闩锁效应,等等.SOI优越性的一个最主要方面是寄生电容小,因而有利于提高电路速度.为了克服FD SOIMOSFET背栅控制作用很弱的问题,发展了双栅 SOIMOSFET,其沟道是一层非常薄的硅,该层硅膜有两个栅,分别在沟道的两面,在这样的结构中短沟道效应被极大的抑制了]8[.为了进一步提高栅极对沟道的控制能力,可以使沟道四周完全用栅极包围,这就是环栅MOS2FET.环栅MOSFET可以是水平沟道,也可以是垂直沟道,环栅器件应该比双栅器件更有利于抑制短沟效应和改善亚阈值斜率,而且柱形垂直沟道的环栅器件可以获得更高的集成密度.抑制短沟效应还有一个途径就是减小源/漏结深.凹陷沟道MOSFET利用局部场氧的方法在沟道区形成凹陷的氧化层,然后再刻蚀掉该氧化层,形成凹陷的沟道区,从而减小了源/漏区相对沟道的结深,同时较深的源/漏区可以减小源/潜心区串联电阻.采用动态阈值可以解决高速度和低功耗的矛盾要求.不仅有利于提高速度,降低静态功耗,而且可以抑制短沟效应,因为工作时的正衬底偏压使源/漏耗尽层减小.早已证明低温下可以改善MOSFET性能,但是由于低温操作需要冷却设备,代价高,因此只要在室温下性能可以不断提高,低温操作就不会被重视.既然我们现在已经接近了室温 CMOS 性能极限,必须重新审视纳米领域的低温CMOS 技术.由于低温下高载流子迁移率与低互连电阻,低温 CMOS 在性能上优于 室温CMOS115- 210倍]9[。

超导场效应管电子元器件详解

超导场效应管电子元器件详解超导场效应管(Superconducting Field-Effect Transistor,SFEIT)是一种利用超导材料和量子力学原理制成的电子器件。

在超导状态下,电子通过量子隧穿效应穿过势垒,形成电流。

当加电压时,通过调节栅极电压,可以控制电子的隧穿行为,从而实现场效应管的开关功能。

一、超导场效应管的结构超导场效应管主要由源极、栅极和漏极三个部分组成。

源极和漏极之间是半导体材料,栅极位于源极和漏极之间。

在源极和漏极之间加上正向电压时,即栅极电压为零或正电压时,电子从源极流向漏极,形成漏极电流。

当加反向电压时,即在源极和漏极之间加负电压,栅极和源极之间加正电压,电子从源极流向栅极,形成栅极电流。

二、超导场效应管的工作原理超导场效应管的工作原理是通过调节栅极电压来控制半导体中的电子的隧穿行为,从而实现开关功能。

当加正电压时,即栅极电压大于源极和漏极之间的电压时,电子从源极流向栅极,形成较薄的N型反转层,使得源极和漏极之间的电阻减小,电流增加。

当加负电压时,即栅极电压小于源极和漏极之间的电压时,电子从栅极流向源极,形成较厚的N型反转层,使得源极和漏极之间的电阻增加,电流减小。

三、超导场效应管的优点超导场效应管具有高速、低功耗、高灵敏度等优点。

由于电子在半导体中通过量子隧穿效应穿过势垒,其速度非常快,可达10的负15次方秒量级。

同时,由于超导材料的电阻率为零,电流在超导材料中不会产生热损耗,因此超导场效应管的功耗非常低。

此外,超导场效应管的灵敏度非常高,可以通过微小的栅极电压控制大的漏极电流。

四、超导场效应管的应用超导场效应管因其高速、低功耗、高灵敏度等优点,在电子科技领域具有广泛的应用前景。

例如,在高速计算机、量子计算、微波振荡器、精密测量等领域,SFEIT都具有重要的应用价值。

在量子计算领域,超导场效应管可以用来制备量子比特,实现量子信息的存储和运算。

在微波振荡器领域,超导场效应管可以用来产生高频率、高稳定性的微波信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西安电子科技大学 XIDIDIAN UNIVERSITY 张丽

第11章 MOSFET基础 11.4 频率限制特性 11.5 CMOS技术 11.6小结

2020/1/3

1

1.4 频率特性

本节内容

模型的基本概念 MOSFET的小信号等效电路 频率限制因素 截止频率的定义、推导和影响因素

• LEVEL3 – 经验模型,公式简单。模拟效率高,精度同LEVEL2。小尺寸管精 度不高。

• BSIM1(Berkly Short-channel IGET ModelLEVEL13,28) – 经验模型,记入电参数对几何尺寸的依赖性。长沟道管(1um以 上的器件)精度高。

2020/1/3

g'm Vgs

Id

g

m

'

1

gm gm

rs

gm

11

1.4 频率特性

高频等效电路

忽略寄生参数rs, rd, rds ,和 Cds,高频小信号等效电路

2020/1/3

12

1.4 频率特性

MOSFET频率限制因素

限制因素1:沟道载流子的沟道输运时间 对Si MOSFET 饱和漂移速度vsl=107 cm/s 设沟道长度L 1μm

2020/1/3

8

1.4 频率特性

模型和模型参数特点:

随着沟长的缩短,短沟窄沟效应凸现,IV公式和阈值电压公 式都需修正,模型的发展级别特别多,模型也越来越复杂。

• LEVEL1 – 最简单,适合长沟道器件,均匀掺杂的预分析

• LEVEL2 – 含详细的器件物理二级模型,但公式复杂,模拟效率低,小尺寸 管符合不好。

2020/1/3

5

1.4 频率特性 完整的小信号等效电路:VBS影响

共源n沟MOSFET小信号等效电路 (VBS<0)

2020/1/3

6

1.4 频率特性

模型参数

模型参数:描述等效电路中各元件值所用的参数。 与IDS相关的模型参数:W,L,KP(ucox),LAMBDA

ID

WnCox

2L

通常RLCgdT 1

密勒效应:将跨越输入-输出端的

电容等效到输入端,C值会扩大(1

+K)倍,K为常数

14

1.4 频率特性

含有密勒电容等效电路

Ii

j

C

gsT

Cgd

T

9

1.4 频率特性

模型和模型参数特点:

• BSIM2(LEVEL39)

– 与BSIM1形式基本相同

– 改进电流公式,L=0.25um以上的器件精度高。

– 在几何尺寸范围大时,必须分成几个几何尺寸范围,对应几套模

型参数,每套参数适用于一个窄范围。

• BSIM3 (LEVEL47、49)

– 基于物理模型,而不是经验公式。

Id

Vd / RL gmVgs

jCgdT

(Vd

Vgs )

Ii

j

C

gsT

Cgd

T

1

1

gm RL

jRLCgd

T

Vgs

j[CgsT

CgdT (1 gm RL )]Vgs

j[CgsT CM ]Vgs

密勒电20容20/1C/3M CgdT (1 gmRL )

+2 fp

ms

2qNa(

Cox

2fp VSB

VT 0 ( S VSB S) : 体效应系数

2fp)

与栅相关的三个电容参数:CGD,CGS,CGB

2020/1/3

7

1.4 频率特性

模型和模型参数特点:

部分模型参数的定义和0.5um工艺模型参数的典型值

– 在保持物理模型的基础上改进精度和计算效率,适用于不同的尺

寸范围。

– 尽可能减少器件模型参数(BSIM2 60个,BSIM3 33个)

– 注意不同工作区域的连续性,以使电路模拟时收敛性好。

– *基于MOS器件的准二维分析(记入几何和工艺参数)

电路设计用到的器件模型、模型参数由晶圆制造厂提供,是工艺 厂家根据制备的器件提取。

2020/1/3

3

1.4 频率特性 MOSFET物理模型:交流小信号参数

栅源交叠电容

栅源电容

栅漏电容 栅漏交叠电容

源极串联电阻

漏极串联电阻

跨导

寄生参数 2020/1/3 本征参数

漏-衬底pn结电容

4

1.4 频率特性

总的栅源电容

完整的小信号等效电路

总的栅漏电容

共源n沟MOSFET小信号等效电路(VBS=0)

20生20/1产/3 工艺线不同、晶圆制造厂不同,器件模型则不同

10

1.4 频率特性

只计入rdsபைடு நூலகம்

简化的小信号等效电路

2020/1/3

rs的影响

Vgs V 'gs (gmV 'gs )rs (1 gmrs )V 'gs V 'gs

I 'd

gmV 'gs

gm 1 gmrs

Vgs

[2(VGS

VT

)VDS

VD2S ]

I D(sat)

WnCox

2L

(VGS

VT

)(2 1

VDS)

与VT相关的模型参数:VT0,GAMMA, PHI

VTN

2qNa 2fp

Cox

VSB

- Q'ss Cox

+2 fp

ms

2qNa

Cox

2fp

- Q'ss Cox

2020/1/3

XIDIAN UNIVERSITY

2

1.4 频率特性

模型概述

电路设计中为准确预测电路性能,利用电路仿真软件对电路进行仿 真验证。

常用的电路仿真软件如HSPICE、PSPICE、SPECTRE 仿真:围绕器件建立电路的IV关系,是一数学求解的过程。

电路中元器件要用模型和模型参数来替代真正的器件。 模型:反映器件特性,可采用数学表达式、等效电路等形式。 常用模型:等效电路模型。 模型参数:描述等效电路中各元件值所用的参数。 等效电路模型建立方法: 首先通过器件物理分析确定器件等效电路模型的具体形式, 再把元器件看成一个“黑箱”,测量其端点的电学特性,提取出描 述该器件特性的模型参数。得到一等效电路模型代替相应器件。

沟道渡越时间 t

L vsl

10ps

截止频率ft

1 t

100GHz

沟道渡越时间通常不是 主要频率限制因素

限制因素2:栅电容充放电需要的时间

2020/1/3

截止频率:fT f Id 1

Ii

13

1.4 频率特性

输入电流

输出电流

电流-频率关系

负载电阻 Ii jCgsTVgs jCgdT (Vgs Vd )