数字电路4数据选择器及数值比较器

第四章4.3数据选择器、数值比较器

逻辑图

2. 两位数值比较器

真值表

输 入 输 出

A1 B1 A1 >B1 A1 < B1 A1 = B1 A1 = B1 A1 = B1

A0

B0

× × A0 >B0 A0 <B0 A0 = B0

FA>B F A<B FA= B 0 0 1 0 1 0 1 0 0 0 1 0 0 0 1

4.4.2 集成数值比较器 1. 集成数值比较器 集成数值比较器74LS85 的功能 功能表

功能说明:表中的输入变量包括A3与B3、A2与B2、A1与B1 、A0与B0和 功能说明:表中的输入变量包括 A与B的比较结果,A>B、A<B和A=B。A与B是另外两个低位数,设置低 与 的比较结果 的比较结果, 是另外两个低位数, 和 与 是另外两个低位数 位数比较结果输入端,是为了能与其它数值比较器连接, 位数比较结果输入端,是为了能与其它数值比较器连接,以便组成更多位 数的数值比较器; 个输出信号 个输出信号: 数的数值比较器;3个输出信号 FA>B、FA<B、和FA = B 分别表示本级的比 较结果。 较结果。

IA>B IA < IA=B A'>B' A'<B'B A'=B'

× × × × × × × × 1 0 0 × × × × × × × × 0 1 0 × × × × × × × × 0 0 1

FA>B A<B BA=B A>B FA < FA=B

1 0 1 0 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1

i =0 7

的与或表达式, Y是C、B、A和输入数据 0~D7的与或表达式,即 是 、 、 和输入数据 和输入数据D

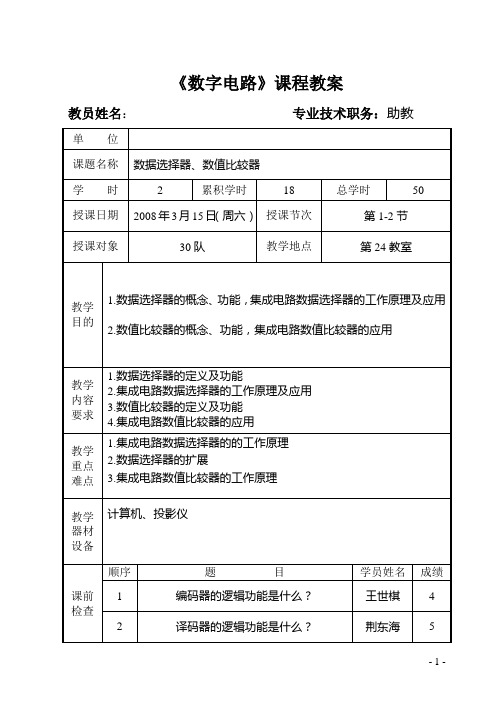

《数字电路》课程教学大纲

《数字电路》课程教学大纲课程编号:课程名称:数字电子技术基础总学时数:80 理论教学学时:60实验教学学时:20前修课程为高等数学,普通物理,电路分析,模拟电路。

后续课程有CPLD,数字信号处理,单片计,通讯原理等一、课程的任务与目的本课程是计算机科学和电子信息工程技术专业的一门专业基础课程。

主要任务是:1.系统的介绍数字系统的数学工具阐述数字系统的基本设计和分析方法。

2.通过数字电路的学习给后面的课程打下一定的理论和实践基础。

3.通过基本理论的学习掌握一定的数字系统的设计方法,及常用器件的应用,再结合实验、培养学生有一定的设计能力。

主要内容有:数制及转换,逻辑代数的公式、定理,逻辑函数的化简方法。

半导体二极管、三极管、MOS管的开关特性。

CMOS、TTL集成逻辑门。

组合逻辑电路的基本分析和设计方法。

加法器、比较器、编码器和译码器,数据选择器和分配器。

基本、同步、主从、边沿触发器、时钟触发器功能分类及转换。

时序电路的基本分析和设计方法。

计数器、寄存器、读/写存储器、只读存储器、序列脉冲发生器。

多谐振荡器,、施密特触发器。

数模、模数转换器。

教学重点与难点:教学重点是:逻辑代数的基本概念、公式、定理,逻辑函数的化简方法。

各种门电路的逻辑功能,两种集成逻辑门的电气特性。

各类触发器的逻辑功能及触发方式。

组合、时序电路的分析、设计方法。

常用典型组合、时序电路的功能、特点和应用。

典型中、大规模集成电路器件的功能和应用。

多谐、施密特、单稳的特点、功能、参数及应用。

数模、模数转换器的典型电路原理、输出量与输入量间的定量关系,特点、参数。

教学难点:逻辑代数的公式、定理的正确应用,逻辑函数化简的准确性。

集成逻辑门的电气特性。

组合、时序电路的设计。

触发器的触发方式以及脉冲产生,整形电路、数模、模数转换电路的工作原理。

采用的教学方法:课堂、实验、课程设计等相结合教材名称:电子技术基础数字部分康华光主编高等教育出版社2000年6月(第四版)主要参考书:1.高教出版社《数字电子技术基础》(四版)阎石编2.《数字电子技术基础》周良权高教出版社3.《数字电子技术基础简明教程》(第二版)余孟尝4.《数字电子技术基础》(第四版) 阎石高教出版社教学基本要求:第一章数字逻辑基础一、教学要求:1)掌握十、二、十六进制和8421码及其相互转换,了解八进制,余三码,GRAY和ASC Ⅱ码。

数字电路4数据选择器及数值比较器

A0 D10 D11 D12

(1 2

D13

)

S1

1 A

由4选1数据选择器实现

(2) 由8选1数据选择器实现 先将所给逻辑函数写成最小项之和形式,即

Y AB AC ABC ABC AB(C C) AC(B B) ABC ABC ABC ABC ABC ABC ABC ABC 1• ABC 0 • ABC 0 • ABC 0 • ABC

0 D0 D1 D3 D2 1 D4 D5 D7 D6

(3)比较逻辑函数 Y 和 Y 的卡诺图

设 Y = Y 、A = A2、B = A1、C = A0

对比两张卡诺图后得:

D0 D3

= =

D1 = D5 =

D2 = D4 = D6 = D7 =

0 1

(4)画连线图 与代数法所得图相同

用数据选择器实现组合逻辑电路(2)

Y1:输出端

S'1 : 附加控制端

输出端的逻辑式为:

Y1

[D10 A1A0

D11 A1A0

D12 A1 A0

D13

A 1

A0 ]S1

Y1

[D10 A1A0

D11 A1A0

D12 A1 A0

D13

A 1

A0 ]S1

其真值表如下表所示:

Y1 的卡诺图

S1 A1 A0 Y1 1 ×× 0

0 0 0 D10 0 0 1 D11 0 1 0 D12 0 1 1 D13

(2) 具有n 位地址输入的数据选择器,可以产生(n+1) 变量的组合逻辑函数。

例如:对于4选1数据选择器,在S'1=0时,输出 与输入的逻辑式为:

Y1 D0(A1A0 ) D1(A1A0 ) D2(A1A0 ) D3(A1A0 ) D0m0 D1m1 D2m2 D3m3

《数字电子技术》习题及答案

第1章 数制和码制 一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数 (10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数 (1001010.011001)2 =( )8 =( )16。

一、填空题答案: 1.26、32、1A ; 2.100011、43、 23; 3.10101001、A9、169; 4.1001011、113、75; 5.1000101、45、105; 6.2331、4D9; 7.112.31、4A.64。

第2章 逻辑代数基础 一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=; 3. ()()()()Y AB BC AC ''''=; 4. Y A '=; 5.1Y =; 6.1Y =; 7.Y A B =+。

数字电路实验报告-4选1数据选择器及其应用

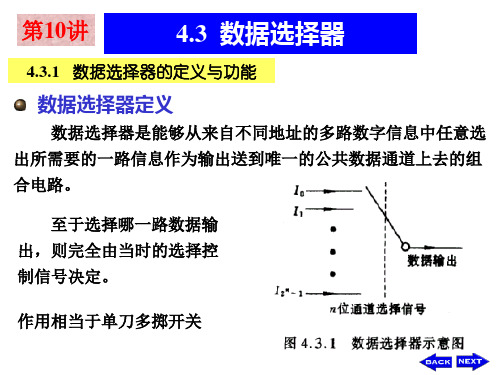

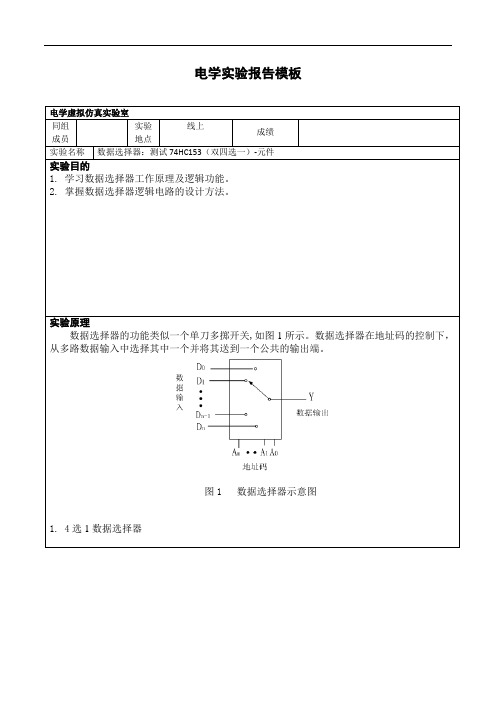

电学实验报告模板实验原理数据选择器的功能类似一个单刀多掷开关,如图1所示。

数据选择器在地址码的控制下,从多路数据输入中选择其中一个并将其送到一个公共的输出端。

图1 数据选择器示意图1. 4选1数据选择器图2 4选1数据选择器及其逻辑图2所示为4选1数据选择器及其逻辑。

该电路有4路输入数据和为地址输入。

为使能控制端,当时,数据选择器正常工作;当时,数据选择器的输出被锁定在“0”,不能选择。

由图2(b)可以得到该数据选择器的逻辑函数式为(1)2. 用4选1数据选择器扩展成8选1数据选择器8选1数据选择器有8路数据输入,3位地址输入。

如果用4选1数据选择器实现8选1,需要2片4选1数据选择器,如图所示。

其中,是通过4选1数据选择器的使能控制端接入的。

由图5并根据式(1),可以得到显然实现了8选1的逻辑功能。

图5 用4选1数据选择器扩展成8选1数据选择器实验仪器实验内容及步骤1. 测试和验证74HC153的逻辑功能(1)集成电路芯片74HC153引脚图74HC153是双4选1数据选择器,芯片内部包含两个独立的、完全相同的4选1数据选择器。

图7-5所示为引脚图。

每一个4选1数据选择器都设置了一个使能控制端。

两个4选1数据选择器共享地址输入端。

图6 74HC151引脚图(2)测试和验证74HC153的逻辑功能按图7连接电路。

实验数据记录在表7-1。

验证74HC153的逻辑功能。

图7 测试74HC151的逻辑功能实验电路表1(3)用一片74HC153扩展成8选1数据选择器图8 74HC153扩展成8选1数据选择器实验电路按图8连接电路。

实验数据记录在表2。

验证电路的逻辑功能。

表2实验结果及分析1.实验结果2.分析该实验结果表明74HC153元件实现了4选1的数据选择功能74HC153与74LS00两个4选1数据选择器拓展实现了8选1的逻辑功能实验结论1.74HC153具有4选1逻辑功能,能够实现数据选择,其有4路输入数据D0、D1、D2、D3,A0、A1为地址输入,为使能控制端,当时,数据选择器正常工作;当时,数据选择器的输出被锁定在“0”,不能选择。

数据选择器(MUX)

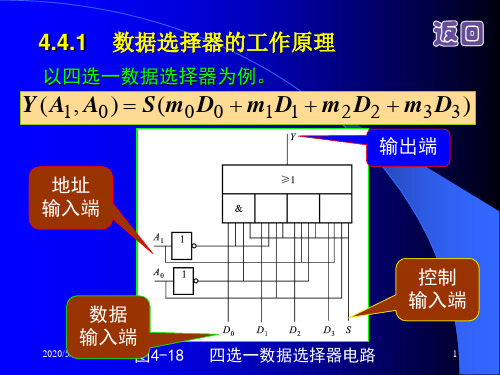

数据选择器(MUX)4.4.3 数据选择器(MUX)数据选择器原理集成数据选择器数据选择器扩展数据选择器应用(MUX-Multiplexer)11. 数据选择器原理数据选择器功能: 将多路输入数据中由n位通道选择信号确定的其中一路数据传送到输出端。

又称为“多路选择器”或“多路(数字)开关”。

数据输入D0 D1 DN-1n位通道选择信号(N=2n)同相或 Y 反相输出数据选择器功能示意图2…数据选择器原理例: 一种4-1MUX的功能表逻辑符号: S1 S0 0 0 1 1 0 1 0 1 F D0 D1 D2 D3S1 S0 F 4-1MUX D0 D1 D2 D3输出表达式: F = S 1 S 0 D 0 + S 1 S 0 D1 + S 1 S 0 D 2 + S 1 S 0 D 3= m0 D0 + m1 D1 + m2 D2 + m3 D3= ∑ mi Dii =03(其中mi是由通道选择信号S1,S0构成的最小项)3MUX的输出信号一般表达式2n -1 MUX的输出信号一般表达式:F = m 0 D 0 + m1 D1 + ? ? ? + m 2 n ? 1 D 2 n ? 1 =2 n ?1 i=0∑m Dii(其中mi 是n 位通道选择信号构成的最小项)42. 集成数据选择器例:8-1 MUX 74151S2X功能表使能 E 1 0 0 0 0 0 0 0 0 输出 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 Y 1 D0 D1 D2 D3 D4 D5 D6 D7通道选择 S1 S0X X输出表达式为:Y = E (∑ mi Di )i =07(mi 是S2,S1,S0构成的最小项)0 0 0 0 1 1 1 10 0 1 1 0 0 1 10 1 0 1 0 1 0 1574151逻辑符号与引脚排列D0 D1 D2 D3 D4 D5 D6 D7 E S2 S1 S0Y8YD3 D2 D1 D0 Y Y G GND11674HC151Vcc D4 D5 D6 D7 S0 S1 S274LS151 74HC1516具有三态输出的集成数据选择器例:8-1 MUX 74251 功能表S2X通道选择 S1 S0X X0 0 0 0 1 1 1 10 0 1 1 0 0 1 10 1 0 1 0 1 0 1使能 E 1 0 0 0 0 0 0 0 0输出 Y Z D0 D1 D2 D3 D4 D5 D6 D7 Y Z D0 D1 D2 D3 D4 D5 D6 D7(Z:高阻态)73. 数据选择器扩展例:用2片74151扩展成16-1MUXY ≥1 Y &- 通道扩展YY 74151(2)YG A 2 A1 S00 E S2 S 1 AD7 D6 D 5 D4 D 3 D2 D1 D0 1E A2 A 0 G S2 S11SA 0D7 D 6 D5 D4 D3 D2 D 1 D0D15 D14 D13 D12 D11 D10 D 9D8S A A A A33 S2 2 S11 S00D7 D6 D 5 D4 D3 D2 D1 D08数据选择器扩展 - 位扩展例:两位数的8-1 数据选择电路 S2 S1 S0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Y1 Y0 I10 I00 I11 I01 I12 I02 I13 I03 I14 I04 I15 I05 I16 I06 I17 I07 I17 I10 I11D0 D1I00 I01D0 D18-1 MUXY0I07D7 S ~S E 2 08-1 MUXY1D7 S ~S E 2 03S2~ S0 E94. 数据选择器应用-多通道数据传输例:I 0 8-1 I 1 MUX I2 I3 Y I4 I5 I6 I 7 S2 S1 S0S2 S1 S0公共数据线Y0 Y1 Y2 Y3 D Y4 Y5 Y6 A2 A1A0 Y71-8 DEMUXA2 A1 A0利用数据选择器与数据分配器实现多路数据的分时传输10数据选择器应用-实现逻辑函数任何逻辑函数都可表示成最小项之和形式:F =∑ m (此 m 是由F的输入变量构成的最小项)i iiMUX的输出表达式: Y =∑2 n ?1i =0mi Di(此mi是由通道选择信号构成的最小项)一般,当用具有n个通道选择端的MUX实现n变量的逻辑函数时,只需将逻辑函数的输入变量与MUX的通道选择端一一对应,并令逻辑函数中mi所对应MUX输出表达式中的Di=1,其余项对应的Di=0,即可实现。

数据选择器比较器

B3 A3 B2 A2 B1 A1 B0 A0

7485(4)

I A>B I A<B

0 0

FA<B

FA>B IA=B 1

7485(3)

I A>B I A<B

0 0

FA<B

FA>B I A=B

1

7485(2)

I A>B I A<B

0 0

FA<B

FA>B I A=B

1

7485(1)

I A>B I A<B

0 0

解:将A、B 接到地址输入端,C 加到适当的数据输入端。

L AB ABC ABC ABC ABC L

AB ABC A B C

Y 4选 1数 据 选 择 器

A1 A0

D 3 D2 D1 D0

1 AB

0

C

1

4.4 常用组合逻辑集成电路

3.实现数据的并/串转换

L

计 Q2 数 Q1 器

Y

Y

②画出数据选择器连线图。

③在函数所包含的最小项对应 的数据输入端写1,没有包含的 最小项对应的数据端写0.

74151

G A2 A1 A0 D7D6 D5 D4D3 D2 D1 D0

0

A BC

1

4.4 常用组合逻辑集成电路

(2)逻辑函数的变量个数大于数据选择器的地址输入变量个数时。 例:用4选1数据选择器实现函数: L AB BC AC

4.4 常用组合逻辑集成电路

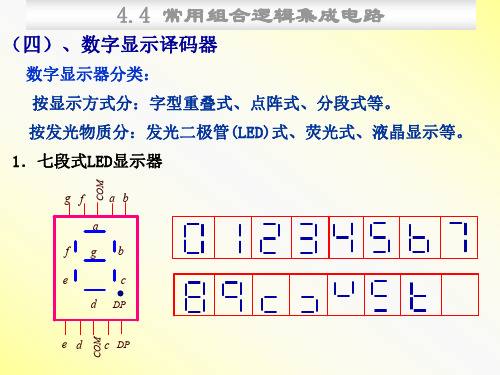

(四)、数字显示译码器

数字显示器分类: 按显示方式分:字型重叠式、点阵式、分段式等。 按发光物质分:发光二极管(LED)式、荧光式、液晶显示等。 1.七段式LED显示器

COM

g f ab

第四章 数据选择器、数值比较器、加法器、竞争冒险

将F与Y对照可得

D0 1, D1 C , D2 C , D3 0

19

A1 A, A0 B, D0 1, D1 C , D2 C , D3 0

F

B A

“1”

C

20

【例3】设计一个用3个开关控制灯的逻 辑电路,要求任一个开关都能控制灯的 由亮到灭或由灭到亮。 A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Y 0 1 1 0 1 0 0 1

24

4.3.3 数据选择器

8选1数据选择器74HC151的输出端逻辑式为

Y ( A2 A1 A0 ) D0 ( A2 A1 A0 ) D1 ( A2 A1 A0 ) D2 ( A2 A1 A0 ) D3 ( A2 A1 A0 ) D ( A2 A1 A0 ) D5 ( A2 A1 A0 ) D6 ( A2 A1 A0 ) D7

25

4.3.3 数据选择器

比较上面两式,令: A2=A,A1=B, A0=C,D1=D2=D3=0, D0=D4=D5=D6=D7=1

故其外部接线图如图所示

Y A B C A2 A1 Y 74HC 151 S Y’

A 0 D 0 D 1 D 2 D 3 D 4 D5 D 6 D 7

实验五--4选1多路复用器和4位比较器设计与仿真

实验五 4选1多路复用器和4位比较器设计与仿真班级信息安全一班姓名邓一蕾学号2指导老师袁文澹一、实验目的1.熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言和逻辑图设计四选一多路选择器,4位比较器。

二、实验内容1.参照芯片74LS153的电路结构,用逻辑图和VHDL语言设计四选一多路复用器;2.从QuartusⅡ中取7485器件(比较器)进行仿真与分析;用VHDL语言设计4位比较器,接着进行仿真与分析,电路逻辑结构参照芯片74x85三.实验原理1.(1)四选一多路选择器逻辑电路的原理4选1多路选择器,GN为使能端,AB为选择通道控制端,c0,c1,c2,c3为数据输入端.Y为输出端。

当GN为1时,y=0;当GN为0,AB=00时,Y为c0的值;当GN为0,AB=01时,Y为c1的值;当GN为0,AB=10时,Y为c2的值;当GN为0,AB=11时,Y为c3的值;(2)通过实验实现逻辑的原理2.(1)4位比较器的逻辑电路图A0,B0,A1,B1,A2,B2,A3,B3为相比较数输入端,ALBI,AEBI,AGBI为级联输入端ALBO,AEBO,AGBO为比较输出端。

2)通过实验实现逻辑的逻辑功能表为四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

1.4选1多路选择器实验步骤:编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击 as以“.vhd”为扩展名存盘文件。

2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

数字电路第4章(3译码器及应用)_4

出 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0

A0 Y7 Y6 Y5 Y4 Y 3 Y2 Y1 Y0

' ' Y0 A2 A1' A0 m0 ' Y1 A2 A1' A0 m1 ' ' Y2 A2 A1 A0 m 2

0 0 0 0 1 1 1 1

Y2 A3 A2 A1 A0 Y3 A3 A2 A1 A0 Y6 A3 A2 A1 A0 Y 7 A3 A2 A1 A0

Yi mi (i 0 ~ 9)

4线-10线译码器74HC42真值表

输

A3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

输入:二进制代码(N位) 输出:2N个,每个输出对应一个最小项。 ★最简单是译码器是2线-4线译码器。 ★输入是三位二进制代码、有八种状态,八个输 出端分别对应其中一种输入状态。因此,又把 三位二进制译码器称为3线—8线译码器。

2线-4线译码器:

2线—4线译码器真值表 输

S' 1 0 0 0 0 A × 0 0 1 1

入

B × 0 1 0 1

输

Y'0 1 0 1 1 1 Y'1 1 1 0 1 1 Y'2 1 1 1 0 1

出

Y'3 1 1 1 1 0

写出各输出函数表达式:

Y0 (SAB) Y1 (SAB) Y2 (SAB)

Y3 (SAB)

Y' 3

数字逻辑教学课件 数字电路2-4

4. 中规模组合逻辑部件 掌握典型集成电路的外部功能、扩展、应用。

–数据选择器:根据地址码的要求,从多路输入信号中 选择其中一路输出。

选择数据

应用:

并 —> 串

实现组合逻辑

–译码器:特定意义信息的二进制代码翻译出来,常用的 有二进制译码器、二-十进制译码器、数码显示译码器。

片选、地址译码

应用:

实现数据分配

0110 1 0110

7+5=12

=(0001 0010)8421

75 0111

0101 1100

0110 1 0010

一旦需要修正,则8421码必有进位输出。

判 9 加 6 修正电路:

1)当有进位输出 或 2) 当和数>9;

应修正让其产生进位,且加(0110);

设计两个一位8421BCD码加法电路应由三部分组成。

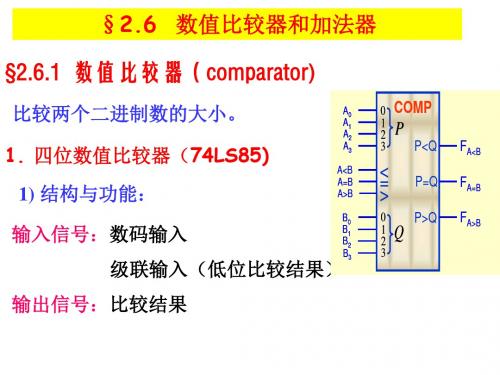

§2.6 数值比较器和加法器

§2.6.1 数值比较器(comparator)

比较两个二进制数的大小。

A0

A1

A2

1. 四位数值比较器(74LS85)

A3

A<B

1) 结构与功能:

A=B A>B

B0

输入信号:数码输入

B1 B2

级联输入(低位比较结果)B3

输出信号:比较结果

0 COMP

1 2

P

3 P<Q FA<B

奇校验位(监督位): P C1 C2 C2 Cn 1

74LS280

A B C EVEN D

E F ODD G H

“1” I

奇校验位

3) 校验位产生 / 校验检测

D0

D7

片1奇校验 位产生器

数电第4章-(3)

1EN 1D 0 1D 1 1D 2 1Y 1D 3 2D 0 74153 2D 1 2Y 2D 2 2D 3 2EN A 1 A 0

图 4.2.21 74153的简化逻辑符号 的简化逻辑符号

2. 八选一数据选择器

EN A0 A1 A2 D0 D 1 74151 Y D2 D3 D4 D5 D6 D7

A2

D0 D1 D2 D3 D4 D5 D6 D7

A1

A0

Y D0~D3 D4~D7

0 1

00 ~ 11 00 ~ 11

1

Y

1

A2

A 1 A0

四选一扩展为八选一MUX 图 4.2.23 ( a ) 四选一扩展为八选一

数选器74LS151扩展成一个 选1数据选择器。 扩展成一个32选 数据选择器 数据选择器。 例:试将8选1数选器 试将 选 数选器 扩展成一个

输出 Y 0 D0 D1 D2 D3

使能 输入 EN 0 0 0 0

输 入 A2 1 1 1 1 A1 0 0 1 1 A0 0 1 0 1

输出 Y D4 D5 D6 D7

八选一MUX的卡诺图 八选一

A1A0 00 01 11 10 A2 0 D0 D1 D3 D2 八选一MUX的逻辑表达式 八选一 1 D4 D5 D7 D6 EN = 1, Y = 0 ; 图4.2.24 ( a ) EN = 0, Y = A2A1A0D0+ A2 A1A0D1+ A2A1A0D2 + A2A1A0D3 +A2A1A0D0+ A2 A1A0D1+ A2A1A0D2 + A2A1A0D3

C B A

1 D D D 1

D

1

图 4.2.28 ( c )

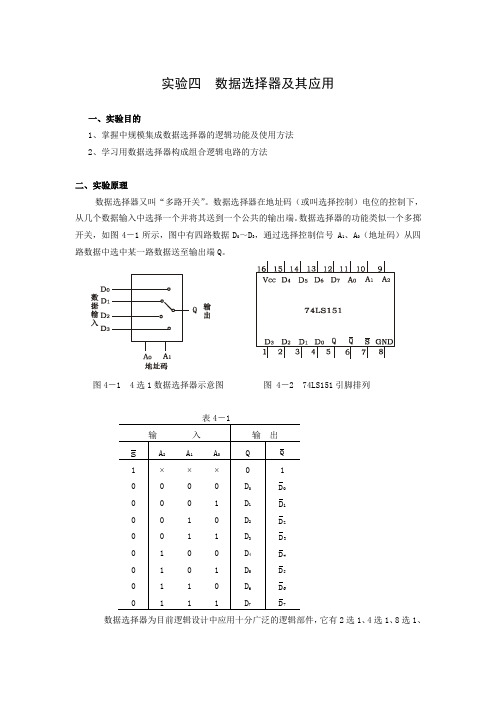

实验四 数据选择器及其应用

实验四数据选择器及其应用一、实验目的1、掌握中规模集成数据选择器的逻辑功能及使用方法2、学习用数据选择器构成组合逻辑电路的方法二、实验原理数据选择器又叫“多路开关”。

数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。

数据选择器的功能类似一个多掷开关,如图4-1所示,图中有四路数据D0~D3,通过选择控制信号 A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q。

图4-1 4选1数据选择器示意图图 4-2 74LS151引脚排列数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。

数据选择器的电路结构一般由与或门阵列组成,也有用传输门开关和门电路混合而成的。

1、八选一数据选择器74LS15174LS151为互补输出的8选1数据选择器,引脚排列如图4-2,功能如表4-1。

选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Q,S为使能端,低电平有效。

1)使能端S=1时,不论A2~A0状态如何,均无输出(Q=0,Q=1),多路开关被禁止。

2)使能端S=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7中某一个通道的数据输送到输出端Q。

如:A2A1A0=000,则选择D0数据到输出端,即Q=D0。

如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推。

2、双四选一数据选择器 74LS153所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。

引脚排列如图4-3,功能如表4-2。

图4-3 74LS153引脚功能S 1、S 2为两个独立的使能端;A 1、A 0为公用的地址输入端;1D 0~1D 3和2D 0~2D 3分别为两个4选1数据选择器的数据输入端;Q 1、Q 2为两个输出端。

1)当使能端S 1(S 2)=1时,多路开关被禁止,无输出,Q =0。

实验五 4选1多路复用器和4位比较器设计与仿真

实验五 4选1多路复用器和4位比较器设计与仿真班级信息安全一班姓名邓一蕾学号201208060106指导老师袁文澹一、实验目的1.熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言和逻辑图设计四选一多路选择器,4位比较器。

二、实验内容1.参照芯片74LS153的电路结构,用逻辑图和VHDL语言设计四选一多路复用器;2.从QuartusⅡ中取7485器件(比较器)进行仿真与分析;用VHDL语言设计4位比较器,接着进行仿真与分析,电路逻辑结构参照芯片74x85三.实验原理1.(1)四选一多路选择器逻辑电路的原理4选1多路选择器,GN为使能端,AB为选择通道控制端,c0,c1,c2,c3为数据输入端.Y 为输出端。

当GN为1时,y=0;当GN为0,AB=00时,Y为c0的值;当GN为0,AB=01时,Y为c1的值;当GN为0,AB=10时,Y为c2的值;当GN为0,AB=11时,Y为c3的值;(2)通过实验实现逻辑的原理2.(1)4位比较器的逻辑电路图A0,B0,A1,B1,A2,B2,A3,B3为相比较数输入端,ALBI,AEBI,AGBI为级联输入端ALBO,AEBO,AGBO为比较输出端。

2)通过实验实现逻辑的逻辑功能表为四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

1.4选1多路选择器实验步骤:编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

2、按照实验箱上FPGA的芯片名更改编程芯片的设臵。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

数值比较器

An ( Bn C n1 ) An ( Bn C n1 )

2014-5-7

An Bn C n1

15

由真值表写 最小项之和 式,再稍加 变换得:

An Bn Cn-1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

Sn 0 1 1 0 1 0 0 1

2014-5-7 14

An Bn Cn-1 Sn Cn 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 由真值表写 1 0 0 1 0 最小项之和 式,再稍加 1 0 1 0 1 变换得: 1 1 0 0 1 1 1 1 1 1 全加器 的真值表 S n An BnC n1表 3-12 An Bn C n1 An Bn C n1 An BnC n1

A<B 最低位 A'<B'

„

A4 B4 A3 B3

„

A0 B0

25

3.3 常用的逻辑电路

例:试用两片4585比较两个7位二进制数

C6C5C4C3C2C1C0和D6D5D4D3D2D1D0的大小。

解:

D3 C3 C2 C1 C0 D2 D1 D0 0 B3 A3 B2 A2 B1 A1 B0 A0 I (A<B ) I (A=B ) I (A>B )

余3码

仿真 8421BCD码

2014-5-7

0011

图3-24 由74LS283构成的代码转换电路

20

3.6

数值比较器

数值比较器:能够比较数字大小的电路。 1.两个一位数A和B相比较的情况: (1)A>B:只有当A=1、B=0时,A>B才为真; (2)A<B:只有当A=0、B=1时,A<B才为真; (3)A = B:只有当A=B=0或A=B=1时,A = B才为真。

4位数值比较器设计

4位数值比较器设计-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN电子技术课程设计报告题目: 4位数值比较器设计学生姓名:学生学号:年级:专业:班级:指导教师:机械与电气工程学院制2016年11月4位数值比较器设计机械与电气工程学院:自动化专业1.课程设计的任务与要求课程设计的任务采用Multisim 软件实现4位数值比较器的设计与仿真。

课程设计的要求(1)设计一个4位数值比较器的电路,对两个4位二进制进行比较。

(2)采用74Ls85集成数值比较器。

(3)要有仿真效果及现象或数据分析。

2.四位数值比较器设计方案制定四位数值比较器工作的原理对两个4位二进制数A3A2A1A0与B3B2B1B0进行比较。

从A的最高位A3和B的最高位B3进行比较,如果他们不相等,则该位的比较结果可以作为两数的比较结果。

若最高位A3=B3,则再比较次高位A2=B2,余此类推。

如果两数相等,那么,必须将进行到最低位才能得到结果。

可以知道:FA>B=FA3>B3+FA3=B3FA2>B2+FA3=B3FA2=B2FA1>B1+FA3=B3FA2=B2FA1=B2F A0>B0+FA3=B3FA2=B2FA1=B1FA0=B0IA>B (2-1)FA<B=FA3<B3+FA3=B3FA2<B2+FA3=B3FA2=B2FA1<B1+FA3=B3FA2=B2FA1=B2F A0<B0+FA3=B3FA2=B2FA1=B1FA0=B0IA<B (2-2)FA=B=FA3=B3FA2=B2FA1=B1FA0=B0IA=B (2-3)IA>B、IA<B和IA=B称为扩展输入端,是来自地位的比较结果。

扩展输入端与其他数值比较器的输出连接,以便组成位数更多的书值比较器。

若仅对4位数进行比较时,IA>B、IA<B、IA=B进行适当处理,IA>B=IA<B=0,IA=B=1。

数字电子技术 第4章 组合逻辑电路

图 4.3.8 7448逻辑符号图

数字电子技术

/// 16 ///

图4.3.9 7448驱动BS201A数码管的工作电路 图4.3.10 有灭零控制的8位数码显示系统

数字电子技术

/// 17 ///

3.译码器的应用 由于译码器的输出为最小项取反,而逻辑函数可以写成最小项之和的形式,故可以利用附加的 门电路和译码器实现逻辑函数。

组合电路就是由门电路组合而成,电路中没有记忆单元,没有反馈通路。

数字电子技术

/// 4 ///

4.1.2 组合逻辑电路的分析

根据逻辑功能的不同特点,可以把数字电路分成两大类,分别是: (1)是组合逻辑电路(简称组合电路) (2)是时序逻辑电路(简称时序电路) 组合电路就是由门电路组合而成,电路中没有记忆单元,没有反馈通路。

图4.5.6 数值比较器逻辑电路图

4.2.3 优先编码器

识别多个编码请求信号的优先级别,并进行相应编码的逻辑部件称为优先编码器。 在优先编码器电路中,允许同时输入两个以上编码信号。 在设计优先编码器时已将所有的输入信号按优先顺序排了队,当几个编码信号同时出现时,只 对其中优先权最高的一个进行编码。

1.设计优先编码器线(4线-2 线优先编码器)

图4.1.3 组合逻辑电路设计步骤

数字电子技术

/// 6 ///

4.1.4 组合逻辑电路的竞争和冒险

同一个门的一组输入信号,由于它们在此前通过不同数目的门,经过不同长度导线的传输,到 达门输入端的时间会有先有后,这种现象称为竞争。

逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲的现象,称为冒险。

图4.1.6 两种冒险波形图

数字电子技术

/// 7 ///

4.2 编码器

9 数据选择器和数值比较器

蛋炒饭作文300字蛋炒饭作文300字(精选26篇)蛋炒饭作文300字篇1每次看到妈妈在厨房里大显身手时,我就两眼冒光,心里很敬佩妈妈做饭时的动作,我学着妈妈做饭时的样子,加上妈妈对我的指点,做饭就成了我的拿手好戏。

我最拿手的一道菜是蛋炒饭,但学习的过程是很艰难的。

记得我第一次做蛋炒饭时,总是往打好的鸡蛋液里放调料,弄得炒出来的蛋炒饭很咸。

把火点着等油锅里的油热好了之后,把蛋液小心翼翼地倒进油锅里时,总把蛋液从高处倒下来,因为怕被油烫到,结果蛋液从高处落到油锅里,油反而四处乱溅,溅到手上、脸上更疼。

妈妈教我:“倒蛋液时,把碗放低一点,这样油就不会乱溅。

”听从妈妈的教诲,我掌握了倒鸡蛋液的技巧。

等鸡蛋液在锅里成型了,一边用锅铲切一个口子,让蛋液流出来,等另外一个成型了又切开一个口子。

蛋液成了蛋饼之后,再切成一段,把米饭倒进去,用锅铲捣碎。

蛋炒饭的米饭用隔夜饭比较好。

等所有技巧都掌握,我有一次自己一个人给爸爸妈妈做蛋炒饭时,看太干了,给加了点水,炒出来的饭黏黏的,真是为难了妈妈和爸爸。

但我知道了做蛋炒饭的基本做法,要想做好吃就要多练了。

现在,我的蛋炒饭已经出神入化了,你可以和我切磋一下吗?蛋炒饭作文300字篇2我特别喜欢吃爸爸做的蛋炒饭,他做的蛋炒饭颜色丰富,味道特别好。

今天上午,爸爸妈妈都在忙,我觉得自己也应该做点什么。

看到厨房里爸爸买好的菜,我灵机一动,心想:我来给爸爸妈妈做一次蛋炒饭吧!我走进厨房,开始准备材料。

我挑了一根胡萝卜、一截春笋、一个青椒、几根小葱,请爸爸帮忙洗干净,并切成小块备用。

这时,我从冰箱里拿出两个鸡蛋,打开倒进碗里,放入料酒和一点点盐,用筷子沿着一个方向把蛋液搅拌均匀。

我小心翼翼地打开煤气灶,等锅有点热气上来,先把油倒进去,再把打好的蛋液慢慢地倒入锅里,学着爸爸的样子用锅铲轻轻地翻动。

刚开始,我还有点害怕,怕油溅到手上,很快,我就觉得蛮好玩的。

蛋煎得差不多了,就把它盛出来,放到一个空盘子里。

4位数值比较器

X X大学课程设计题目4位数值比较器学院X学院专业XXX班级XXX学生XXX学号*********指导教师XXX二〇一〇年十二月二十七日摘要随着时代的进步,社会的发展,科学技术的进步,我们会在很多地方用到比较器。

例如,在体育竞技场地对一些选手的成绩进行比较,选出他们中的成绩优异者;我们为了比较一下不同物品的参数,我们可以利用一些科学技术来实现这些功能,使得我们的工作效率得以提高,减少了我们认为的工作量。

我们可以根据不同的需要来制造出不同类型的比较器。

我们可以利用一些我们所学的知识,利用一些简单的二极管、三极管、MOS管的开关特性来组成各种门电路的基本开关元件。

我们再利用这些元件组成比较器的组合逻辑电路。

根据不同的需要,来用不同的方法来连接元件实现不同的功能。

我们可以实现1位数比较器,2位数比较器,4位数比较器,8位数比较器等多种比较器。

关键词门电路;开关元件;比较器;逻辑电路;目录摘要 (1)1前言.................................................................. ................ .. (3)1.1C M O S组成的门 (3)1.1.1C M O S组成的非门 (4)1.1.2C M O S组成的与非门 (4)1.2位数比较器 (5)2 4位数比较器 (7)2.1 原理框图 (7)2.2逻辑电路图 (8)2.2.14位数逻辑电路图 (8)2.2.24位数比较器原理 (9)2.2.3 电路板示意图 (10)结论 (11)心得体会 (12)致谢 (14)参考文献 (14)1前言本课程设计主要是根据我们学习的余孟尝主编的《数字电子技术简明教程(第三版)》的后续课程。

这个课程设计在保证基础,精选内容,加强感念理解,联系实际,利于我们学习这门课程,加深对这门课程的理解 。

它还可以增加我们的实际思维能力和动手能力。

1.1 CMOS 组成的门本次课程设计需要一些简单的电路,我们开始先介绍简单的电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

解:如图连接方式, (1)当 A2=0 时, ★ 地址范围:000 ~ 011 ★ 上边选择器工作;通过

地址A1A0从D0~D3中选 择一个数据经Y1输出。 ★ 下边选择器被禁止,输 出Y2为低电平。 (2) 当A2=1时, ★ 地址范围:100 ~ 111

★ 下边选择器工作; 通过地址A1A0 从D4~D7中选择一个数 据经Y2 输出。

例2. 分别用4选1和8选1数据选择器实现逻辑函数

Y AB AC ABC ABC

解:(1)用4选1(四路)数据选择器实现

Y ( A2 A1A0 )D0 ( A2 A1A0 )D1 ( A2 A1A0 )D2 ( A2 A1A0 )D3 ( A2 A1A0 )D ( A2 A1A0 )D5 ( A2 A1A0 )D6 ( A2 A1A0 )D7

(2) 双 “4选1”数据选择器可以提供8个数据输入端; (3) “4选1”数据选择器只有2位地址输入,故需要利用

★ 编码器 ★ 译码器 ★ 数据选择器(多路选择器)、数据分配器 ★ 算术逻辑运算单元 ★ 数值比较器

数据选择器

工作原理:

数据选择器就是在数字信号的传输过程中,从一组 数据中选出某一个送到输出端,也叫多路开关。

又称多路选择器(Multiplexer,简称MUX)或多路开关。

数据选择器: 根据地址码的要求,从多路输入信号中 选择其中一路输出的电路.

即可得输出函数

Y

ST'

Y

A A2

74LS151

B A1

C

A0 D0 D1 D2 D3 D4 D5 D6 D7

0

1

卡诺图法求解

解:(1)选择数据选择器 选用 74LS151

(2)画出Y 和数据选择器输出Y' 的卡诺图

BC Y的卡诺图 A 00 01 11 10

0 001 0 1 0 11 1

A1A0 Y' 的卡诺图 A2 00 01 11 10

Y1:输出端

S'1 : 附加控制端

输出端的逻辑式为:

Y1

[D10 A1A0

D11 A1A0

D12 A1 A0

D13

A 1

A0 ]S1

Y1

[D10 A1A0

D11 A1A0

D12 A1 A0

D13

A 1

A0 ]S1

其真值表如下表所示:

Y1 的卡诺图

S1 A1 A0 Y1 1 ×× 0

0 0 0 D10 0 0 1 D11 0 1 0 D12 0 1 1 D13

4 选 1 数据选择器工作示意图

D0

多路输入

D1 D2

பைடு நூலகம்D3

Y=D1 一路输出

地址码输入

A01 A10

数据常选用择2器选的1、输4入选信1号、个8选数1N和与1地6选址1码等个数数据n的选关择系器为。N = 2n

以双4选1数据选 择器74HC153为 例说明数据选择 器的工作原理

逻辑图形符号

其中对于一个数据选择器: D10 ~ D13 : 数据输入端 A1、A0 : 选通地址输入端

Y = m0 D0 + m1 D1+ m2 D2+ m3 D3 当 D0 = D1 = D2 = D3 = 1 时,Y = m0 + m1+ m2 + m3 。

当 D0 ~ D3 为0、1的不同组合时,Y 可输出不同的最小项 表达式。

而任何一个逻辑函数都可表示成最小项表达式.因此,当逻 辑函数的变量个数和数据选择器的地址输入变量个数相同时, 可直接将逻辑函数输入变量有序地接数据选择器的地址输入 端。

(3)写出数据选择器的输出表达式

Y = m0D0+m1D1+m2D2+m3D3+m4D4+m5D5+m6D6 +m7D7 (4)比较两式中最小项的对应关系

令 A = A2 ,B = A1 ,C = A0 应令:D0 = D1 = D2 = D4= 0, D3 = D5 = D6 = D7 = 1

(5)画连线图

★ 上边选择器被禁止,输出Y1为低电平。

综上所说:8选1数据选择器的输出 Y=Y1+Y2

用数据选择器实现组合逻辑函数(1)

(1) 具有n位地址输入的数据选择器,可实现(不大于) n变量的任何形式组合逻辑函数。

由于数据选择器在输入数据全部为 1 时,输出为地址 输入变量全体最小项的和。

例如:4选1数据选择器的输出:

A0 A1

0

1

0 D0 D1

1 D2 D3

(1)当S'1=1时,数据选择器被禁止,输出封锁为低电平; (2)当S‘1=0时,数据选择器工作;

例1. 试用双4选1数据选择器74HC153组成8选1数据选 择器。

分析: (1) “8选1”数据选择器需要3位地址码,8个输入端,1

个输出端,输出端的逻辑式为:

例:试用数据选择器实现函数 Y = AB + AC + BC 。 代数法求解

解:(1)选择数据选择器

Y为三变量函数,故选用8选1数据选择器(74LS151)

(2)写出逻辑函数的最小项表达式

Y = AB + AC + BC = A'BC + AB'C + ABC' + ABC = m3 + m5 + m6 + m7

(2) 具有n 位地址输入的数据选择器,可以产生(n+1) 变量的组合逻辑函数。

例如:对于4选1数据选择器,在S'1=0时,输出 与输入的逻辑式为:

Y1 D0(A1A0 ) D1(A1A0 ) D2(A1A0 ) D3(A1A0 ) D0m0 D1m1 D2m2 D3m3

若将A1、A0作为两个输入变量,D0~D3为第三 个变量的输入或其他形式,则可由4选1数据选择器实 现任何3变量的组合逻辑函数。(逻辑函数产生器)

第四章 组合逻辑电路

本章主要内容

4.1 概述 4.2 组合逻辑电路的分析和设计 4.3 若干常用的组合逻辑电路 4.4 组合逻辑电路中的竞争-冒险现象

§4.3 常用的组合逻辑电路

MSI组合部件具有功能强、兼容性好、体积小、 功耗低、使用灵活等优点,因此得到广泛应用。本 节介绍几种典型MSI组合逻辑部件的功能及应用:

0 D0 D1 D3 D2 1 D4 D5 D7 D6

(3)比较逻辑函数 Y 和 Y 的卡诺图

设 Y = Y 、A = A2、B = A1、C = A0

对比两张卡诺图后得:

D0 D3

= =

D1 = D5 =

D2 = D4 = D6 = D7 =

0 1

(4)画连线图 与代数法所得图相同

用数据选择器实现组合逻辑电路(2)