dsp-ev-事件管理器

第八章DSP事件管理器

8.2 通用定时器

1个可读写的16位计数器TxCNT(x=1~4) 1个可读写的16位比较寄存器(双缓冲)TxCMPR(x=1~4) 1个可读写的16位的周期寄存器(双缓冲) TxPR(x=1~4) 可读写的定时器控制寄存器TxCON(x=1~4) 输入时钟可编程预定标器 控制和中断逻辑 定时器比较输出 输出控制逻辑 定时器2(4)可以选择定时器1(3)的周期寄存器值作为自己的 定时周期

B B B B B B B B B B B B B B B

PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM PHANTOM

连续增减计数:GP定时器按照定标的输入时钟加计

数,直到计数器的值和周期寄存器的值匹配,之后的 下一个时钟的上升沿,GP减计数直到计数器为0,并开 始以加计数的方式开始下一个计数周期,其间外设周 期匹配、下溢、上溢等中断事件产生并产生可以启动 ADC模块的事件(中断允许的条件下)。 定时周期: 2*TxPR*定标时钟 说明:TxCON.TENABLE位控制定时器的启动计数; GPTCONA/B中的状态位指示当前的计数方向; 适合产生对称的PWM波形。

说明:TDIRA/B引脚变化后,计数方向的改变在当前计

数完成一个时钟周期之后。在该方式下,第一个计数 脉冲将会丢失。

该方式能够用于事件管理器模块的QEP脉 冲计数或者作为外部脉冲计数。

例子

通用定时器1在定向增减计数模式下的初始化 LDP #DP_EVA ;指向7400h~7480h单元 SPLK #41H,GPTCONA ;TCOMPOE=1 允许定时器比较输出 SPLK #5H,T1PR ;设置周期寄存器 SPLK #3H,T1CMPR ;设置比较寄存器 SPLK #0H,T1CNT ;设置计数寄存器 SPLK #9852H,T1CON ;TMODE=11 定向增/减计数模式,TPS=000,预分频为1 ;TENABLE=1 定时器计数使能,TCLKS=01 外部时钟 ;TECMPR=1 定时器1比较使能,SELT1PR=0

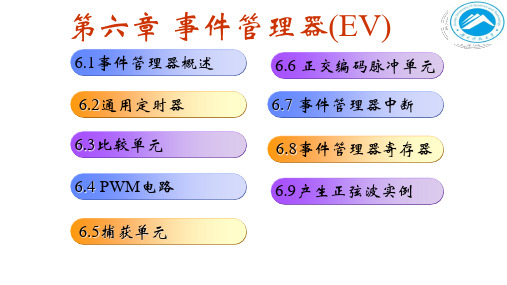

DSP原理与应用-【第6章-事件管理器EV】

第13页,共59页。

6.2.3.1 PWM信号概述

通用定时器的比较操作用来产生脉宽调制PWM信号。

方波高电平时间跟周期的比例叫占空比,例如,1秒高 电平1秒低电平的PWM波占空比是50%

要产生一个PWM信号:

➢ 1.需要一个定时器计数;计数周期与PWM载波周期相 同;

第21页,共59页。

6.4 PWM电路

PWM单元由对称/不对称波形发生器、可编程死区单元 DBU、PWM输出逻辑和空间向量SVPWM状态机组成;

对称/不对称波形发生器与通用定时器中的波形发生器 是相同的;

PWM电路能够在电机控制和运动控制应用领域中,将 CPU开销和用户工作量降到最低程度;

产生PWM波形时要涉及的寄存器主要有:定时器1控制 寄存器T1CON、比较控制寄存器COMCONA、比较动 作控制寄存器ACTRA和死区控制寄存器DBTCONA。

供电 输出

晶体管导通比截止快 同时导通的瞬间会发生直流电压短路

第24页,共59页。

可编程死区模块

外设时钟 对称/ 非对称 波形 死区

DTPHx

DTPHx_

死区

非对称PWM

HSPCLK

PHx 边沿 检测

预分频

DBTCONA . 4 - 2

ENA 4-bit reset 计数器

第25页,共59页。

比较器

➢ 如果比较中断未被屏蔽,将产生一个外设中断申请;

在PWM输出引脚TxPWM上可以产生对称或不对称的PWM波形 。

第15页,共59页。

6.2.3.3 不对称 PWM 波形发生

定时周期 周期结束 比较值

计数值

DSP课件 事件管理器EV

停止/保持模式

当TMODE的值为0时,定时器工作于停止/保持模式。 在这种模式下,通用定时器停止计数并保持当前的状态。 此时,定时器的计数寄存器T1CNT、比较输出 T1PWM_T1CMP将保持不变。

连续增/减计数模式

当TMODE的值为1时,定时器工作于连续增/减计数模式。

连续增/减计数模式时不同初始值情况下的计数

每个事件管理器有两个16位通用定时器。 EVA:T1、T2 EVB:T3、T4 通用定时器作用: 1.计时 2.使用定时器的比较功能产生PWM波 3.给其他子模块提供时基

通用定时器的结构框图

阴影寄存器的作用

Shadowed register-阴影寄存器

定时器比较寄存器重载条件——T1CON

T1产生对称的PWM波形

12.3 比较单元与PWM电路

桥电路理想的驱动波形 三相全桥电路

开关管状态切换

桥电路所需的实际带有死区的驱动波形

全比较单元

带有死区控制的PWM电路

死区单元模块图

比较单元1产生不对称PWM波

比较单元1产生对称PWM波

比较单元的中断事件

比较中断 功率驱动保护中断

电机转过的角度为

T2CNT[(K 1)t] T2CNT[kt] *360 4096

电机的转速n为

n

T2CNT[(K 1)t] T2CNT[kt] *60rpm 4096*t

模块

信号引脚 T1PWM_T1CMP T2PWM_T2CMP PWM1 PWM2 定时器3 定时器4

模块

信号引脚 T3PWM_T3CMP T4PWM_T4CMP PWM4 PWM5

比较单元1 比较单元 比较单元2

“简简单单DSP”系列学习活动——第七期事件管理器——通用定时器

“简简单单DSP”系列学习活动第七期事件管理器——通用定时器事件管理器(EV)强大的功能使它特别适用于运动控制和电机控制领域。

DSP 有两个相同的事件管理器EVA、EVB。

每个事件管理器模块包括通用定时器CP、全比较单元、可编程的死区发生器,PWM波形发生器、捕获单元CAP和和正交编码单元,A/D转换器的外部启动信号,功率驱动保护单元、EV寄存器以及EV中断等多个部分。

每一个EV还包含两路单独的PWM输出。

事件管理器的接口框图下图所示:从图中我们可以看出,每一个事件管理器模块都包含有:两个通用定时器、3个比较单元、三个捕获单元、一个正交编码电路,还可以有外部时钟、外部触发功率保护模块等。

常用的就是通用定时器、全比较PWM单元、和输入捕获单元,下面重点介绍这三个单元。

一、通用定时器CP1、通用定时器有四个中断:A、通用定时器1上溢中断B、通用定时器下溢中断C、通用定时器比较中断D、通用定时器周期中断这四个中断标志位在EVA中断标志寄存器A(EVAIFRA)中,这四个中断的使能位在EVA屏蔽寄存器EVAIMRA中设置。

2、通用定时器有三个16位的和定时比较有关的寄存器:A、通用定时器计数寄存器TXCNTB、通用定时器周期寄存器TxPRC、通用定时器比较寄存器TXCMPR通用定时器计数寄存器TxCNT根据通用定时器的时钟和计数模式开始计数,不停的和周期寄存器和比较寄存器从而产生中断或者各种事件。

当工作在定时器的模式时,TxCNT得值和TxPR中设置的值比较,当比较匹配后的一个时钟后,产生相应的事件当工作在比较的模式时,TxCNT得值和TxCMPR中设置的值比较,当比较匹配后的一个时钟后,产生相应的比较事件TxPR和TxCMPR都是带有影子寄存器的,在一个周期的任何时刻都可以对这两个寄存器进行读写,读写的是他们的影子寄存器。

对于TxCMPR,只有当TxCON 寄存器指定的特定条件满足时,影子寄存器中的值才加载到比较寄存器中;对于周期寄存器,只有当计数寄存器为0时,影子寄存器的值才能重新加载到周期寄存器。

DSP学习 7)_事件管理器及其应用

D5

R/W-0

D4

R/W-0

D3

R/W-0

D2

D1

R/W-0

D0

T1TOADC TCMPOE T2CMPOE T1CMPOE

通用定时器A控制寄存器

T2PIN

T1PIN

D15

R-0

D14

R-1

D13

R-1

D12

R/W-1

D11

R/W-1

D10

D9

D8

R/W-0

Reserved T4STAT T3STATT4CTRIPE T3CTRIPE T4TOADC T3TOADC

T3PWM/T3CMPT4 PWM/T4CMP

PWM1/2 PWM3/4 PWM5/6 CAP1 CAP 2 CAP3 QEP1 QEP2 QEPI1 TDIRA TCLKINA

PWM7/8 PWM9/10 PWM11/12 CAP4 CAP5 CAP6 QEP4 QEP5 QEPI2 TDIRB TCLKINB

TxOFINT位(x=1,2,3,4,下同)置1。

▲ 下溢:定时器计数器的值达到0000H,产生下溢中断。此时TxUFINT置1。 ▲ 比较匹配:当计数器值与比较器相等时,产生比较匹配中断。此时TxCINT置1。 ▲ 周期匹配:当计数器值与周期寄存器相等时,产生周期匹配中断。TxPINT置1。

一、通用定时器

▲ 比较输出TxCMP ▲ ADC转换启动信号 ▲ 提供上溢、下溢、

比较匹配和周期 匹配信号 ▲ 计数方向标识位

一、通用定时器

通用定时器 控制寄存器 TxCON

▲ 选择4种计数模式的一种 ▲ 使用内部还是外部时钟 ▲ 确定输入时钟使用的预定标参数 ▲ 确定比较寄存器重新装载的条件 ▲ 使能或禁止通用定时器 ▲ 使能或禁止通用定时器的比较操作 ▲ 定时器2或1的周期寄存器 ▲ 定时器4或3的周期寄存器

2005.2dsp EV模块功能简介

QEN时钟 QEN时钟

心得:QEP并不是一个单独的电路模块, 心得:QEP并不是一个单独的电路模块, 而是以上模块功能的集合。 工作:由捕捉模块对两个脉冲进行检测, 把CAPCONA的CAPQEPN设为11就把捕捉 CAPCONA的CAPQEPN设为11就把捕捉 模块设成了QEP模式,其实就是指捕捉模 模块设成了QEP模式,其实就是指捕捉模 块的时钟源来自两个引脚CAP1,2(对EVA)而 块的时钟源来自两个引脚CAP1,2(对EVA)而 不是GP。 不是GP。

相关寄存器

注意:捕获单元是由GP提供时钟 注意:捕获单元是由GP提供时钟 FIFO中存放的是TxCNT的值,要在中断时 FIFO中存放的是TxCNT的值,要在中断时 及时读出以免下一个值覆盖

四、QEP(正交编码脉冲模块) QEP(正交编码脉冲模块)

QEP:指两个频率变化且正交(相位相差90 QEP:指两个频率变化且正交(相位相差90 度)的脉冲,由电机轴上的光电编码器产 生。 功能:通过检测两个脉冲序列中的哪一列 先到可以判断出电机旋转方向,通过检测 脉冲数和脉冲频率可以检测电机旋转的角 位置和转速。

EV模块功能简介 EV模块功能简介

作者: 王世伟

学习心得

1 不用管内部硬件结构,即不管事件管理器 的功能是如何通过硬件实现的,会用即可 2 有些工作过程是cpu自动完成的,编程时 有些工作过程是cpu自动完成的,编程时 可不用管 3分别学习每一个部分功能(GP,比较,捕 分别学习每一个部分功能(GP,比较,捕 捉,QEP),最后再归纳一下各个部分的 捉,QEP),最后再归纳一下各个部分的 联系 4 EVA,EVB功能完全相同,仅仅是对其定义 EVA,EVB功能完全相同,仅仅是对其定义 的寄存器有A,B之分 的寄存器有A,B之分

第六章 DSP EV事件管理器

寄存器 EVBIMRA EVBIMRB EVBIMRC EVBIFRA EVBIFRB EVBIFRC

名

称

中断屏蔽寄存器A

中断屏蔽寄存器B

中断屏蔽寄存器C

中断标志寄存器A

中断标志寄存器B

中断标志寄存器C

6.2 通用定时器

6.2.1 通用定时器(GPT-General Purpose Timer)概述

TPWM/T1CMP 输出引脚

输出逻辑 T1PWM

预定标计数分频器,可

中断标志

设置为对内部时钟或外 部时钟进行分频计数

ADC启动 CPU时钟

T1CNT 控制逻辑

可选择方向的 输入引脚TDIRx

GPTCONA

TDIRA

GP控制寄存器

TCLKINA<1/4fc(外部时钟)

预定标:1-1/128fc

T1CON 可选择的内部或外部输入时钟

6.1.1 事件管理器结构、引脚

比较/PWM输出引脚:每个事件管理器都有8个比较/PWM输出引脚。 其中,2个为通用定时器的比较/PWM输出,6个全比较器的

比较/PWM输出。

片外时钟输入引脚:定时器可以通过软件编程决定使用片内时钟 还是片外时钟。当使用片外时钟时,TCLKINA、TCLKINB 作为片外时钟输入引脚。

通用定时器的控制寄存器

6.2.1 通用定时器概述

1)单个通用定时器控制寄存器TxCON(x=1,2,3,4) TxCON决定着定时器的操作模式

15

14

13

12

11

10

9

8

Free Soft 保留位 TMODE1 TMODE0 TPS2 TPS1 TPS0

7

6

DSP事件管理器实验报告

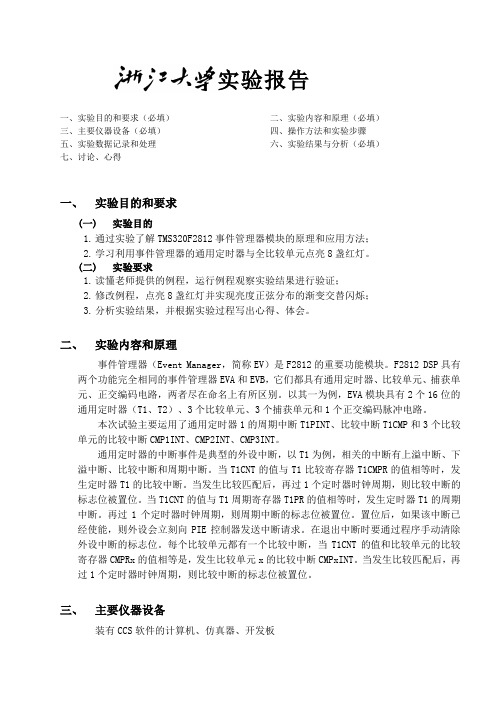

实验报告一、实验目的和要求(必填)二、实验内容和原理(必填)三、主要仪器设备(必填)四、操作方法和实验步骤五、实验数据记录和处理六、实验结果与分析(必填)七、讨论、心得一、实验目的和要求(一)实验目的1.通过实验了解TMS320F2812事件管理器模块的原理和应用方法;2.学习利用事件管理器的通用定时器与全比较单元点亮8盏红灯。

(二)实验要求1.读懂老师提供的例程,运行例程观察实验结果进行验证;2.修改例程,点亮8盏红灯并实现亮度正弦分布的渐变交替闪烁;3.分析实验结果,并根据实验过程写出心得、体会。

二、实验内容和原理事件管理器(Event Manager,简称EV)是F2812的重要功能模块。

F2812 DSP具有两个功能完全相同的事件管理器EVA和EVB,它们都具有通用定时器、比较单元、捕获单元、正交编码电路,两者尽在命名上有所区别。

以其一为例,EVA模块具有2个16位的通用定时器(T1、T2)、3个比较单元、3个捕获单元和1个正交编码脉冲电路。

本次试验主要运用了通用定时器1的周期中断T1PINT、比较中断T1CMP和3个比较单元的比较中断CMP1INT、CMP2INT、CMP3INT。

通用定时器的中断事件是典型的外设中断,以T1为例,相关的中断有上溢中断、下溢中断、比较中断和周期中断。

当T1CNT的值与T1比较寄存器T1CMPR的值相等时,发生定时器T1的比较中断。

当发生比较匹配后,再过1个定时器时钟周期,则比较中断的标志位被置位。

当T1CNT的值与T1周期寄存器T1PR的值相等时,发生定时器T1的周期中断。

再过1个定时器时钟周期,则周期中断的标志位被置位。

置位后,如果该中断已经使能,则外设会立刻向PIE控制器发送中断请求。

在退出中断时要通过程序手动清除外设中断的标志位。

每个比较单元都有一个比较中断,当T1CNT的值和比较单元的比较寄存器CMPRx的值相等是,发生比较单元x的比较中断CMPxINT。

dsp课件6-事件管理器

EVA模块

Synchronize With

1. 置T1CON的TENABLE位为1,置T2CON的T2SWT1位为1,

同时启动两个定时器的计数器。

2. 在启动同步操作前,定时器1、2的计数器初始化成不同的

值。

3. 置T2CON的SELT1PR位为1,使定时器2用定时器1作为它的

周期寄存器。

EVB模块作类似的操作,使定时器3、4同步。

事件管理器A、B的定时器寄存器地址

事件管理器A、B的比较控制寄存器地址

事件管理器A、B的捕获控制寄存器地址

中 断 寄 存 器

事件管理器A、B的中断寄存器地址

7.1.3.1 PDPINTx中断(x=A/B) 1. 当功率变换器过压、过流、过温,保护功率器件,如IGBT。 2. 如PDPINTx中断未被屏蔽,当PDPINTx引脚被拉到低电平,

内部CPU时钟。 外部时钟TCLKINA/B,最大频率是CPU时钟频率的1/4。 方向输入TDIRA/B,用于控制通用定时器定向增/减计数模式。 复位信号RESET。

通用定时器比较输出TxCMP。 至模数转换启动信号。 比较逻辑和比较单元的下溢、上溢、比较匹配和周期匹

配信号。

计数方向指示位。

1. 上溢-TxOFINT(X=1、2、3、4):计数器的值达到FFFF时。 2. 下溢-TxUFINT(X=1、2、3、4):计数器的值达到0000时。 3. 比较匹配-TxCINT(X=1、2、3、4) 4. 周期匹配-TxPINT(X=1、2、3、4)

Note:每个中断标志位都是在每个事件发生后两个周期被置位。

Control logic

TCLKINA TDIRA

TxCON

GPTCONA (shadowed)

第六章 事件管理器

TCLKINA/TDIRA ADC Start

T1PWM

PWM1 PWM2 PWM3 PWM4 PWM5 PWM6

T2PWM

CAP1/QEP1 CAP2/QEP2 CAP3/QEPI1

6.2 通用定时器

输入信号:时 钟信号,计数 方向(增/减 计数模式时) 输出信号:4路 比较输出,启 动A/D转换信 号,下溢、上 溢、比较匹配 和周期匹配信 号 ,计数方向 指示

定时器1 比较器单元

T1PWM

总

线

PWM比较单元1 PWM比较单元2

PWM比较单元3

PWM电路 输出逻辑

PWM1 PWM2 PWM3 PWM4 PWM5 PWM6

GP定时器2

MUX

CLK

DIR

捕获比较 单元

定时器2

比全较单比元 较 P电QWE路P M单

元

T2PWM

CAP1/QEP1 CAP2/QEP2 CAP3/QEPI1

MUX

捕获比较 单元

定时器2 比较单元

PWM波形 CLK

DIR

QEP 电路

发生器

TCLKINA/TDIRA ADC Start

T1PWM

PWM1 PWM2 PWM3 PWM4 PWM5 PWM6

T2PWM

CAP1/QEP1 CAP2/QEP2 CAP3/QEPI1

事件管理器内部结构

复位

PIE

事件管理器控制单元

如果GPTCONA/B选择比较匹配作为ADC启动转换信号, 则同时产生ADC启动转换信号SOC;

如果比较中断未被屏蔽,将产生一个外设中断申请;

在PWM输出引脚TxPWM上可以产生对称或不对称的 PWM波形。

事件管理器(EV)

3---2

T2PIN

1---0

T1PIN

通用定时器框图

定时器控制寄存器TxCON,x=1,2,3,4

15

Free

14

Soft

13

reserved

通用定时器(GP)

• 通用定时器是常用的外设接口,其核心为计数器。 • 16位的全局通用定时器控制寄存器GPTCONA(EVA)和GPTCONB(EVB) 用来规定通用定时器在不同定时事件中所采取的操作,并记录他们的方向。 • 每个通用定时器包括: * 一个16位可读写的定时计数器TxCNT * 一个16位可读写的定时器比较寄存器(带影子寄存器)TxCMPR ^注:每个比较寄存器和周期寄存器都有一个暂存单元(称为影子寄存器) * 一个16位可读写的定时器周期寄存器TxPR (带影子寄存器) * 一个16位可读写的定时控制器TxCON * 一个通用定时器比较输出引脚TxCMP * 用于内部或外部时钟输入的可编程定标器。

周期寄存器TxPR

• 每个通用定时器都有一个周期寄存器,其映射地

址为:T1PR——7403H, T2PR——7407H,

T3PR——7503H, T4PR——7507H; • 周期寄存器的数值决定定时器的周期,当定时器 的计数值与周期寄存器数值相等时产生周期匹配, 此时通用定时器停止操作并保持当前计数值,然

T1PIN

位

14

名称

T2STAT 定时器2状态 0 减计数 1 增计数 定时器1状态 0 减计数 1 增计数 定时器2事件启动ADC 00 不启动ADC 01 下溢中断启动ADC 10 周期中断启动ADC 11 比较中断启动ADC 定时器1事件启动ADC 00 不启动ADC 01 下溢中断启动ADC 10 周期中断启动ADC 11 比较中断启动ADC

DSP的事件管理器1

第11章事件管理器(EV)事件管理器模块为用户提供了众多的功能和特点,它们在运动控制和马达控制的应用中是特别有用的。

事件管理器模块包括通用目的(GP)定时器、全比较/PWM单元、捕捉单元和正交编码脉冲电路等。

EVA和EVB两个EV模块都是特定的外围设备,它们是为多轴运动控制应用而设计的。

每个EV都具有控制三个半高桥(three Half-H bridges)的能力,当各个桥需要互补的PWM对去控制时,EV可以提供这种能力。

每个EV还可以输出两个附加的PWM,而不是互补的PWM对输出。

11.1 事件管理器功能概述11.1.1 事件管理器功能EVA和EVB的定时器、比较单元及捕捉单元的功能是相同的。

但定时器单元的名称因为EVA和EVB而有所区别。

表11-1中列出了事件管理器模块可以被使用的功能和特点,并重点说明了EVA的命名。

事件管理器EVA和EVB 拥有功能相同的外围寄存器组。

EVA的寄存器组地址开始于7400h,EVB的寄存器组地址开始于7500h。

本章中讲述了采用EVA命名方式的GP定时器、比较单元、捕捉单元和正交编码脉冲电路(QEPs)的功能。

这些段落对于与EVB相关的器件功能同样是适用的,只是模块及信号的命名不同而已。

事件管理器(EV)的器件接口如图11-1所示。

事件管理器A(EVA)的功能模块图如图11-2所示,事件管理器B(EVB)的功能模块图与该图类似,只是模块及信号的命名有所不同。

1.通用目的(GP)定时器事件管理器各有两组GP定时器。

GP定时器x(x=1或2属于EVA;x=3或4属于EVB)包括:(1)1个16位的定时器TXCNT,为增/减计数器,TXCNT可以读/写。

(2)1个16位的定时器比较寄存器TxCMPR(带阴影的双缓冲寄存器),可以读/写。

(3)1个16位的定时器周期寄存器TxPR(带阴影的双缓冲寄存器),可以读/写。

(4)1个16位的定时器控制寄存器TxCON,可以读/写。

事件管理器EV

第12章 事件管理器EV

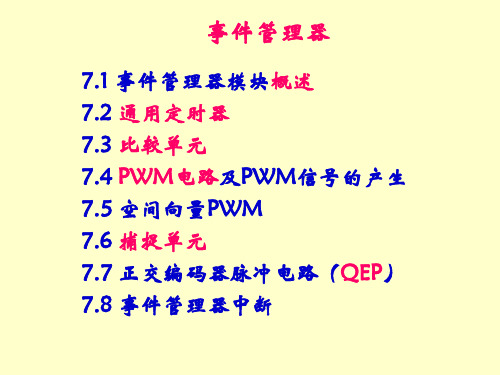

事件管理器的功能

Event Manager——EV X281x具有两个事件管理器模块——EVA和EVB 两个事件管理器模块具有完全相同的功能 EVA: 2个16位的通用定时器(通用定时器1和通用定时器2); 3个比较单元(比较单元1,比较单元2,比较单元3); 3个捕获单元(捕获单元1,捕获单元2,捕获单元3); 1个正交编码电路(QEP电路)。 EVB: 2个16位的通用定时器(通用定时器3和通用定时器4); 3个比较单元(比较单元4,比较单元5,比较单元6); 3个捕获单元(捕获单元4,捕获单元5,捕获单元6); 1个正交编码电路(QEP电路)。

T1时钟脉冲产生原理

HSPCLK TCLK= p 2

通用定时器的计数模式

四种计数模式:停止/保持、连续增、连续增/减,定向增/减 工作的模式取决于T1控制寄存器的第12位TMODE1和第11位 TMOD0

TMOD=0 定时器停止计数并保持当前状态。定时器计数器寄存 器T1CNT、比较输出T1PWM_T1CMP保持不变 TMOD=1 T1CNT先从初始值开始递增至周期寄存器的值,再递 减至零。然后从0开始递增至周期寄存器的值,接着再递减至0, 不断循环

(5)通用定时器全局控制寄存器A ——GPACONA

(6)通用定时器全局控制寄存器B——GPACONAB

比较单元与PWM电路

比较单元与PWM电路

X281x的EV提供了全比较单元和带有死区控制的PWM电路。

全比较单元

EVA具有3个全比较单元,分别是比较单元1,比较单元2,比 较单元3. 由通用定时器1提供时钟。 EVB具有3个全比较单元,分别是比较单元4,比较单元5,比 较单元6. 由通用定时器3提供时钟。 每个比较单元输出两路互补的PWM波形,也可以通过相应寄 存器设置死区时间,这样EVA和EVB都有能力驱动一个三相 全桥电路。

DSP事件管理器的学习

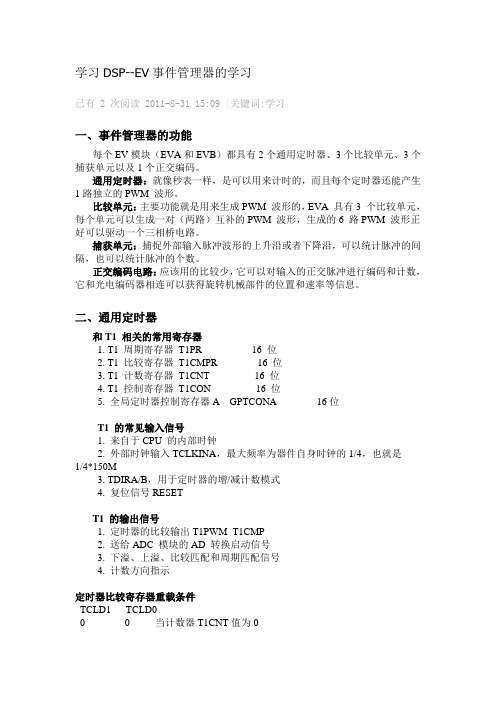

学习DSP--EV事件管理器的学习已有 2 次阅读2011-8-31 15:09|关键词:学习一、事件管理器的功能每个EV模块(EVA和EVB)都具有2个通用定时器、3个比较单元、3个捕获单元以及1个正交编码。

通用定时器:就像秒表一样,是可以用来计时的,而且每个定时器还能产生1路独立的PWM 波形。

比较单元:主要功能就是用来生成PWM 波形的,EVA 具有3 个比较单元,每个单元可以生成一对(两路)互补的PWM 波形,生成的6 路PWM 波形正好可以驱动一个三相桥电路。

捕获单元:捕捉外部输入脉冲波形的上升沿或者下降沿,可以统计脉冲的间隔,也可以统计脉冲的个数。

正交编码电路:应该用的比较少,它可以对输入的正交脉冲进行编码和计数,它和光电编码器相连可以获得旋转机械部件的位置和速率等信息。

二、通用定时器和T1 相关的常用寄存器1. T1 周期寄存器T1PR 16 位2. T1 比较寄存器T1CMPR 16 位3. T1 计数寄存器T1CNT 16 位4. T1 控制寄存器T1CON 16 位5. 全局定时器控制寄存器A GPTCONA 16位T1 的常见输入信号1. 来自于CPU 的内部时钟2. 外部时钟输入TCLKINA,最大频率为器件自身时钟的1/4,也就是1/4*150M3. TDIRA/B,用于定时器的增/减计数模式4. 复位信号RESETT1 的输出信号1. 定时器的比较输出T1PWM_T1CMP2. 送给ADC 模块的AD 转换启动信号3. 下溢、上溢、比较匹配和周期匹配信号4. 计数方向指示定时器比较寄存器重载条件TCLD1 TCLD00 0 当计数器T1CNT值为00 1 当计数器T1CNT 值为0 或者等于周期寄存器1 0 立即载入1 1 保留当某个中断的标志位被置位,如果该中断已经使能,则会向PIE模块发送中断申请。

退出中段的时候,一定要手动清除外设中断标志位。

事件除了能够产生中断以外,还能够在事件发生的时候,产生一个ADSOC 信号,就是启动AD 转换的信号,这样可以周期性的去启动AD 转换。

《dsp》事件管理器(EV

7.1.4 EV寄存器及地址 下面四个表列出EVA所有寄存器的地址,EVB的类似。

地址 7400h 7401h 7402h 7403h 7404h 7405h 7406h 7407h 7408h

EVA定时器寄存器地址

寄存器 GPTCONA T1CNT T1CMPR T1PR T1CON T2CNT T2CMPR T2PR T2CON

GP定时器2

预定标

TCLKINA CLKOUT

MUX 捕捉单元

T2CON[4,5] CLOCK T2CON[8,9,10]

TDIRA CAPCONA[14,13]

DIR

QEP

电路

CAP1/QEP1 CAP2/QEP2

CAP3

7.1.2 事件管理器引脚 事件管理器A和B的引脚描述见表7-1(P83)。 输入跳变脉冲宽度至少保持两个CPU时钟周期才能被识

PWM6

比较单元3输出2

T1CMP/T1PWM 定时器1比较/PWM输出

引脚名称

事件管理器B的引脚 描述

CAP4/QEP3 CAP5/QEP4 CAP6

捕捉单元4输入,QEP电路 输入3

捕捉单元5输入,QEP电路 输入4

捕捉单元6输入

PWM7 PWM8 PWM9 PWM10 PWM11

比较单元4输出1 比较单元4输出2 比较单元5输出1 比较单元5输出2 比较单元6输出1

数,直到定时器计数器的值和周期寄存器的值匹配 为止。产生周期匹配之后在下一个输入时钟的上升 沿,定时器复位为0 ,开始另一个计数周期。

图7-4

在产生周期匹配的下一个CPU时钟周期后,周期中断 被置位,产生一个中断请求,也可作ADC转换启动信 号。定时器变成0的一个CPU时钟周期之后,定时器 的下溢中断标志被置位,也可发出一个ADC启动信号。 定时器计数到FFFFh后,定时器的上溢中断标志在一 个CPU时钟周期之后被置位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第12章事件管理器EV(重点)

重要性:事件管理器为用户提供了众多的功能使其在电机控制、变频器、逆变器等应用场合中特别重要。

在电力电子中的应用

切断比较输出的外部控制输入、切断定时器比较输出的外部控制输入定时器的功能:1是比较功能产生pwm波、2是给事件管理器的其他模块提供基准时钟。

__PR周期寄存器、__CMPR比较寄存器、__CNT计数器

产生比较中断、中期中断等事件

重载的重要性:在需要改变pwm频率或者脉宽的时候就需要重载值

TMODE0、TMODE1

停止、保持模式(00);连续增减模式(01);连续增计数模式(10);定向增减计数模式(11)连续增减:TPR(4)01234 43210

关于ADCSOC信号的理解:应当把中断当成一个事件,并不是中断本身产生了这个信号,因为中断的产生还跟有没有屏蔽、使能等有关系。

不能认为是中断导致了信号,只能说事件导致产生了信号。

同步:通过相关寄存器的设置,T2可以使用T1的寄存器,忽略自身的寄存器,同理T1也可以用T2的,从而达到同步的目的。

定时器比较输出的极性:

GPTcona的位0、位1决定了输出高电平还是低电平或者强制高低电平。

在电力电子的应用中:定时器产生的PWM不能满足要求,因此时间管理器还提供了全比较单元和带有死区控制的PWM电路。

全比较单元:TPR CMPR

比较控制寄存器COMCONA

行为控制寄存器ACTR决定是高电平有效还是低电平有效。

最主要是其中含有可编程死区单元

产生两类中断:

比较中断、功率驱动保护中断

死区时间mpt

捕获单元

捕获单元可以测量脉冲或数字信号的宽度 估计电机的转速

正交编码电路光电编码测速

输入两路正交脉冲

1024格 4096个时钟脉冲

如何输出占空比可变的pwm波呢?关键:多设置一个变量存储累加次数。