七招教你规避嵌入式PCB工程更改

嵌入式系统程序开发注意事项

嵌入式系统程序开发注意事项嵌入式系统程序开发是一个复杂而关键的工作,要求开发人员具备深厚的技术知识和丰富的经验。

在开发嵌入式系统程序时,有几个关键的注意事项需要开发人员牢记。

本文将对这些注意事项进行详细介绍,以便开发人员在工作中能够避免一些常见的错误和问题。

1.了解硬件平台在进行嵌入式系统程序开发之前,开发人员必须对所使用的硬件平台有深入的了解。

这包括芯片架构、处理器类型、内存布局以及外设接口等。

只有全面了解硬件平台的特性,才能够更好地进行程序开发和优化。

2.合理规划系统资源嵌入式系统通常具有有限的资源,如内存、处理器速度和存储容量等。

在程序开发的初期,要合理规划和分配这些资源,以确保程序能够在资源有限的环境中高效运行。

合理利用资源亦能避免程序开发过程中的性能瓶颈和资源竞争问题。

3.选择合适的编程语言选择合适的编程语言是嵌入式系统程序开发中的重要决策之一。

针对不同的应用场景和需求,开发人员可以选择C、C++、Python等不同的编程语言。

在做出选择时,要考虑语言的性能、开发工具的支持以及团队成员的熟悉程度等因素。

4.注意内存管理由于嵌入式系统的内存资源通常受限,因此在程序开发过程中要特别注意内存管理。

避免内存泄漏、内存溢出和野指针等问题的发生,不仅可以提高程序的稳定性和可靠性,还可以节约内存资源。

使用动态内存分配时要小心,确保正确释放已分配的内存空间。

5.编写可维护和可扩展的代码嵌入式系统程序通常需要长期维护和更新,因此编写可维护和可扩展的代码至关重要。

要遵循代码规范,使用有意义的变量和函数命名,注释清晰,模块化程序结构等。

合理地分离和封装代码可以使程序更易于理解和修改,提高开发效率。

6.进行严格的测试与调试在嵌入式系统程序开发完成后,必须经过严格的测试和调试过程。

通过单元测试、集成测试和系统测试等方法,发现并修复可能存在的问题和错误。

定期将软件固件升级到最新版本,保持稳定性和兼容性。

7.设计安全性和可靠性对于嵌入式系统程序开发来说,安全性和可靠性是最重要的要求之一。

PCB板EMC整改方法讲解

电容

内存条插座电源针必须有滤波电路

• 如下图所示,因为插针会导致阻抗失配,引起电源母线上的高频阻抗存 在,所以内存条插座的电源管脚附近需要有电容滤波,

滤波电容

主板 内存条

内存插座

电源母线电感 插针电感

等效电路:

内

存

• 构成一T型滤波电路,可以有效抑制内存条的高频噪声,并且可以满足内 存条的快速电流供电。

• 走线粗细的跳变会导致信号出现阻抗失配问题,使信号波形产生 畸变,引起EMI问题;

强烈的EMI源

辐射问题总结

上述只是一些比较典型的辐射问题整改 方法及定位流程,相对来说比较有效, 但是要想彻底解决问题,还是需要在产 品的设计阶段考虑充分的EMC设计,这 样才能够预测到问题并防患于未然,特 对对于一些产品测试阶段是无法实施的 对策,例如3W原则等,必须在设计阶段 提前考虑到。

MHz

问题整改:通过在电源线上增加去耦磁环(可开合)进行验证,如 果有改善则说明和电源线有关系,采用以下整改方法:

滤波器是否良好接地

• 如果设备有一体化滤波器,检查滤波器的接地是否良好,接地线 是否尽可能短;

• 建议:金属外壳的滤波器的接地最好直接通过其外壳和地之间的 大面积搭接。

滤波器或滤波电路的输入输出是否隔离

独立窄带尖蜂噪声抑制方法

谱线问题描述:全频段内出现间隔均匀的窄带尖蜂群噪声(如下图)或单立尖蜂噪声。

166MHz over 22.84dB

问题定位:如果是均匀的窄带尖蜂群噪声,计算其间隔频率差是多少,这个频率差可 能就是其辐射源的基频;如果是单立的尖蜂噪声,则看看这个尖蜂噪声和单板上 的时钟频率是否有倍频关系。

R

R

R

晶振

GND

嵌入式系统的安全分析及对策

网络通讯及安全本栏目责任编辑:冯蕾嵌入式系统的安全分析及对策胡博,王晓平(同济大学电子与信息工程学院,上海201804)摘要:综述了产生嵌入式系统各种安全问题的瓶颈因素、根本原因,系统攻击的分类及应对具体攻击的策略。

分析了层级结构设计,使安全策略从以功能为中心的观点转向系统结构设计的角度,以更好的应对各种安全挑战。

同时介绍了几种提升嵌入式系统安全性的几种解决方案。

关键词:嵌入式系统;安全;结构设计中图分类号:TP309文献标识码:A 文章编号:1009-3044(2008)29-0295-03Embedded System Security Analysis and CountermeasureHU Bo,WANG Xiao-ping(College of Electronics &Information Engineering,Tongji University,Shanghai 201804)Abstract:Summarizes the bottlenecks,root causations which lead to security problems of embedded systems,the variety of system attacks as well as the corresponding countermeasures.Analysises the hierarchy architecture design of embedded system,moving security considera -tions from a function-centric perspective into a system architecture design issue in order to meet the various security challenge better.And introduces several solutions to improve the security of embeded system.Key words:embedded system;security;architecture design1引言普通计算机系统存在的安全问题已受到人们广泛关注,并采取了各种应对措施。

避免 pcb 设计中出现 emc 和 emi 的 9 个技巧 -回复

避免pcb 设计中出现emc 和emi 的9 个技巧-回复PCB(Printed Circuit Board)设计中,EMC(Electromagnetic Compatibility)和EMI(Electromagnetic Interference)是两个重要的考虑因素。

EMC是指电子设备在同一环境下,互相之间不会对彼此的正常工作产生负面影响的能力。

而EMI则是指电子设备在工作时,产生的电磁辐射对周围的其他电子设备和系统产生的有害影响。

为了确保PCB设计不会出现EMC和EMI问题,以下是9个技巧供设计工程师参考:1. 分层设计:将电路板的信号层、地层和电源层进行合理的分层设计,可以有效地减小信号之间的干扰,并降低电磁辐射的水平。

信号和电源层之间应确保有足够的地层以提供良好的屏蔽效果。

2. 阻抗匹配:在设计信号线路时,要注意保持合适的阻抗匹配。

通过匹配信号线和驱动电路的阻抗,可以减小信号的反射和干扰,降低电磁辐射。

3. 使用电磁屏蔽材料:在设计中使用电磁屏蔽材料可以有效地抑制电磁辐射和吸收外部的电磁干扰。

常见的电磁屏蔽材料包括电磁屏蔽膜和金属屏蔽箱等。

4. 地线设计:合理的地线设计可以减小电磁辐射,降低EMI问题的发生。

在设计过程中要确保地线的连通性好,并且尽量避免共地引发的回流路径问题。

5. 电源滤波设计:在电源输入和输出端添加适当的滤波电路,可以有效地限制电磁干扰的传播和扩散,提高抗干扰能力。

滤波电路可以包括电容、电感和滤波器等元件。

6. 合理布局:合理的布局可以减小信号回流路径的长度,降低电磁辐射的水平。

将高频和低频信号线路进行分离布局,并减小信号线与电源线和地线之间的交叉干扰,可以有效地减小EMC和EMI问题。

7. 防护接地:在设计中要合理设置防护接地,确保各个部分之间的接地电位相同,并保证接地回路的连续性。

防护接地可以有效地降低EMI问题,提高系统的电磁兼容性。

8. 外部电磁屏蔽:在设计中可以考虑添加外部电磁屏蔽,如金属屏蔽罩或金属屏蔽网格等。

如何消除PCB设计中的干扰

环测威官网:/随着信息技术的不断发展,电子产品在功能,类别和结构方面变得越来越复杂,朝着多层方向和高密度方向推动PCB设计。

因此,必须对PCB设计的EMC(电磁兼容性)给予很多关注,因为PCB的EMC设计不仅可以确保板上所有电路的正常和稳定工作,因此它们不会相互干扰。

还有效地减少了辐射传输和PCB的传导发射,以阻止电路受到外部辐射和传导的干扰。

干扰是EMC最重要的敌人。

但是,工程师,你应该不要担心这篇文章了。

PCB干扰的分类PCB干扰可分为三类:1)。

布局干扰是指由于PCB上不适当的元件放置而引起的干扰。

2)。

堆叠干扰是指由不科学的设置引起的噪声干扰。

3)。

路由干扰是指PCB信号线,电源线和接地线之间距离设置不当,线宽或不科学的PCB 布线方法造成的干扰。

在PCB干扰分类方面,可以从布局规则,堆叠策略和布线规则的角度分别采取一些抑制措施,减少甚至消除PCB干扰的影响,以确保与EMC设计标准的兼容性。

基于分类的PCB干扰相应抑制措施•布局干扰的抑制措施停止布局干扰的特权在于合理的PCB布局,应符合以下六条规则:1)。

每个功能模块的电路位置应根据信号电流位置合理设定,其流向应保持尽可能相同。

2)。

模块电路中的核心部件应设置在中心位置,并且应尽可能缩短元件之间的引线,特别是高频元件。

3)。

热敏元件和芯片之间的集成应远离加热元件。

4)。

连接器位置应根据板上的元件位置确定。

连接器应放置在PCB的一侧,以阻止电缆从两侧引出,并减少共模(CM)电流辐射。

5)。

I / O驱动器应紧密靠近连接器,以阻止板上I / O信号的长距离路由。

6)。

热敏元件不能彼此靠得太近,输入和输出元件也应远离它们。

•抑制堆叠干扰的措施首先,PCB设计信息应该通过考虑的综合元素来控制,包括信号线密度,功率和接地分类,以确定功率和确保实现电路功能的层数。

堆叠策略的质量基本上与地平面或电源平面的瞬态电压以及电源和信号的电磁屏蔽相关。

根据实际的堆叠设计经验,堆叠设计应符合以下规则:1)。

嵌入式系统面临的安全问题及解决措施

对于此类破坏 , 连接 网络 的计 算机所遭受到 的损 失

比嵌入式系统更严重 , 但随着嵌入 式系统应用 的越来 越 广泛 , 嵌入式设备 的许多功 能要 直接联 网或 间接联 网才 能实现或更好地发挥 ,设备 可以作为数据传输 的通 道 ,

也可 以是数 据传 输 的起 点端 或终 点端 。传输环 节上 的 任何 一个 节 点 出现 问题 , 都可 能导 致整 个传 输 错误 或

析, 否则也会造成误差 。 鉴于两者 的局 限性 , 大规模 应用是不 可能的 。但一 旦发生此类破坏 , 就会造成严重 的损失 。目前 , 芯 片的来

别 是蠕 虫和木 马 , 依赖 网络传 播 , 其次 是 U盘 , 再 次是 光盘 。网络 的传播 速度最 快 , 随着 I N T E R N E T的 日益普

虫是 自包含 的程序 , 能传播 自身功能或部分功能 到其它

非侵入式是指保 留芯片封装 , 利用芯片在运 行过程

中泄露出的物理信息进行破坏 , 也称边频攻击 。非侵人

式破 坏是利用 了芯片 的功耗 、电磁辐射等物理 特性 , 猜 测系统 中的秘密信息 ,其代 表性 的方式是 差分 功耗分

操作 系统 中, 通 常利用 网络复 制和传 播 , 消耗 系统 资源 并破 坏重要数 据 ; 木 马与一般 的病毒 不 同 , 它不会 自我

嵌入式系统面临的安全问题及解决措施

电子质量 ( 2 0 1 4 第1 2 期)

当昂贵 , 且 每次 只针对 一块芯 片 ; 其次 是芯 片在运行 过

程 中的状态不可预知 。

要是病毒 、 蠕虫和木 马等 。 病毒具 有非授 权可执行性 、 隐 蔽性 、 破 坏性 、 传 染性 、 可触发 性 , 能通 过很 多途径潜 伏 在系统 的存储介质或程序 中,对 用户的危害性很 大 ; 蠕

嵌入式系统开发中的常见问题与解决方法

嵌入式系统开发中的常见问题与解决方法对于嵌入式系统开发工程师来说,解决开发中的问题是日常工作的一部分。

在这篇文章中,我将探讨开发嵌入式系统时常见的一些问题,并提供解决方案。

1. 电源问题一个嵌入式系统必须使用稳定可靠的电源。

在一些设计中,可能会出现电源质量不稳定的问题,这会导致系统的稳定性和可靠性受损。

在处理这个问题时,需要使用电压稳压器或电源滤波器来解决电压扰动的问题。

此外,对于要求高电源容量的设备,还可以使用双电源来确保稳定供电。

2. 内存问题内存管理是嵌入式系统开发中一个极其重要的问题。

内存不足或内存管理不当可能导致系统性能下降、甚至死机。

因此,要采取有效的措施来管理内存,例如使用内存池(即预先分配一定数量的固定大小内存块)以减少内存分配和释放的时间开销。

此外,对于某些需要大量操作大内存的应用程序,还可以建立虚拟内存或采用分布式内存的方式来提升系统处理速度。

3. 时序问题在嵌入式系统的设计中,时序是一个不可避免的问题。

时序问题是指系统中信号传输速度、时钟频率、数据总线宽度、各种射频信号的时间同步等问题。

解决时序问题的方法是通过芯片设计和编程实现系统的精确定时。

通常采用的是硬件时序控制电路、时钟同步电路和软件时序控制的方法等。

4. 中断问题中断是嵌入式系统中常见的事件触发机制。

在一些设计中,可能会出现中断处理不及时、丢失中断的情况,导致系统出现紊乱。

解决中断问题的关键是处理中断过程。

中断处理过程应该尽可能简单、高效、可重入,不应该占用过多的系统资源。

因此,在设计中需要考虑中断的优先级、中断向量的管理和中断处理程序等问题。

5. 软件问题在嵌入式系统开发中,软件问题也是一个非常常见的问题。

软件问题可以包括软件编程错误、编程过程中的缺陷、软件低效等。

解决软件问题的方法是通过使用软件调试工具来进行软件测试与分析,以便在开发初期即发现软件问题和缺陷。

此外,为了避免软件开发中的常见错误而导致的严重问题,在开发过程中需要加强反思和代码审查,同时加强对每个模块的单元测试、模块集成测试以及系统测试等。

深入探讨各种PCB设计疏忽及应对策略

深入探讨各种PCB设计疏忽及应对策略技术分类:EDA工具与服务 | 2011-08-24Maxim射频印制板(PCB)布局很容易出现各种缺陷工业、科学和医疗射频(ISM-RF)产品的无数应用案例表明,这些产品的印制板(PCB)布局很容易出现各种缺陷。

人们时常发现相同IC安装到两块不同电路板上,所表现的性能指标会有显著差异。

工作条件、谐波辐射、抗干扰能力,以及启动时间等等诸多因素的变化,都能说明电路板布局在一款成功设计中的重要性。

本文罗列了各种不同的设计疏忽,探讨了每种失误导致电路故障的原因,并给出了如何避免这些设计缺陷的建议。

本文以FR-4电介质、厚度0.0625in的双层PCB为例,电路板底层接地。

工作频率介于315MHz到915MHz之间的不同频段,Tx和Rx功率介于-120dBm至+13dBm之间。

表1列出了一些可能出现的PCB布局问题、原因及其影响。

其中大多数问题源于少数几个常见原因,我们将对此逐一讨论。

电感方向当两个电感(甚至是两条PCB走线)彼此靠近时,将会产生互感。

第一个电路中的电流所产生的磁场会对第二个电路中的电流产生激励(图1)。

这一过程与变压器初级、次级线圈之间的相互影响类似。

当两个电流通过磁场相互作用时,所产生的电压由互感LM决定:式中,YB是向电路B注入的误差电压,IA是在电路A作用的电流1。

LM对电路间距、电感环路面积(即磁通量)以及环路方向非常敏感。

因此,紧凑的电路布局和降低耦合之间的最佳平衡是正确排列所有电感的方向。

图1.由磁力线可以看出互感与电感排列方向有关对电路B的方向进行调整,使其电流环路平行于电路A的磁力线。

为达到这一目的,尽量使电感互相垂直,请参考低功率FSK超外差接收机评估(EV)板(MAX7042EVKIT)的电路布局(图2)。

该电路板上的三个电感(L3、L1和L2)距离非常近,将其方向排列为0°、45°和90°,有助于降低彼此之间的互感。

电路板(PCB)制造出现各种问题及改善方法

电路板(PCB)制造出现各种问题及改善方法(一)一、电路板工程设计制作1.1CAM制作的基本步骤每一个PCB 板基本上都是由孔径孔位层、DRILL 层、线路层、阻焊层、字符层所组成的,在CAM350 中,每载入一层都会以不同的颜色区分开,以便于我们操作。

1.1.导入文件首先自动导入文件(File-->Import-->Autoimport),检查资料是否齐全,对齐各层(Edit-->Layers-->Align)并设定原点位置(Edit-->Change-->Origin-->Datum Coordinate),按一定的顺序进行层排列(Edit-->Layers-->Reorder),将没用的层删除(Edit-->Layers-->Reorder)。

1.2.处理钻孔当客户没有提供钻孔文件时,可以用孔径孔位转成Flash(Utilities-->Draw-->Custom,Utilities-->Draw-->Flash-->Interactive)后再转成钻孔(钻孔编辑状态下,Utilities-->Gerber to Drill);如果有提供钻孔文件则直接按制作要求加大。

接着检查最小钻孔孔径规格、孔边与孔边(或槽孔)最小间距(Analysis-->Check Drill)、孔边与成型边最小距离(Info-->Measure-->Object-Object)是否满足制程能力。

1.3.线路处理首先测量最小线径、线距(Analysis-->DRC),看其是否满足制程能力。

接着根据PC 板类型和基板的铜箔厚度进行线径补偿(Edit-->Change-->Dcode),检查线路PAD 相对于钻孔有无偏移(如果PAD 有偏,用Edit-->Layers-->Snap Pad to Drill 命令;如果钻孔有偏,则用Edit-->Layers-->Snap Drill to Pad 命令),线路PAD 的Ring 是否够大(Analysis-->DRC),线路与NPTH 孔边、槽边、成型边距离是否满足制作要求。

嵌入式系统的电路板布线优化方法

嵌入式系统的电路板布线优化方法在嵌入式系统的设计中,电路板的布线是至关重要的一步。

电路板布线的优化能够提高系统的性能和可靠性,并减少电磁干扰和信号噪声。

本文将介绍几种常用的电路板布线优化方法,以帮助设计师们在嵌入式系统设计过程中达到更好的效果。

首先,合理划分电路板的区域是电路板布线优化的重要一步。

根据电路板上的功能模块和器件,将板上的元件划分为几个不同的区域,可以减少信号之间的干扰,提高系统的可靠性。

同时,合理划分区域还有助于简化布线路径,并减少信号通过长距离传输导致的信号衰减。

其次,考虑信号走线的路径是电路板布线的关键。

布线时应尽量避免信号线的交叉和平行走线,以减少电磁干扰。

当信号线交叉时,会导致信号互相干扰,从而影响系统的性能。

而平行走线容易引起电磁辐射,并增加信号互相干扰的可能性。

因此,在布线过程中,应尽量使信号线远离彼此,并采用十字走线的方式,尽量减少信号线的交叉。

另外,将电源和地线布线与信号走线分离是布线优化中的一个重要策略。

电源和地线往往具有较高的电流,它们会在传输过程中产生较强的电磁干扰。

为了减少这种干扰对信号的影响,布线时应将电源和地线与信号走线分开布置。

可以通过设置地面位于电路板的中心位置,然后将信号层放置在地面层的上方,电源和地线层放置在地面层的下方,这样能有效地减少电源和地线对信号的干扰。

此外,合理的走线方式和长度匹配也是电路板布线优化的重要考虑因素。

布线时应尽量保持走线路径的均匀和对称,以减少信号路径的不对称性带来的差异。

同时,对于差分信号线,走线时应尽量保持两条线的长度相等,以避免差异延迟对信号的影响。

最后,进行合理的层间连接和引脚指派可以进一步优化电路板布线。

在布线过程中,应尽量将连接件放置在电路板的一个特定区域,并通过层间连接来减少信号线的走线长度。

同时,在指定引脚的位置时,应尽量减少引脚之间的距离,并确保引脚与其所连接元件之间的最短路径,以降低电路板的复杂度和布线的复杂度。

多层齐平印制电路板的嵌入式元件布局优化

多层齐平印制电路板的嵌入式元件布局优化嵌入式元件的布局对于多层齐平印制电路板(PCB)的设计非常重要。

优化嵌入式元件的布局可以提高电路板的性能、可靠性和生产效率。

本文将介绍多层齐平印制电路板的嵌入式元件布局优化的几个关键方面,包括元件位置、信号完整性和热管理。

首先,讨论元件位置的优化。

在进行嵌入式元件布局时,应尽量将功能相关的元件放置在靠近一起的位置,以减少信号传输的路径长度,降低信号损耗和干扰。

对于高速信号传输线路,布局时需要避免信号线和噪声源之间的交叉,以减少互相干扰。

此外,对于复杂的电路板布局,可以使用模块化的设计方法,将电路板分为若干个模块,每个模块内部进行布局和连接,然后再将模块进行整体布局。

这种模块化的设计方法有助于提高电路板的可维护性和可升级性。

其次,考虑信号完整性的优化。

在高速信号传输中,信号完整性对系统性能至关重要。

为了确保信号的完整性,应避免信号线的走线过长、过窄,尽量保持信号线的宽度和间距符合设计规范。

此外,可以采用差分信号线对进行信号传输,差分信号线对可以降低信号干扰和噪声。

对于高速信号线,还可以采用阻抗匹配技术,将信号线的阻抗与驱动源和负载的阻抗匹配,减少信号的反射和损耗。

同时,在布局中应尽量减少信号线的弯曲和交叉,以降低信号的串扰和干扰。

最后,要考虑热管理的优化。

在高密度的多层齐平印制电路板设计中,热量的产生和分散是一个重要的问题。

过高的温度可能导致电路性能退化、元件寿命减少甚至故障。

为了进行热管理的优化,可以采用以下几个方法。

首先,合理布局元件,避免元件之间过于紧密,以保证充足的空气流通。

其次,根据元件的功耗和发热特性,合理分布热量,避免热点集中在局部区域。

此外,可以使用散热片、散热模块等辅助散热装置,增加热量的传导和散发。

对于一些特定的高功耗元件,还可以采用主动散热技术,如风扇、热管等设备。

在进行多层齐平印制电路板的嵌入式元件布局优化时,还需要考虑制造工艺和成本等因素。

pcb电路移植注意事项

pcb电路移植注意事项PCB电路移植是指将一个电路设计从一个PCB板上移植到另一个PCB板上的过程。

在进行PCB电路移植时,需要注意以下几个方面:1. PCB板尺寸和布局:在进行电路移植时,首先需要确保目标PCB板的尺寸和布局与原始PCB板相匹配。

如果目标PCB板的尺寸较小,可能需要重新布局电路元件和走线,以确保电路的正常工作。

2. 元件选型和替代:在进行电路移植时,可能会遇到原始PCB板上使用的元件在目标PCB板上无法获得的情况。

在这种情况下,需要仔细选择合适的替代元件,并进行相应的电路调整和测试,以确保电路的性能和稳定性。

3. 电源和地线:在进行电路移植时,需要特别注意电源和地线的连接。

确保电源和地线的连接正确可靠,以避免电路工作不稳定或损坏。

4. 信号完整性:在进行电路移植时,需要特别关注信号完整性。

确保信号线的长度和走线路径符合设计要求,避免信号受到干扰或衰减。

5. 电磁兼容性:在进行电路移植时,需要考虑电磁兼容性。

确保电路布局和走线符合电磁兼容性的要求,避免电磁干扰对电路性能的影响。

6. 热管理:在进行电路移植时,需要考虑热管理。

确保电路元件的散热条件良好,避免过热对电路性能的影响。

7. 电路测试和验证:在进行电路移植后,需要进行电路测试和验证,以确保电路的正常工作。

可以使用示波器、逻辑分析仪等测试设备对电路进行测试,验证电路的性能和稳定性。

8. 文件和文档更新:在进行电路移植后,需要及时更新相关的文件和文档,包括电路图、PCB布局图、元件清单等。

这样可以方便后续的维护和修改工作。

9. 注意电路的保密性:在进行电路移植时,需要注意电路的保密性。

确保电路设计和相关信息不被未经授权的人员获取和使用。

总之,进行PCB电路移植时,需要仔细考虑各个方面的问题,并进行相应的调整和测试,以确保电路的正常工作。

同时,还需要注意保密性和文件更新等问题,以便后续的维护和修改工作。

处理PCB时建议使用的几种预防措施 附处理和存储柔性电路板时的重要预防措施

在使用电路板时采取适当的处理预防措施的非常重要。

如果没有采取适当的措施可能会导致电路板意外损坏。

采取适当的预防措施不仅对于组件很重要,对于整个电路板也是一样的。

在处理PCBA时如果不采取预防措施很有可能会使电路板损坏从而无法使用。

如果情况不是很严重,可以采取一些措施补救一下。

例如,PCB板只是受潮导致无法使用,则可以通过烘烤进行修复。

当然,PCB防潮只是维护PCB需要采取的多种措施之一。

为了防止电路板过早损坏,还应该了解各种不同的PCB处理预防措施,并将其用于电路板的制造,生产和存储。

开发、生产和存储PCB的注意事项PCBA的发展是提高质量的迭代过程。

这个过程最需要注意的是研发速度(在短时间内研发出高质量的电路板)和灵活性(并行设计)。

但是,只有在整个制造、生产和存储阶段正确处理电路板,才能得到最好的研发成果,因此,开发、生产和存储中需要注意以下问题。

Ol开发过程中需要注意的要点研发避免将铜迹线暴露在空气中如果电路板的铜走线暴露于空气中,尤其是制造和组装之间有较长的时间间隔时,它们可能会被氧化污染。

避免这种情况的最好方法是在制造过程中尽量的让表面光洁。

避免杂物残留在PCB组装(PCBA)期间,可能会有碎屑堆积在板上。

由于碎屑较小,可能很难被发现。

因此,最好使用光学检查并在组装完成后清洁电路板。

避免过大的压力手动搬运电路板时,需要避免对电路板施加过大的压力,过大的压力可能会导致电路板变形或破裂,从而影响电路板结构的完整性。

磨损防护在手动处理板时,也可能会沉积污染物。

这包括灰尘,汗水等。

所以,应该在处理时注意戴上手套。

测试使用工具要谨慎在电路板上工作时,一定要小心。

对小型板来说,这点非常重要,如果不小心可能会造成很大的损害,因此使用适当的工具至关重要。

注意防潮如果电路板表面与其周围环境之间的温差太大,则可能会让电路板变得潮湿,从而影响测试时的准确性。

所以应该注意在通风的环境下进行测试,并控制测试环境的温度来避免这种情况。

工程师福利:3招有效规避PCB设计风险

工程师福利:3招有效规避PCB设计风险

PCB设计过程中,如果能提前预知可能的风险,提前进行规避,PCB 设计成功率会大幅度提高。

很多公司评估项目的时候会有一个PCB设计一板成功率的指标。

提高一板成功率关键就在于信号完整性设计。

下面就随嵌入式小编一起来了解一下相关内容吧。

目前的电子系统设计,有很多产品方案,芯片厂商都已经做好了,包括使用什么芯片,外围电路怎么搭建等等。

硬件工程师很多时候几乎不需要考虑电路原理的问题,只需要自己把PCB做出来就可以了。

但正是在PCB设计过程中,很多企业遇到了难题,要么PCB设计出来不稳定,要么不工作。

对于大型企业,芯片厂商很多都会提供技术支持,对PCB设计进行指导。

但一些中小企业却很难得到这方面的支持。

因此,必须想办法自己完成,于是产生了众多的问题,可能需要打好几版,调试很长时间。

其实如果了解系统的设计方法,这些完全可以避免。

接下来我们就来谈谈降低PCB设计风险的三点技巧。

第1、系统规划阶段最好就考虑信号完整性问题,整个系统这样搭建,信号从一块PCB传到另一块PCB能不能正确接收?这在前期就要评估,而评估这个问题其实并不是很难,懂一点信号完整性知识,会一点简单的软件操作就能做到。

第2、在PCB设计过程中,使用仿真软件评估具体走线,观察信号质量能不能满足要求,这个仿真过程本身非常简单,关键是要理解信号完整性的原理知识,并用来指导。

第3、做PCB的过程中,一定要进行风险控制。

有不少问题,目前仿真软件还没有办法解决,必须设计者人为控制。

这一步关键是了解哪些地方会有。

PCB常见问题的预防

板弯板曲

因铜箔与纤维布的澎胀系数不同而引起

开料后一定要进行120ºC 4小时的烤板,驱除潮气,使板材的尺寸稳定性得到进一步的加强;由经验丰富的工程师根据制程情况及Gerber资料进行合理的生产资料设计,如倒扣排版和阴阳排版,尽可能使两面的铜面积趋于平衡,减少因澎胀系数不同而导致的板弯板曲;对多层板则要求使用同一厂家的PP片及芯板,并使其经纬向保持一致;最后在包装前进行一次快速压板,使板弯板曲在要求范围内.同时我司将按IPC-A-600G Class II的相关标准进行板弯板曲全检控制(针规及平整大理石台面,取弯曲最大值与对角线的比值),达标的板才可以送下工序,否则送MRB申请报废处理.

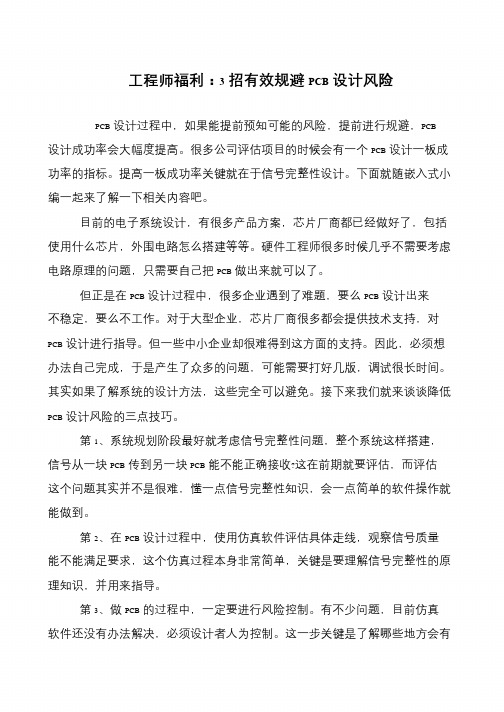

PCB常见问题的解决办法

序号

常见问题

Common quality problem

主要原因

Cause

预防和解决的办法

Precaution and solution

1

孔铜不够

Insufficient copper in hole

药水均镀能力不达标或是电镀时间及电流值没调控到要求值

Electrolyte concentration or its plating ability iቤተ መጻሕፍቲ ባይዱ not up to required level.

8

绿油脱落或起泡

板面不干净或油墨固化不足

(铜表面氧化,污染,导致板面清洗不净或不干燥,有水汽)加强磨板清洗及前处理后的彻底烘干;严格控制固化时间,温度,并检查烘箱热量均匀度.目视如有绿油脱落或起泡,则要分析原因后进行补油或返工处理.

兰胶厚度不足或本身不耐高温而被灼焦

根据我司长期的生产实践,我司全部使用Peters系列兰胶,并使用铝片网印制,确保兰胶厚度在0.3-0.5mm,十分有效地避免这类现象.

如何防止别人抄你的PCB板?

如何防止别人抄你的PCB板?

今天看了篇《如何抄板》,现在来谈谈“如何防止抄板”:

1、磨片,用细砂纸将芯片上的型号磨掉.对于偏门的芯片比较管用;

2、封胶,用那种凝固后成固体的胶,将PCB及其上的元件全部覆盖.里面还可故意搞五六根飞线(用细细的漆包线最好)拧在一起,使得抄板者拆胶的过程必然会弄断飞线而不知如何连接.要注意的是胶不能有腐蚀性,封闭区域发热量小;

3、使用专用加密芯片;

4、使用不可破解的芯片,但有成本付出;

5、使用MASK IC,一般来说MASK IC要比可编程芯片难破解得多;MASK(掩膜):单片机掩膜是指程序数据已经做成光刻版,在单片机生产的过程中把程序做进去。

优点是:程序可靠、成本低。

缺点:批量要求大,每次修改程序就需要重新做光刻板,不同程序不能同时生产,供货周期长。

6、使用裸片,小偷们看不出型号也不知道接线.但芯片的功能不要太容易猜,最好在那团黑胶里再装点别的东西,如小IC、电阻等;

7、在电流不大的信号线上串联60欧姆以上的电阻(让万用表的通断档不响);

8、多用一些无字(或只有些代号)的小元件参与信号的处理,如小贴片电容、TO-XX的二极管、三极管、三到六个脚的小芯片等;

9、将一些地址、数据线交叉(除RAM外,软件里再换回来);

10、PCB采用埋孔和盲孔技术,使过孔藏在板内.此方法成本较高,只适用于高端产品,增加抄板难度;

11、使用其它专用定制的配套件;

12、申请专利,鉴于知识产权保护的环境太差,国外最优选的方法在咱们这只能放在最后一条。

最后说一点,任何措施都是只能延迟作案时间,不能杜绝被抄板。

只有找到自身的绝对优势,形成技术断裂点,能够勇敢的开源,才能做成像谷歌这样伟大的公司。

避免PCB设计陷阱的小妙招

避免PCB设计陷阱的小妙招

1 元件选择与布局

每个元件的规格都不一样,即使同一产品不同厂商生产的元件特性也可能不一样,所以在设计时对于元器件的选择,必须要与供应商联系以了解元件的特性,并且知道这些特性对设计的影响。

在现今,选择合适的内存对于电子产品设计来说也是件非常重要的事情,由于DRAM 和Flash 存储器不断的更新,PCB 的设计者要想新的设计不受外界不断变化的内存市场对其的影响是一个很大的挑战。

现在DDR3 占领当前DRAM 市场的85%-90%,但是在2014 年预计DDR4 将从12%上升至56%。

所以设计者必须瞄紧内存市场,与制造商保持紧密的联系。

元器件过热烧毁

另外对于一些散热量大的元器件必须进行必要的计算,他们的布局也需要特别考虑,大量的元器件在一起时能产生更多的热量,从而引起阻焊层变形分离,甚至引燃整个板子。

所以设计和布局工程师必须一起工作,保证元件有合适的布局。

布局时首先要考虑PCB 尺寸大小。

PCB 尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增加;过小,则散热不好,且邻近线条易受干扰。

在确定PCB 尺寸后,再确定特殊元件的位置。

最后,根据电路的功能单元,对电路的全部元器件进行布局。

2 散热系统

散热系统的设计包括冷却方法和散热元器件选择,以及对冷膨胀系数的考虑。

目前PCB 散热采用的主要有通过PCB 板本身散热,加散热器和导热板等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

七招教你规避嵌入式PCB工程更改

工程更改(ECO)将推高设计成本,造成产品开发大量延迟,进而延迟产品上市时间。

然而,通过认真思考经常发生问题的七大关键领域,可以规避大多数ECO。

这七大领域是:元器件选择,存储器,湿度敏感等级(MSL),可测性设计(DFT),冷却技术,散热器以及热膨胀系数(CTE)。

元器件选择

为了规避ECO,全面通读元器件规格书很重要。

PCB设计师一般都会例行检查元器件的电气和工程数据以及产品寿命和可用性。

但当元器件处于市场推广的早期阶段,数据手册上可能还没有全部的关键指标。

如果元器件上市才几个月,或者只能提供小批量样品,那么当前可获得的可靠性数据可能没有普遍性,或不够详细。

举例来说,最终可能无法提供足够多的可靠性数据,或有关现场失效率的质量保证数据。

不要轻信规格书中写的表面文章很重要,而是要积极联系元器件供应商,尽可能多地了解元器件的特性以及如何将这些特性应用于设计。

元件需要处理的最大期望电流或电压就是一个很好的例子。

如果所选的元件不能处理足够的电流或电压,那么元件很可能烧坏。

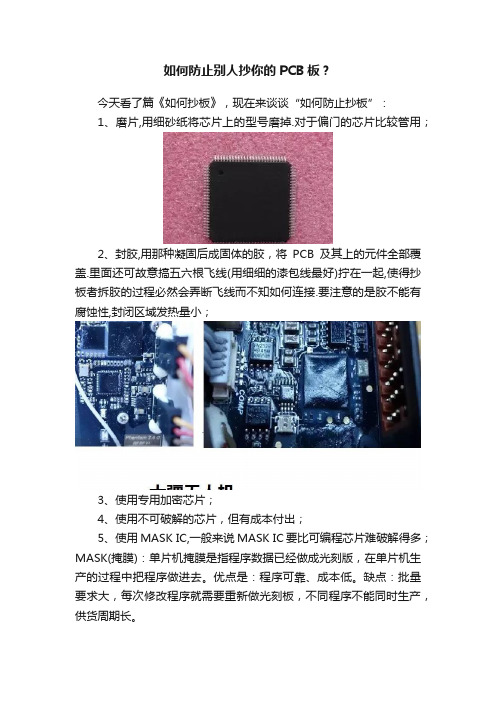

图1显示的是一个烧坏了的电容。

图1:由于元件选择不当致使电路中流过相当大的电流或电压将有可能发生像这个烧过的电容这样的损坏。

让我们看另外一个例子--栅格阵列(LGA)封装的器件。

除了电气和机械约束外,你可能需要考虑推荐的助焊剂类型、允许或不允许的回流焊温度以及允许的焊点空洞等级。

目前还没有专门与LGA器件相关的空洞方面的IPC标准。

目前在一些情况下,空洞等级最高为30%的LGA器件被认为是可靠的。

然而一般来说,最大为25%的较低空洞等级更好,20%最好了。

图2显示了空洞等级为20.41%的焊球,这是IPCClassII标准能够接受的。