第5章 DSP系统设计

第5讲 通用IO口(xkj201611)4

数字I/O端口模块通过64个16位寄存器来设置所有I/O引脚的功能 这些寄存器大概可以分为以下六类

-复用控制寄存器GPxMUX,确定I/O引脚为基本功能,还是 通用I/O功能引脚

- 方向控制寄存器GPxDIR-用来控制I/O引脚的数据方向 -数据寄存器GPxDAT-用来控制I/O引脚的数据 - 设置寄存器GPxSET-用来设置输出引脚的数据(高电平有效) - 清除寄存器GPxCLEAR-用来清除输出引脚的数据(高电平有效) -切换寄存器GPxTOGGLE-用来切换输出引脚的数据(高电平有效) LOGO

no qualification (SYNC to SYSCLKOUT) QUALPRD = SYSCLKOUT/2 QUALPRD . = SYSCLKOUT/4 . QUALPRD = SYSCLKOUT/510

. .

. .

C28x GPIO MUX/DIR Registers

Address 70C0h 70C1h 70C2h 70C4h 70C5h 70C6h 70CCh 70CDh 70CEh 70D0h 70D1h 70D2h 70D4h 70D5h 70D8h 70D9h Register GPAMUX GPADIR GPAQUAL GPBMUX GPBDIR GPBQUAL GPDMUX GPDDIR GPDQUAL GPEMUX GPEDIR GPEQUAL GPFMUX GPFDIR GPGMUX GPGDIR Name GPIO A Mux Control Register GPIO A Direction Control Register GPIO A Input Qualification Control Register GPIO B Mux Control Register GPIO B Direction Control Register GPIO B Input Qualification Control Register GPIO D Mux Control Register GPIO D Direction Control Register GPIO D Input Qualification Control Register GPIO E Mux Control Register GPIO E Direction Control Register GPIO E Input Qualification Control Register GPIO F Mux Control Register GPIO F Direction Control Register GPIO G Mux Control Register GPIO G Direction Control Register

DSP第5章-F28335-概述

外设总线: 用于外设互联,复用多种总线。

5.3.3 外设

1. ePWM:6个,可单独控制各个引脚,功能更强大 2.eCAP:6个 3.eQEP:2个,测速更加方便 4.ADC:12位,16路,80ns转换时间 5.Watchdog Timer:1个 6.McBSP:2个,用于连接高速外设,如音频处理模块 7.SPI:1个,连接具有SPI借口的外设

得益于F28335浮点运算单元,从而简化软件开发,缩 短开发周期,降低开发成本。

5.1 F28335的性能

高性能静态CMOS技术:主频150MHZ,指令周期6.67ns; 低功

耗设计,1.9V/1.8V内核电压,3.3VI/O引脚电压;Flash编 程电压为3.3V

高性能32位CPU:IEEE-754单精度浮点运算单元(FPU) ;

3个32位CPU定时器:定时器0、1、2。T0、T1为一般定时器 ,T0连接至PIE,T1连接至中断INT13,T2用作DSP/BIOS的

5.1 F28335的性能

串行端口外设:2个eCAN2.0B; 3个SCI(UART);2个 McBSP;1个SPI; 1个I2C总线接口。

16通道12位模数转换模块:转换时间80ns,2X8通道复用输入 接口;2个采样保持电路;单/连续通道转换;内部或外部参考电 压

▪32位定点CPU架构,支持16位和32位指令操作。前者减 少存储,提高代码密度。后者加快指令执行时间。 ▪32位IEEE-754单精度FPU,具有高效C/C++引擎,可使 用高级语言编程。 ▪32X32位MAC64位处理能力。 ▪快速中断响应。 ▪“原子指令”读写简化机制。执行更快,代码更少。

DSP原理及应用-绪论

1982年问世的第一个定点DSP芯片是TMS320C10 同一代TMS320系列DSP产品的CPU结构是相同的, 但片内存储器及外设电路的配置不一定相同

15

TI的三大主力芯片

TMS320C2000系列 用于数字控制系统 TMS320C5000系列 用于低功耗、便携的无线通信终端产品 TMS320C6000系列

2

要求:

不迟到、不早退、更不能无故旷课 按时完成作业,决不容许抄袭现象

课堂上积极回答问题,积极参与讨论

3Leabharlann 第1章 绪论1.1 数字信号处理概述

4

数字信号处理:滤波、参数提取、频谱分析、压缩等

Digital Signal Processing 广义理解 DSP Digital Signal Processor 狭义理解

美国Inmos公司的:IMSA100卷积/相关器

14

TMS320 DSP芯片(通用型)

定点型

TMS320C1x、 TMS320C2x、 TMS320C2xx、 TMS320C5x、 、 TMS320C54x、 TMS320C62x

浮点型

TMS320C3x、 TMS320C4x、 TMS320C67x

外部可扩展的程序和数据空间,总线接口,I/O接口等。

不同的DSP芯片所提供的硬件资源是不相同的,应根据系统的 实际需要,考虑芯片的硬件资源。

27

4.DSP芯片的运算精度

运算精度取决于DSP芯片的字长。定点DSP芯片的字长通常

为16位和24位。浮点DSP芯片的字长一般为32位。

5.DSP芯片的开发工具 快捷、方便的开发工具和完善的软件支持是开发大型、复杂 DSP应用系统的必备条件。

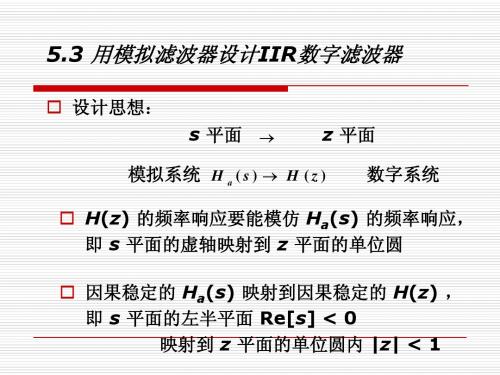

DSP5第五章IIRDF的设计方法

其中:Ha(s)是模拟滤波器的系统函数。 • 假 设p1, z1为Ha(s) 的一个零点和一个极点,则-p1, -z1

必为Ha(-s)的一个零点和极点,Ha(s)、Ha(-s)的零极点 成象限对称分布。所以必然有如下形式: zpA 11 2 ( * ) *H a --( zps 11) H a ( s )s j k 2 ( ( 2 2 z p 1 2 1 ) 2 ) 2 ( 2 ( z 2 2 p ) 2 2 ) ( ( 2 2 z N 2 p ) m 2 )

1、低通滤波器的性能指标

|H(ejw)|或|H(f)

1

Ap

1-δ1

δ2 fp fs wp ws

δ1:通带的容限

δ2:阻带容限

通带截止频率:fp(wp)又称 为通带上限频率。

通带衰减:Ap

As f

阻带截止频率:fp(ws)又称 阻带下限截止频率。

w

阻带衰减:As

2、高通滤波器的性能指标

|H(ejw)|或|H(f) Ap 1

• 根 据 给 定 设 计 要 求, 把 数 字 滤 波 器的 性能指标变成模拟滤波器的 性 能 指 标。

2、模拟滤波器设计

• 设计出符合要求的模拟滤波器的 系 统 函 数。可以选择多种类型的滤波器。 如Butterworth,Chebyshev,Elliptic,Bessel等。

3、 映 射 实 现

二、IIR DF频率特性

• 它是由三个参量来表征: 1.幅度平方响应 2.相位响应 3.群延时

第5章:DSP(CCS)PPT演示课件

停止运行程序。

② Load Kernel: Lode Kernel 命令重新装入DSP核

③ Restart: Debug → Restart 命令将PC恢复到当前载

入程序的入口地址,但不执行当前程序。

④ Go main: Debug → Go main命令提供了一种快速运

行用户应用程序的方法。

11

5.1 CCS集成开发环境简介

• 源程序文件名和目标库; • 编译器、汇编器和链接器选项; • 头文件; 2.创建和管理工程

10

5.1 CCS集成开发环境简介

5.1.4 .调试

(1)装载可执行程序

File→Load Program

(2)复位(CCS提供4种方法)

① Reset DSP: Debug→Reset DSP命令初始化所有R并

CCS快捷图标

3

5.1 CCS集成开发环境简介

2. 系统配置 原因:为使CCS IDE能工作在不同的硬件或仿真

目标上

3. 系统启动 双击桌面上CCS 2(’C 5000)图标,启动CCS

IDE显示CCS主界面。

4

5.1 CCS集成开发环境简介

5.1.2 . CCS的窗口、菜单和工具条 1. CCS的窗口

编源程序的方法 • Target Control Toolbar:提供了目标程序控制的一些

工具 • Debug Window Toolbar:提供了调试窗口工具

9

5.1 CCS集成开发环境简介

5.1.3 . CCS的工程管理

CCS对程序采用工程(Project)的集成管理方法。工程保持 并跟踪在生成目标程序或库过程中的所有信息。 1.典型工程文件记录的信息

8

《DSP控制技术》课程教学大纲

DSP控制技术课程教学大纲DSPContro1Techno1ogy学时数:48其中:实验学时:8学分数:3适用专业:普通本科电气工程与自动化专业一、课程的性质、目的和任务本课程是电气工程与自动化本科专业的的专业选修课。

数字信号处理己发展成一门理论与实践紧密结合的、应用日益广泛的、迅速替代传统模拟信号处理方法的、具有丰富器件支持的先进技术和方法。

DSP 器件是数字信号处理技术的最佳载体。

了解和掌握数字信号处理的实用技术对电气类学生而言,显得越来越重要且迫切。

数字信号处理器是微处理器技术发展的一个重要分支,处理的高速性和高集成度和在信号处理方面的卓越性能,使其在IT业界的用途越来越广。

本课程正是顺应这一发展方向而为电气工程与自动化本科专业学生开设的专业选修课。

本课程的目的是使该专业学生在数字信号处理器件及应用方面具有一定的基础知识,掌握DSP的结构、工作原理、特性、应用及发展方向,使该专业毕业生在工作中具有利用DSP 开发产品和解决实际问题的基本能力。

二、课程教学的基本要求本课程以TMS320F2xx为蓝本,剖析TMS320'C2000系列数字信号处理器的结构、内部资源、运行方式和指令系统、开发系统。

借鉴DSP系统实例,要求学生了解DSP的原理、用途和性能,了解软件集成开发环境的使用,掌握采用DSP进行工程项目开发的过程和软硬件调试工具的使用,熟练掌握使用汇编/C语言编写应用处理程序的方法。

本课程总学时为48学时,3学分,其中课堂教学为40学时,实验教学8学时,在第七学期完成。

三、课程的教学内容、重点和难点第零章绪论(4学时)基本内容:数字信号处理器的特点,DSP器件的发展,DSP器件的特点,DSP与其它微处理器的比较,DSP器件的应用领域,DSP应用系统设计,Mat1ab在DSP应用系统中的作用。

第一节数字信号处理器第二节专用DSP和DSP-IP核第三节通用DSP器件第四节小结基本要求:1. 了解数字信号处理器的特点2. 了解DSP器件的发展,DSP器件的特点;3. 了解DSP器件的应用领域,掌握DSP应用系统设计流程;4. 了解Uat1ab在DSP应用系统中的作用。

第五章 通用输入输出端口-TMS320F28335 DSP原理、开发及应用-符晓

0

QUALPRD0

GPIO39-32 GPIO7-0

C2833x GPIO 控制寄存器

寄存器 GPACTRL GPAQSEL1 GPAQSEL2 GPAMUX1 GPAMUX2 GPADIR GPAPUD GPBCTRL GPBQSEL1 GPBQSEL2 GPBMUX1 GPBMUX2 GPBDIR GPBPUD GPCMUX1 GPCMUX2 GPCDIR GPCPUD

输入限定

GPIO Port C 方向寄存器 (GPCDIR) [GPIO 64 到 87]

GPIO Port C

F2833x GPIO管脚示意图

GPxSET GPxCLEAR GPxTOGGLE

I/O DIR Bit 0 = Input 1 = Output

GPxDIR

GPxDAT Out

I/O DAT Bit (R/W) In

C2833x GPIO 数据寄存器

寄存器 GPADAT GPASET GPACLEAR GPA到GGLE GPBDAT GPBSET GPBCLEAR GPB到GGLE GPCDAT GPCSET GPCCLEAR GPC到GGLE

描述 GPIO A Data 寄存器 [GPIO 0 – 31] GPIO A Data 置位寄存器[GPIO 0 – 31] GPIO A Data 清除寄存器[GPIO 0 – 31] GPIO A Data 翻转寄存器[GPIO 0 – 31] GPIO B Data 寄存器 [GPIO 32 – 63] GPIO B Data 置位寄存器[GPIO 32 – 63] GPIO B Data 清除寄存器[GPIO 32 – 63] GPIO B Data 翻转寄存器[GPIO 32 – 63] GPIO C Data 寄存器 [GPIO 64 – 87] GPIO C Data 置位寄存器[GPIO 64 – 87] GPIO C Data 清除寄存器[GPIO 64 – 87] GPIO C Data 翻转寄存器[GPIO 64 – 87]

《电机数字控制系统集成设计》系列讲座(九) 第5章 基于DSP架构交流电机数字控制系统集成设计

握了 A D MC 3 3 1 D S P的基 本结 构 ,进行 了电机 系统 三相 电流 的 采样 、坐 标 变换 电

流环 设 计 以及 电 压解 耦控 制 等 ,为 无刷 直 流 电动 机 系统 的数 字 控 制提 供 了 必要 条 件 ,本节 重点 介绍 无刷 直流 电机 系统 的数学 模型 及在 位置 控制 系统 中的 应用 。

尼 情 况 下 且 能 实现 Fra bibliotek 超 调 ,但 要 达 到

图5 — 1 A 1 D l f C 3 3 1构 成 的 角位 置 控 制 系 统 原 理 框 图

无超 调 , 必 须 以牺牲 响应 速度 为代 价 ,

换 句 话 说 ,在 采 用 该 控 制 时 ,要 想 达

到 性 能 指 标 要 求 ,其 响 应 时 间 的 延缓 必 须 通 过 其 它 方 法 进 行 补 偿 。 为 此 选 择B a n g — B a n g控 制 ,P D 控 制 和 过 阻 尼

k p . m :k k p ,

即i  ̄ d = 0 ) ,等 式 ( 5 - 3 9 ) 可 表示 为 :

k

=

( ‘ 一 k ) + k l f , 一 『 ( ‘ 一 七 d t ( 5 - 3 8 )

q

R s i _ q +L q

( 5 — 4 0 )

式 中 ,V V 为调 节 器 的 输 出 ,用来 控 制 S P WM( 或 S V P WM) 逆 变 电路 ,驱 动 永磁 无刷 电动机 : k 为 电流反馈 系 数 ;k 为逆 变驱 动 电路等效 增 益 。 在 由 MO S F E T或 I G B T构 成 的 三 相 桥 式功 率 逆 变驱 动

挥 每 一 种 控 制 算 法 的优 点 ,从 而 达 到 较佳 的控 制 效 果 。 由分 析 可 知 : B a n g —

DSP复习总结

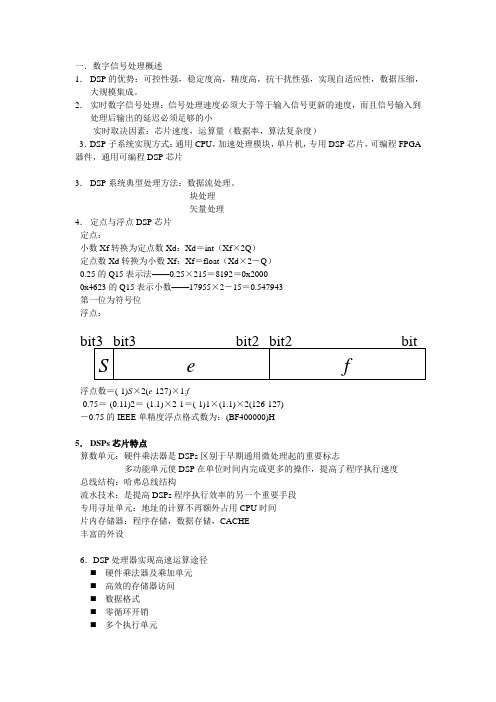

一.数字信号处理概述1.DSP的优势:可控性强,稳定度高,精度高,抗干扰性强,实现自适应性,数据压缩,大规模集成。

2.实时数字信号处理:信号处理速度必须大于等于输入信号更新的速度,而且信号输入到处理后输出的延迟必须足够的小实时取决因素:芯片速度,运算量(数据率,算法复杂度)3.DSP子系统实现方式:通用CPU,加速处理模块,单片机,专用DSP芯片,可编程FPGA 器件,通用可编程DSP芯片3.DSP系统典型处理方法:数据流处理。

块处理矢量处理4.定点与浮点DSP芯片定点:小数Xf转换为定点数Xd:Xd=int(Xf×2Q)定点数Xd转换为小数Xf:Xf=float(Xd×2-Q)0.25的Q15表示法——0.25×215=8192=0x20000x4623的Q15表示小数——17955×2-15=0.547943第一位为符号位浮点:bit3bit3bit2bit2bit S e f浮点数=(-1)S×2(e-127)×1.f-0.75=-(0.11)2=-(1.1)×2-1=(-1)1×(1.1)×2(126-127)-0.75的IEEE单精度浮点格式数为:(BF400000)H5.DSPs芯片特点算数单元:硬件乘法器是DSPs区别于早期通用微处理起的重要标志多功能单元使DSP在单位时间内完成更多的操作,提高了程序执行速度总线结构:哈弗总线结构流水技术:是提高DSPs程序执行效率的另一个重要手段专用寻址单元:地址的计算不再额外占用CPU时间片内存储器:程序存储,数据存储,CACHE丰富的外设6.DSP处理器实现高速运算途径⏹硬件乘法器及乘加单元⏹高效的存储器访问⏹数据格式⏹零循环开销⏹多个执行单元⏹数据流的线性I/O⏹专门的指令集6.DSP评价方法:传统性能评价MIPS-----百万指令每秒MOPS-----百万操作每秒MFLOPS-----百万浮点操作每秒MACS-------乘加次数每秒完整应用评价核心算法评价7.选型依据:速度,精度,芯片资源,开发工具,支持多处理器,功耗与电源管理,成本。

DSP设计课程设计

DSP设计课程设计一、课程目标知识目标:1. 让学生理解DSP(数字信号处理)的基本原理和概念,包括采样定理、傅里叶变换和数字滤波器设计等。

2. 使学生掌握DSP算法的数学推导和实现方法,具备使用DSP芯片进行信号处理的能力。

3. 帮助学生了解DSP技术在通信、音视频处理等领域的应用。

技能目标:1. 培养学生运用数学工具进行DSP相关算法推导和仿真能力。

2. 提高学生实际操作DSP芯片,完成信号处理实验的能力。

3. 培养学生团队协作和沟通能力,能够就DSP技术问题进行讨论和分析。

情感态度价值观目标:1. 激发学生对数字信号处理技术的兴趣,培养其探索精神和创新意识。

2. 培养学生严谨的科学态度,注重实践和理论相结合。

3. 引导学生关注DSP技术在国家和社会发展中的应用,增强其社会责任感和使命感。

分析课程性质、学生特点和教学要求,本课程旨在让学生通过学习DSP设计,掌握数字信号处理的基本原理和方法,培养其实践操作能力。

课程目标分解为具体学习成果,以便后续教学设计和评估:学生能够独立完成DSP算法推导、仿真和实验操作,具备解决实际问题的能力,并在团队合作中发挥积极作用。

二、教学内容1. DSP基本原理与概念- 采样定理与信号重建- 傅里叶变换及其应用- 数字滤波器设计原理2. DSP算法及其数学推导- 离散时间信号处理基础- 快速傅里叶变换(FFT)算法- 数字滤波器算法实现3. DSP芯片与应用- DSP芯片架构与特点- DSP芯片编程与实验操作- DSP技术在通信、音视频处理等领域的应用案例4. 教学大纲安排与进度- 第一阶段:基本原理与概念(2周)- 课本章节:第1-3章- 第二阶段:DSP算法及其数学推导(3周)- 课本章节:第4-6章- 第三阶段:DSP芯片与应用(3周)- 课本章节:第7-9章教学内容按照课程目标进行选择和组织,确保科学性和系统性。

在教学过程中,教师将依据教学大纲,引导学生学习课本相关章节,完成教学内容的学习。

TMS320C55Xdsp原理及应用汪春梅第5章详解

使用方法

省电(IDLE)

与省电有关的位是IAI

DSP复位

CLKMD引脚为低电平,输出频率等于输入频率; CLKMD引脚为高电平,输出频率等于输入频率的一半

失锁

锁相环对输入时钟跟踪锁定之后,由于其他原因使其 输出时钟发生偏移

使用方法及实例

利用库函数配置时钟发生器的方法

首先要声明PLL配置结构,具体声明如下:

自动重装控制位:ARB ; 定时器开始停止状态位:TSS 定时器装载位 : TLB ; 时钟输出极性位:POLAR 定时器工作模式位: FUNC ; 定时器输出时钟脉冲选择位:C/P 定时器输出脉冲的宽度:PWID;

二、定时器的工作原理

2、 通用定时器内部寄存器

定时器发送定时中断信号或者同步事件信号的 频 率计算公式:

当usb的dma控制器访问外部存储器时dma控制器向外部存储器接口发出一个申请并等待服务主机dma模式usb模块中的中断usb模块的寄存器dma内容寄存器为每个输入输出端点都单独提供了一套内容寄存器内容寄存器主要有控制寄存器主寄存器和重载寄存器通用端点描述寄存器端点配置寄存器x缓冲区基址寄存器x缓冲区计数寄存器输出端点x缓冲区计数扩展寄存器输入端点xy缓冲区数量扩展寄存器xy缓冲区数量寄存器y缓冲区基址寄存器y缓冲区计数寄存器输出端点y缓冲区计数扩展寄存器控制端点描述寄存器配置寄存器和计数寄存器中断寄存器usb中断源寄存器中断事件标志寄存器中断使能寄存器主机dma模式寄存器通用控制及状态寄存器usb时钟模式寄存器usbclkmdusb空闲控制寄存器usbidlectlusb模块的应用模数转换器adc模数转换器结构和时序转换时序图模数转换器结构示意图模数转换器的寄存器控制寄存器adcr数据寄存器addr时钟分频寄存器adcdr时钟控制寄存器adccr模数转换控制寄存器adcr模数转换数据寄存器addr模数转换时钟分频寄存器adcdr模数转换时钟控制寄存器adccr一个设置模数转换器的例子在该例子中dsp系统主时钟为144mhz1首先对系统主时钟分频产生模数转换器时钟该时钟应尽量运行在较低频率下以降低功率消耗在本例中模数转换器时钟是通过对系统主时钟36分频产生的则此时模数转换时钟144mhz364mhz根据公式adcclocksystemclocksystemclkdiv1得出systemclkdiv35

dsp原理及应用课程设计

dsp原理及应用 课程设计一、课程目标知识目标:1. 理解数字信号处理(DSP)的基本原理,掌握其核心概念,如采样、量化、滤波器设计等。

2. 掌握DSP技术在音频、视频和通信领域的应用,了解不同应用场景下的技术特点和要求。

3. 学习DSP相关算法,如快速傅里叶变换(FFT)、数字滤波器设计等,并能运用所学知识解决实际问题。

技能目标:1. 能够运用所学知识分析实际问题,提出基于DSP技术的解决方案。

2. 掌握使用DSP开发工具和软件,如MATLAB、Python等,进行算法仿真和实现。

3. 培养团队协作和沟通能力,通过项目实践,提高解决实际问题的综合能力。

情感态度价值观目标:1. 培养学生对数字信号处理技术的兴趣和热情,激发其探索精神和创新意识。

2. 增强学生对我国在DSP领域取得的成果的自豪感,培养其爱国主义情怀。

3. 培养学生严谨、务实的学术态度,提高其面对挑战、克服困难的信心和勇气。

课程性质分析:本课程为专业核心课程,旨在使学生掌握数字信号处理的基本原理、方法和应用,培养具备实际工程能力的专业人才。

学生特点分析:学生已具备一定的数学基础和编程能力,具有较强的逻辑思维和动手实践能力,但对DSP技术的了解相对有限。

教学要求:1. 结合实际案例,深入浅出地讲解DSP原理,注重理论与实践相结合。

2. 采用项目驱动教学法,引导学生主动探索,培养其解决实际问题的能力。

3. 注重培养学生的团队协作和沟通能力,提高其综合素质。

二、教学内容1. 数字信号处理基础:包括采样定理、量化原理、信号的表示与处理等基本概念,参照教材第一章内容。

2. 离散傅里叶变换(DFT):讲解DFT的基本原理、性质、应用,以及快速傅里叶变换(FFT)算法,涉及教材第二章。

3. 数字滤波器设计:包括数字滤波器的基本类型、设计方法、性能分析,参照教材第三章。

4. DSP应用案例分析:分析音频处理、图像处理、通信系统等领域的DSP技术,结合教材第四章内容。

dsp语音通信系统课程设计

dsp语音通信系统课程设计一、课程目标知识目标:1. 理解数字信号处理(DSP)的基本原理,掌握其在语音通信中的应用。

2. 学习并掌握语音信号的采集、处理、传输和接收等基本环节。

3. 掌握语音信号的数字化过程,包括采样、量化、编码等关键技术。

技能目标:1. 能够运用所学知识,设计并实现一个简单的DSP语音通信系统。

2. 培养学生动手实践能力,学会使用相关软件和硬件工具进行语音信号处理和通信。

3. 提高学生的问题分析和解决能力,能够针对实际通信过程中的问题进行优化和调试。

情感态度价值观目标:1. 培养学生对通信工程领域的兴趣,激发学生的创新意识和探索精神。

2. 培养学生的团队合作意识,学会与他人合作共同解决问题。

3. 增强学生的责任心和使命感,认识到通信技术在我国经济社会发展中的重要地位。

分析课程性质、学生特点和教学要求:1. 课程性质:本课程为电子信息类学科的专业课程,具有较强的理论性和实践性。

2. 学生特点:学生已具备一定的电子技术和数字信号处理基础,具有一定的编程和实践能力。

3. 教学要求:结合实际应用,注重理论与实践相结合,强调学生的动手实践能力和创新能力。

二、教学内容1. DSP基本原理回顾:包括数字信号处理的基本概念、系统函数、傅里叶变换等基础理论。

相关教材章节:第一章 数字信号处理基础2. 语音信号处理技术:学习语音信号的特性、预处理方法、特征提取等关键技术。

相关教材章节:第二章 语音信号处理技术3. 语音信号的数字化:介绍语音信号的采样、量化、编码等过程,分析其影响通信质量的因素。

相关教材章节:第三章 语音信号的数字化4. 语音通信系统设计:学习语音通信系统的基本架构,探讨各个环节的设计方法。

相关教材章节:第四章 语音通信系统设计5. DSP语音通信系统实践:结合实际案例,指导学生设计并实现一个简单的DSP语音通信系统。

相关教材章节:第五章 实践环节6. 系统优化与调试:分析通信过程中的问题,探讨优化和调试方法,提高通信质量。

TMS320C55xDSP应用系统设计

DSP的含义

数字信号处理(Digital Signal Processing)

数字信号处理的理论和算法

数字信号处理器(Digital Signal Processor)

实现数字信号处理算法的微处理器芯片

1979年,美国Intel公司推出商用可编程器件DSP芯 片Intel2920

1980年,日本NEC公司推出μPD7720,第一片具 有乘法器的商用DSP芯片 1982年,TI公司成功推出其第一代DSP芯片 TMS32010及其系列产品TMS32011、 TMS320C10/C14 /C15/C16/C17

1.3 DSP芯片产品简介

TI公司的DSP芯片概况 其它公司的DSP芯片概况 TMS320C5000概况

1.3.1 TI公司的DSP芯片概况

经典产品

TMS320C1X、TMS320C25、TMS320C3X/4X、 TMS320C5 X、TMS320C8X TMS320C2000,用于数字化控制领域

Motorola公司的DSP5600、9600系列,AT&T公司的 DSP32等。

第三阶段,DSP的完善阶段(2000年以后)

信号处理能力更加完善,而且使系统开发更加方便、 程序编辑调试更加灵活、功耗进一步降低、成本不 断下降 各种通用外设集成到片上,大大地提高了数字信号 处理能力 DSP运算速度可达到单指令周期10ns左右,可在 Windows 下用C语言编程,使用方便灵活

1.2.4 DSP芯片的应用领域

第五章 TMS320C20X系列DSP的功能单元

定时器的中断速率: 定时器的定时周期:

TINT 速率 = CLKOUT1 × 1 (TDDR + 1) × (PRD + 1)

定时器的时间(周期):

(TDDR + 1 ) × (PRD + 1 ) Ts = CLKOUT 1 = (TDDR + 1 ) × (PRD + 1 )*tc

例:设DSP的时钟CLKOUT1为10MHz,要在引脚 例:设DSP的时钟CLKOUT1为10MHz,要在引脚 TOUT上获得10kHz脉冲信号,则定期器的PRD TOUT上获得10kHz脉冲信号,则定期器的PRD 和TDDR分别为 TDDR分别为 取 TDDR=4,则有关系: TDDR=4,则有关系:

3. 定时器的应用及编程

TMS320C2000系列中断分类 中断分类 软件中断:由指令INTR、NMI、TRAP向CPU发出中断请求; 触发源 外部硬件中断:由外部中断引脚上的中断申请信号触发; 硬件中断 内部硬件中断:由片内外围设备的请求信号触发; 可屏蔽中断:仅包括硬件中断,可以通过软件屏蔽或使能; 可控性 非屏蔽中断:包括所有软件终端和外部硬件中断RS和NMI,他们不能被屏蔽

中断相关的寄存器

中断标志寄存器

15 6 5 4 3 2 1 0

保留 TXRXINT XINT RINT TINT INT2/INT3

HOLD/INT1

中断屏蔽寄存器

15 6 5 4 3 2 1 0

保留 TXRXINT XINT RINT TINT INT2/INT3

HOLD/INT1

中断控制寄存器

D6~D9位PSC,定时器预定标计数器,用于保存定时器的当 前预定标计数值,PSC不能被直接设置,他只能从TDDR寄 存器取得其值。 D5位 TRB,定时器重载位,当向TRB写入1时,TIM装载 D5位 TRB,定时器重载位,当向TRB写入1时,TIM装载 PRD中的值,且PSC装载TDDR中的值; PRD中的值,且PSC装载TDDR中的值; D4位 TSS,定时器停止控制位: D4位 TSS,定时器停止控制位: TSS=0,启动或者重新启动定时器; TSS=0,启动或者重新启动定时器; TSS=1,停止定时器; TSS=1,停止定时器; D0~D3位 TDDR,定时器周期寄存器。 D0~D3位 TDDR,定时器周期寄存器。

DSP第5章-F28335-概述

5.1 F28335的性能

高性能静态CMOS技术:主频150MHZ,指令周期6.67ns; 低功

耗设计,1.9V/1.8V内核电压,3.3VI/O引脚电压;Flash编 程电压为3.3V

高性能32位CPU:IEEE-754单精度浮点运算单元(FPU) ;

534存储器存储空间映射如右图534存储器resetsleepstate芯片复位后的状态standbystate耗能比sleep状态多但转为下个状态时间短activereadstatecpu在flash和otp读取访问由fbankwait寄存器和fotpwait寄存器控制534flash和otp存储器的低功耗模式可提高flash中线性代码的执行效率对fopt寄存器中的enpipe置位来使能流水线模式独立于cpu的流水线模式535flash的流水线模式536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器54代码安全模块csm541csm的功能阻止对片内存储器未授权访问防止代码被复制或反解两级保护

5.5 总结

外设帧的寄存器映射如下图所示。

5.5 总结

外设帧的寄存器映射如下图所示。

5.6 F28335与F2812的比 较

5.6 F28335与F2812的比 较

5.4 代码安全模块(CSM)

5.4.2 CSM对其它片内资源的影响

5.4 代码安全模块(CSM)

5.4.3 CSM的使用

工程开发阶段,一般不使用CSM 开发出可靠代码后,才使用CSM 在Flash中烧写代码前,采用密码对芯片进行保护 之后,通过JTAG或运行片内外存储器对安全存储器调试,需输入正 确密码

第5章基于FPGA的DSP开发(一)

(10)添加Product(乘法)模块。在

Altera DSP Builder库中选择Arithmetic子 库,找到Product模块。

将之拖放到新建模型窗口中去,这里Product有两 个输入一个是经过Delay的SinLUT输出,另一个是 一位端口SinCtrl,Product实现了SinCtrl对 SinLUT查找表输出的控制。双击Product模块,打 开Product模块参数设置对话框。其中Pipeline (流水线)参数指定该乘法器模块使用几级流水线, 即乘积延时几个时钟周期后输出,选中”Use LPM”,表示使用参数化的模块库来实现,选 择”Use Dedicated Circuitry”表示可以使用 FPGA中的专用模块来实现.

设计流程的第五步

在Quartus

II中编译用户的设计,最后将设计 下载,进行测试验证。

经过测试、验证的设计可以单独执行相应的

DSP功能。如果DSP Builder产生的DSP模 型只是整个设计中的一个子模块,那么可以 在设计中调用DSP Builder产生的VHDL文件, 以构成完成的设计。

(5)添加Increment

Decrement模块。 Increment Decrement模块是DSP Builder 库中Arithmetic子库中的模块。选中Altera DSP Builder中的Arithmetic子库,然后在 其中选择Increment Decrement模块。然后 按照添加SignalCompiler的方法将 Increment Decrement添加到模型文件中。

5.2.1 建立设计模型

(1)运行Matlab,Matlab的主窗口被分成3部分: Command Window、Workspace/Current Directory、Command History。 (2)建立工作目录。在建立一个新的设计模型前, 先要建立一个文件夹,作为工作目录,来保存相应 的设计文件,在进行设计之前要先切换到该文件夹 下。新建和切换到工作目录可以在命令窗口中使用 Matlab 命令,也可以在Current Directory窗口中 实现。

DSP第5章3-冲激响应不变法

1 T

H (z)

ze

sT

k

2 Has j k T

H (z)

ze

sT

ˆ H a (s)

1 T

k

2 Has j k T

2、混迭失真

H (e

j

)

1 T

k

2 k Ha j T

缺点: 频率响应混迭 只适用于限带的低通、带通滤波器

n

u(n )

n N

h( n ) z

n 0 k 1 1

Ak e

N

n

z

n

k 1

Ak e

n0

sk T

z

n

1e

k 1

Ak

sk T

z

1

H a (s)

k 1

N

Ak s sk

H (z)

1 e

k 1

sk T

N

Ak

sk T

z

1

f s

T

T

s 2

混迭

当滤波器的设计指标以数字域频率 c 给定时, 不能通过提高抽样频率来改善混迭现象

fs T

T

, T T

T

c

c

T

3、模拟滤波器的数字化方法

H a ( s ) ha ( t ) ha ( n T ) h ( n ) H ( z )

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

编辑功能(Edit)

1、Undo (取消键入) 2、Redo (重复键入) 3、Cut (剪切) 4、Copy (复制) 5、Paste (粘贴) 6、Delete (删除) 7、Select All (全选) 8、Find/Replace (寻找/替换) 9、Find in Files (在多个文件中寻找文本) 11、Memory (存储器) 12、Edit Register (编辑寄存器) 13、Edit Veriable (编辑变量) 14、Edit Command Line(编辑命令行) 15、Column Edit (列编辑) 16、Bookmarks (书签)

为提高实时信号处理系统的开发进程,TI公司针对TMS320C2XX, C54X\C54XX\C55X,C6X,C3X\C4X 分别提供了一套全新的集成开发环 境CCS(Code Compose Studio) 。 CCS集编译、仿真、下载为一体的DSP开发软件。可以通过CCS新建工程、 编译仿真工程、在线调试、下载程序。与Keil及伟福类似,它也由菜单栏、 工具栏、工程窗口、程序窗口等组成。 CCS采用图形接口,提供有编辑指令,参数修改工具,它为非代码产生工 具集成了一个统一的集成环境,包括了TI公司提供的C源代码调试器 和模拟器所具有的功能,能对TMS320系列DSP进行指令级的仿真和进行 可视化的实时数据分析,可大大提高开发工作效率,缩短应用系统开发周 期。

观察窗口的使用

观察存储空间的内容

点击View\memory, 出现如图界面。可 以根据需要设置存 储空间的数据显示 格式。

观察窗口的使用

跟踪变量的值

① 在调试程序时,经常需要掌握程序运行过程中变量的变化情况。 利用CCS提供的观察窗口,可以很方便监测C语言中的局部或全局 变量。 ② 点击View\Watch window,弹出观察窗口。观察窗口包含两个部 分,即局部观察窗口(Watch Locals)和观察窗口1(Watch 1).

CCS的安装

安装CC2000到软件中,运行CC2000安装程序setup.exe。安装完成后, 在桌而上会有“CCS’C2000”和“Setup CCS2’C2000”两个快捷方式图 标。分别对应CCS 2C000应用程序和配置程序,如图所示。

运行CCS2000配置程序设置驱动程序,如果CCS2000是在目标板上

器件选型 原理设计 检查PCB板 上各硬件是 否能正常工 作。 PCB版图设计

系 统 分 析

系 统 综 合

硬件调试

5.3 软件设计步骤

编写C语言源程序 优化ANSI C编译器 生成汇编文件 宏汇编源文件 文档管理器 宏汇编库

编写汇编语 言源程序

汇编语言汇编器 生成目标文件 链接器

软件仿真

软件开发系统

软件开发平台CCS的应用

工程管理

假设已在D盘上建立了工程文件夹 nomal,该文件夹包含 了.c、.cmd以及.h文件等。 运行CCS,在“projiect”菜单打开该工程,选择.pjt 文件。 点击source文件夹,展开所有文件。选择.c,双击,就 可以打开该文件了。

工程管理

• 编译、链接时,CCS下面的输出窗口会显示相应的状态 信息。如果CCS的编译链接过程出现问题,CCS会给出 提示,用户可以根据提示的信息,寻找问题出现在什么 地方。双击该错误提示,光标会跳转到错误行上,可以 检查是不是有语法等错误,直到无任何错误信息。 • 打开File,选择“Load Program”装载应用程序。经过编 译、链接后生成的代码文件在工程文件夹中的Debug文 件夹中,.out文件,通过File\Load Program加载此文件。 运行程序。

第四步:模拟数字混合电路设计 实现DSP与模拟混合产品的无缝连接,以及保 证数据的吞吐量,实现模拟与数字部分隔离。 第五步:系统电路设计 重点是合理进行系统技术指标的分配,在时序 设计上保证系统速度(包括处理速度、接口速度、 元器件速度等)和实时控制。 第六步:系统对软件的编写与调试 对信号处理的算法进行编程,并提供系统监控 程序。

运行,则要先安装目标板驱动卡,然后运行“Setup CCS’C2000”配置 驱动程序,最后才能执行 CCS2000 。除非用户改变 CCS2000 应用平台 类型,否则只需运行一次CCS2000配置程序。

CCS软件界面介绍

文件管理功能(File)

File(文件)菜单如图所示。其中常用的菜单选项如下: New(新建文件):新建一个源文件(默认为.c)。 Open(打开):打开一个源文件。 Close(关闭):关闭现有的文件。 Save/Save As(保存/另存为):保存源文件。 Load Program(下载程序):将生成的.out文件下载到目标板上。 图 File菜单 Reload Program(重新下载程序):下载上一次生成的.out文件。 Data/Load(数据下载):将文件下载到目标板上,下载的数据可以指定存 放的地址和数据长度。 Workspace/Load(装入工作空间)。 Workspace/Save(保存当前的工作环境)。

调试

有单步调试、运行到光标处、 运行到断点处、停止, 以及全 速运行等。 – Breakpoints(添加断点): 当程序运行遇到断点时,程 序自动停止并跳出。 – Step Into(单步运行):可 以单步运行程序,并观察各 变量及寄存器的状态,可以 方便地调试程序。 – Step out:跳出当前执行的子 程序,返回到上一级程序代码。 – Run:自由运行程序。 – Halt:暂停正在运行的程序。

视图功能(View)

…Toolbar:常用的工具栏选择, 可以激活相应的工具栏。 Registers(寄存器):可以观察相 应寄存器的状态。 Graph/Time/Frequent:在时域 或频域上显示信号波形,时域分析 时数据无需进行处理,频域分析时 需将数据进行FFT处理。 Graph/Constellation:采用星座 图显示信号波形。 Graph/Eye Diagram:使用眼图 来量化失真度。 Watch Window(观察窗口): 可以实时观察相应的变量的值。

第七步:系统测试与验证 • 硬件部件的原理验证:电路的调试 • 通过DSP的原理验证:在线仿真电路调试 • 软件的仿真与算法验证:算法的实际硬件实现 • 系统硬件功能验证与指标测试:验证系统技术 指标 • 系统软件完善:确保系统的智能化与可程控性 • 其他测试与验证:软硬件可靠性,自检,环境 实验

1.5v 0.8v 0.4v 0v

VOH VIH

VT VIL VOL GND

2.4v 2.0v

1.5v 0.8v 0.4v 0v

VOH VIH

VT VIL VOL GND

5V CMOS

5V TTL

3.3V TTL

确定硬件方案

器件选型 原理设计 PCB版图设计 PCB布线不是 简单的端口 互连

确定硬件方案

格式转换 烧录EPROM

输出可执行文件

调试器

目标DSP系统

评测模块

系统仿真XDS

5.4 系统集成

系统集成是将软硬件结合起来,并组装成一台样机, 在实际系统中运行,进行系统测试。

出现问题时,一般采用修改软件的方法。如果

软件修改无法解决问题,则必须调整硬件,这时问 题就较为严重了。

5.5 软件开发平台CCS及其应用

第一步:算法分析与优化 根据需求,完成算法的仿真验证 第二步:DSP的选择 根据核心算法、数据吞吐率,以及系统要求进 行选择 第三步:DSP配置 DSP基本电路包括本身的基本引脚连接、总线 驱动、时钟控制、引导程序方式控制、存储器配置、 通信口配置、IO口控制、时序设计等,保证DSP的 基本工作模式。

DSP芯片基本管脚的配置

DSP引导方式选择 DSP扩展存储器设计 原理设计 DSP时钟设计 DSP电源设计 DSP电平转换电路设计

DSP电平转换电路设计

5v 4.4v Vcc VOH 5v Vcc 3.3v Vcc

3.5v

2.5v 1.5v 0.5v 0v

VIH

VT VIL VOL GND

2.4v 2.0v

滤波器

ADC

通信口

典型DSP目标板原理框图

DSP目标板的设计要素 算法分析及优化 DSP运算量核算及DSP选择 数字化要求 模拟混合电路ADC/DAC设计 吞吐量要求 存储器需求ROM/RAM/FLASH 通信口要求 其他控制(电源、时钟、同步) 体系结构设计(单DSP还是多DSP,并行还是串 行,全DSP、DSP/MCU或DSP/FPGA混合)

5.2 硬件设计步骤

系 统 分 析

系 统 综 合

确Leabharlann 硬件方案根据性能指标、工期、成本等, 确定最优硬件实现方案,并画 出硬件原理框图。

确定硬件方案

器件选型

一般系统中常用AD、DA、存储 器、电源、逻辑控制、人机接口、 通信、总线等基本部件。

确定硬件方案

器件选型 原理设计

原理设计是DSP系统集成中关键的 一步,其成功与否是DSP系统能否 正常工作的最重要的一个因素。

根据需求写出任务说明书 软件设计说明 根据任务确定技术指标 软件编程与调试 硬件设计说明 硬件sch / pcb 硬件调试 系统测试

总体设计确定软硬件分工

确定DSP芯片与外围芯片

系统集成

DSP总体设计框图

DSP方案设计基本步骤 控制 EPROM DSP RAM 滤波器 DAC

信号 预处 理 MUX 程控 放大

第5章 DSP系统设计

• • • • • 5.1 总体方案设计 5.2 硬件设计步骤 5.3 软件设计步骤 5.4 系统集成 5.5 CSS开发平台

5.1 总体方案设计

根据需求写出任务说明书 根据任务确定技术指标

具体技术指标 由信号频率、带宽决定系统的采样频率。 由采样频率确定任务书中最复杂算法所需最大 时间以及系统对实时性要求判断系统能否完成工 作。 由数据量及程序长度决定片内RAM的容量,是 否需要扩展。 由系统精度决定是16位还是32位,定点还是浮 点运算。 根据系统用途是计算还是控制,来决定对输入输 出端口的要求。