60 GHz tapered-helix antenna for WPAN applications

Mellanox SX6710G 高性能、低延迟 56Gb s FDR InfiniBand 到 4

©2018 Mellanox Technologies. All rights reserved.†For illustration only. Actual products may vary.The SX6710G is a high-performance, low-latency 56Gb/s FDR InfiniBand to 40Gb/s Ethernet gateway.SCALING-OUT DATA CENTERS WITH INFINIBAND TO ETHERNET GATEWAYFaster servers based on PCIe 3.0, combined with high-performance storage and applications that use increasingly complex computations, are causing data bandwidth requirements to spiral upward. As servers are deployed with next generation processors, High-Performance Computing (HPC) environments and Enterprise Data Centers (EDC) will need every last bit of bandwidth delivered with Mellanox’s FDR InfiniBand to 40GbE high-speed smart gateways.VIRTUAL PROTOCOL INTERCONNECT ® (VPI)Virtual Protocol Interconnect (VPI) flexibility enables any standard networking, clustering, storage and management protocol to seamlessly operate over any converged network leveraging a consolidated software stack. VPI simplifies I/O system design and makes it easier for IT managers to deploy infrastructure that meets the challenges of a dynamic data center.With its high bandwidth, low latency and reduced overhead, InfiniBand is the ideal choice for speeding application performance while simultaneously consolidating network and I/O infrastructure. Combining InfiniBand and Ethernet into a single solution provides an ideal rack backbone for next generation data centers.SUSTAINED NETWORK PERFORMANCEBuilt with Mellanox’s SwitchX ®-2-based switches, the InfiniBand to Ethernet gateway software license or system, provides full port flexibility to choose between 56Gb/s InfiniBand to either 10, 40 and 56Gb/s Ethernet with low 430ns latency.SX6710G, when combined with Mellanox’s ConnectX ®host adapter family, delivers cost savings byintegrating two networks on a single wire. Consolidating multiple networks on a single wire delivers both CAPEX and OPEX savings. OPEX savings are provided by reducing cabling complexity, reducing switch and server infrastructure and delivering a consistent and easy to use management software.MANAGEMENTSX6710G MLNX-OS ® software delivers complete chassis management, to manage the firmware, power supplies, fans, ports and other interfaces. SX6710G can also be coupled with Mellanox’s Unified Fabric Manager (UFM ®) software for managing scale-out computing environments. UFM enables data center operators to efficiently provision, monitor and operate the modern data center fabric.36-port Non-blocking Managed 56Gb/s InfiniBand to 40GbE Ethernet GatewaySX6710G InfiniBand to Ethernet GatewayPRODUCT BRIEFGATEWAY SYSTEM †350 Oakmead Parkway, Suite 100, Sunnyvale, CA 94085Tel: 408-970-3400 • Fax: © Copyright 2018. Mellanox Technologies. All rights reserved.Mellanox, Mellanox logo, ConnectX, SwitchX, MLNX-OS, Virtual Protocol Interconnect and UFM are registered trademarks of Mellanox Technologies, Ltd. All other trademarks are property of their respective owners.Mellanox SX6710G InfiniBand to Ethernet Gatewaypage 2Mellanox SX6710G –19’’ rack mountable chassis, 1Uwith redundant power supplies and fan units –36 QSFP non-blocking ports with aggregate data throughput up to 4.032Tb/s (FDR) –InfiniBand port-to-port latency 200ns –Ethernet port-to-port latency 230ns InfiniBand Switch Specifications –Compliant with IBTA 1.21 and 1.3 –9 virtual lanes: 8 data + 1 management–256 to 4Kbyte MTU–48K L2 forwarding entriesEthernet Switch Specifications –48K L2 forwarding entries –Static MAC –802.1w Rapid Spanning Tree Protocol–802.3ad Link Aggregation/LACP–802.3x Flow control–802.1Qbb Priority Flow Control (PFC) –802.1Qaz Enhanced Transmission Selection –802.1AB LLDP –VLAN 802.1Q (4K) –IGMP v1,v2, Snooping –Access Control Lists (L2-L4) –Jumbo Frames (9216 Bytes) –sFlow –Port Mirroring Management –Dual 100/1000Mb/s Ethernet ports–RS232 port over DB9–USB port–DHCP –SNMP v1,2,3 –JSON & CLI, Enhanced WebUI –ZTP –Dual software image–SYSLOGConnectors and Cabling –QSFP+ connectors –Passive copper or active fiber cables–Optical modulesIndicators–Per port status LED Link, Activity–System status LEDs: System, fans, power supplies –Port Error LED –Unit ID LEDPhysical Characteristics–Dimensions:1.72’’H x 16.84’’W x 27’’D –Weight: 19.4 lb (8.8 kg)Power Supply–Dual redundant slots –Hot plug operation –Input range:100-127VAC, 200-240VAC –Frequency:50-60Hz, single phase ACCooling–Front-to-rear or rear-to-front coolingoption –Hot-swappable fan unit Power Consumption Typical power consumption:–Passive cable - 130W –Active cable - 235WFEATURESSafety–CB –cTUVus –CE –CUEMC (Emissions)–CE –FCC –VCCI –ICES –RCMOperating Conditions–Operating 0ºC to 45ºC–Non-Operating -40ºC to 70ºC –Humidity: Operating 5% to 95% –Altitude: Operating -60m to 3200mAcoustic–ISO 7779 –ETS 300 753Others–RoHS-6 compliant –Rack-mountable, 1U –1-year warrantyCOMPLIANCETable 1 - Part Numbers and Descriptions060064PB Rev 1.1* This section describes hardware features and capabilities. Please refer to the driver and firmware release notes for feature availability.。

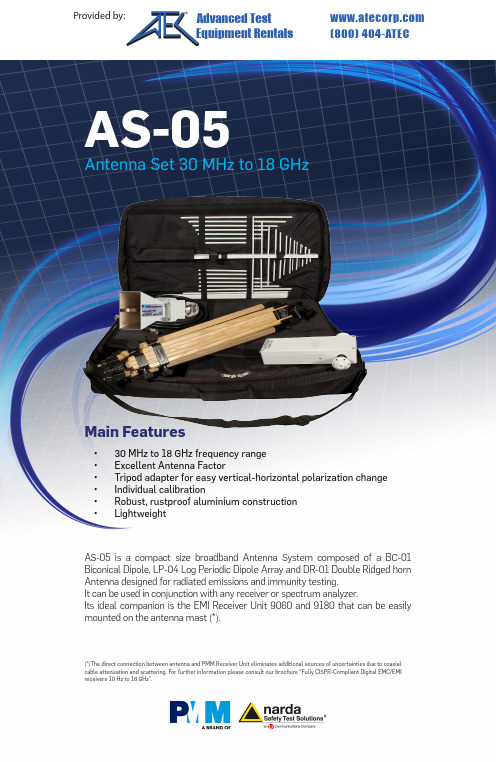

ATE Corporation AS-05 Antenna Set 30 MHz to 18 GHz

Main Features•30 MHz to 18 GHz frequency range •Excellent Antenna Factor•Tripod adapter for easy vertical-horizontal polarization change •Individual calibration•Robust, rustproof aluminium construction •LightweightAS-05 is a compact size broadband Antenna System composed of a BC-01 Biconical Dipole, LP-04 Log Periodic Dipole Array and DR-01 Double Ridged horn Antenna designed for radiated emissions and immunity testing. It can be used in conjunction with any receiver or spectrum analyzer.Its ideal companion is the EMI Receiver Unit 9060 and 9180 that can be easily mounted on the antenna mast (*).(*)The direct connection between antenna and PMM Receiver Unit eliminates additional sources of uncertainties due to coaxial cable attenuation and scattering. For further information please consult our brochure “Fully CISPR-Compliant Digital EMC/EMI receivers 10 Hz to 18 GHz”.Antenna Set 30 MHz to 18 GHzProvided by: (800)404-ATECAdvanced Test Equipment Rentals®Ordering Information:AS-05 antenna set 30 MHz to 18 GHz with individual calibration reports.AS-05/TC antenna set 30 MHz to 18 GHz with typical calibration reports.Includes: BC-01 biconical antenna; LP-04 Log-periodic antenna; DR-01Double-rideged antenna; TR-01 wooden tripod; RF cable, 6 GHz, N(m)-N(m), 5 m; Soft carrying case; Rigid carrying case (for DR-01), Operating manual; Calibration reports*.* Individual calibration reports are provided with AS-05.AS-05/TC does not include individual calibration but typical antenna factor.Optional accessories:Additional TR-01 Wooden tripod extensible 60 - 180 cm with antenna mounting adapter for fast horizontal to vertical polaritazion changing. Additional RF cable, 3 GHz, N(m)-N(m), 5 m.Sales Office:Via Leonardo da Vinci, 21/2320090 Segrate (Milano) - ITALY Phone: +39 02 2699871Fax: +39 02 26998700Headquarter:Via Benessea, 29/B17035 Cisano sul Neva (SV) - ITALY Phone: +39 0182 58641Fax: +39 0182 586400E-Mail:**************************Internet: www.narda-sts.itRelated ProductsReceiversAntennasCalibrations service• 7010/00: EMI receiver 150 kHz to 1 GHz • 7010/01: EMI receiver 9 kHz to 1 GHz • 7010/03: EMI receiver 9 kHz to 3 GHz • 9010: EMI receiver 10 Hz to 30 MHz • 9010F: EMI receiver 10 Hz to 30 MHz• 9010/03P: EMI receiver 10 Hz to 300 MHz • 9010/30P: EMI receiver 10 Hz to 3 GHz • 9010/60P: EMI receiver 10 Hz to 6 GHz • 9030: EMI Receiver 30 MHz to 3 GHz • 9060: EMI Receiver 30 MHz to 6 GHz •FR-4003: Field Receiver 9 kHz to 30 MHz• LP-02: Log Periodic Antenna 200 MHz to 3 GHz • LP-03: Log Periodic Antenna 800 MHz to 6 GHz • TR-01: Antenna Tripod• VDH-01: Van der Hoofden test-head 20 kHz to 10 MHz • Antenna Set AS-02 (BC01+LP02+TR01)• Antenna Set AS-03 (BC01+LP02+LP03+TR01) • Antenna Set AS-04 (BC01+LP04+TR01)• RA01: Rod Antenna 9 kHz to 30 MHz• RA01-HV: Rod Antenna 150 kHz to 30 MHz •RA01-MIL: Rod Antenna 9 kHz to 30 MHz• Ansi 63,5 Antenna Factor • SAE ARP 958-D• Free-Space Antenna FactorSPECIFICATIONSFrequency range GainAntenna factor Max input power Connector Dimensions (L x H x W)Weight Colour Impedance ConstructionBC-0130 to 200 MHz -15 +2 dBi typical 8 to 14 dB/m typical 100 W N-female 65 x 65 x 137 cm1,8 kg RAL 703550 Ω nominal AluminiumA S 05-F E N -60801 - S p e c i fi c a t i o n s s u b j e c t t o c h a n g e s w i t h o u t p r i o r n o t i c eAS-05Antenna set 30 MHz to 18 GHzLP-04200 MHz to 6 GHz 6 dBi typical 12 to 40 dB/m typical100 W N-female 78 x 10 x 75 cm 1,1 kg RAL 703550 Ω nominal AluminiumDR-016 to 18 GHz 9 to 16 dBi typical 36 to 41 dB/m typical 150 W N-female 55 x 44 x 177 mm 0,25 kg RAL 703550 Ω nominal AluminiumBC-01 - Antenna Factor 106141822A F (d B /m )3090150210MHz MHz MHz MHz LP-04 - Antenna Factor 155253545A F (d B /m )1356GHzGHz GHz GHz DR-01 - Antenna Factor3634384042A F (d B /m )6101418GHzGHz GHz GHz。

AT28HC64B高性能电擦可编程只读存储器(EEPROM)说明书

Features Array•Fast Read Access Time – 70 ns•Automatic Page Write Operation–Internal Address and Data Latches for 64 Bytes•Fast Write Cycle Times–Page Write Cycle Time: 10 ms Maximum (Standard)2 ms Maximum (Option – Ref. AT28HC64BF Datasheet)–1 to 64-byte Page Write Operation•Low Power Dissipation–40 mA Active Current–100µA CMOS Standby Current•Hardware and Software Data Protection•DATA Polling and Toggle Bit for End of Write Detection•High Reliability CMOS Technology–Endurance: 100,000 Cycles–Data Retention: 10 Years•Single 5 V ±10% Supply•CMOS and TTL Compatible Inputs and Outputs•JEDEC Approved Byte-wide Pinout•Industrial Temperature Ranges•Green (Pb/Halide-free) Packaging Option Only1.DescriptionThe AT28HC64B is a high-performance electrically-erasable and programmable read-only memory (EEPROM). Its 64K of memory is organized as 8,192 words by 8 bits. Manufactured with Atmel’s advanced nonvolatile CMOS technology, the device offers access times to 55 ns with power dissipation of just 220 mW. When the device is deselected, the CMOS standby current is less than 100µA.The AT28HC64B is accessed like a Static RAM for the read or write cycle without the need for external components. The device contains a 64-byte page register to allow writing of up to 64 bytes simultaneously. During a write cycle, the addresses and 1 to 64 bytes of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the device will automatically write the latched data using an internal control timer. The end of a write cycle can be detected by DATA polling of I/O7. Once the end of a write cycle has been detected, a new access for a read or write can begin.Atmel’s AT28HC64B has additional features to ensure high quality and manufactura-bility. The device utilizes internal error correction for extended endurance and improved data retention characteristics. An optional software data protection mecha-nism is available to guard against inadvertent writes. The device also includes anextra 64 bytes of EEPROM for device identification or tracking.20274L–PEEPR–2/3/09AT28HC64B2.Pin Configurations2.128-lead SOIC Top ViewPin Name Function A0 - A12Addresses CE Chip Enable OE Output Enable WE Write Enable I/O0 - I/O7Data Inputs/Outputs NC No Connect DCDon’t Connect2.232-lead PLCC Top ViewNote:PLCC package pins 1 and 17 are Don’t Connect.2.328-lead TSOP Top View30274L–PEEPR–2/3/09AT28HC64B3.Block Diagram4.Device Operation4.1ReadThe AT28HC64B is accessed like a Static RAM. When CE and OE are low and WE is high, the data stored at the memory location determined by the address pins is asserted on the out-puts. The outputs are put in the high-impedance state when either CE or OE is high. This dual line control gives designers flexibility in preventing bus contention in their systems.4.2Byte WriteA low pulse on the WE or CE input with CE or WE low (respectively) and OE high initiates a write cycle. The address is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the first rising edge of CE or WE. Once a byte write has been started, it will automatically time itself to completion. Once a programming operation has been initiated and for the duration of t WC , a read operation will effectively be a polling operation.4.3Page WriteThe page write operation of the AT28HC64B allows 1 to 64 bytes of data to be written into the device during a single internal programming period. A page write operation is initiated in the same manner as a byte write; after the first byte is written, it can then be followed by 1 to 63 additional bytes. Each successive byte must be loaded within 150 µs (t BLC ) of the previous byte. If the t BLC limit is exceeded, the AT28HC64B will cease accepting data and commence the internal programming operation. All bytes during a page write operation must reside on the same page as defined by the state of the A6 to A12 inputs. For each WE high-to-low transition during the page write operation, A6 to A12 must be the same.The A0 to A5 inputs specify which bytes within the page are to be written. The bytes may be loaded in any order and may be altered within the same load period. Only bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not occur.4.4DATA PollingThe AT28HC64B features DATA Polling to indicate the end of a write cycle. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data to be presented on I/O7. Once the write cycle has been completed, true data is valid on all outputs, and the next write cycle may begin. DATA Polling may begin at any time during the write cycle.40274L–PEEPR–2/3/09AT28HC64B4.5Toggle BitIn addition to DATA Polling, the AT28HC64B provides another method for determining the end of a write cycle. During the write operation, successive attempts to read data from the device will result in I/O6 toggling between one and zero. Once the write has completed, I/O6 will stop toggling, and valid data will be read. Toggle bit reading may begin at any time during the write cycle.4.6Data ProtectionIf precautions are not taken, inadvertent writes may occur during transitions of the host system power supply. Atmel ® has incorporated both hardware and software features that will protect the memory against inadvertent writes.4.6.1Hardware ProtectionHardware features protect against inadvertent writes to the AT28HC64B in the following ways: (a) V CC sense – if V CC is below 3.8 V (typical), the write function is inhibited; (b) V CC power-on delay – once V CC has reached 3.8 V, the device will automatically time out 5 ms (typical) before allowing a write; (c) write inhibit – holding any one of OE low, CE high or WE high inhib-its write cycles; and (d) noise filter – pulses of less than 15 ns (typical) on the WE or CE inputs will not initiate a write cycle.4.6.2Software Data ProtectionA software-controlled data protection feature has been implemented on the AT28HC64B. When enabled, the software data protection (SDP), will prevent inadvertent writes. The SDP feature may be enabled or disabled by the user; the AT28HC64B is shipped from Atmel with SDP disabled.SDP is enabled by the user issuing a series of three write commands in which three specific bytes of data are written to three specific addresses (refer to the “Software Data Protection Algorithm” diagram on page 10). After writing the 3-byte command sequence and waiting t WC , the entire AT28HC64B will be protected against inadvertent writes. It should be noted that even after SDP is enabled, the user may still perform a byte or page write to the AT28HC64B. This is done by preceding the data to be written by the same 3-byte command sequence used to enable SDP.Once set, SDP remains active unless the disable command sequence is issued. Power transi-tions do not disable SDP, and SDP protects the AT28HC64B during power-up and power-down conditions. All command sequences must conform to the page write timing specifica-tions. The data in the enable and disable command sequences is not actually written into the device; their addresses may still be written with user data in either a byte or page write operation.After setting SDP, any attempt to write to the device without the 3-byte command sequence will start the internal write timers. No data will be written to the device, however. For the dura-tion of t WC , read operations will effectively be polling operations.4.7Device IdentificationAn extra 64 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12 V ±0.5 V and using address locations 1FC0H to 1FFFH, the additional bytes may be written to or read from in the same manner as the regular memory array.50274L–PEEPR–2/3/09AT28HC64BNotes:1.X can be VIL or VIH.2.See “AC Write Waveforms” on page 8.3.VH = 12.0 V ±0.5 V.Note:1.I SB1 and I SB2 for the 55 ns part is 40 mA maximum.5.DC and AC Operating RangeAT28HC64B-70AT28HC64B-90AT28HC64B-120Operating Temperature (Case)-40°C - 85°C -40°C - 85°C -40°C - 85°C V CC Power Supply5 V ±10%5 V ±10%5 V ±10%6.Operating ModesMode CE OE WE I/O Read V IL V IL V IH D OUT Write (2)V IL V IH V IL D IN Standby/Write Inhibit V IH X (1)X High ZWrite Inhibit X X V IH Write Inhibit X V IL X Output Disable X V IH XHigh ZChip Erase V ILV H (3)V IL High Z7.Absolute Maximum Ratings*Temperature Under Bias................................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityStorage Temperature.....................................-65°C to +150°C All Input Voltages(including NC Pins)with Respect to Ground.................................-0.6 V to +6.25 V All Output Voltageswith Respect to Ground...........................-0.6 V to V CC + 0.6 V Voltage on OE and A9with Respect to Ground..................................-0.6 V to +13.5V8.DC CharacteristicsSymbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0 V to V CC + 1 V 10µA I LO Output Leakage Current V I/O = 0 V to V CC10µA I SB1V CC Standby Current CMOS CE = V CC - 0.3 V to V CC + 1 V 100(1)µA I SB2V CC Standby Current TTL CE = 2.0 V to V CC + 1 V 2(1)mA I CC V CC Active Current f = 5 MHz; I OUT = 0 mA40mA V IL Input Low Voltage 0.8V V IH Input High Voltage 2.0V V OL Output Low Voltage I OL = 2.1 mA 0.40V V OH Output High VoltageI OH = -400 µA2.4V60274L–PEEPR–2/3/09AT28HC64B10.AC Read Waveforms (1)(2)(3)(4)Notes:1.CE may be delayed up to t ACC - t CE after the address transition without impact on t ACC .2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE or by t ACC - t OE after an address changewithout impact on t ACC .3.t DF is specified from OE or CE whichever occurs first (C L = 5 pF).4.This parameter is characterized and is not 100% tested.9.AC Read CharacteristicsSymbol ParameterAT28HC64B-70AT28HC64B-90AT28HC64B-120Units MinMax MinMax MinMax t ACC Address to Output Delay 7090120ns t CE (1)CE to Output Delay 7090120ns t OE (2)OE to Output Delay 035040050ns t DF (3)(4)OE to Output Float 035040050ns t OHOutput Hold00ns70274L–PEEPR–2/3/09AT28HC64B11.Input Test Waveforms and Measurement Level12.Output Test LoadNote:1.This parameter is characterized and is not 100% tested.R F 13.Pin Capacitancef = 1 MHz, T = 25°C (1)Symbol Typ Max Units Conditions C IN 46pF V IN = 0 V C OUT 812pFV OUT = 0 V815.AC Write Waveforms15.1WE Controlled15.2CE Controlled14.AC Write CharacteristicsSymbol ParameterMin MaxUnits t AS , t OES Address, OE Setup Time 0ns t AH Address Hold Time 50ns t CS Chip Select Setup Time 0ns t CH Chip Select Hold Time 0ns t WP Write Pulse Width (WE or CE)100ns t DS Data Setup Time 50ns t DH , t OEHData, OE Hold Timens90274L–PEEPR–2/3/09AT28HC64B17.Page Mode Write Waveforms (1)(2)Notes: 1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE).2.OE must be high only when WE and CE are both low.18.Chip Erase Waveformst S = t H = 5 µs (min.)t W = 10 ms (min.)V H = 12.0 V ±0.5 V16.Page Mode CharacteristicsSymbol Parameter MinMax Units t WC Write Cycle Time10ms t WC Write Cycle Time (Use AT28HC64BF))2ms t AS Address Setup Time 0ns t AH Address Hold Time 50ns t DS Data Setup Time 50ns t DH Data Hold Time 0ns t WP Write Pulse Width 100ns t BLC Byte Load Cycle Time 150µs t WPHWrite Pulse Width High50ns100274L–PEEPR–2/3/09AT28HC64B19.Software Data Protection EnableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4.1 to 64 bytes of data are loaded.20.Software Data Protection DisableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4. 1 to 64 bytes of data are loaded.21.Software Protected Write Cycle Waveforms (1)(2)Notes:1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE) after the softwarecode has been entered.2.OE must be high only when WE and CE are both low.11AT28HC64BNote:1.These parameters are characterized and not 100% tested. See “AC Read Characteristics” on page 6.23.Data Polling WaveformsNotes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 6.25.Toggle Bit Waveforms (1)(2)(3)Notes: 1.Toggling either OE or CE or both OE and CE will operate toggle bit.2.Beginning and ending state of I/O6 will vary.3.Any address location may be used, but the address should not vary.22.Data Polling Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 0ns t OEH OE Hold Time 0ns t OE OE to Output Delay (1)ns t WR Write Recovery Timens24.Toggle Bit Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 10ns t OEH OE Hold Time 10ns t OE OE to Output Delay (2)ns t OEHP OE High Pulse 150ns t WR Write Recovery Timens12AT28HC64B26.Normalized I CCGraphs13AT28HC64B27.Ordering Information27.1Green Package Option (Pb/Halide-free)t ACC (ns)I CC (mA)Ordering Code Package Operation RangeActive Standby 70400.1AT28HC64B-70TU 28T Industrial (-40°C to 85°C)AT28HC64B-70JU 32J AT28HC64B-70SU 28S 90400.1AT28HC64B-90JU 32J AT28HC64B-90SU 28S AT28HC64B-90TU 28T 120400.1AT28HC64B-12JU 32J AT28HC64B-12SU28SPackage Type32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)28T28-lead, Plastic Thin Small Outline Package (TSOP)27.2Die ProductsContact Atmel Sales for die sales options.28.Packaging Information 28.132J – PLCC14AT28HC64BAT28HC64B 28.228S – SOIC1528.328T – TSOP16AT28HC64BHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2009 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

一种高吞吐低延迟片上互连网络路由器

第50 卷第 8 期2023年8 月Vol.50,No.8Aug. 2023湖南大学学报(自然科学版)Journal of Hunan University(Natural Sciences)一种高吞吐低延迟片上互连网络路由器李晋文†,申慧毅,齐树波(国防科技大学计算机学院,湖南长沙 410073)摘要:本文提出了一种用于片上互连网络的低延迟高吞吐量动态虚拟输出队列路由器,该路由器可以利用前瞻路由计算和虚拟输出队列方案将路由器延迟减低到两个周期.仿真结果表明,与虫孔路由器和虚通道路由器相比,4×4网格上的网络吞吐量分别提高了46.9%和28.6%,并且在相同输入加速比下,性能比双缓冲虚通道路由器要高1.9%.在随机合成流量下,片上网络的零负载延迟也分别降低了25.6%和41%.设计实现结果表明,路由器的工作频率可以达到2.5 GHz.关键词:片上网络;路由器;吞吐量;延迟中图分类号:TN913.3 文献标志码:AA High-throughpur Low-latency Router for On-chip InterconnectNetworksLI Jinwen†,SHEN Huiyi,QI Shubo(School of Computer Science, National University of Defense Technology, Changsha 410073, China)Abstract:A low-latency high-throughput Dynamic Virtual Output Queues Router for On-chip interconnect networks is proposed in this paper,which can reduce the router latency to two cycles by leveraging look-ahead routing computation and virtual output queues scheme. The simulation results show that,compared with the wormhole router and virtual-channel router, the network throughput on a 4×4 mesh increases by up to 46.9% and 28.6%, respectively, and outperforms doubled buffer virtual channel by 1.9% under the same input speedup. Under random synthetic traffic,the zero-load-latency of the network on chip is also reduced by 25.6% and 41%,respectively. Synthesis results indicate the frequency of router can reach 2.5 GHz.Key words:on-chip network;router;throughput;latency随着半导体技术的飞速发展,越来越多的处理器核(多核和众核)集成在单个芯片上,而随着MOS 管尺寸的不断缩小,门级电路延迟在不断缩小,全局互连线的延迟相对于MOS管延迟还在不断增加.微∗收稿日期:2022-11-03基金项目:HPCL国家重点实验室基金项目(202101-02);国家自然科学基金资助项目(60873212),National Natural Science Foundation of China(60873212)作者简介:李晋文(1975—),男,山西武乡人,国防科技大学研究员,博士† 通信联系人,E-mail:*****************文章编号:1674-2974(2023)08-0141-06DOI:10.16339/ki.hdxbzkb.2023289湖南大学学报(自然科学版)2023 年处理器体系结构设计的重点正在从以提高计算为中心的单核能力设计转向以互连通信为中心的多核设计.由于互连延迟可预测、设计复杂度比较低、易扩展性和结构规整,片上网络已成为CMP和MPSoC中片上众核互连最有前途的选择[1].其中2D mesh互连网络已广泛应用于许多原型芯片,如Intel 80核Tera⁃flop、Tilera 64核和TRIPS[2-4].片上网络的概念来源于多处理器间互连网络,但实际与多芯片间互连网络有着许多不同的特点.最重要的一点,芯片内互连线和引脚比芯片间网络中的互连线和引脚资源更丰富[1].然而,片上网络中缓冲buffer容量不足.网络的延迟对实际多核的计算性能有很大影响.当路由器的每跳延迟从一个周期增加到五个周期时,全系统的性能将下降10%[5].基准的虚通道路由器的流水线级数为4.近年来,业界提出了几种新型架构的低延迟路由器,包括推测虚通道路由器[6]、采用虫孔交换的两虚通道结构路由器[7]、混合电路交换路由器[5]、带bundle的两周期路由器[8]、组合型两周期路由器[9]、无缓存片上路由器[10]、基于时间序列开关分配路由器[11]以及关键路径延迟只有35个FO4[12]的单周期路由器(FO4是指一个反相器驱动四个相同尺寸反相器产生的延迟,高性能微处理器的周期一般约为20个FO4).缓冲buffer的实现对互连网络的性能至关重要.缓冲buffer可以用寄存器或SRAM来实现.在芯片中,通常缓冲buffer的容量相对较小,因此使用低延迟的寄存器实现更为有利,而使用SRAM会存在较大的地址译码延迟以及存储阵列访问延迟,这些延迟与全局位线相关;此外还能节省位线预充电功耗[13].在标准的虚通道路由器中,每个虚通道都需要自带缓冲buffer,一个虚通道无法使用其他虚通道的缓冲buffer[14].DAMQ路由器设立了5个缓冲buffer队列,每个队列对应一个虚通道,多出的一个队列作为共享缓冲buffer,一个报文flit从到达到离开路由器需要3个时钟周期[15].VichaR路由器能够根据数据流量(traffic)来调节和分配每个物理通道的虚通道和缓冲buffer数量,并使用复杂的VC控制表来管理报文flit,能够有效提高缓冲buffer的使用效率,其缺点是路由器延迟会达到四个时钟周期.当路由器中发生拥塞时,无论是采用基于信用还是基于开关的流控策略,通道流水线中的缓冲buffer都不能用于缓冲flit.iDEAL路由器提出用中继器(repeater)电路来缓冲flit报文[16],然而中继器存在较大漏流问题,会导致不可靠.本文提出了一种新型的两周期路由器——动态虚通道输出队列路由器(DVOQR),采用多端口缓冲buffer和虚拟输出队列来消除虚通道路由器中的分配站(allocation stage).采用Ready/Valid握手机制来控制路由器之间的flit流,在这种策略下,流水线通道中的存储器可以用于缓冲flit报文.本文其余部分组织如下,第1节介绍了路由器的微架构.第2节给出了路由器的具体设计实现.第3节分析了模拟结果.最后,第4节对本文工作进行了简要总结.1 路由器微架构1.1 DVOQR路由器微架构本文提出了一种新型动态虚通道输出队列路由器(DVOQR),其微架构如图1所示.路由器包括P个输入端口和P个输出端口.对于二维mesh网络,P= 5;一个端口连接到本地处理器(核),其他端口连接到相邻路由器.输入单元由三个主要模块组成:集中动态缓冲器(Unified Dynamic Buffer,UDB)、集中动态缓冲分配器(Unified Dynamic Buffer Allocation,UDBA)、P个虚拟输出地址队列(Virtual Ouput Address Queue,以下简称VOAQ).输出端口包括一个P选1的仲裁器和一个P输入的多路复用器.由多个flit组成1个数据报文,存储在同一FIFO队列中,路由到同一输出端口.每个输入端口有P个FIFO队列,它们共享一个UDB并各自带一个私有的VOAQ.每个FIFO中flit的地址存储在虚拟输出地址队列(VOAQ)中.这样一来,就可以有效消除队列头阻塞(HOL)延迟问题[17].芯片间网络路由器中的缓冲buffer一般使用SRAM来实现.大容量的多端口SRAM存储器由于需要较大的面积开销、较高的功耗和访问延迟而难以实现,而使用小容量的寄存器来实现多端口缓冲器buffer要容易得多.受片上资源的限制,UDB用低延迟的多端口寄存器实现,具有1个写端口和P个读端口.每个读端口对应1个FIFO队列.尽管使用多个端口会导致面积开销增加,但可以消除虚通道路由器流水线的分配站.连接到输出端口的CDB,由CDB控制器和两项142第 8 期李晋文等:一种高吞吐低延迟片上互连网络路由器寄存器组成,如图2(a )所示.其中一个寄存器负责接收来自路由器的flit ,而另一个寄存器负责将flit 发送到下一个路由器,一收一发.在下一个周期中,两个寄存器交换收发功能.因此CDB 可以同时接收和发送flit ,可以避免流水线产生气泡.图2(b )给出了CDB 控制器的实现电路.state [1:0]表征两个寄存器的状态.读指针rd_ptr 对应发送寄存器,写指针wr_ptr 对应接收寄存器.当路由器之间的线延迟超过一个时钟周期时,可以插入多个CDB.UDBA 用于为队列分配时隙或释放空时隙.使用状态向量来跟踪所有时隙的状态,1表示时隙可用.当时隙分配给flit 时,相应的位将被清掉.采用固定优先级仲裁器以简化分配逻辑,最低可用时隙将被分配最高的优先级.设计了四个物理VOAQ 来缓存同一队列中的flit.当某一个flit 注入UDB 时,UDBA 负责将分配给它的时隙号写入对应的VOAQ ,该VOAQ 还会保存该报文的路由信息以及flit 类型.在UDB 读操作之前,需要首先从VOAQ 中读出UDB 中flit 的地址,这将增加UDB 的访问延迟.本文设计了一种新颖的移位FIFO ,可以有效减少UDB 的读延迟.图3给出了VOAQ 的微架构,使用one-hot 向量来指向FIFO 的尾部,而第一项指向FIFO 的头部.尾向量的宽度比UDB 的深度D 要大1.当tail_vector [0]为1时,FIFO 为空;而tail_vector [D ]等于1时,FIFO 为满.当头数图1 DVOQR 路由器微架构Fig.1 Microarchitecture of DVOQR(a )Architecture of channel double buffer(b ) Channel double buffer controller图2 通道的双缓存控制器Fig.2 Channel double buffer controller143湖南大学学报(自然科学版)2023 年据离开队列时,VOAQ 中的其他数据将向前移一位,而tail_vector 将进行右移.当新数据到达时,数据将被添加到VOAQ 的尾部,并且tail_vector 左移1位.当新数据在同一时钟周期内到达和离开时,tail_vector 将不发生移位.DVOQR 中的交换分配单元使用P 个round-robin 仲裁器实现.交换分配单元只需要一级仲裁,即可实现最大匹配,从而提高路由器吞吐量并降低分配延迟.1.2 DVOQR 流水线设计DVOQR 路由器的流水线由两站组成:flit 交换站(Flit Switch ,FS )和链路传输站(Link Traversal ,LT ).FS 站:完成交叉开关分配、前瞻路由计算、UDB读操作和Crossbar 传输.其中交叉开关分配、前瞻路由计算和UDB 读操作能够并行.当VOAQ 的第一项是head flit 报文片时,会为目的仲裁器产生一个请求信号.同时,发送VOAQ 中的flit 地址到UDB ,启动读操作,根据报文的路由信息,采用维序路由算法进行路由的前瞻计算.如果请求未被批准,将在下一个周期中重试,而不需要再次读取flit 报文.LT 站:在这一站中,flit 通过物理链路发送并写入UDB ,并根据FS 站的前瞻路由计算结果,将分配给flit 的地址写入VOAQ 中.1.3 流控机制DVOQR 使用了一种新的流控机制,称为ready-valid 握手机制(handshake ).ready 输出表示UDB/CDB 有可用的存储来接收flit 报文.valid 信号标识当前的flit 报文是有效的.当ready 和valid 信号在同一个周期内有效时,说明flit 报文已经提交.当下一级路由器发生拥塞时,链路上流水线中的CDB 可以缓冲flit 报文,这等效于增加了缓冲buffer 容量.基于维序路由算法,这种流控机制可以有效避免死锁.2 设计实现基于RTL 设计实现了用于片上2D mesh 网络的DVOQR 路由器,数据位宽128位,带有16项UDB ,评估了路由器的性能和功耗,综合生成门级网表,并对时序进行了详细的分析.FS 站和LT 站的关键路径延迟分别为400 ps (11.4 FO4)和252 ps (7.2 FO4),该工艺下的FO4为35 ps.表1给出了路由器中各功能部件的面积和功耗.3 模拟结果3.1 模拟方法本文采用随机人工合成流量模型评估互连网络的性能.表2给出了模拟实验的参数设置.采用周期精确模拟器Booksim [14]来评估虫孔路由器(Worm⁃hole Router ,WH )和虚通道路由器(Virtual-channel Router ,VC ).本文使用Verilog HDL 设计实现了DVOQR 的RTL 模型.测试程序采用随机通讯的合成程序,进行了仿真模拟,预热时间为1万个时钟周期,测量时间为10万个时钟周期.3.2 模拟结果分析3.2.1 不同缓冲容量的影响图4为带16项UDB 的DVOQR 路由器在随机流量负载下的平均延迟曲线.虫孔路由器和虚信道路由器中的输入缓冲buffer 数量为16~64 flit.与其他两种路由器相比,DVOQR 的吞吐量分别增加了33.2%和12%,而其他路由器缓冲buffer 的容量是DVOQR 的3倍.因此,DVOQR 可以更有效地使用输入缓冲器.其中,三种路由器的零负载延迟分别为10.4、14.0和17.7.表1 路由器中各功能部件的面积和功耗Tab.1 Area and power consumption of each functionalcomponent模块UDBVOAQinput portoutput port CDBrouter 组合逻辑面积/(μm )218 9452 49629 7311 5102 236167,385时序逻辑面积/(μm )231 47531 6844 0931133 065221,595总面积/(μm )250 4205 66473 8241 6235 301403,740功耗/mW58.87.589.30.60312.1507.5数量/个5205551图3 VOAQ 的微架构Fig.3 Microarchitecture of virtual ouput address queue144第 8 期李晋文等:一种高吞吐低延迟片上互连网络路由器3.2.2 相同输入加速比UDB 有四个读端口,因此DVOQR 的输入加速比是4.图5给出了在随机流量负载相同输入加速比时的平均延迟曲线.与VC_4×4和VC_4×8相比,VOQ_16的吞吐率分别增加17.6% 和1.9%,而VC_8×8 和VC_8×16的吞吐率分别比VOQ_16要高2.9%和7.5%.DVOQR 吞吐率比双缓冲虚通道路由器要高1.9%.在相同的输入加速比下,采用动态缓冲buffer分配只需要一半的buffer 容量就能达到相同的吞吐率.3.2.3 UDB 深度的影响图6给出了随机流量下DVOQR 网络性能与UDB 深度的相关性.2项UDB 的网络饱和点约为50%,16项UDB 的饱和点可达到82.4%.当UDB 的深度大于8时,吞吐率的增加随着UDB 深度的增加速度放缓.当注入流量小于0.4时,采用不同深度UDB 的平均延迟几乎是相同的.可以根据网络流量打开或关闭一部分UDB ,这样可以有效减少缓冲buffer 的漏流功耗.事实上,缓冲buffer 产生的漏流功耗是整个NoC 路由器漏流功耗的最主要来源.3.2.4 报文长度的影响图7给出了随机流量下带16项UDB 的DVOQR平均延迟与数据报文长度的关系,报文长度为2~32个flit.吞吐率随着报文长度的增加而降低.报文长度为32 flit 和2 flit 网络的饱和点分别为57.5%和87.5%.报文长度进一步增加将导致阻塞,因此需要占用更多的物理通道,而且竞争增加将导致更大的延迟.图7 对应不同报文长度下DVOQR 平均延迟Fig.7 Average latency of DVOQR under differentmessage lengths表2 模拟参数设置Tab.2 Simulation parameter settingsnetwork路由算法报文长度流量注入DVOQR 路由器虫孔路由器(WH )虚通道路由器(VC )4×4 meshdimension-order routing four flitsBernoulli processtwo-stage pipeline ,the depth of UDB is 16 for VOQ_16three-stage pipeline ,the depth of buffer is 16 for WH_16.four-stage pipeline ,the channel number is 4 and the depth of buffer in channel is 8for VC_4×8.图4 不同buffer 容量的DVOQR 路由器平均延迟Fig.4 Average latency of DVOQR with different buffer capacities图5 相同输入加速比下DVOQR 平均延迟Fig.5 Average latency of DVOQR under the sameinput acceleration ratio图6 不同深度UDB 的DVOQR 的平均延迟Fig.6 Average latency of DVOQR with different UDB145湖南大学学报(自然科学版)2023 年4 结论本文提出了一种基于ready-valid握手流控策略的两级流水线片上互连网络路由器,该路由器采用维序路由可以避免死锁.与虫孔路由器和虚通道路由器相比,4×4 mesh网络中的网络吞吐量分别提高了46.9%和28.6%,并且在相同的输入加速比下,DVOQR路由器比双缓冲虚通道路由器性能提高了1.9%.综合结果表明,路由器的时钟频率可达2.5 GHz.参考文献[1]DALLY W J,TOWLES B.Route packets,not wires:on-chip interconnection networks[C]//Proceedings of the 38th DesignAutomation Conference .Las Vegas,NV,USA:IEEE,2005:684-689.[2]VANGAL S,HOWARD J,RUHL G,et al.An 80-tile 1.28TFLOPS network-on-chip in 65nm CMOS[C]//2007 IEEE InternationalSolid-State Circuits Conference. San Francisco,CA,USA:IEEE,2007:98-589.[3]GRATZ P,KIM C,SANKARALINGAM K,et al.On-chip interconnection networks of the TRIPS chip[J].IEEE Micro,2007,27(5):41-50.[4]WENTZLAFF D,GRIFFIN P,HOFFMANN H,et al.On-chip interconnection architecture of the tile processor[J].IEEE Micro,2007,27(5):15-31.[5]JERGER N E,LIPASTI M,PEH L S.Circuit-switched coherence [J].IEEE Computer Architecture Letters,2007,6(1):5-8.[6]PEH L S,DALLY W J.A delay model and speculative architecture for pipelined routers[C]//Proceedings HPCA SeventhInternational Symposium on High-Performance ComputerArchitecture. Monterrey,Mexico:IEEE,2002:255-266.[7]胡哲琨,陈杰.消息传递型片上多核系统的设计[J].湖南大学学报(自然科学版),2013,40(8):102-109.HU Z K,CHEN J.Design of a message-passing multi-core system[J].Journal of Hunan University (Natural Sciences),2013,40(8):102-109.(in Chinese)[8]KUMARY A,KUNDUZ P,SINGHX A P,et al.A 4.6Tbits/s3.6GHz single-cycle NoC router with a novel switch allocator in65nm CMOS[C]//2007 25th International Conference onComputer Design. Lake Tahoe,CA,USA:IEEE,2008:63-70.[9]TIWARI V , KHARE K , SHANDILYA S . An efficient 4×4 mesh structure with a combination of two NoC router architecture[J].International Journal of Sensors,Wireless Communication andControl, 2021,11(2):169-180.[10]CHIOU S Y . Bufferless routing algorithms:a survey[J].Advances in Computational Sciences and Technology,2018,11(5):381-386.[11]李存禄,董德尊,吴际,等.低延迟路由器中高效开关分配机制的实现与评测[J].湖南大学学报(自然科学版),2015,42(4):78-84.LI C L,DONG D Z,WU J,et al.Design and implementation ofefficient switching in low-latency router[J].Journal of HunanUniversity (Natural Sciences),2015,42(4):78-84.(in Chinese)[12]MULLINS R,WEST A,MOORE S.The design and implementation of a low-latency on-chip network[C]//Proceedings of the 2006Asia and South Pacific Design Automation Conference.New York:ACM,2006:164-169.[13]HU J C,MARCULESCU R.Energy- and performance-aware mapping for regular NoC architectures[J].IEEE Transactions onComputer-Aided Design of Integrated Circuits and Systems,2005,24(4):551-562.[14]MULLINS R,WEST A,MOORE S.The design and implementation of a low-latency on-chip network[C]//Proceedings of the 2006Asia and South Pacific Design Automation Conference.New York:ACM,2006:164-169.[15]TAMIR Y,FRAZIER G L.High-performance multiqueue buffers for VLSI communication switches[C]//[1988]The 15th AnnualInternational Symposium on Computer Architecture.Honolulu,HI,USA: IEEE,2002:343-354.[16]KODI A,SARATHY A,LOURI A.Design of adaptive communication channel buffers for low-power area-efficientnetwork-on-chip architecture[C]//Proceedings of the 3rd ACM/IEEE Symposium on Architecture for Networking andCommunications Systems.New York:ACM,2007:47-56.[17]KAROL M,HLUCHYJ M,MORGAN S.Input versus output queueing on a space-division packet switch[J].IEEE Transactionson Communications,1987,35(12):1347-1356.146。

2.4GHz无线网络或WIFI频段螺旋天线

Helical/helix antenna cookbook recipe for 2.4 GHz wavelans and/or WiFi applications2.4GHz无线网络或WIFI频段应用螺旋状/螺旋结构天线烹饪菜谱by Dr. Remco den Besten, PA3FYM (mail: helix at )Remco den Besten 博士,PA3FYM (mail: helix at )Bookmark/refer to this page as I innocently made this cookbook recipe and placed it on my local ADSL-connected machine, never expecting that so many of you want to have this information. This (co-located) bandwidth is kindly donated by ds9a.nl本页链接是。

本人无偿制作此烹饪菜谱,放在我的本地ADSL连接机器,一点也不介意众多像你一样的人想拥有这一资料。

本文存储空间由ds9a.nl友情提供。

If you have IPv6 connectivity, look here(co-located at ISP Services.nl) 如果你有IPv6连接结点,请看这里(存储在ISP Services.nl )If you want to listen to MP3 audio streams using IPv6 as transport layer look here ( <- accessible with IPv4).如果你使用Ipv6做为传输层想收听MP3请看这里(<-用Ipv4很容易取得)。

Abstract摘要The helix antenna, invented in the late fourties(疑为forties-译者注)by John Kraus (W8JK), can be considered as the genious(疑为genius-译者注) ultimate simplicity as far as antenna design is concerned. Especially for frequencies in the range 2 - 5 GHz this design is very easy, practical, and, non critical. This contribution describes how to produce a helix antenna for frequencies around 2.4 GHz which can be used for e.g. high speed packet radio (S5-PSK, 1.288 Mbit/s), 2.4 GHz wavelans, and, amateur satellite (AO40). Developments in wavelan equipment result in easy possibilities for high speed wireless internet access using the 802.11b (aka WiFi) standard.螺旋天线,是四十年代末期由John Kraus (W8JK)发明的,被推崇为天才的到目前为止最简单的天线设计而受到关注。

60 GHz SIW Steerable Antenna Array in LTCC

60 GHz SIW Steerable Antenna Array in LTCC Bahram Sanadgol;Sybille Holzwarth;Peter Uhlig;Alberto Milano;Raft Popovich【期刊名称】《中兴通讯技术(英文版)》【年(卷),期】2012(010)004【摘要】In this paper, we present a 60 GHz substrate-integrated waveguide fed-steerable low-temperature cofired ceramics array. The antenna is suitable for transmitting and receiving on the 60 GHz wireless personal area network frequency band. The wireless system can be used for HDTV, high-data-rate networking up to 4.5 GBit/s, security and surveillance, and similar applications.【总页数】4页(P29-32)【关键词】天线阵列;GHz;LTCC;操纵;低温共烧陶瓷;高清晰度电视;区域网络;无线系统【作者】Bahram Sanadgol;Sybille Holzwarth;Peter Uhlig;Alberto Milano;Raft Popovich【作者单位】IMST GmbH CarI-Friedrich-Gauss-Str. 2, 47475 Kamp-Lintfort, Germany;IMST GmbH CarI-Friedrich-Gauss-Str. 2, 47475 Kamp-Lintfort, Germany;IMST GmbH CarI-Friedrich-Gauss-Str. 2, 47475 Kamp-Lintfort, Germany;Beam Networks, 1 Ehad Ha'am 76248 Rehovot, Israel;Beam Networks, 1 Ehad Ha'am 76248 Rehovot, Israel【正文语种】中文【中图分类】TN820.15;TP332因版权原因,仅展示原文概要,查看原文内容请购买。

TACO天线资料

Lightning Rod “Option”

Military Mounts

D2000 Series High Gain

Key Models:

D2266 – 225-400 MHz, 7.5 dBi

Gain, 1 Output

D2267 – 225-400 MHz, 5.5 dBi Gain, 1 Output

D2000 Series Multiple Dipole

TACO Helical SystemWare Europe Installation

TACO Helical SystemWare Europe Installation

Portable UHF SATCOM

Designed for UHF portable quick deployment

ANTENNA OVERVIEW

WADE PRODUCT OVERVIEW

Commercial Antennas VHF UHF 900 MHz Wireless Applications Wi-Fi WiMax

2.4GHz 5.8 GHz Pure Log Periodic Arrays for Cable

Features: Metallic Base DC grounded dipoles Supplied to the FAA and NAV Canada VHF / UHF frequency Multiple Dipole similar to military models >30 dB isolation

RUCKUS ZF7025 ZF7055 ZF7321 ZF7352 Product Guide

—

Up to 15dB

Up to 15dB

Up to 15dB

Up to 15dB

Up to 15dB

Up to 15dB

Up to 15dB

—

Dual

Vertical

Dual

Dual

Dual

Vertical

Dual

Dual

-94/-95 dBm

✓ ✓

2

-94/-95 dBm

✓ ✓

2

-94/-95 dBm

SMARTCELL GATEWAY 200 (SCG-200)

Up to 10,000

Up to 100,000

50.8 cm (L), 45.53 cm (W), 8.76 cm (H) 40 Lbs. (18.14 kilograms) 2RU rack mountable Control: Six 10/100/1000 Mbps RJ-45 ports Data: two 10 GigE data ports Serial ports, RJ-45 (one front, one back) See Data Sheet Clientless 802.1X solution; Ruckus TTG-PDG gateway based tunneling offload; Wi-Fi edge network data offload (local breakout) 6,144 Incorporates on-board EAP-server enabling SIGTRAN based authentication with external HLR/HSS; RADIUS AAA proxy

✓

— 1

wireless产品介绍

WiHD Value Proposition

CABLE-FREE TV ELEGANCE WITH HIGHEST VIDEO QUALITY

ROBUST CONNECTION FOR MOBILE INTERACTIVE APPS TO LARGE DISPLAY

Confidential Information This Presentation is Provided Under NDA - Copyright © 2013 Silicon Image, Inc.

Tx, Rx Modules with HDMI interface for CE

SK63102A – Gen3 WirelessHD Tx Module SK63101A – Gen3 WirelessHD Rx Module

Applications

Sil6312

Transmitter Solution 6310 + 6320

14

Confidential Information This Presentation is Provided Under NDA - Copyright © 2013 Silicon Image, Inc.

UltraGig 6400 Applications

13

Wireless Video Technology Comparison

WirelessHD Miracast

Blockiness due to APU encode failures

Source content: GLBBenchmark 2.1 Egypt

Error message indicates poor wireless connection

英特尔收发器选型表

英特尔收发器选型表【原创版】目录1.英特尔收发器概述2.英特尔收发器的产品组合3.英特尔收发器的应用领域4.英特尔收发器的优势5.结论正文英特尔收发器概述英特尔收发器是一种用于光纤通信领域的高性能光器件,能将光信号和电信号进行相互转换,从而实现数据传输。

英特尔作为全球知名的科技公司,在光纤通信领域有着丰富的经验和技术积累,其收发器产品在市场上具有很高的知名度和竞争力。

英特尔收发器的产品组合英特尔收发器的产品组合丰富多样,涵盖了从 600 Mbps 到 30 Gbps 不等的数据速率,可以满足不同应用场景的需求。

同时,英特尔还提供高达 58 Gbps 的 PAM4 Gbps 收发器,其性能更为出色。

英特尔收发器的产品系列包括:1.英特尔 FPGA 收发器:采用集成收发器的英特尔 FPGA,可提供多种数据速率,适用于从 600 Mbps 到 30 Gbps 的不归零 (NRZ) 以及高达 58 Gbps 的 PAM4 Gbps 应用。

2.英特尔以太网收发器:英特尔以太网收发器支持多种数据速率和接口类型,适用于各种以太网应用,包括 1 Gbps、10 Gbps 和 100 Gbps 等。

3.英特尔光纤收发器:英特尔光纤收发器支持多种光纤接口和数据速率,具有高可靠性和低功耗等特点,适用于长距离光纤通信应用。

英特尔收发器的应用领域英特尔收发器广泛应用于各种电信、数据中心和工业领域,具体包括:1.电信领域:英特尔收发器可应用于光纤通信网络中的光纤接入、光纤传输和光纤分配等环节,实现高速、稳定的数据传输。

2.数据中心:英特尔收发器在数据中心中的应用主要包括数据存储、数据处理和数据传输等环节,可以提高数据中心的运行效率和可靠性。

3.工业领域:英特尔收发器在工业领域的应用包括工业自动化、机器人控制和智能制造等,可以提高工业生产的效率和可靠性。

英特尔收发器的优势英特尔收发器在光纤通信领域具有明显的优势,具体包括:1.高性能:英特尔收发器具有高数据传输速率和低信号衰减,能实现长距离、高速、稳定的光纤通信。

Sennheiser 双通道真正度双频道接收器说明书

FEATURES20 fixed frequency banks with up to64 compatible presets in up to 75 MHz switching bandwidth and 6 user banks Integrated antenna splitter for cas c adingup to 8 devices without using additional splittersRugged 19“ all-metal housing withintegrated power supply unitEthernet for monitoring and controlusing Sennheiser WSM Mac or PC soft-wareTransmitters can be configured in thereceiver menu and can be synchronized via the infrared interfaceEnhanced AF frequency response(25....18000 Hz) ARCHITECT’S SPECIFICATIONSThe device shall be a dual channel, true diversity (two tuners per receiver channel) receiver for use with two discrete companion transmitters as part of a high reliability, true diversity, dual channel wireless radio fre-quency transmission system. Each channel of the stationary receiver shall provide the following features and performance: The receiver shall operate within a RF frequen-cy range of 516 – 865 MHz in 20 fixed frequency banks and 6 user banks, each with a maximum of 64 presets with a switching bandwidth of maximum 75 MHz tunable in 25 kHz steps; carrier frequencies shall be maximum 3000. Squelch threshold shall be defeatable (off) or adjustable from 5 – 25 dBµV in 2dB steps. Nominal/peak deviation shall be ±24 kHz/±48 kHz. Intermodulation spacing shall be ≥75dB. A compander fea-ture shall be included and shall be Senn-heiser HDX system with pilot-tone squelch (switchable). Sensitivity shall be < 2.0 µV for 52 dBArms S/N with HDX engaged at peak deviation.Continued on page 2Equipped with the same features as EM 2000 but designed as a twin receiver, EM 2050 makes it possible for the RF signal to be looped through with the help of an integrated active splitter. With this design, you can set up systems with up to 16 channels without using external splitters. An integrated equalizer and guitar tuning device complete the package.TECHNICAL DATARF frequency range .............................................516 – 865 MHzCarrier frequencies ..............................................max. 3000Presets ................................................................... m ax. 64, max. 75 MHz, tuneable in25 kHz stepsNominal / Peak deviation...................................±24 kHz / ±48 kHzSquelch threshold ................................................ O ff, 5 – 25 dBµV: Can be set in2 dB stepsIntermodulation spacing ....................................≥ 75 dBSensitivity(with HDX, peak deviation) ...............................≤ 2 µV for 52 dBArms S/N Adjacent channel rejection ................................typ. ≥ 80 dBBlocking ................................................................≥ 80 dBAntenna connector ..............................................2 BNC (50 OHM)Cascadable ............................................................2 BNC (50 OHM)Gain ........................................................................ 0 dB ±0,5 dB : Based on antennainputsCompander ............................................................HDXFrequency response ............................................25 ... 18000 HzSignal-to-noise ratio ...........................................> 120 dB(A)THD, total harmonic distortion .........................< 0,9 %Audio-XLR connector ..........................................2 x XLR-3 + 2 x 6,3 mm: JackAudio output level (balanced) .......................... +18 dBu max : Setting range:49 dB in 1 dB steps + 6 dB gain reserve Booster Feed ......................................................... 12 V DC, 2 x 200 mA: Short-circuitproofContinued on page 2EM 2050 True Diversity Twin ReceiverARCHITECT’SSPECIFICATIONSAdjacent channel rejection shall be ≥80 dB (typical); blocking shall be ≥80dB. Audio frequency response shall be 25 – 18,000 Hz; to-tal harmonic distortion (THD) shall be <0.9 %. Audio frequency output level shall be adjustable within a 49dB range in 1dB steps to a maximum of level of +18dBu (balanced). Signal-to-noise ratio shall be > 120 dB(A). The audio output shall utilize a transformer-balanced male XLR-3 audio socket along with a transformer-balanced ¼“ (6.3 mm) audio socket; a stereo headphone output with local level control shall be provided on the front panel and shall utilize a ¼“ (6.3mm) stereo audio socket. Menu-based software adjustments shall be made using a backlit LCD user display; associated transmitters shall be configured in the receiver menu and synchronized with the receiver via an integrated infrared interface. Four selectable equalizer presets shall be provided. An integra-ted guitar tuner shall be provided. The following features and performance shall be provided to support both receiver channels: Two 50O BNC connectors shall provide attachment points for the main receiver antennae and two additional 50O BNC connectors with an integrated antenna splitter shall provide for cascading the antennae for up to 8 receivers without the use of external splitters; gain shall be 0dB ±0.5dB (based on antenna inputs). To supply active antennas or an antenna booster, a direct voltage of 12Vdc (200mA with short circuit protection) shall be provided via the antenna sockets. An Ethernet port (RJ45) shall be provided to allow remote network-based monitoring and control of the receiver using Sennheiser Wireless System Manager Mac or PC software. The receiver shall be fully compatible with all Sennheiser 2000 series and G3 transmitters; partial compatibility shall be provided for Sennheiser ew G2 and G1 transmitters. Power shall be supplied to the receiver by the internal power supply with auto-switching mains voltage of 100 – 240 VAC at 50/60 Hz. Current draw shall be maximum 0.25 A. The receiver chassis shall be fabricated from metal and shall be capable of mounting in a standard 19“ equipment rack without additional hardware; case dimensions shall be approximately 8.54“ x 19.02“ x 1.69“ (217 x 483 x 43 mm). Weight shall be 102.29 oz (2900 grams). Operating conditions shall be ambient temperature +14°F to +131°F (-10°C to +55°C). The dual channel receiver shall be Sennheiser model EM 2050. TECHNICAL DATAOperating temperature ......................................–10 °C – +55 °CPower supply ........................................................100 - 240 V AC, 50/60 HzCurrent consumption ..........................................max. 0,25 ADimensions ...........................................................217 x 483 x 43 mmWeight ...................................................................2900 gDELIVERy INCLuDES1 EM 2050 stationary twin receiver3 mains cables (Eu, uK, and uS)2 rod antennas4 self-adhesive device feet1 instruction manual1 supplementary frequency sheet1 supplementary RF power sheetSennheiser electronic GmbH & Co. KG Am Labor 1, 30900 Wedemark, Germany 0 3 / 1 2 S e n n h e i s e r i s a r e g i s t e r e d t r a d e m a r k o f S e n n h e i s e r e l e c t r o n i c G m b H & C o . K G . w w w . s e n n h e i s e r . c o m . C o p y r i g h t ©1 2 / 2 0 1 1 . A l l r i g h t s r e s e r v e d . E r r o r s a n d o m i s s i o n s e x c e p t e d .PRODUCT VARIANTSEM 2050 AW 516 ... 558 MHz Cat. No. 503144 EM 2050 AW-X 516 ... 558 MHz / Europe Cat. No. 503739 EM 2050 GW 558 ... 626 MHz Cat. No. 503742 EM 2050 GW-X 558 ... 626 MHz / Europe Cat. No. 503743 EM 2050 BW 626 ... 698 MHz Cat. No. 503746 EM 2050 BW-X 626 ... 698 MHz / Europe Cat. No. 503747 EM 2050 CW 718 ... 790 MHz Cat. No. 503750 EM 2050 CW-X 718 ... 790 MHz / Europe Cat. No. 503751 EM 2050 DW 790 ... 865 MHz Cat. No. 503754 EM 2050 DW-X 790 ... 865 MHz / Europe Cat. No. 503755RECOMMENDED ACCESSORIESAB 3700 broadband antenna booster Cat. No. 502196 AD 3700 directional antenna Cat. No. 502197 A 3700 omni-directional antenna Cat. No. 502195 GA 3030-AM antenna mount Cat. No. 4368 A 2003-uHF directional antenna Cat. No. 3658Contact your local Service Partner:。

ADP UHF 半导体方向性无线电天线(470-1075MHz)商品说明说明书

Passive directional antenna for use with Evolution Wireless Digital systems.The ADP UHF passive directional antenna is the perfect addition for enhancing the wireless performance of your Evolution Wireless Digital system. The ⅝" and ⅜" threads make it easy to mount on any mic stand. The ADP UHF can be connected to the EW-D EM receiver, the EW-D AB antenna booster or EW-D ASA antenna splitter.FEATURES• UHF transmission greatly enhances range, reliabilityand scalability • Built-in ⅝" and ⅜" threads allow for easy mic standmountingACCESSORIESEW-D AB (Q)Antenna Booster 470 - 550 MHz Art. no. 508873EW-D AB (R)Antenna Booster 520 - 608 MHz Art. no. 508874EW-D AB (S)Antenna Booster 606 - 694 MHz Art. no. 508875EW-D AB (U)Antenna Booster 823 - 865 MHz Art. no. 508876EW-D AB (V)Antenna Booster 902 - 960 MHz Art. no. 508877EW-D ASA (Q-R-S)Active Antenna Splitter 470 - 694 MHz Art. no. 508879EW-D ASA (T-U-V-W)Active Antenna Splitter 694 - 1075 MHz Art. no. 508880EW-D ASA CN/ANZ (Q-R-S)Active Antenna Splitter470 - 694 MHzArt. no. 508998ARTICLE INFORMATIONADP UHF (470 - 1075 MHz)Art. no. 508863SPECIFICATIONSFrequency range 470 – 1075 MHz Apex angle (-3 dB)approx. 100°Front-to-back ratio > 14 dB Gain typ. 5 dBi Impedance 50 ΩConnection BNC female, no DC path Threads for tripod mounting 3/8" and 5/8"Dimensions 319 x 310 mmWeightApprox. 1100 g (2.43 lbs)Operating temperature range-10 °C - +55 °C (14 °F - 131 °F)Storage temperature range-20 °C - +85 °C (-4 °F - 185 °F)Relative humiditymax. 95 % (non-condensing)POLAR PATTERN90°90°0°180°Sennheiser electronic GmbH & Co. KG · Am Labor 1 · 30900 Wedemark · Germany · DIMENSIONSPOSITIONING。

对数周期天线 HyperLOG7040

对数周期天线 HyperLOG7040介绍对数周期天线(Logarithmic Periodic Antenna)是一种宽带落地式碟形天线,广泛用于电磁测量、电子测试、无线通信等领域。

而HyperLOG7040是其中一种常用的对数周期天线,能够覆盖频率范围20MHz至1GHz,并且在小型载体、大动态范围、双极性模式等方面具有优越的性能。

特点宽带性HyperLOG7040采用了对数周期结构,能够覆盖频率范围20MHz至1GHz,而且在整个频率范围内保持一定的增益和较低的VSWR。

小型化设计HyperLOG7040整体尺寸相对较小,方便携带和操作。

其尺寸为229 x 229 x18毫米(L x W x H),重量仅为450克。

同时,HyperLOG7040还具有强大的抗振性能,能够在恶劣的环境中稳定运行。

双极性模式HyperLOG7040还具有双极性模式,能够实现快速切换天线的极性,以适应不同的测量环境和应用场景。

双极性模式可以通过连接两个同类HyperLOG7040天线并进行校准后实现。

高灵敏度HyperLOG7040具有高灵敏度,能够测量非常弱的信号。

其灵敏度可达到-50dBm。

高动态范围HyperLOG7040具有高动态范围,能够测量信号的高峰值并抑制干扰。

其动态范围可达到+40dBm。

优势相对于其他类型天线,HyperLOG7040的主要优势在于其宽带性和小型化设计。

HyperLOG7040是一种非常适合在不同频段进行测量的天线,而且方便携带,适合实地测试。

与传统测量仪器相比,HyperLOG7040可以大大提高测试效率和准确度,特别是需要在不同频段进行测量的场合。

应用HyperLOG7040常用于电磁测量、无线通信和电子测试等领域。

具体应用包括:•电磁兼容性测试•无线电信号测量和分析•无线电环境监测•电磁干扰和鉴定HyperLOG7040在这些领域中的应用,能够提高测试的精确度和效率,帮助用户更好地了解电磁环境和信号特征。

60GHz天线技术概览

60GHz天线技术概览要求:1.该频段WiFi的发展,标准2.现在WiFi的发展应用情况3.这个频段antenna的技术要素,研究情况,现在发展情况,发展趋势4.相关文章,包括重要会议文章,期刊文章5.antenna的技术难点一、60GHz频段WiFi的发展,标准,特点60GHz频段是一个无需注册的、开放的ISM频段,在目前2.4GHz和5.2GHz ISM 频段已经被大量使用的情况下,人们的注意力自然转向了尚未被开发和利用的60GHz频段来。

该频段的特点有:1、绝对带宽很宽,高达9GHz带宽2、波长短,具有毫米波的属性3、在空气中衰耗得比较快4、适合室内使用该频段在2012年被IEEE纳入了802.11ad标准中,是标准802.11n/ac的演变。

该标准允许(技术特点):1)支持高达2.16 G H z的信道带宽,物理层传输速率接近7 Gbit/s;2)采用高增益、低复杂度和低处理时延的低密度奇偶校验码(LDPC);3)采用旋转调制、差分调制、扩展QPSK等改进的调制技术;4)采用波束赋形技术对抗60 GHz频段的高路径损耗,支持传输距离超过10 m的可靠通信;5)针对无线视频、快速文件传输等应用场景和60 GHz无线通信技术特点,引入新的组网方式——个人基本服务集(PBSS);6)采用增强的安全协议和功率管理技术;7)支持在2.4 G H z、5 G H z和60 GHz频带之间的快速会话转移;8)支持与其他60 G H z系统(如IEEE 802.15.3c及802.19)的共存。

WiGig技术是由WiGig(无线吉比特联盟)主导基于802.11ad标准制定的。

2013年,WiGig联盟与Wi-Fi联盟合并二、60GHz频段WiFi的发展和应用1、2014年10月三星推出60GHz Wi-Fi 技术。

三星方面表示,新的Wi-Fi 技术将能够将数据传输速度提高到 4.6Gbps,实际的数据传输速度将达到575MB 每秒,五倍于现有Wi-Fi 最快速度。

石墨烯太赫兹芯片

石墨烯太赫兹芯片石墨烯太赫兹芯片是一种基于石墨烯材料的微型电子芯片,可以在太赫兹频段进行信号传输和处理。

石墨烯是一种由碳原子组成的单层蜂窝状结构,具有优异的导电性、热导性和机械强度,被广泛应用于各种领域的科技产品中。

太赫兹波段是指频率范围在0.1 THz到10 THz之间的电磁波。

这一频段的电磁波具有穿透力强、分辨率高、无辐射危害等优点,在生物医学、安全检测、通信等领域有着重要的应用前景。

然而,由于太赫兹波段的特殊性,传统的电子器件很难在该频段上进行高效的信号传输和处理。

石墨烯作为一种具有出色电子特性的材料,被认为是太赫兹应用领域的理想材料之一。

石墨烯的高载流子迁移率和宽带隙特性,使其能够在太赫兹频段实现高速、低噪声的信号传输和处理。

利用石墨烯材料制备的太赫兹芯片,可以实现更高的频率响应、更低的功耗和更小的尺寸,为太赫兹技术的发展提供了重要的支持。

石墨烯太赫兹芯片的制备主要包括两个关键步骤:石墨烯的制备和芯片的加工。

石墨烯的制备可以通过机械剥离、化学气相沉积、化学气相沉积还原等方法进行。

在制备过程中,需要控制石墨烯的层数、晶格缺陷等参数,以获得具有理想电子特性的石墨烯材料。

芯片的加工则包括沉积金属电极、制作微纳结构等步骤,用于实现电子器件的连接和信号传输。

石墨烯太赫兹芯片在各个领域都具有广泛的应用前景。

在生物医学领域,石墨烯太赫兹芯片可以用于皮肤病变的早期检测、癌症细胞的检测和治疗等。

在安全检测领域,石墨烯太赫兹芯片可以用于爆炸品和毒品的检测、隐蔽武器的探测等。

在通信领域,石墨烯太赫兹芯片可以用于高速无线通信、毫米波雷达等。

然而,石墨烯太赫兹芯片的商业化应用还面临一些挑战。

首先,石墨烯的制备成本较高,导致石墨烯太赫兹芯片的价格较高。

其次,石墨烯的稳定性和可靠性有待提高,以满足实际应用的需求。

此外,石墨烯太赫兹芯片的标准化和产业化程度较低,需要进一步加强研发与产业的结合,推动其商业化进程。

石墨烯太赫兹芯片作为一种具有巨大潜力的新型微电子器件,将在太赫兹应用领域发挥重要作用。

60GHz毫米波技术白皮书——IEEE 802.11ad

● 11ac is intended for the frequency range under 6 GHz and uses "conventional" technologies, such as those seen in 11n. It uses bandwidths of up to 160 MHz and eight MIMO streams to achieve data rates of more than 1 Gbit/s for the 80 MHz bandwidth (see http:\\/appnote/1MA192).

WLAN 802.11

The 802.11 WLAN standard has also been continuously updated to permit higher throughput. These changes were developed as amendments, but have since been assigned their own letter as enhancements to the standard using the MAC and PHY layers. The relevant standard enhancements are 11a,b,g,n and these cover the two bands in the 2.4 GHz and the 5 GHz range. The 11n extension (also called High Throughput (HT)) uses up to four MIMO streams to achieve a data rate of up to 600 Mbit/s. The 11p standard is an extension that permits robust data traffic between automobiles (car to car).

2.4GHz Band Dielectric Ceramic PIFA SMD Antenna 商品

PA.12SPECIFICATIONPart No.: PA.12Product Name : 2.4GHz Band Dielectric Ceramic PIFASMD Antenna for Bluetooth/WLAN/ZigBeeApplicationsDescription : 2400-2484MHz3.27dBi Peak GainSize: 10*4*3mmDesigned for the top left hand corner edge of theComponent side of the board (bottom right corneredge)SMD MountRoHS & REACH Compliant1.IntroductionThis specification covers the Dielectric PIFA Antenna for 2400-2484MHz, covering such applications as Wi-Fi, Bluetooth and ZigBee. A ceramic dielectric PIFA antenna offers smallest footprint, superior gain characteristics and improved isolation over traditional PCB based antennas. This antenna has been developed for the top left hand corner edge of the component side of the Board (bottom right corner edge), the antenna has to be positioned on a non-ground (copper/metal free) area with the feed-point matched direct to the module. Please refer to Recommended Foot print Diagram (8.0 Page 13.).Many module manufacturers specify peak gain limits for any antennas that are to be connected to that module. Those peak gain limits are based on free-space conditions. In practice, the peak gain of an antenna tested in free-space can degrade by at least 1 or 2dBi when put inside a device. So ideally you should go for a slightly higher peak gain antenna than mentioned on the module specification to compensate for this effect, giving you better performance.Upon testing of any of our antennas with your device and a selection of appropriate layout, i ntegration technique, or cable, Taoglas can make sure any of our antennas’ peak gain will be below the peak gain limits. Taoglas can then issue a specification and/or report for the selected antenna in your device that will clearly show it complying with the peak gain limits, so you can be assured you are meeting regulatory requirements for that module.For example, a module manufacturer may state that the antenna must have less than 2dBi peak gain, but you don’t need to select an embedded antenna that has a peak gain of less than 2dBi in free-space. This will give you a less optimized solution. It is better to go for a slightly higher free-space peak gain of 3dBi or more if available. Once that antenna gets integrated into your device, performance will degrade below this 2dBi peak gain due to the effects of GND plane, surrounding components, and device housing. If you want to be absolutely sure, contact Taoglas and we will test. Choosing a Taoglas antenna with a higher peak gain than what is specified by the module manufacturer and enlisting our help will ensure you are getting the best performance possible without exceeding the peak gain limits.2.Electrical SpecificationsThe antenna has the electrical characteristics given in Table 1 under the Taoglas standard installation conditions as shown in the Evaluation Board figure.SpecificationWorking Frequency 2400MHz ~ 2484MHzDimensions 10*4*3mmPeak Gain 3.27dBi maxPolarization LinearImpedance 50 ΩVSWR 2.0 maxOperating Temperature -40~+85°CTermination Ag (Environmentally Friendly Lead-Free)* Data is measured on T aoglas Standard Reference PCB (40*80*0.8mm)3.S11 Response Curve* Gain is measured on test PCB (40*80*0.8mm) * Ant position: Left side, top corner, horizontal4.Test Position5.Summary of Test Results5.1.Gain & EfficiencyFrequency (GHz) Peak Gain(dBi) Efficiency (%)2.4000 2.78 80.642.44203.12 85.652.45003.27 86.502.4835 2.76 75.912.5000 2.34 68.075.2.Power Average GainFrequency (GHz) Plane Average Gain (dB)2.4000 XY Plane -1.622 YZ Plane -1.324 XZ Plane -0.5612.4420 XY Plane -2.464 YZ Plane -0.859 XZ Plane -0.3122.4500 XY Plane -1.424 YZ Plane -0.950 XZ Plane -0.2242.4835 XY Plane -2.949 YZ Plane -1.548 XZ Plane -0.7842.5000 XY Plane -2.444 YZ Plane -2.084 XZ Plane -1.2586.Antenna Pattern – Wi-Fi & Bluetooth 6.1.Frequency: 2.400 GHz6.2.Frequency: 2.442GHz6.3.Frequency: 2.450GHz6.4.Frequency: 2.4835GHz6.5.Frequency: 2.500GHz7.Drawing8.Recommended foot print for EvaluationBoard9.Packaging1 Blister tape to IEC 286-3,polyester2 Pieces/tape:1000No Index Spec. (mm)1 A 4.62 B 10.63 P1 124 W 245 F 8.56 T 3.57 D 1.510.Recommended Reflow Temperature Profile1.Time shown in the above figures is measured from the point when chip surfacereaches temperature.2.Temperature difference in high temperature part should be within 110°C.3.After soldering, do not force cool, allow the parts to cool gradually.*General attention to soldering:●High soldering temperatures and long soldering times can cause leaching of the termination, decrease in adherence strength, and the change of characteristic may occur.●For soldering, please refer to the soldering curves above. However, please keepexposure to temperatures exceeding 200°C to under 50 seconds.●Please use a mild flux (containing less than 0.2wt% Cl). Also, if the flux is watersoluble, be sure to wash thoroughly to remove any residue from the underside of components that could affect resistance.Cleaning:When using ultrasonic cleaning, the board may resonate if the output power is too high. Since this vibration can cause cracking or a decrease in the adherence of the termination, we recommend that you use the conditions below.Frequency: 40kHzOutput Power: 20W/literCleaning Time: 5 minutes maxT aoglas makes no warranties based on the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. T aoglas reserves all rights to this document and the information contained herein.Reproduction, use or disclosure to third parties without express permission is strictly prohibited.© T aoglasPA.12。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Figure 1: The average atmospheric absorption in the range 10 to 400 GHz (fig. 1 in [2]) without the contribution of fog and rain at sea level and 9150 m of altitude. The most prominent application of MMW communications is data transfer between personal digital devices (smartphones, personal digital assistant, mobile computing devices, etc.). The term personal area network (PAN) has been coined to describe this kind of communications. Devices in a PAN typically use short-range, high-bandwidth links to exchange data between them (i.e., multimedia file transfer between mobile devices) and medium

60 GHz Tapered-Helix Antenna for Байду номын сангаасPAN Applications

Paolo Nenzi, Francesco Tripaldi, Frank Silvio Marzano, Fabrizio Palma and Marco Balucani University of Roma “Sapienza” - DIET Via Eudossiana, 18 – 00184 Roma (Italy) nenzi@diet.uniroma1.it, phone: +39-0644585433 Abstract In this work the design of a broadband, high gain conical helical antenna is presented. The antenna is realized using a MEMS process that guarantees the high repeatability and throughput necessary for industrial applications. The designed antenna works in the 55GHz to 85GHz frequency range and has a gain greater than 8 dBi. This antenna presents potential applications in the emerging 60GHz communication band (assigned to WPAN) and in 76GHz RADAR applications for the automotive industry. The design procedure, mechanical and electromagnetic simulations are presented. Introduction The recent availability of CMOS processes that allows the realization of transistors with transit frequencies of hundreds of gigahertz [1] makes possible the production of siliconbased analog microwave circuits operating in the millimeterwave (MMW) frequency range. The advantage of using digital compatible, silicon-based, CMOS processes, for the realization of radio-frequency circuits, is the possibility to integrate on the same IC (integrated circuit) the entire communication system, reducing design and manufacturing costs. The type of communication systems developed in this frequency range are mostly dictated by the propagation characteristics of the atmosphere, that presents several absorption peaks, due to the molecular oxygen and water, as shown in figure 1. range links to transfer data to remote sites via a central infrastructure. The atmospheric propagation limits the interdevice communications to a few tens of meters and the device-infrastructure communication to few-hundreds. This is not a drawback in PAN as the concept of “personal area” suggests that communications should occur in an area under the control of the single person. For such applications, carrier frequency should be centered on absorption peaks to reduce interferences from nearby devices and, to provide some form of security against eavesdropping. The second application by importance is short-range RADARs, mainly collision avoidance radars for the automotive industry. Automotive RADARs are studied since the 70s of the past century [3] and only recently have been installed on high-end cars, and their general deployment is not yet foreseeable. On board millimeter-wave RADARs are used to inform the driver about potential collision risk with the preceding vehicle, to reduce the braking time by pretensioning brakes, to deploy the passive restraint systems, to reduce the risk associated to blind-spots in lane change and to provide information to station-keeping for automatic cruisecontrol. Automotive RADARs should operate under all atmospheric conditions (e.g., heavy rain or fog) when severe additional absorption (with respect to the values shown in figure 1) is present, therefore the operating frequencies should be chosen around the absorption minima. The contrasting needs of the two different applications (communications and ranging) imply that they cannot share the same frequencies. Regulatory agencies share at least 5GHz of continuous unlicensed bandwidth between 56 GHz and 66 GHz, assigned to WPAN (Wireless Personal Area Network) applications, centered on the O2 absorption peak. All share the 76 GHz - 77 GHz band for the automotive RADARs, near the minimum of absorption. ITU and MPT (Japan) have assigned the 60 GHz - 61 GHz band to RADAR service and FCC the 46.7 GHz – 46-9 GHz band, where absorption is lower. It is evident that there exists a continuous frequency range of 21 GHz bandwidth (i.e. from 56 GHz to 77 GHz) that can be exploited for combining communication and ranging systems in automotive applications. Such combination is the essence of the ITS (Intelligent Transportation Systems) applications, in which the vehicle is required to react to stimuli coming from the environment, co-operate with its neighboring vehicles and with the road traffic-control systems. In this view the concept of WPAN can be extended to include the car in the “personal digital devices” in the network and the traffic-control systems in the infrastructures. In this work we present a high gain antenna that can operate across the entire (21 GHz) bandwidth and can be integrated into the package of an IC. The antenna can be used