周立功高工的FPGA宝贵实战经验与FPGA编程规范

关于大三找实习的经历分享(周立功公司)

关于周立功2013夏令营的面试经历今天收到了周立功名下的致远电子的实习通过邀请通知,心情久久不能平静,回想从投简历到终面,还真是一个漫长的时间。

现在回想起来,发现这个找实习的道路还真是非常艰难。

我报的是模拟电路开发工程师这个岗位,网申之后就去听周立功的宣讲会,地点是在广工,刚开始对周立功这家公司没什么感觉,感觉像是在做单片机似的,不过我还是去听了他的宣讲会,听了之后才发现这家公司不全是做销售的,他名下的致远电子有限公司专门搞高端仪器研发,听HR说这次名是招实习,实际是将2014招聘提前招了。

感觉现在就业好严峻。

当天听完宣讲会,了解了一下相关的企业文化等等,这天就这样过去了。

具体网申是否通过,要明天等通知。

第二天(4月27日)中午2点33分,收到了周立功公司发送的短信,说我通过了网筛,并当天晚上18:30分去参加笔试,我报的是模拟电路开发工程师,所以我要考的内容是模电+数电。

因为那时候我还不在状态,收到短信通知的时候我还在学英语,突然收到要晚上考试,感觉准备是来不及了。

所以我就没特意去复习相关的书籍,只是顺它自然。

晚上我和舍友准时到达考场,笔试的内容挺多的,模拟部分考得最多的就是一些关于电容、电感的基础问题,感觉挺简单,数方面考数制运算、求补和一些基本的时序电路,这部分靠平时积累,考试的时候半推导,半回忆地完成了,最后还有4道大题,第一道大题是关于晶体管的,第二道是要C语言写一个带有优先级的译码模块,第三道是关于一个移位寄存器的题,最后一道是单片机和LED结合的题。

感觉最后的大题如果做过实验的,都可以做出大部分了。

做完之后我感觉一般,就这样回去等通知了。

HR说如果通过,会在第二天3点前发通知。

第三天(4月28日),这天早上有课,我就没多大心思查看手机的信息了,下午3点,还是没收到通知,我估计是没戏了,毕竟做完题目之后没感觉,所以下午就和班里同学一起去打球了,打完球后,我打开手机,却发现有3条未读信息,我估计有希望了。

FPGA推荐书籍

标签: FPGA 初学经典书籍FPGA初学推荐书籍Verilog数字系统设计教程夏宇闻这本书着重讲的是Verilog的语法,有综合语法还有仿真的语法。

看的时候可以只看前七章,后面是应用的例子。

EDA实验与实践周立功周立功写的书对初学者来说很好用,写的很详细,注释也很清晰,非常适合入门。

本书中不仅有可综合的代码,还有quartus 软件的常用功能的讲解。

跟随本书,将实验一个一个的做下去,对FPGA的开发流程就基本了解了。

设计与验证Verilog HDL 吴继华王诚本书是有FPGA开发经验的人写的,关于代码规范性的一本书,里面是FPGA高手的经验总结,对提高写verilog 代码的水平很有帮助。

Verilog HDL应用程序设计实例精讲(含光盘1张)刘福奇刘波这是他们推荐的一本书,我没看过,里面的例程据说讲的很好,可以作为参考代码数字信号处理的FPGA实现(第2版)刘凌译本书详细讲解了FPGA中常用的DSP算法,有详细的代码,可以直接用。

如果想用FPGA做数字信号处理,这本书不错。

无线通信FPGA设计田耘本书和上面一本书,都是非常经典的了。

再推荐两本老外的高级FPGA设计结构、实现也优化(美)马克斯菲尔德(Maxfiel,C.)FPGA设计指南器件、工具和流程(美)马克斯菲尔德(Maxfiel,C.)书名: Xilinx FPGA开发实用教程作者:田耘徐文波出版社:清华大学出版社日期: 2010-3-27 9:51:33价格: 59元详细介绍2007年10月份,作者有幸聆听了Xilinx公司全球CTO Ivo Bolsens先生在清华大学题为“FPGA: The future platform fortransforming, transporting and computing”的演讲,感触颇深。

Ivo先生指出了FPGA的三大应用领域:数字处理中的信号变换、高速交换中的数据收发以及求解中的复杂计算。

周立功 EasyPRO 90B 通用编程器

周立功EasyPRO 90B 通用编程器支持ATMEL A VR全系列芯片编程支持MYSON芯片BIOS专用烧录器485-850EasyPRO 90B是同类产品中集成度最高,功耗最小,支持型号最全的电脑主板BIOS专用烧录机。

EasyPRO 90B采用USB通讯技术,内置高速CPU并采用程控电源和程控分频器,使得编程深度加大,速度更快,稳定性更好,编程效果更加流畅。

此外,整机体积小巧,连接方便,极适合外出携带。

参考照片功能特点界面美观,操作简单方便,编程速度快,工作效率高;电脑主板BIOS专用烧录机,可供维修、培训使用;采用表面贴片工艺生产,可靠性高,使用寿命长;编程器体积小巧,适合外出携带;所有算法均经过批量烧写测试,杜绝烧毁芯片的现象;支持用户对所编程芯片序列号的二次开发;当用户插入坏片时系统具有自动保护和检测功能;USB1.1接口,即插即用,方便手提电脑现场编程;是国内市场中能够真正准确烧写P89C66xHxx、P89V51Rx2等系列芯片的并行烧写器。

支持windows 98/ME/NT/2000/XP操作系统(中/英文)。

不定期地增加对新器件的编程支持并在网上更新软件;对4M及以下的Flash,可做软件升级。

电路特点基本配置40脚万能驱动电路;DAC数模转换控制I/O电平;支持芯片工作电压Vcc:3.3V-5.0V;支持芯片烧录电压Vpp:3.3V-21V;系统内部预设500mA过流保护电路,彻底防止意外事件。

过流容限可由用户自行修改;主控芯片的每个端口设有过压保护电路,可以防止编程时高压的冲击;进口锁紧座的每一个管脚都可以用作数据总线、地址总线、控制总线、编程电压驱动总线和管脚接触不良测量专用总线等等;烧录电压范围为0V~18.0V,最少分256级可调,编程电流最大可提供500mA;功耗极低,在未编程时,整机电流小于60mA。

支持芯片支持芯片数量:6000以上;支持芯片型号:并行与串行MCU、A VR、EPROM、EEPROM、FLASH、PLD、CPLD、EPLD、标准逻辑器件等。

周立功谈我的25年嵌入式生涯

有些理念,很值得工程师们思考!

周立功,男,1964年3月出生,毕业于东华大学自动化及计算机系,高级工程师,中国单片机学会理事,中国海洋大学讲座教授,硕士生导师,主要研究方向为嵌入式系统与现场总线,目前正在从事80C51、ARM与Nios II等软核SoC的研究与开发。

下面我会把我“第一桶金”的故事告诉你,这也是尽量减少“阶段0”开发一个非常典型的例子。

当年,《羊城晚报》几乎每天都有半版广告刊登信息台(听歌、悄悄话等)广告,一打听广告费每天几十万。当时相信不少人在利用公费电话在拨打这些信息台。后来我送货到客户那里发现电话机都外加了一个铁壳并上了一把锁,从看到那一幕开始,我决定做电话加密码锁,锁长途电话0字头,手机、BB机、信息台的9字头。通过朋友介绍,福州某公司有这个技术,于是我打了一个试探性的电话,使用5000元购买方案和源代码,对方非常爽快地同意了。我生怕有变立即坐飞机到福州去,很快就见到了郑新建工程师,他原来在福州某公司工作,我见到他的时候已经离开了福州某公司,但仍然自己写一些产品解决方案,通过福州某公司销售。买到方案与源代码之后,我立即带样机到各地去做测试,发现这台样机兼容性太差,而且市场已经开始在卖的产品也存在同样的问题,我想只要解决好兼容性的问题,如果在任何地区交换机局域网都能够使用,那就是最好的产品不愁没有市场。

也许有程序员会关心JTAG开发工具问题,那也是一个“外包”的项目。当时,我们在网上发现了一个由计算机爱好者业余时间设计的H-JTAG,这是一个比较稳定的调试器软件,正好适合我们使用。于是我就同设计者联系,并决定由周立功单片机资助他继续开发,同时,其开发成果还免费提供给网上的用户下载,保证它作为一个自由软件。其实,无论是Linux还是H-JTAG都是开源软件,如果担心其它的同行因此受益而超越自己的话,难免需要在公司负担很多开发人员,面面俱到地做许多事实上是重复的开发工作。其实,我们的合作伙伴都是所在领域的专家,如果自己从头到尾去学习和开发,不仅抢了合作伙伴的饭碗,而且结果未必理想。这种情况下不但会延误宝贵的商机,而且还会影响与合作伙伴之间的关系。其实只要引入我们企业长期积累和制定的嵌入式系统工程管理思想和规范,即可得到自己想要的结果:“做你最擅长的,其余的外包”,类似这样的案例在周立功单片机将会越来越多。

广州周立功单片机 LPC2114 2124 2212 2214 使用指南

LPC2114/2124/2212/2214使用指南1.介绍 (10)1.1 概述 (10)1.2 特性 (10)1.3 应用 (11)1.4 器件信息 (11)1.5 结构概述 (11)1.6 ARM7TDMI-S处理器 (12)1.7 片内FLASH程序存储器 (12)1.8 片内静态RAM (12)1.9 LPC2114/2124/2212/2214寄存器 (13)2. LPC2114/2124/2212/2214存储器寻址 (22)2.1 存储器映射 (22)2.2 LPC2114/2124/2212/2214存储器重新映射和BOOT BLOCK (26)2.2.1 存储器映射概念和操作模式 (26)2.2.2 存储器的重新映射 (26)2.3 预取指中止和数据中止异常 (28)3. 外部存储器控制器(EMC) (28)3.1 特性 (28)3.2 概述 (29)3.3 管脚描述 (29)3.4 寄存器描述 (29)3.4.1 存储器组配置寄存器0-3(BCFG0-3 - 0xFFE00000-0C) (30)3.5 外部存储器接口 (31)3.6 典型总线时序 (33)3.7 外部存储器选择 (33)4. 系统控制模块 (34)4.1 系统控制模块功能汇总 (34)4.2 管脚描述 (34)4.3 寄存器描述 (35)4.4 晶体振荡器 (35)4.5 外部中断输入 (38)4.5.1 寄存器描述 (38)4.5.2 外部中断标志寄存器(EXTINT - 0xE01FC140) (38)4.5.3 外部中断唤醒寄存器(EXTWAKE - 0xE01FC144) (39)4.5.4 外部中断方式寄存器(EXTMODE – 0xE01FC148) (40)4.5.5 外部中断极性寄存器(EXTPOLAR – 0xE01FC14C) (40)4.5.6 多个外部中断管脚 (41)4.6 存储器映射控制 (41)4.6.1 存储器映射控制寄存器(MEMMAP – 0xE01FC040) (41)4.6.2 存储器映射控制的使用注意事项 (42)4.7 PLL(锁相环) (42)4.7.1 寄存器描述 (43)4.7.2 PLL控制寄存器(PLLCON – 0xE01FC080) (44)4.7.3 PLL配置寄存器(PLLCFG – 0xE01FC084) (44)4.7.4 PLL状态寄存器(PLLSTAT - 0xE01FC088) (44)4.7.5 PLL中断 (45)4.7.6 PLL模式 (45)4.7.7 PLL馈送寄存器(PLLFEED – 0xE01FC08C) (45)4.7.8 PLL和掉电模式 (46)4.7.9 PLL频率计算 (46)4.7.10 确定PLL设定的过程 (46)4.7.11 PLL举例 (47)4.8 功率控制 (47)4.8.1 寄存器描述 (48)4.8.2 功率控制寄存器(PCON – 0xE01FC0C0) (48)4.8.3 外设功率控制寄存器(PCONP – 0xE01FC0C4) (48)4.9 功率控制注意事项 (49)4.10 复位 (49)4.11 VPB分频器 (51)4.11.1 VPBDIV寄存器(VPBDIV - 0xE01FC100) (51)4.12 唤醒定时器 (52)5. 存储器加速模块(MAM) (53)5.1 介绍 (53)5.1.1 存储器加速器模块 (53)5.1.2 Flash存储器组 (54)5.1.3 指令锁存和数据锁存 (54)5.1.4 Flash编程问题 (54)5.2 存储器加速器模块的操作模式 (55)5.3 MAM配置 (55)5.4 寄存器描述 (55)5.4.1 MAM控制寄存器(MAMCR - 0xE01FC000) (56)5.4.2 MAM定时寄存器(MAMTIM - 0xE01FC004) (56)5.5 MAM使用注意事项 (57)6. 向量中断控制器(VIC) (57)6.1 特性 (57)6.2 描述 (57)6.3 寄存器描述 (59)6.4 VIC寄存器 (60)6.4.1 软件中断寄存器(VICSoftInt - 0xFFFFF018,读/写) (60)6.4.2 软件中断清零寄存器(VICSoftIntClear - 0xFFFFF01C,只写) (60)6.4.3 所有中断状态寄存器(VICRawIntr - 0xFFFFF008,只读) (61)6.4.4 中断使能寄存器(VICIntEnable - 0xFFFFF010,读/写) (61)6.4.5 中断使能清零寄存器(VICIntEnClear - 0xFFFFF014,只写) (61)6.4.6 中断选择寄存器(VICIntSelect - 0xFFFFF00C,读/写) (61)6.4.7 IRQ状态寄存器(VICIRQStatus - 0xFFFFF000,只读) (61)6.4.8 FIQ状态寄存器(VICFIQStatus - 0xFFFFF004,只读) (62)6.4.9 向量控制寄存器0-15(VICVectCnt l0-15 - 0xFFFFF200-23C,读/写) (62)6.4.10 向量地址寄存器0-15(VICVectAddr0-15 - 0xFFFFF100-13C,读/写) (62)6.4.11 默认向量地址寄存器(VICDefVectAddr - 0xFFFFF034,读/写) (62)6.4.12 向量地址寄存器(VICVectAddr - 0xFFFFF030,读/写) (63)6.4.13 保护使能寄存器(VICProtection - 0xFFFFF020,读/写) (63)6.5 中断源 (63)6.6 伪中断 (65)6.6.1 伪中断的详述和个案 (66)6.7 VIC使用事项 (67)7. 管脚配置 (69)7.1 LPC2114/2124的管脚分布 (69)7.2 LPC2114/2124的管脚描述 (69)7.3 LPC2212/2214的管脚分布 (74)7.4 LPC2212/2214的管脚描述 (74)8. 管脚连接模块 (80)8.1 应用 (80)8.2 描述 (81)8.3 寄存器描述 (81)8.3.1 管脚功能选择寄存器0(PINSEL0 - 0xE002C000) (81)8.3.2 管脚功能选择寄存器1(PINSEL1 - 0xE002C004) (82)8.3.3 管脚功能选择寄存器2(PINSEL2 - 0xE002C014) (83)8.3.4 管脚功能选择寄存器值 (84)8.4 144脚封装的引导控制 (85)9. GPIO (85)9.1 特性 (85)9.2 应用 (85)9.3 管脚描述 (85)9.4 寄存器描述 (86)9.4.1 GPIO管脚值寄存器(IO0PIN - 0xE0028000,IO1PIN – 0xE0028010,IO2PIN –0xE0028020,IO3PIN – 0xE0028030) (86)9.4.2 GPIO输出置位寄存器(IO0SET - 0xE0028004,IO1SET – 0xE0028014,IO2SET – 0xE0028024,IO3SET – 0xE0028034) (88)9.4.3 GPIO输出清零寄存器(IO0CLR - 0xE002800C,IO1CLR – 0xE002801C,IO2CLR – 0xE002802C,IO3CLR – 0xE002803C) (88)9.4.4 GPIO方向寄存器(IO0DIR - 0xE0028008,IO1DIR – 0xE0028018,IO2DIR –0xE0028028,IO3DIR – 0xE0028038) (88)9.5 GPIO使用注意事项 (89)10. UART 0 (89)10.1 特性 (89)10.2 管脚描述 (89)10.3 寄存器描述 (90)10.3.1 UART0接收器缓存寄存器(U0RBR - 0xE000C000,DLAB=0,只读) (90)10.3.2 UART0发送器保持寄存器(U0THR - 0xE000C000,DLAB=0,只写) (91)10.3.3 UART0除数锁存LSB寄存器(U0DLL - 0xE000C000,DLAB=1) (91)10.3.4 UART0除数锁存MSB寄存器(U0DLM - 0xE000C004,DLAB=1) (91)10.3.5 UART0中断使能寄存器(U0IER - 0xE000C004,DLAB=0) (91)10.3.6 UART0中断标识寄存器(U0IIR - 0xE000C008,只读) (92)10.3.7 UART0 FIFO控制寄存器(U0FCR - 0xE000C008) (93)10.3.8 UART0线控制寄存器(U0LCR - 0xE000C00C) (94)10.3.9 UART0线状态寄存器(U0LSR - 0xE000C014,只读) (94)10.3.10 UART0高速缓存寄存器(U0SCR – 0Xe000C01C) (95)10.4 结构 (95)11. UART1 (97)11.1 特性 (97)11.2 管脚描述 (97)11.3 寄存器描述 (98)11.3.1 UART1接收器缓存寄存器(U1RBR - 0xE0010000,DLAB=0,只读) (98)11.3.2 UART1发送器保持寄存器(U1THR - 0xE0010000,DLAB=0,只写) (99)11.3.3 UART1除数锁存LSB寄存器(U1DLL - 0xE0010000,DLAB=1) (99)11.3.4 UART1除数锁存MSB寄存器(U1DLM - 0xE0010004,DLAB=1) (99)11.3.5 UART1中断使能寄存器(U1IER - 0xE0010004,DLAB=0) (99)11.3.6 UART1中断标识寄存器(U1IIR - 0xE0010008,只读) (100)11.3.7 UART1 FIFO控制寄存器(U1FCR - 0xE0010008) (101)11.3.8 UART1线控制寄存器(U1LCR - 0xE001000C) (102)11.3.9 UART1 Modem控制寄存器(U1MCR - 0xE0010010) (102)11.3.10 UART1线状态寄存器(U1LSR – 0Xe0010014,只读) (103)11.3.11 UART1 Modem状态寄存器(U1MSR - 0x0E0010018) (104)11.3.12 UART1高速缓存寄存器(U1SCR - 0xE001001C) (105)11.4 结构 (105)12. I2C接口 (106)12.1 特性 (106)12.2 应用 (107)12.3 描述 (107)12.3.1 I2C操作模式 (107)12.3.1.1 主发送器模式: (107)12.3.1.2 主接收器模式 (108)12.3.1.3 从接收器模式 (109)12.3.1.4 从发送器模式 (110)12.4 管脚描述 (110)12.5 寄存器描述 (111)12.5.1 I2C控制置位寄存器(I2CONSET - 0xE001C000) (111)12.5.2 I2C控制清零寄存器(I2CONCLR – 0xE001C018) (112)12.5.3 I2C状态寄存器(I2STAT - 0xE001C004) (113)12.5.4 I2C数据寄存器(I2DAT - 0xE001C008) (113)12.5.5 I2C从地址寄存器(I2ADR - 0xE001C00C) (113)12.5.6 I2C SCL占空比寄存器(I2SCLH - 0xE001C010和I2SCLL - 0xE001C014)11313. SPI接口 (116)13.1 特性 (116)13.2 描述 (116)13.2.1 SPI概述 (116)13.2.2 SPI数据传输 (116)13.2.3 SPI外设描述 (117)13.2.3.1 概述 (117)13.2.3.2 主机操作 (118)13.2.3.3 从机操作 (118)13.2.3.4 异常状况 (119)13.3 管脚描述 (120)13.4 寄存器描述 (120)13.4.1 SPI控制寄存器(S0SPCR - 0xE0020000, S1SPCR - 0xE0030000) (121)13.4.2 SPI状态寄存器(S0SPSR - 0xE0020004, S1SPSR - 0xE0030004) (121)13.4.3 SPI数据寄存器(S0SPDR - 0xE0020008,S1SPDR – 0xE0030008) (121)13.4.4 SPI时钟计数寄存器(S0SPCCR - 0xE002000C,S1SPCCR – 0xE003000C) (122)13.4.5 SPI中断寄存器(S0SPINT - 0xE002001C,S1SPINT – 0xE003001C) (122)13.5 结构 (122)14. 定时器0和定时器1 (123)14.1 特性 (123)14.2 应用 (123)14.3 描述 (124)14.4 管脚描述 (124)14.5 寄存器描述 (124)14.5.1 中断寄存器(IR: 定时器0 - T0IR:0xE00040000;定时器1 - T1IR:0xE0008000) (125)14.5.2 定时器控制寄存器(TCR: 定时器0 – T0TCR:0xE0004004;定时器1 –T1TCR:0xE0008004) (126)14.5.3 定时器计数器(TC: 定时器0 – T0TC:0xE0004008;定时器1 – T1TC:0xE0008008) (126)14.5.4 预分频寄存器(PR: 定时器0 – T0PR:0xE000400C;定时器1 – T1PR:0xE000800C) (126)14.5.5 预分频计数器寄存器(PC: 定时器0 – T0PC:0xE0004010;定时器1 –T1PC:0xE0008010) (126)14.5.6 匹配寄存器(MR0 - MR3) (127)14.5.7 匹配控制寄存器(MCR: 定时器0 – T0MCR:0xE0004014;定时器1 –T1MCR:0xE00080014) (127)14.5.8 捕获寄存器(CR0 - CR3) (127)14.5.9 捕获控制寄存器(CCR: 定时器0 – T0CCR:0xE0004028;定时器1 –T1CCR:0xE0008028) (127)14.5.10 外部匹配寄存器(EMR: 定时器0 – T0EMR:0xE000403C;定时器1 –T1EMR:0xE0008003C) (128)14.5.11 定时器举例操作 (129)14.6 结构 (130)15. 脉宽调制器(PWM) (130)15.1 特性 (131)15.2 描述 (131)15.2.1 单边沿控制的PWM输出规则 (135)15.2.2 双边沿控制的PWM输出规则 (135)15.3 管脚描述 (135)15.4 寄存器描述 (135)15.4.1 PWM中断寄存器(PWMIR - 0xE0014000) (137)15.4.2 PWM定时器控制寄存器(PWMTCR - 0xE0014004) (137)15.4.3 PWM定时器计数器(PWMTC - 0xE0014008) (137)15.4.4 PWM预分频寄存器(PWMPR - 0xE001400C) (137)15.4.5 PWM预分频计数器寄存器(PWMPC - 0xE0014010) (138)15.4.6 PWM匹配寄存器(PWMMR0 –PWMMR6) (138)15.4.7 PWM匹配控制寄存器(PWMMCR - 0xE0014014) (138)15.4.8 PWM控制寄存器(PWMPCR - 0xE001404C) (139)15.4.9 PWM锁存使能寄存器(PWMLER - 0xE0014050) (140)16. A/D转换器 (141)16.1 特性 (141)16.2 描述 (141)16.3 管脚描述 (141)16.4 寄存器描述 (141)16.4.1 A/D控制寄存器(ADCR – 0xE0034000) (143)16.4.2 A/D数据寄存器(ADDR – 0xE0034004) (144)16.5 操作 (144)16.5.1 硬件触发转换 (144)16.5.2 时钟产生 (144)16.5.3 中断 (144)16.5.4 精度和数字接收器 (144)17. 实时时钟 (145)17.1 特性 (145)17.2 描述 (145)17.3 结构 (145)17.4 寄存器描述 (146)17.5 RTC中断 (147)17.6 混合寄存器组 (147)17.6.1 中断位置(ILR - 0xE0024000) (147)17.6.2 时钟节拍计数器(CTC - 0xE0024004) (147)17.6.3 时钟控制寄存器(CCR - 0xE0024008) (148)17.6.4 计数器增量中断 (148)17.6.5 报警屏蔽 (148)17.7 完整时间寄存器 (149)17.7.1 完整时间寄存器0(CTIME0 - 0xE0024014) (149)17.7.2 完整时间寄存器1(CTIME1 - 0xE0024018) (149)17.7.3 完整时间寄存器2(CTIME2 - 0xE002401C) (150)17.8 时间计数器组 (150)17.8.1 闰年计算 (150)17.9 报警寄存器组 (151)17.10 RTC使用注意事项 (151)17.11 基准时钟分频器(预分频器) (151)17.11.1 预分频整数寄存器(PREINT - 0xE0024080) (152)17.11.2 预分频小数寄存器(PREFRAC - 0xE0024084) (152)17.11.3 预分频器的使用举例 (152)17.11.4 预分频器操作 (153)18. 看门狗 (154)18.1 特性 (154)18.2 应用 (154)18.3 描述 (154)18.4 寄存器描述 (154)18.4.1 看门狗模式寄存器(WDMOD - 0xE0000000) (155)18.4.2 看门狗定时器常数寄存器(WDTC - 0xE0000004) (155)18.4.3 看门狗喂狗寄存器(WDFEED - 0xE0000008) (156)18.4.4 看门狗定时器值寄存器(WDTV - 0xE000000C) (156)18.5 方框图 (156)19. FLASH存储器系统和编程 (157)19.1 FLASH存储器系统 (157)19.2 FLASH BOOT装载程序 (157)19.3 特性 (157)19.4 应用 (157)19.5 描述 (157)19.5.1 通信协议 (159)19.5.1.1 ISP命令格式 (159)19.5.1.2 ISP响应格式 (159)19.5.1.3 ISP数据格式 (159)19.5.1.4 ISP流程控制 (159)19.5.1.5 ISP命令中止 (159)19.5.1.6 ISP过程中的中断 (159)19.5.1.7 IAP过程中的中断 (159)19.5.1.8 ISP命令处理器使用的RAM (159)19.5.1.9 IAP命令处理器使用的RAM (160)19.5.1.10 RealMonitor使用的RAM (160)19.6 BOOT处理流程图 (160)19.7 扇区数 (161)19.8 代码读保护 (162)19.8.1 ISP命令 (163)19.8.1.1 解锁<解锁代码> (163)19.8.1.2 设置波特率<波特率> <停止位> (164)19.8.1.3 回声<设定> (164)19.8.1.4 写RAM<起始地址> <字节数> (164)19.8.1.5 读存储器<地址> <字节数> (165)19.8.1.6 准备写操作的扇区<起始扇区号> <结束扇区号> (165)19.8.1.7 将RAM内容复制到Flash <Flash地址> <RAM地址> <字节数>..16619.8.1.8 运行<地址><模式> (166)19.8.1.9 擦除扇区<起始扇区号><结束扇区号> (167)19.8.1.10 扇区查空<起始扇区号><结束扇区号> (167)19.8.1.11 读器件ID (167)19.8.1.12 读Boot代码版本 (168)19.8.1.13 比较<地址1><地址2><字节数> (168)19.8.2 IAP命令 (169)19.8.2.1 准备编程扇区 (171)19.8.2.2 将RAM内容复制到Flash (171)19.8.3 擦除扇区 (172)19.8.3.1 扇区查空 (172)19.8.3.2 读器件ID (172)19.8.3.3 读Boot代码版本 (173)19.8.3.4 比较 (173)19.9 JTAG Flash编程接口 (174)20. EmbeddedICE逻辑 (174)20.1 特性 (174)20.2 应用 (174)20.3 描述 (174)20.4 管脚描述 (176)20.5 复用管脚的复位状态 (176)20.6 寄存器描述 (176)20.7 方框图 (177)21. 嵌入式跟踪宏单元 (177)21.1 特性 (177)21.2 应用 (177)21.3 描述 (178)21.3.1 ETM配置 (178)21.4 管脚描述 (178)21.5 复用管脚的复位状态 (179)21.6 寄存器描述 (179)21.7 方框图 (181)22. REALMONITOR (181)22.1 特性 (181)22.2 应用 (181)22.3 描述 (182)22.3.1 RealMonitor部件 (182)22.3.1.1 RMHost (182)22.3.1.2 RMTarget (182)22.3.2 RealMonitor是如何工作的 (183)22.4 如何使能RealMonitor (184)22.4.1 增加堆栈 (184)22.4.1.1 IRQ模式 (185)22.4.1.2 未定义模式 (185)22.4.1.3 SVC模式 (185)22.4.1.4 预取指中止模式 (185)22.4.1.5 数据中止模式 (185)22.4.1.6 用户/系统模式 (185)22.4.1.7 FIQ模式 (185)22.4.2 处理异常 (185)22.4.2.1 RealMonitor异常处理 (185)22.4.3 RMTarget初始化 (186)22.4.4 例程 (186)22.5 RealMonitor建立选项 (189)修订记录 (191)1.介绍1.1 概述LPC2114/2124/2212/2214是基于一个支持实时仿真和跟踪的16/32位ARM7TDMI-S TM CPU的微控制器,并带有128/256 k字节(kB)嵌入的高速Flash存储器。

TFT控制方案 FPGA

广州致远电子有限公司TFT 控制器方案基于Actel FPGA 实现类别内容关键词 TFT ,Actel FPGA摘 要TFT 诞生于80年代末,在1995年之后被广泛的应用,随着TFT 价格的下降,应用范围出现了前所未有的变化,可以适用于医疗、电梯、数控机床、汽车电子、消费类电子等行业。

修订历史版本日期原因V0.00 2009/11/30 创建文档V1.00 2010/05/10 文档修订销售与服务网络(一)广州周立功单片机发展有限公司地址:广州市天河北路689号光大银行大厦12楼F4 邮编:510630电话:(020)38730916 38730917 38730972 38730976 38730977 传真:(020)38730925 网址:广州专卖店地址:广州市天河区新赛格电子城203-204室 电话:(020)87578634 87569917 传真:(020)87578842南京周立功地址:南京市珠江路280号珠江大厦2006室 电话:(025)83613221 83613271 83603500 传真:(025)83613271北京周立功地址:北京市海淀区知春路113号银网中心A 座1207-1208室 (中发电子市场斜对面) 电话:(010)62536178 62536179 82628073 传真:(010)82614433重庆周立功地址:重庆市石桥铺科园一路二号大西洋国际大厦(赛格电子市场)1611室 电话:(023)68796438 68796439 传真:(023)68796439杭州周立功地址:杭州市天目山路217号江南电子大厦502室 电话:(0571)89719480 89719481 89719482 89719483 89719484 89719485 传真:(0571)89719494成都周立功地址:成都市一环路南二段1号数码同人港401室(磨子桥立交西北角)电话:(028)85439836 85437446 传真:(028)85437896深圳周立功地址:深圳市深南中路 2070号电子科技大厦C 座4楼D 室电话:(0755)83781788(5线) 传真:(0755)83793285武汉周立功地址:武汉市洪山区广埠屯珞瑜路158号12128室(华中电脑数码市场)电话:(027)87168497 87168297 87168397 传真:(027)87163755上海周立功地址:上海市北京东路668号科技京城东座7E 室 电话:(021)53083452 53083453 53083496 传真:(021)53083491西安办事处地址:西安市长安北路54号太平洋大厦1201室 电话:(029)87881296 83063000 87881295 传真:(029)87880865销售与服务网络(二)广州致远电子有限公司地址:广州市天河区车陂路黄洲工业区3栋2楼邮编:510660传真:(020)38601859网址:(嵌入式系统事业部)(工控网络事业部)(楼宇自动化事业部)技术支持:CAN-bus:电话:(020)22644381 22644382 22644253 邮箱:can.support@ iCAN及数据采集:电话:(020)28872344 22644373 邮箱:ican@MiniARM:电话:(020)28872684 28267813邮箱:miniarm.support@ 以太网:电话:(020)22644380 22644385邮箱:ethernet.support@无线通讯:电话:(020) 22644386邮箱:wireless@ 串行通讯:电话:(020)28267800 22644385 邮箱:serial@编程器:电话:(020)22644371邮箱:programmer@ 分析仪器:电话:(020)22644375 28872624 28872345 邮箱:tools@ARM嵌入式系统:电话:(020)28872347 28872377 22644383 22644384 邮箱:arm.support@楼宇自动化:电话:(020)22644376 22644389 28267806 邮箱:mjs.support@mifare.support@销售:电话:(020)22644249 22644399 22644372 22644261 28872524 28872342 28872349 28872569 28872573 38601786维修:电话:(020)22644245目录1. TFT简介 (1)2. 原理概述 (2)2.1方案简介 (2)2.2基于Actel FPGA的TFT控制器方案 (2)2.2.1低成本、多功能、低分辨率显示方案 (2)2.2.2低成本、多功能、高分辨率显示方案 (3)2.2.3高性能、低分辨率显示方案 (4)2.2.4多功能、高分辨率显示方案 (4)3. 典型应用 (6)4. 免责声明 (7)1. TFT简介在1970年,Fergason制造了第一台具有实用性的LCD,从此之后,用户产品的界面发生了巨大改变,变得更加的美观、实用,在一定场合下逐渐取代传统的数码管、LED的显示。

Actel+FPGA的PWM+IP的应用

脉冲宽度调制(PWM)是英文“Pluse Width Modulation”的缩写,简称脉宽调制。

它是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,根据相应的载荷的变化来调制晶体管栅极或基极的偏置,来实现开关稳压电源输出晶体管或晶体管导通时间的改变。

这种方式能使电源的输出电压在工作条件变化时保持恒定,广泛应用于测量、通信、功率控制与变化等许多领域。

Actel公司免费提供PWM IP核:Core PWM。

Core PWM是基于APB总线形式的,它的优点是可以连接到Core8051或者是CortexM1处理器上,方便用户进行SoC设计,本文将主要介绍Core PWM的原理与应用。

1. Core PWM介绍(1) PWM的控制方法采样控制理论中有一个重要结论:量相等而形状不同的窄脉冲加在具有惯性的环节上时,效果基本相同。

PWM控制技术就是以该结论为理论基础,对半导体开关器件的导通和关断进行控制,使输出端得到一系列幅值相等而宽度不相等的脉冲,用这些脉冲来代替正弦波或其他所需要的波形。

按一定的规则对各脉冲的宽度进行调制,既可改变逆变电路输出电压的大小,也可改变输出频率。

现在,PWM控制技术主要有8种,分别为:相电压控制PWM、线电压控制PWM、电流控制PWM、空间电压矢量控制PWM、矢量控制PWM、直接转矩控制PWM、非线性控制PWM和谐振软开关PWM。

在这里要重点介绍一下相电压控制PWM中的等脉宽PWM法。

VVVF(Variable Voltage Variable Frequency)装置在早期是采用PAM(Pulse Amplitude Modulation)控制技术来实现的,其逆变器部分只能输出频率可调的方波电压而不能调压,等脉宽PWM法正是为了克服PAM法的这个缺点发展而来的,是PWM法中最为简单的一种,它是把每一脉冲的宽度均相等的脉冲列作为PWM波,通过改变脉冲列的周期可以调频,改变脉冲的宽度或占空比可以调压,采用适当控制方法即可使电压与频率协调变化,相对于PAM法,该方法的优点是简化了电路结构,提高了输入端的功率因数,但同时也存在输出电压中除基波外,还包含较大的谐波分量。

周立功CANET-100_200硬件使用及帧格式

产品数据手册

Date:2006/08/18

4/32

Rev 1.01 ©2006 Zhiyuan Electronics CO., LTD.

广州致远电子有限公司 CANET-100/CANET-200

产品数据手册

Date:2006/08/18

2/32

Rev 1.01 ©2006 Zhiyuan Electronics CO., LTD.

广州致远电子有限公司 CANET-100/CANET-200

CANET-100/CANET-200 CAN 转以太网适配器

销售信息

如果需要购买本产品,请在办公时间(星期一至五上午 8:30~11:50;下午 1:30~5:30; 星期六上午 8:30~11:50)拨打电话咨询广州致远电子有限公司。

CAN to 10M Ethernet,CAN 最大波特率为 1000K bps(CAN 波特率任意设定); 可利用 Windows utility 轻松进行设定; UDP 作业模式; 支持动态(DHCP) ;或静态获取 IP 地址; 转换效率非常高(CAN_Bus 的收发都可实 现 4000 帧/秒 以上的速度);

DataSheet

CANET-100/CANET-200

CANET-100/CANET-200 CAN 转以太网适配器

Rev 1.01 Date: 2006/08/18

产品数据手册

———————————————概述 ——————————————产品特性

CANET-100/CANET-200 是周立功公 司开发的嵌入式网络设备,它内部集成了一 路 CAN_Bus 接口(CANET-100)或两路 CAN_Bus 接口(CANET-200)和 EtherNet 接口以及 TCP/IP 协议栈,用户利于它可以 轻松完成 CAN_Bus 网络和 EtherNet 网络 的互连互通,进一步拓展 CAN_Bus 网络 的范围。

周立功致远电子:ISP、IAP、ICP、JTAG、SWD的编程特点

周立功致远电子:ISP、IAP、ICP、JTAG、SWD的编程特点摘要:ISP、IAP、ICP、JTAG、SWD这些术语,经常看到、听到,在日常的工作中也经常用到,但你真的了解她们吗?电子工程师都知道,半导体技术发展迅猛,带动了各种芯片技术的不断升级。

在数据存储方面,从最初的掩膜ROM,发展到现在的Flash技术,存储技术的不断改进,相对应的编程技术也在不断发展。

记得老一辈工程师在烧写51单片机的时候还是用一台硕大的编程器进行程序下载,而且还是一次性的(OTP),每次都小心谨慎的把代码调试了又调试后才下载看效果。

现在简单到只需一个串口下载器即可实现程序下载,基本不需要考虑编程次数的问题,一有想法随时编译下载更新。

在这个发展过程中,也诞生了很多编程技术,比如ISP、IAP、ICP,另外还有JTAG编程、SWD编程、UART编程等等。

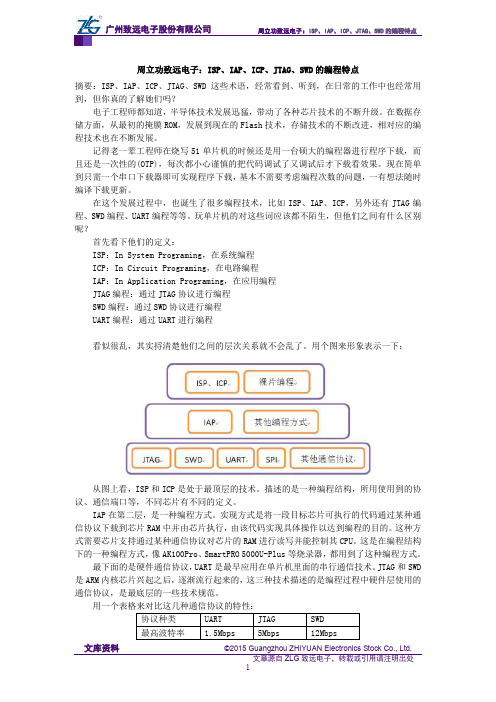

玩单片机的对这些词应该都不陌生,但他们之间有什么区别呢?首先看下他们的定义:ISP:In System Programing,在系统编程ICP:In Circuit Programing,在电路编程IAP:In Application Programing,在应用编程JTAG编程:通过JTAG协议进行编程SWD编程:通过SWD协议进行编程UART编程:通过UART进行编程看似很乱,其实捋清楚他们之间的层次关系就不会乱了。

用个图来形象表示一下:从图上看,ISP和ICP是处于最顶层的技术。

描述的是一种编程结构,所用使用到的协议、通信端口等,不同芯片有不同的定义。

IAP在第二层,是一种编程方式。

实现方式是将一段目标芯片可执行的代码通过某种通信协议下载到芯片RAM中并由芯片执行,由该代码实现具体操作以达到编程的目的。

这种方式需要芯片支持通过某种通信协议对芯片的RAM进行读写并能控制其CPU。

这是在编程结构下的一种编程方式,像AK100Pro、SmartPRO 5000U-Plus等烧录器,都用到了这种编程方式。

LIN规范

LIN规范LIN标准LIN是低成本网络中的汽车通讯协议标准。

10M1M125K20K图1 汽车中的主要网络协议LIN概念LIN(Local Interconnect Network)是低成本的汽车网络,它是现有的汽车复用网络功能上的补充。

为了获得更多的质量提高和降低成本,LIN将是在汽车中使用汽车分级网络的启动因素。

LIN的标准化将减少重复使用现有的低端复用解决方案,而且将减低汽车电子的开发、生产、服务和后勤成本。

LIN标准包括传输协议规范、传输介质规范、开发工具接口规范和软件编程接口规范。

LIN在硬件和软件上保证了网络节点的互操作性,并能预测EMC。

这个规范包包括了3个主要部分:LIN协议规范部分——介绍了LIN的物理层和数据链路层。

LIN配置语言描述部分——介绍了LIN配置文件的格式。

LIN配置文件用于配置整个网络并作为OEM 和各种网络节点供应厂商的通用接口,以及作为开发和分析工具的输入。

LIN API部分——介绍了网络和应用程序之间的接口。

这个概念可以实现开发和设计工具之间的无缝连接,并提高了开发的速度,增强了网络的可靠性。

电子控制单元工具软件级硬件级图2 LIN 规范的范围各部分链接第一部分 LIN 协议规范 第二部分 LIN 配置语言规范 第三部分LIN API 操作规程建议LIN协议规范目录1.介绍 (2)1.1 修订历史 (2)1.2 投稿人 (2)2.基本概念 (3)3.报文传输 (6)3.1 报文帧 (6)3.1.1 字节场(BYTE fields) (7)3.1.2 报头场(HEADER fields) (7)3.2 保留的标识符 (9)3.3 报文帧的长度和总线睡眠检测 (11)3.4 唤醒信号 (11)4.报文滤波 (12)5.报文确认 (12)6.错误和异常处理 (12)6.1 错误检测 (12)6.2 错误标定 (13)7.故障界定 (13)8.振荡器容差 (13)9.位定时要求和同步过程 (13)9.1 位定时要求 (13)9.2 同步过程 (13)10.总线驱动器/接收器 (14)10.1 总体配置 (14)10.2 信号规范 (14)10.3 线的特性 (16)10.4 ESD/EMI的符合条件 (16)11.参考文献 (17)A 附录 (17)A.1 报文序列的举例 (17)A.1.1 周期性的报文传输 (17)A.1.2 总线唤醒过程 (17)A.2 ID场有效值表 (17)A.3 校验和计算举例 (19)A.4 报文错误的原因 (20)A.5 故障界定的建议 (20)A.5.1 主机控制单元 (20)A.5.2 从机控制单元 (21)A.6 物理接口的电源电压定义 (21)1.介绍LIN(Local Interconnect Network)是一个串行通讯协议,它有效地支持分布式汽车应用中机械电子节点的控制。

周立功ARM培训精华(全套).pdf

周立功单片机

• 现实中的嵌入式系统

周立功单片机

• 嵌入式系统的概念

目前,对嵌入式系统的定义多种多样,但没有一 种定义是全面的。下面给出两种比较合理定义: ●从技术的角度定义:以应用为中心、以计算机技 术为基础、软件硬件可裁剪、适应应用系统对功能、 可靠性、成本、体积、功耗严格要求的专用计算机 系统。 ●从系统的角度定义:嵌入式系统是设计完成复杂 功能的硬件和软件,并使其紧密耦合在一起的计算 机系统。术语嵌入式反映了这些系统通常是更大系 统中的一个完整的部分,称为嵌入的系统。嵌入的 系统中可以共存多个嵌入式系统。

周立功单片机

• 嵌入式处理器

——嵌入式片上普及化及半导体工艺的迅速发 展,在一个硅片上实现一个更为复杂的系统的时代已来临,这就是 System On Chip(SOC)。各种通用处理器内核将作为SOC设计公司的 标准库,和许多其它嵌入式系统外设一样,成为 VLSI设计中一种标 准的器件,用标准的 VHDL等语言描述,存储在器件库中。用户只 需定义出其整个应用系统,仿真通过后就可以将设计图交给半导体 工厂制作样品。这样除个别无法集成的器件以外,整个嵌入式系统 大部分均可集成到一块或几块芯片中去,应用系统电路板将变得很 简洁,对于减小体积和功耗、提高可靠性非常有利。 SoC可以分为通用和专用两类。通用系列包括Infineon的TriCore、 Motorola的M-Core、某些ARM系列器件、Echelon和Motorola联合研 制的Neuron芯片等。专用SoC一般专用于某个或某类系统中,不为 一般用户所知。一个有代表性的产品是Philips的Smart XA,它将XA 单片机内核和支持超过2048 位复杂RSA算法的CCU单元制作在一块 硅片上,形成一个可加载JAVA或C语言的专用的SOC,可用于公众 互联网如Internet安全方面。

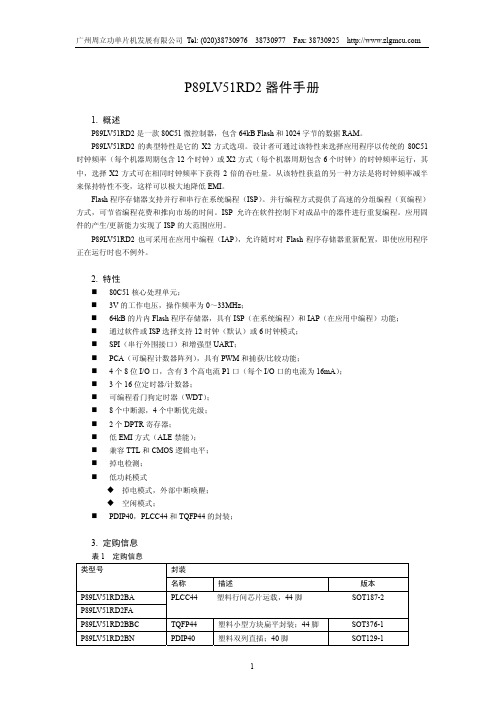

广州周立功单片机发展有限公司 P89LV51RD2 微控制器手册说明书

P89LV51RD2器件手册1. 概述P89LV51RD2是一款80C51微控制器,包含64kB Flash和1024字节的数据RAM。

P89LV51RD2的典型特性是它的X2方式选项。

设计者可通过该特性来选择应用程序以传统的80C51时钟频率(每个机器周期包含12个时钟)或X2方式(每个机器周期包含6个时钟)的时钟频率运行,其中,选择X2方式可在相同时钟频率下获得2倍的吞吐量。

从该特性获益的另一种方法是将时钟频率减半来保持特性不变,这样可以极大地降低EMI。

Flash程序存储器支持并行和串行在系统编程(ISP)。

并行编程方式提供了高速的分组编程(页编程)方式,可节省编程花费和推向市场的时间。

ISP允许在软件控制下对成品中的器件进行重复编程。

应用固件的产生/更新能力实现了ISP的大范围应用。

P89LV51RD2也可采用在应用中编程(IAP),允许随时对Flash程序存储器重新配置,即使应用程序正在运行时也不例外。

2. 特性80C51核心处理单元;3V的工作电压,操作频率为0~33MHz;64kB的片内Flash程序存储器,具有ISP(在系统编程)和IAP(在应用中编程)功能;通过软件或ISP选择支持12时钟(默认)或6时钟模式;SPI(串行外围接口)和增强型UART;PCA(可编程计数器阵列),具有PWM和捕获/比较功能;4个8位I/O口,含有3个高电流P1口(每个I/O口的电流为16mA);3个16位定时器/计数器;可编程看门狗定时器(WDT);8个中断源,4个中断优先级;2个DPTR寄存器;低EMI方式(ALE禁能);兼容TTL和CMOS逻辑电平;掉电检测;低功耗模式掉电模式,外部中断唤醒;空闲模式;PDIP40,PLCC44和TQFP44的封装;3. 定购信息表1 定购信息类型号封装名称描述版本P89LV51RD2BAPLCC44 塑料行间芯片运载,44脚 SOT187-2P89LV51RD2FAP89LV51RD2BBC TQFP44塑料小型方块扁平封装;44脚SOT376-1P89LV51RD2BN PDIP40塑料双列直插;40脚SOT129-1表2 定购选项类型号 温度范围 频率P89LV51RDBA 0℃~+70℃ P89LV51RD2FA -40℃~+85℃ P89LV51RD2BBC 0℃~+70℃ P89LV51RD2BN 0℃~+70℃0~33MHz4.功能框图图1 P89LV51RD2功能框图5.1 管脚RSTNCINT0/P3.2T0/P3.4T1/P3.5图2PLCC44管脚配置INT0/P3.2INT1/P3.3图4 TQFP44管脚配置5.2 管脚描述表3 P89LV51RD2管脚描述管脚符号DIP40 TQFP44 PLCC44类型描述P0.0~P0.7 39~32 37~30 43~36 I/O P0口:P0口是一个开漏双向I/O口。

广州周立功单片机 P89C51 89C52 89C54 89C58 说明书

指针低字节

82H

AF

AE

AD

AC

AB

IE*

中断使能

A8H

EA

ET2

ES

ET1

BF

BE

BD

BC

BBB

IP*

中断优先级

B8H

PT2H

PSH

PT1H

B7

B6

B5

B4

B3

IPH#

中断优先级高字节 B7H

PT2H

PSH

PT1H

87

86

85

84

83

P0*

P0 口

80H

AD7

AD6

AD5

AD4

AD3

97

96

95

94

特性

y 80C51 核心处理单元 y 片内 FLASH 程序存储器 y 速度可达 33MHz y 全静态操作 y RAM 可扩展到 64K 字节 y 4 个中断优先级 y 6 个中断源 y 4 个 8 位 I/O 口 y 全双工增强型 UART

―帧数据错误检测 ―自动地址识别 y 电源控制模式 ―时钟可停止和恢复 ―空闲模式 ―掉电模式 y 可编程时钟输出 y 异步端口复位 y 双 DPTR 寄存器 y 低 EMI (禁止 ALE) y 3 个 16 位定时器 y 掉电模式可通过外部中断唤醒

复位值

E0

00H

AO xxxxxxx0B1

DPS

02H1

F0

00H

00H

00H

A8

EX0 0x000000B

B8

PX0H xx000000B

B0

PX0H xx000000B

80

AD0

周立功写给学单片机的年轻人

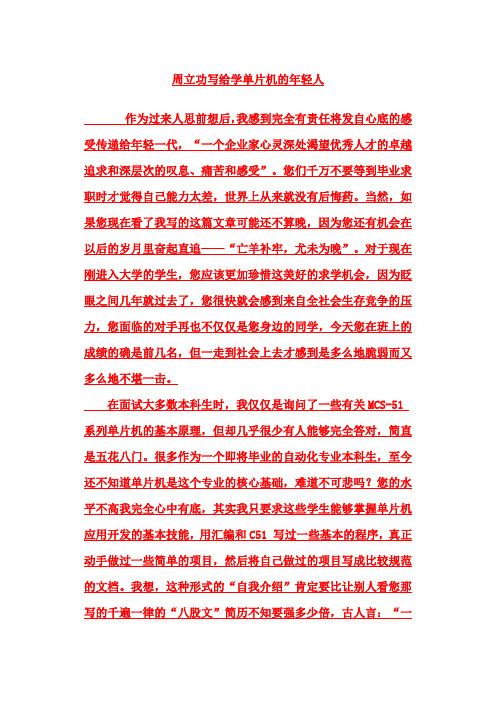

周立功写给学单片机的年轻人作为过来人思前想后,我感到完全有责任将发自心底的感受传递给年轻一代,“一个企业家心灵深处渴望优秀人才的卓越追求和深层次的叹息、痛苦和感受”。

您们千万不要等到毕业求职时才觉得自己能力太差,世界上从来就没有后悔药。

当然,如果您现在看了我写的这篇文章可能还不算晚,因为您还有机会在以后的岁月里奋起直追——“亡羊补牢,尤未为晚”。

对于现在刚进入大学的学生,您应该更加珍惜这美好的求学机会,因为眨眼之间几年就过去了,您很快就会感到来自全社会生存竞争的压力,您面临的对手再也不仅仅是您身边的同学,今天您在班上的成绩的确是前几名,但一走到社会上去才感到是多么地脆弱而又多么地不堪一击。

在面试大多数本科生时,我仅仅是询问了一些有关MCS-51 系列单片机的基本原理,但却几乎很少有人能够完全答对,简直是五花八门。

很多作为一个即将毕业的自动化专业本科生,至今还不知道单片机是这个专业的核心基础,难道不可悲吗?您的水平不高我完全心中有底,其实我只要求这些学生能够掌握单片机应用开发的基本技能,用汇编和C51 写过一些基本的程序,真正动手做过一些简单的项目,然后将自己做过的项目写成比较规范的文档。

我想,这种形式的“自我介绍”肯定要比让别人看您那写的千遍一律的“八股文”简历不知要强多少倍,古人言:“一叶知秋”其实讲的就是这个道理。

平心而论只有具备这样基础的学生才配得上企业花钱对您进行二次“开发”事实上,很多学生根本就不管老师平时是多么地劝导都听不进去,我认为您只要平时善于做一个有心人,主动一些多找老师请教,然后从大三开始帮老师打打下手干一些活。

还有一个途径就是自己花钱购买一些学习开发实验板,加强动手能力的训练。

但也有很多学生说没有钱,可事实上并非如此,现在的学生购买手机成风,我不知道手机对您们现在来说到底有多大的用途?事实上,现在的学生家庭条件普遍都不太好,可这些孩子们的攀比心里却十分地严重和可怕。

到今天即将毕业之际才感到找工作太难。

周立功单片机使用说明

周立功单片机使用说明:1.运行Keil uVision2,先建立工程,选择单片机型号philips 87C52X22.建立asm应用程序,目录和工程在同一地方,然后在Target 1中加载应用程序(用户程序***.asm)到工程中。

3.运行“Option for target”,在“OUTPUT”选项中选择“HEX FILE”4.编译生成HEX文件5.运行DPFLASH软件将HEX文件下载到单片机实验箱,注意改变load/run的模式。

该单片机实验箱有两款模式:直接下载模式与调试模式。

1.直接下载模式该模式把用户程序直接下载到实验相中的单片机外扩程序存储器flash中,该flash空间为64K,注意用户程序的首地址应为0000H,把用户声称的HEX文件通过DPFLSH下载到flash中,load完后,切换到Run状态,按下复位按键即可运行用户程序。

注意在Options for Target中的Output中选上Creat HEX File选项。

2.调试模式在该模式中需要把MON51监控程序下载到实验箱中的flash中,所占地址空间为0000—7FFFH,用户程序空间为8000---BFFFH,但是用户调试程序所占的空间为为外部SRAM,而非flash,用户数据空间为C000---FFFFH。

当MON51下载至实验箱后,将拨键拨到RUN状态。

在Options for Target 中off-chip code momory设置EProm 0x8000 size 0x4000; Off-chip Xdata momory Ram start oxc000 size ox4000.C51标签中Define :monitor51,并且选中Interrupt vectors at a 0X8000. Debug标签中选择USE Keil Monotor-51 Debug。

Setting:选波特率9600。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2

always @ (current_state ...) ... case(current_state) ... s1: if ...

next_state = s2; ... ... always @(posedge clk or negedge rst_n) ... else a <= 1'b0; c <= 1'b0; c <= 1'b0;//赋默认值

如果在另一个设计中的时钟是 40ns,复位周期不变,我们只需对 CLK_PERIOD 进行 重新例化就行了,从而使得代码更加易于重用。

1.2.2 信号命名要规范化

1) 信号名一律小写,参数用大写。 2) 对于低电平有效的信号结尾要用_n 标记,如 rst_n。 3) 端口信号排列要统一,一个信号只占一行,最好按输入输出及从哪个模块来到哪 个模块去的关系排列,这样在后期仿真验证找错时后 方便很多。如:

11)状态机要写成 3 段式的(这是最标准的写法),即

... always @(posedge clk or negedge rst_n) ... current_state <= next_state; ...

工程技术笔记

©2010 Guangzhou ZHIYU AN Electronics CO., LTD.

case(current_state) s1: a <= 1'b0;//由于上面赋了默认值,这里就不用再对 b 、c 赋值了(b、c 在该状态为 0,不会产生锁存器,下同) s2: b <= 1'b1; s3: c <= 1'b1; default: ...

...

1.3 ALTERA 参考设计准则

1) Ensure Clock, Preset, and Clear configurations are free of glitches. 2) Never use Clocks consisting of more than one level of combinatorial logic. 3) Carefully calculate setup times and hold times for multi-Clock systems. 4) Synchronize signals between flipflops in multi-Clock systems whenthe setup and hold time requirements cannot be met. 5) Ensure that Preset and Clear signals do not contain race conditions. 6) Ensure that no other internal race conditions exist. 7) Register all glitch-sensitive outputs. Synchronize all asynchronous inputs. 9) Never rely on delay chains for pin-to-pin or internal delays. 10)Do not rely on Power-On Reset. Use a master Reset pin to clear all flipflops. 11)Remove any stuck states from state machines or synchronous logic. 其它方面的规范一时没有想到,想到了再写,也欢迎大家补充。

在逻辑详细设计方案这一级的时候,我们已经将各级模块的接口时序都设计出来了,各 级模块内部是怎么实现的也基本上确定下来了。由于做到这一点,在编码的时候自然就很快 了,最重要的是这样做后可以让设计会一直处于可控的状态,不会因为某一处的错误引起整 个设计从头进行。

1.3

ALTERA 参考设计准则 ............................................................................... 3

2. 时序是设计出来的...................................................................................................4

5) 尽量在底层模块上做逻辑,在高层尽量做例化,顶层模块只能做例化,禁止出现任 何胶连逻辑(glue logic),哪怕仅仅是对某个信号取反。理由同上。

6) 在 FPGA 的设计上禁止用纯组合逻辑产生 latch,带 D 触发器的 latch 的是允许的, 比如配置寄存器就是这种类型。

7) 一般来说,进入 FPGA 的信号必须先同步,以提高系统工作频率(板级)。 所有模 块的输出都要寄存器化,以提高工作频率,这对设计做到时序收敛也是极有好处的。

在我们公司,每一个项目都有很严格的评审,只有评审通过了,才能做下一步的工作。 以做逻辑为例,并不是一上来就开始写代码,而是要先写总体设计方案和逻辑详细设计方案, 要等这些方案评审通过,认为可行了,才能进行编码,一般来说这部分工作所占的时间要远 大于编码的时间。

总体方案主要是涉及模块划分,一级模块和二级模块的接口信号和时序(我们要求把接 口信号的时序波形描述出来)以及将来如何测试设计。在这一级方案中,要保证在今后的设 计中时序要收敛到一级模块(最后是在二级模块中)。什么意思呢?我们在做详细设计的时 候,对于一些信号的时序肯定会做一些调整的,但是这种时序的调整最多只能波及到本一级 模块,而不能影响到整个设计。记得以前在学校做设计的时候,由于不懂得设计时序,经常 因为有一处信号的时序不满足,结果不得不将其它模块信号的时序也改一下,搞得人很郁闷。

o|> || | /

clk | -------- |---- -----------------------------------10)禁止用计数器分频后的信号做其它模块的时钟,而要用改成时钟使能的方式,否则 这种时钟满天飞的方式对设计的可靠性极为不利,也大大增加了静态时序分析的复杂性。如 FPGA 的输入时钟是 25M 的,现在系统内部要通过 RS232 与 PC 通信,要以 rs232_1xclk 的 速率发送数据。 不要这样做:

©2010 Guangzhou ZHIYU AN Electronics CO., LTD.

1

avalon_dout, //related to avalon bus ...

);

4) 一个模块尽量只用一个时钟,这里的一个模块是指一个 module 或者是一个 entity。 在多时钟域的设计中涉及到跨时钟域的设计中最好有专门一个模块做时钟域的隔离。这样做 可以让综合器综合出更优的结果。

1.1 设计必须文档化

要将设计思路,详细实现等写入文档,然后经过严格评审通过后才能进行下一步的工作。 这样做乍看起来很花时间,但是从整个项目过程来看,绝对要比一上来就写代码要节约时间, 且这种做法可以使项目处于可控、可实现的状态。

1.2 代码规范

1.2.1 设计要参数化

比如一开始的设计时钟周期是 30ns,复位周期是 5 个时钟周期,我们可以这么写:

3. 如何提高电路工作频率...........................................................................................5

3.1

通过改变走线的方式减少时延 ..................................................................... 5

工程技术笔记

©2010 Guangzhou ZHIYU AN Electronics CO., LTD. 1

1. 规范很重要

工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是 硬件),不按照规范走几乎是不可实现的。逻辑设计也是这样:如果不按规范做的话,过一 个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错 了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版 本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。在逻辑方面,我觉 得比较重要的规范有这些:

parameter CLK_PERIOD = 30; parameter RST_MUL_TIME = 5; parameter RST_TIME = RST_MUL_TIME * CLK_PERIOD; ... rst_n = 1'b0; # RST_TIME rst_n = 1'b1; ... # CLK_PERIOD/2 clk <= ~clk;

always (posedge rs232_1xclk or negedge rst_n) begin ... end

而要这样做:

always (posedge clk_25m or negedge rst_n) begin ... else if ( rs232_1xclk == 1'b1 ) ... end

module a( //input clk, rst_n,//globle signal wren, rden, avalon_din, //related to avalon bus sdi,//related to serial port input //output data_ready,

工程技术笔记

目录

1. 规范很重要...............................................................................................................1

1.1 1.2 1.2.1 1.2.2