【SoCVista】数字信号处理系列讲座之6.折叠

【SoCVista】6.折叠

折叠在我们讨论的四种上古神器(包括:重定时、展开、折叠和脉动)中,展开和折叠是相生相克的。

这两件神器一伸一缩,代表两种相反的做法,但各有其用武之地。

这一帖推出的上古神器是:双刃剑之一折叠。

在电子系统的设计过程中,有时可用的逻辑资源非常有限。

也许这时候不得不牺牲系统的吞吐率来换取占用面积的减少。

以4x4乘法器设计为例:如果要求高速度,那么宜采用阵列式乘法器结构,如图一,其中使用了12个一位加法器(全加器/半加器);相反,如果对速度要求不高,而要求面积占用要小,那么应该使用串行时序乘法器,如图二所示。

注意一点,图一的阵列乘法器为纯组合逻辑电路,而图二串行时序乘法器是由时钟控制的时序电路。

将一个阵列乘法器改写为串行时序乘法器是比较容易的,仔细观察图一的阵列式乘法器结构可知,一个阵列式乘法相当于“三个”加法的级联,串行时序乘法器的思路就是,只采用“一个”加法器来实现乘法运算,如此显然还需要一些寄存器来存放中间数据,以及一些控制逻辑(状态机等)。

一般说来,串行时序乘法器比阵列式乘法器实现所占资源要少一些。

题外话:某些情况,串行时序乘法器不见得比阵列式乘法器所占资源少,比如2x2 的乘法器,阵列式结构需要资源反而少一些,这与控制逻辑和中间寄存器的复杂程度有关。

这里只是想说明一个观点:折叠起来的结构往往比展开的结构更省资源,但不表示绝对100%成立。

图 1 4x4 阵列式乘法器结构图 2 串行时序乘法器结构总而言之,当对吞吐率要求不高而且系统中存在大量功能相同的节点时,可以考虑使用分时复用的折叠技术,把功能相同节点折叠成一个节点(或若干个,反正是比原来要少)来达到缩减资源占用的目的。

可想而知,折叠之后的系统结构要想保持原有功能不变,必然要加入一定量的寄存器资源用于存放中间计算结果,以及控制逻辑(包括状态机和选路器等)。

本章给大家介绍的是一种极为通用的折叠技术,能让你把系统中功能相同的节点折叠成一个节点,不仅给出如何来构造控制逻辑的方法,还进一步优化寄存器资源的使用。

数字信号处理方法及技巧总结

数字信号处理方法及技巧总结数字信号处理(Digital Signal Processing,简称DSP)是指对离散信号进行一系列算法和技术处理的过程。

本文总结了数字信号处理的一些常见方法和技巧,供参考使用。

傅里叶变换傅里叶变换是一种广泛应用于数字信号处理中的重要方法。

它可以将时域信号转换为频域信号,从而揭示信号的频率特征。

常见的傅里叶变换包括离散傅里叶变换(Discrete Fourier Transform,DFT)和快速傅里叶变换(Fast Fourier Transform,FFT)。

在信号的频谱分析、滤波和相关性分析中,傅里叶变换是一种不可或缺的工具。

滤波技术滤波是数字信号处理中常用的技术之一。

它可以去除信号中的噪声或不需要的频率成分,以提取感兴趣的信号信息。

常见的滤波方法包括低通滤波、高通滤波、带通滤波和带阻滤波。

根据信号的特点和需求,选择适当的滤波技术可以有效改善信号质量。

采样与重构数字信号的采样与重构是数字信号处理中一个重要的环节。

采样是将连续时间域信号转换为离散形式的过程,而重构则是根据离散信号重新生成连续信号。

采样定理(Nyquist定理)指出,为了完全还原原始信号,采样频率需满足一定条件。

在实际应用中,合理选择采样频率可以平衡信号质量与计算复杂度。

时域与频域分析时域分析和频域分析是数字信号处理中常用的分析方法。

时域分析关注信号在时间上的变化,常见的时域分析方法有自相关函数和互相关函数等。

而频域分析则关注信号在频率上的特性。

通过频域分析,我们可以得到信号的频谱信息,来研究信号的频率分布和频率成分之间的关系。

数字滤波器设计数字滤波器是数字信号处理中的重要组成部分。

根据滤波器的结构和响应特性,可以将其分为滤波器与无限脉冲响应(FIR)滤波器等。

设计数字滤波器的关键是确定滤波器的参数,如截止频率、通带和阻带的波动范围等。

选择合适的滤波器类型和参数可以实现对信号的有效滤波和增强。

运算速度与算法优化在数字信号处理中,运算速度和算法优化是需要考虑的重要问题。

折叠式共源共栅cmos运算放大器的设计与优化

折叠式共源共栅cmos运算放大器的设计与优化下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!折叠式共源共栅CMOS运算放大器的设计与优化1. 引言在集成电路领域,CMOS运算放大器一直是研究的热点之一。

【SoCVista】2007年国际半导体技术发展路线图摘要介绍

2007年国际半导体技术发展路线图摘要介绍2007年版的国际半导体技术发展路线图,是ITRS面世之后的第5次全面修订,于2008年2月正式在世界范围内发布其最后定稿。

本文将向读者介绍本版路线图一些新的重要理念,并对未来十五年内半导体行业面临的严峻挑战进行了汇总。

四十年来,半导体工业最明显的特征之一,就是它的产品的更新换代非常迅速。

绝大部分的改进和提高都是由一个重要特征表示的,即:制造集成电路的最小尺寸可以不断地呈指数性地迅速缩小。

显然,我们最常引用的发展趋势就是摩尔提出来并以他的名字命名的“摩尔定律”。

对于社会来讲,最为重要的发展趋势是降低单位功能的成本,使人们可以享用到更多的计算机、电子通讯产品和消费电子产品,从而大幅度提高了劳动生产率和人们的生活质量。

自从集成电路诞生的那一天起,就有一个基本的假设:微电子器件可以继续按比例缩小并进而降低单位功能的成本,同时扩展半导体集成电路的市场。

在高度竞争的半导体市场,从业者无不思考着这样一个问题:究竟需要研发出什么样的技术才能继续沿着摩尔定律指引的方向前进?为了回答这个问题,美国半导体工业协会(the Semiconductor Industry Association,SIA)发起编写了美国国家半导体技术发展路线图(National Technology Roadmap for Semiconductor,NTRS),共发表了1992年、1994年和1997年三个版本。

在1998年,由美国半导体工业协会提议,邀请了欧洲、日本、韩国和台湾等国家和地区的人士参加,对路线图进行了更新,最终形成了1999年的第一版国际半导体技术发展路线图(The International Technology Roadmap for Semiconductors,ITRS)。

在此之后,国际半导体技术发展路线图在每偶数年份进行更新,每单数年份进行全面修订。

ITRS的整体目标是提供被工业界广泛认同的对未来十五年内研发需求的最佳预测。

【SoCVista】有关FSDB文件的一些问题

有关FSDB波形文件的一些问题作者:justdoit、winfire、dicer、5life 等等一、介绍三个术语:VCD:Value Change Dump 文件,Fsdb:Fast Signal DataBase文件,WLF:Wave Log File 文件,对于WLF波形日志文件,只要我们使用过modelsim,应该都很熟。

但我们在波形窗口观察波形时,仿真结束时都会生成一个*.wlf的文件(默认是vsim.wlf)。

我们下次就可以通过通过modelsim直接打开这个保存下来的波形。

vsim -view vsim.wlf -do run.do其中run.do中的内容为要查看的波形信号。

要强调的是这个wlf文件只能是由modelsim来生成,也只能通过modelsim来显示。

不是一个通用的文件文件格式。

VCD文件是IEEE1364标准(Verilog HDL语言标准)中定义的一种ASCII文件。

可以通过Verilog HDL的系统函数$dumpfile,$dumpvars等来生成。

我们可以通过$dumpvars的参数来规定。

我们抽取仿真中某个特定模块和信号的 VCD数据。

它主要包含了头信息,变量的预定义和变量值的变化信息。

正是因为它包含了信号的变化信息,就相当于记录了整个仿真的信息。

我们可以这个文件来再现仿真,也就能够显示波形。

另外我们还可以通过这个文件来估计设计的功耗。

解决了前一段时间一直不知道这个vcd文件用来干什么的疑问。

因为VCD是Verilog HDL语言标准的一部分,因此所有的verilog的仿真器都要能实现这个功能。

因此我们可以在verilog代码中通过系统函数来dump VCD文件。

另外,我们可以通过modelsim 命令来dump VCD文件,这样可以扩展到VHDL中。

具体的命令:vcd file myfile.vcdvcd add /test/dut/*这个就生成一个含dut下所有信号的VCD数据信息。

数字信号处理ppt课件共150页PPT

数字信号处理ppt课件

1、战鼓一响,法律无声。——英国 2、任何法律的根本;不,不成文法本 身就是 讲道理 ……法 律,也 ----即 明示道 理。— —爱·科 克

3、法律是最保险的头盔。——爱·科 克 4、一个国家如果纲纪不正,其国风一 定颓败 。—— 塞内加 5、法律不能使人人平等,但是在法律 面前人 人是平 等的。 ——波 洛克

12

•good reasons for learning DSP

• It's the future! Think how electronics has changed the world in the last 50 years. DSP will have the same role over the next 50 years. Learn it or be left behind!

– filtering, speech recognition, – image enhancement, – data compression, – neural networks, – and much more.

10

• Digital Signal Processing (DSP) is used in a wide variety of applications.

Digital Signal Processing----

【SoCVista】关于CPU的local memory的一些杂谈

关于CPU的local memory的一些杂谈Bruce Zhan2008-7-41.为什么使用local memory?简单来说,就是让memory系统贴近CPU,最大限度发挥(而不是提高)CPU自身的性能。

几乎所有的SOC设计,都是分层的memory架构,越贴近CPU,access所需要的时间越短,越远离CPU,access所需要的时间越长;每多一个memory层次(可以用x86系统的L1 cache,L2 cache想象),访问时间都有数倍的增加。

我前段时间的参与设计的一个SOC项目中,当cache missed后,CPU(cache)访问片外的SDRAM,delay达到30多个cycle(可以想象,当没有cache,而只使用CPU直接访问外部SDRAM,CPU的性能会被拖累成什么样子,读一个数据要等30个cycle,恐怖啊;当然memory子系统访问的延迟,不同的设计会导致较大的差距,并不是每个SOC访问片外的memory的delay都会达到30个cycle)。

CPU访问cache,命中时是可以即时取道的。

因此不同的应用情况,cache会有不同的大小,不同的实现复杂度。

但是cache的问题是,无法预测什么时候会命中,什么时候会miss。

在一些实时性要求高的应用中不能满足要求。

而所谓的close-coupled local memory就不会存在这个问题。

2.Local memory的设计目标?Local memory设计目标就是,CPU访问时尽量达到zero/或近似zero的延迟。

3.Local memory和cache的主要区别?Local memory和cache的区别主要就是数据的换入换出是否CPU或者程序员是否知道。

Local memory中的数据在“大部分”时间是不会与外部memory交换数据的,如果需要的话,是在CPU与DMA(DMA根据应用需要考虑要或者不要)配合下完成的,并且可以通过用类似pingpong等小trick使数据在local memory和外部memory的搬移时间隐藏起来,使性能进一步提高。

【SoCVista】5.展开

双刃剑之一展开在我们讨论的四种上古神器(包括:重定时、展开、折叠和脉动)中,展开和折叠是相生相克的。

这两件神器一伸一缩,代表两种相反的做法,但各有其用武之地。

这一帖推出的上古神器是:双刃剑之一展开。

那么展开是什么意思呢?看看课本上的定义:展开用于产生一个新的程序来描述原有程序的多次迭代。

更具体的说,以展开因子J(unfolding factor J)展开一个DSP程序,就会产生一个以原程序连续迭代J次的新程序。

展开也被称为“环路展开”。

试图直接去理解这个定义很困难。

我猜测这是因为看问题的角度不正确而致,往往直到看完了整章才恍然大悟。

我们不急着进入正题,而是先来谈谈DSP程序到底是个什么,可以怎么来看待DSP程序。

个人见解:DSP程序本质上是对一系列的输入数据进行某种形式的处理(如滤波),然后按一定的次序输出结果数据。

可由软件或者硬件来进行这种处理,但不论何种实现形式,都会涉及到数据的存储和计算。

如果是软件实现,数据是存储在用户定义的变量中;如果是硬件实现,数据存储在延时单元中。

DSP程序具有特定的功能,对于设计者而言,只要能保证DSP的功能不变,可以对DSP的具体实现进行各种调整,以满足实际应用的指标。

综上所述,DSP程序的实现可以看成是对输入数据进行存储和计算的过程,期间还会产生中间数据,也需要临时的存储。

打个比方,制衣厂将面料做成漂亮的衣服,面料就是输入数据,衣服就是输出数据,要将面料做成衣服需要经过多道工序,中间的半成品需要临时仓库来存储;同样是制衣厂,完成相同功能,但是工厂的部门配置、员工组织和仓库等却可以因地制宜。

我们讨论的其他三件神器,都是可以看做一个“工厂”,在保证功能不变的提前下,可以对内部的数据存储和计算流程进行重新的安排,以便达到各个性能指标之间的折中。

下面的讨论分三节:1.展开的概念和做法,读完这一节,就可以对任何一个没有开关(多路选择器)的DFG进行J(J为任意正整数)阶展开。

【SoCVista】cyclone系列FPGA SOPC学习套件

Cyclone 系列 FPGA SOPC学习套件EP1C6型V2.0版本仅需550元!核心板和实验板全面升级EP1C6核心板升级为V2.0版本,增加8MByte SDRAM,2MByte Flash,可容纳更多的用户程序和数据;实验板升级为V2.0版本,增加了USB等功能!CT-SOPCx学习套件,针对Altera的低成本高性能Cyclone系列FPGA,助学习者快速掌握FPGA/SOPC设计技术。

(1) 学习FPGA的设计技术;(2) 了解NiosII可编程片上系统的设计流程,学习在FPGA上包括定制32位的处理器、DSP处理模块、逻辑功能模块等组成的系统;学习利用ALTERA公司提供的软件集成开发环境(NIOS IDE)设计、调试片上系统的软件;(3) FPGA核心板可用于系统设计前期快速评估设计方案。

CT-SOPCx学习套件有以下主要特点:(一) 设计独特,既适合学生学习使用,也适合于实际项目设计中快速搭建系统原型以验证设计方案。

核心板(EP1C6型V2.0)实际上是一块独立的SOPC最小系统板,SDRAM和Flash都集成在核心板上,用户甚至可以用面包板制作特定项目所需的外围电路,并插上该核心板就构成了一个完整的项目系统原型。

另外,如果项目试验中只需用到FPGA功能(即无需定制Nios系统),则可以将SDRAM和Flash卸下,核心板就成了一个将所有FPGA的IO管脚引出的FPGA核心板,同样可用于快速搭建项目系统原型。

(二) 模块化结构,简单明了,有详尽文档、教程,真正适合初学者。

经验表明,很多学生在学习FPGA、ARM、DSP等设计技术的过程中,虽然刚开始学习热情很高,但真正能坚持下来一直到“学会”的却只有寥寥几个。

除了学生个人的毅力因素的原因外,另外一个更主要的原因是由于所选用的学习板不适合初学者学习使用。

对于初学者来说,理解和消化开发板并不容易(事实上如果能达到这种程度的话,也就没必要借助学习板了),再加上这些开发板在文档资料、教程上都非常欠缺,有些几乎连说明文档都没有,这就给学生们的学习增添了更多的困难,很多学生会因为找不到入门的口子而慢慢失去兴趣和信心。

【SoCVista】Candence NC-Verilog simulator tutorial

Candence NC-Verilog simulator tutorial第一章介绍这个手册将向你介绍使用NC-Verilog simulator和SimVision。

本文使用的是一个用Veilog硬件编程语言编写的一个饮料分配机,通过这个例子你将学会:·编译Verilog源文件,描述设计,在NC-Launch(用于管理你的大型设计的图形交互接口)上进行设计的仿真。

NCLaunch帮助你配置和启动编译器,描述器和仿真器。

当然你还可以在NCLaunch上运行像SDF compiler,HDL Analysis and Lint,Code Coverage Analyzer, NCBrowse, and Comparescan.之类的工具。

·在SimVision分析环境下进行对设计中的问题的调试。

SimVision是一个candence 仿真器统一的图形化的调试环境。

SimVision可以用于调试用verilog,vhdl,SystemC或者它们混合写成的数字,仿真,或数模混合电路的设计。

你可以在以下几种模式运行SimVision:·Simulate模式在Simulate模式下你可以实时的看到仿真的数据。

也就是说,你可以在仿真仿真的过程中就进行数据的分析。

你可以通过对设计设置断点和分步来达到控制仿真的。

为了帮助你追踪整个仿真过程,SimVision提供了几个工具:·控制台窗口 Console Window·源浏览器 Source Browser·设计浏览器 Design Browser·循环阅读器 Cycle Viewer·原理图追踪 Schematic Tracer·信号流浏览器 Signal Flow Browser·波形窗口 Waveform Window·寄存器窗口 Register Window这些窗口之间是连接了的,所以如果你在一个窗口中选中了一个对象,那么在其它窗口中也会被选中。

【SoCVista】Xilinx FPGA仿真与验证实例

Digital IC Lab文件名稱:Simulation and Verification with Xilinx FPGA撰寫人員:林宜民(依姓氏筆劃)硬體要求:PC、Xilinx FPGA Spartan3 XC3S1500軟體要求:ModelSim SE 5.6、Synplify Pro 7.2、Xilinx ISE 6.3i文件版本:Version 1.2 (1/24/2006)工作內容:1.設計一個組合電路(解碼器)。

2.設計一個循序電路(移位暫存器)。

3.利用Xilinx ISE的CoreGenerator(以下簡稱CoreGen)產生RAM,ROM跟一個乘法器的IP,並藉以完成一個新的電路設計。

補充事項:1.一般硬體描述語言(Hardware Description Language,HDL)可分為VHDL與Verilog兩種,而Verilog是以類似C的語法來描述硬體電路,並擁有各種不同層次的表示方式。

2.模擬器(Simulator)是用來模擬電路的波形。

3.合成工具(Synthesizer)的功用是將HDL轉換成由電路所組成的Netlist。

4.一般而言,在電路設計的模擬上可分為Pre-Sim跟Post-Sim。

Pre-Sim是針對電路的function做模擬,此時只在意由HDL所撰寫的程式之function 是否正確,而Post-Sim則是針對合成過且做完APR(Auto Place and Route)的電路做模擬,以確保所設計的電路實現在FPGA上時,與Pre-Sim的function一樣。

組合電路二對四解碼器※名詞解釋:解碼器(Decoder)的功能是將編碼過的資料做解碼,以得到原始的資料。

※真值表:※示意圖:in0out0enablein1out1out2out3Pre-Sim步驟一:開啟ModelSim ,然後建立一個Project 。

※建立Project 的方式為點選File → New → Project …。

【SoCVista】一种基于DDS芯片AD9959的高精度信号发生器

e r Z le asr cu o A】 9 9 i 各 n r tu tr f 刃 5 tl n

内有 F u r最大可选4 i串行 F O口Bf , e b t O口, 且 高低位 M B巧B S/ 可选, 大大增加了数据的传输量。

时钟后, 回到初态( 其中N为相位累加器的字长) 。 在实际设计中, 由于受到成本、O R M容量等的限 制, 相位累加器输出的位并不完全用于寻址, 通常会截 取高X 位用于寻址, N一 低 X位则无效。这样做会造 成少量的相位误差, 但不影响频率的分辨率。

一下它的特点 :

① 最大采样频率可达s M P ; o S S ② 内含四通道 D S每通道之间可独立进行频 D, 率、 相位、 幅度的控制; ③ 具有良 好的通道间隔离( 6 d ; > B 5 ) 输出的频率是由参考时钟f、 c 相位累加器字长N ④ 线性的频率、 相位、 幅度扫描能力; 和频率控制字f 决定的, c , 关系式如下: ⑤4 通道配有各自 ob DA 的ri / 转换器; t ⑥ 每个通道具有 犯 b 的频率分辨率、 b 的 i t 巧i t o f 几/ f = x 2“ c ( ) 1 相位分辨率以及 1 b 的幅度分辨率; 0i t 当 ,1 即为频率 c f = 时, 分辨率: 二 /“ 鱿 f c 2 ⑦ 最多可达 6 1 级电平的调制( K PK A K ; S S F 、 、S ) 根据奈奎斯特准则, 在一个周期内至少采样两点, ⑧ DC A 满偏电流可灵活设置; 但在实际设计中一般为了可靠性至少取3 4 一 个点, 这 ⑨ 软硬件皆可控制开关; 样最- ,· 出 率 达“ ’ “‘率 丰一 。 可 一 系 频 的 3. · , 的, 频” 一 到 统 、,” 4 李 ,- 大 输 , ,。/ - “一 份’ ⑩ 4 2 倍乘可选的系统时钟; 一0 ⑩ 可多芯片同步等。 2 A 99 9 D 5 芯片性能简介 在图2中可看出, 由于内部 R M的限制, 位相 O 犯 A 99 9 D5 芯片是 A 公司生产的高采样频率、 D 高精 位累加器输出的值取前 巧 位进行 R M寻址, O 转换成 度DS D 芯片, 其内部结构如图2 所示。下面简要介绍 0 1 位幅度信号, 最后经 r 位 D C输出为正弦信号。 o A

信号发生器频谱折叠

信号发生器频谱折叠1.引言1.1 概述信号发生器频谱折叠问题是在数字信号处理中常见的一个现象,它对信号发生器的性能和精度有着重要的影响。

频谱折叠指的是当信号的频率超过采样频率的一半时,信号的高频分量会被错误地表示为低频分量,从而导致频谱的混叠现象。

在今天的数字信号处理应用中,信号发生器扮演着至关重要的角色。

它们用于产生各种类型的信号,包括正弦波、方波、脉冲信号等。

然而,由于信号发生器的输出是离散的,其输出信号的频谱存在限制,即采样定理要求采样频率必须高于信号频谱的两倍。

然而,在实际的应用中,由于采样率的限制或信号本身的特性,频谱折叠问题可能会出现。

频谱折叠会导致信号频谱中的高频分量被错误地表示为低频分量,从而影响到信号的完整性和准确性。

这对于很多需要高精度和高稳定性的应用来说是不可忽视的。

因此,本文将重点讨论信号发生器频谱折叠问题,探讨其对信号发生器的影响以及如何避免频谱折叠问题的方法。

通过深入了解频谱折叠的概念和原因,读者将能够更好地理解信号发生器的工作原理,并在实际应用中更好地应对频谱折叠问题。

文章结构部分(1.2 文章结构):本文将按照以下结构进行叙述:引言、正文和结论三个部分。

引言部分首先概述了本文的主题:“信号发生器频谱折叠”。

随后介绍了本文的结构,包括各个章节的大致内容和目的。

正文部分将详细探讨信号发生器的作用和频谱折叠的概念。

在信号发生器的作用部分,我们将详细介绍信号发生器在各个领域中的应用,并解释其重要性。

接下来,在频谱折叠的概念部分,我们将对频谱折叠进行定义和解释,包括其产生的原因和影响。

结论部分将总结本文的主要内容。

首先,我们将讨论频谱折叠对信号发生器的影响,包括可能引起的误差和失真。

然后,我们将提供一些解决频谱折叠问题的方法和建议,以避免潜在的影响。

通过以上结构,本文将全面介绍信号发生器频谱折叠这一主题,并为读者提供有效的解决方案和建议。

下面将详细阐述各个部分的内容。

文章1.3 目的部分的内容可以描述为:为了进一步探讨信号发生器频谱折叠问题,本文旨在分析频谱折叠对信号发生器的影响并提出相应的解决方案。

halcon 折叠相位提取方法

halcon 折叠相位提取方法Halcon是一种用于深度学习的开源框架,提供了许多强大的功能,包括折叠(folded)和相位(相位)提取方法。

折叠是一种常用的神经网络参数更新方法,用于在损失函数和梯度下降算法之间实现平衡。

相位是一种用于处理时间序列数据的数学概念,可以用于预测和分类问题。

下面是Halcon折叠相位提取方法的详细步骤:1. 加载数据:使用Halcon中的`load_data`函数加载需要计算折叠相位的数据。

该函数支持多种数据格式,包括张量、矩阵和JSON等。

2. 定义折叠:定义折叠的符号和类型。

在Halcon中,折叠符号由两个部分组成:前缀和后缀。

前缀表示折叠的位置和方向,后缀表示折叠的内容。

例如,对于向左折叠,前缀为"<",后缀为"|";对于向右折叠,前缀为">",后缀为"?"。

类型指定了折叠的性质,例如是否只保留行或只保留列。

3. 计算折叠相位:使用Halcon中的`calculate_folded`函数计算折叠相位。

该函数需要输入两个张量:输入张量(input)和输出张量(output)。

它返回一个新的张量,该张量包含了输入张量和输出张量之间的折叠关系。

例如,对于输入张量"input.h",输出张量"output.h",计算折叠相位的代码如下:```#include <halcon/v5/math.h>#include <halcon/v5/table.h>#include <halcon/v5/vector.h>using namespace halcon;int calculate_folded(vector<vector<int>>& input,vector<vector<int>>& output, vector<int>& fold_data){// 定义输入张量vector<vector<int>> input_data = input;// 定义输出张量vector<vector<int>> output_data = output;// 定义折叠张量vector<int> fold_info = {0, 0, 0, 0};// 计算折叠相位halcon::Table<double>折叠_相位 =calculate_folded_table(fold_data.size(), fold_info);double折叠_相位_value =折叠_相位.get();// 更新折叠张量fold_info[0] = fold_相位_value;// 返回更新后的折叠张量return fold_info;}void calculate_folded_table(size_t n, vector<int>& fold_info) {// 定义输入张量vector<vector<int>> input_data = {1, 2, 3, 4, 5};// 定义输出张量vector<vector<int>> output_data = {fold_info[0], fold_info[1], fold_info[2], fold_info[3], fold_info[4]};// 计算折叠相位halcon::Table<double>折叠_相位 =calculate_folded_table_table(input_data.size(), fold_info);double折叠_相位_value =折叠_相位.get();// 更新折叠相位for (int i = 0; i < input_data.size(); i++){double 相位 =折叠_相位_value - fold_info[i];折叠_相位[i] = fold_相位_value;折叠_相位_value = 相位;}}int main(){// 加载数据vector<vector<int>> input = {1, 2, 3, 4, 5};vector<vector<int>> output = {1, 2, 3, 4, 5};// 计算折叠相位vector<int> fold_info = calculate_folded(input, output, input); // 输出结果cout << "Folded相位提取结果:";for (int i = 0; i < fold_info.size(); i++){cout << fold_info[i] << " ";}cout << endl;return 0;}这段代码中,`calculate_folded`函数用于计算折叠相位,它接收输入张量、输出张量和折叠数据作为参数。

(完整版)七年级计算机科学折叠问题总结

(完整版)七年级计算机科学折叠问题总结本文旨在总结七年级计算机科学研究中的折叠问题,并给出方便理解和解决这些问题的简明策略。

1. 什么是折叠问题?折叠问题是指在计算机科学中,对于具有一定长度和宽度的纸张进行叠折后,与折叠前纸张上的图案相对应的问题。

常见的折叠问题包括纸飞机的折叠路径、纸片上的几何图形等。

2. 折叠问题的解决策略为了解决折叠问题,我们可以采用以下简明策略:2.1. 简化问题在解决折叠问题之前,我们可以尝试简化问题,例如将复杂的图形转化为简单的几何形状,或者对纸张进行抽象化,以便更容易理解和推导。

2.2. 几何知识的应用对于涉及几何图形的折叠问题,我们可以运用几何知识来辅助求解。

例如,通过计算折叠后的纸张上某个点的位置,我们可以推导出折叠前这个点所在位置的坐标。

2.3. 迭代和模拟对于复杂的折叠问题,我们可以采用迭代的方法来逐步求解。

可以将纸张的折叠过程分成多个步骤,每个步骤都根据前一步的结果来进行计算。

另外,模拟折叠过程也是一种常用的解决策略,通过模拟折叠过程来获得最终结果。

2.4. 数字化和编程对于涉及大量计算的折叠问题,可以考虑将纸张和折叠过程数字化,并使用计算机编程来求解。

编写程序可以提高计算速度和准确性,同时也能够实现对不同情况的扩展和自动化处理。

3. 注意事项在解决折叠问题时,我们需要注意以下几点:3.1. 保持精确性折叠问题涉及到几何计算和数字计算,对数值的精确性要求较高。

在计算过程中,需使用合适的数值表示方法和准确的计算方式,以避免计算误差。

3.2. 验证和优化在求解折叠问题后,需对结果进行验证,确保答案符合预期。

同时,我们也可以优化求解过程,减少计算时间和资源消耗。

3.3. 整体思考解决折叠问题不仅仅是局部计算,还需要将整体情况考虑在内。

预先规划好计算步骤,并在计算过程中及时调整和优化。

4. 总结折叠问题是计算机科学中的常见问题,解决这类问题需要运用数学、几何知识和计算机编程等多方面的技能。

光变曲线 相位折叠程序

光变曲线相位折叠程序

光变曲线(Lightcurve)是指天体在一段时间内亮度随时间变化的情况。

相位折叠程序(Phase folding program)是一种用于处理光变曲线的算法,它将周期性的信号转换为一个静态的信号。

在光变曲线中,如果天体的运动或变化是周期性的,如行星的自转或卫星的绕行,那么光变曲线就会呈现出周期性的变化。

而相位折叠程序则是将这种周期性的信号进行转换,使其变为一个静态的信号。

具体来说,相位折叠程序首先会确定信号的周期,然后根据这个周期将信号分成多个阶段。

接着,程序会计算出每个阶段信号的平均值,并将这些平均值连接起来,形成一个新的静态信号。

通过相位折叠程序的处理,原本周期性的信号就被转换为了一个静态的信号,可以更加方便地进行处理和分析。

例如,在处理行星的自转时,相位折叠程序可以将每个自转周期的信号转换为一个静态的信号,从而可以更加准确地计算出行星的自转速度和质量等参数。

需要注意的是,相位折叠程序只适用于周期性的信号,对于非周期性的信号则无法进行有效的处理。

此外,由于相位折叠程序需要先确定信号的周期,因此对于一些不规则变化的信号,其处理效果可能会受到一定的影响。

基于折叠变换的 CORDIC 算法实现

基于折叠变换的 CORDIC 算法实现黄宇声;李朝海【期刊名称】《雷达科学与技术》【年(卷),期】2014(000)004【摘要】在现代数字信号处理领域中,CORDIC算法是一种重要的数学计算方法。

该算法采用一种迭代的方式,运算简便,被广泛应用于乘除法、开方以及一些三角函数运算当中。

但 CORDIC 算法需要较高的迭代级数以保证运算精度,在进行FPGA 实现时仍然会消耗较多的硬件逻辑资源。

为进一步减少 CORDIC算法实现时的资源消耗,设计并实现了一种基于折叠变换的 CORDIC 算法。

相比传统的流水结构 CORDIC算法,该折叠结构的 CORDIC 算法消耗的硬件资源大大减少。

文中给出了这一方法的实现结构,并给出了仿真结果。

%The CORDIC algorithm is an important method in modern digital signal processing.The CORDIC algorithm functions in an iterative manner,which makes it easy to compute.So the application of the CORDIC algorithm has become popular in many arithmetical operations,such as multiplication,division, square root and some trigonometric functions.To ensure the accuracy of the CORDIC algorithm,large num-bers of iterations is required,which leads to large resource consumption in its FPGA implemention.To re-duce its hardware resource consumption,a new structure for CORDIC algorithm based on folding transfor-mation is pared with traditional pipelined CORDIC algorithm,the folded structure costs much less hardwareresources.This paper introduces the structure of the folded CORDIC algorithm in details and shows its simulation results.【总页数】4页(P446-449)【作者】黄宇声;李朝海【作者单位】电子科技大学电子工程学院,四川成都 611731;电子科技大学电子工程学院,四川成都 611731【正文语种】中文【中图分类】TN957【相关文献】1.基于System Generator/CORDIC算法实现高精度鉴频 [J], 蔡雪颖;秦永左;刘立2.基于CORDIC的高速Sobel算法实现 [J], 黄虎;杨丁;雷宇辉;谢佳讯;陈诗瑶;邹瑜3.基于FPGA的CORDIC算法实现 [J], 蔡权利;高博;龚敏4.一种基于System Generator的CORDIC算法实现 [J], 胡天翔; 陈科; 赵志强5.基于CORDIC算法实现数字下变频 [J], 许彦辉;年夫顺;许建华;张超因版权原因,仅展示原文概要,查看原文内容请购买。

关于折叠式运放输入级电流和折叠级电流的分配

首先,我真是个大懒人!!不行,从现在开始要好好写博客了,以后争取每周都有新的东西发布。

其实关于模拟电路的设计,自己在eetop论坛上和大家也讨论了一些东西,只不过一直没有整理出来(自己真是太懒了),从这篇博客开始,分别会总结些关于运放设计的一些东西,由于笔者接触模拟集成电路没多久,经验还不是很多,希望大家能够批判性接收我博客里的知识。

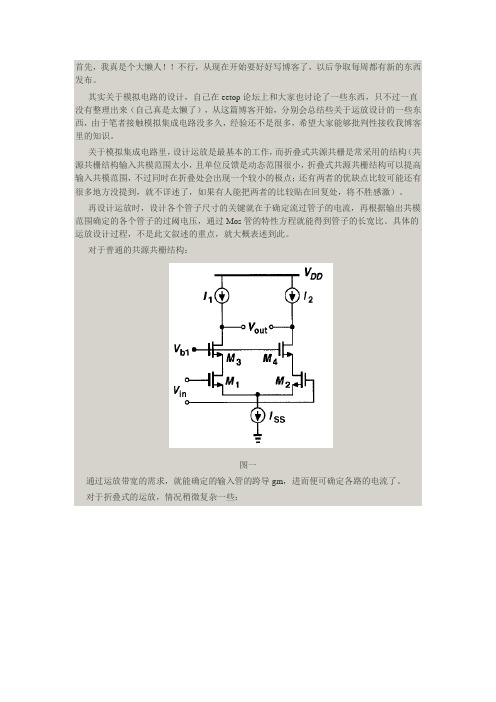

关于模拟集成电路里,设计运放是最基本的工作,而折叠式共源共栅是常采用的结构(共源共栅结构输入共模范围太小,且单位反馈是动态范围很小,折叠式共源共栅结构可以提高输入共模范围,不过同时在折叠处会出现一个较小的极点;还有两者的优缺点比较可能还有很多地方没提到,就不详述了,如果有人能把两者的比较贴在回复处,将不胜感激)。

再设计运放时,设计各个管子尺寸的关键就在于确定流过管子的电流,再根据输出共模范围确定的各个管子的过阈电压,通过Mos管的特性方程就能得到管子的长宽比。

具体的运放设计过程,不是此文叙述的重点,就大概表述到此。

对于普通的共源共栅结构:图一通过运放带宽的需求,就能确定的输入管的跨导gm,进而便可确定各路的电流了。

对于折叠式的运放,情况稍微复杂一些:图二为了,便于讲解,我们先只看一路(其实两路是完全对称的),由上图可知I5=I1+I3;那么I1和I3该如何分配呢?首先I1很好确定,由运放的带宽BW就能确定(同普通共源共栅结构),那么I3该取大于I1还是小于I1呢?这个就得具体情况具体分析,由你的的设计需求而定了:一,当在高速应用中,需要大的摆率SR及高的带宽BW,那么此时I3应该取得较大,对于摆率SR自然不用说,电流越大充电速度越快;那么带宽BW又是受什么限制呢?上文提到过折叠式共源共栅结构有个很大的缺点,就是在折叠处(图二的X处,暂时只分析一路,两路其实完全对称,再次强调)引入了一个较小的极点,也就是这个运放的次主极点p2,为了保证运放稳定,那么次主极点离主极点越远越好(只是出于稳定性的考虑),那么就要求p2越大越好,那么p2到底有什么决定呢?通过推导传递公式我们可知:p2=gm3/Cx,gm3是M3管的跨导,Cx是X点处的电容;Cx确定好尺寸后一般就确定了,但是在相同的尺寸下,流过M3的电流越大则M3的跨导越大,也即p2也就越大,因此主极点也就可以越大。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

动手练练! 动手练练!——双2次节滤波器

1、规定 折叠集以及节点序数

2、计算 折叠方程

仔细看看 如何计算

最终电路: 最终电路:验证一下

最终电路: 最终电路:验证一下

折叠会怎样? 对最原始的DFG折叠会怎样?

先去掉(左下角) 先去掉(左下角)割集重定时

再去掉流水线重定时

结论: 结论:重定时可以消除折叠违例 但不是100%

基本术语(修改的) 基本术语(修改的)

折叠序数 i、j: 、 某个节点在大周期中被执行的时刻; 某个节点在大周期中被执行的时刻; 折叠因子 N: 折叠集元素个数,表征折叠的强度。 折叠集元素个数,表征折叠的强度。

总括(修改的) 折叠变换——之 总括(修改的)

折叠方程(修改的) 折叠变换——之 折叠方程(修改的)

第六章 折叠

——也就是展开的反操作

折叠是“展开”的反操作

看看示例:什么叫分时复用? 看看示例:什么叫分时复用?

思考题: 思考题: 你能直观画出一个折叠后的结构吗? 你能直观画出一个折叠后的结构吗?

更复杂的示例: 更复杂的示例:折叠前后的区别

折叠——分时复用的结构

折叠示例(课本,详细) 折叠示例(课本,详细)

结合重定时的“折叠”

寄存器“最小化” 技术

课本表述的 修正

一个样值(也称变量)从产生的周期起 一个样值(也称变量)从产生的周期起 周期 到被应用的周期(包括被应用的周期) 周期 到被应用的周期(包括被应用的周期) 是激活的。变量被应用之后(之后的 是激活的。变量被应用之后( 周期),就消亡了。 ),就消亡了 周期),就消亡了。 变量在它激活的每个周期内(不包括产 周期 变量在它激活的每个周期内 生周期)都要占据一“个”寄存器。 寄存器。 生周期)都要占据一“

“前向后向” 寄存器 分配技术

最终电路

最终电路

最终电路

动手试试! 动手试试!双2次节滤波器

1、折叠方程

2、用折叠方程构造寿命表来自3、寿命分析:求最小寄存器数目 寿命分析:

激活的周期为 跨越的周期个数为

Tinput+1,Tinput+2,…,Toutput Tdiff=Toutput-Tinput

寿命分析——线性寿命图

寿命分析——循环寿命图

示例: 示例: 3x3矩阵转置

3x3矩阵转置:因果违例 矩阵转置:

3x3矩阵转置:因果违例 矩阵转置:

因果违例 的 修正

3x3矩阵转置 的寿命表

分析寿命图

分析寿命图

9个时钟周期为

一个大周期

最小寄存器数目 —— 4个

“前向后向” 寄存器 分配技术

控制单元(选路控制) 控制单元(选路控制)

折叠所带来的变化

基本术语

折叠序数 u、v: 、 某个节点在大周期中被执行的时刻; 某个节点在大周期中被执行的时刻; 折叠因子 N: 折叠集元素个数,表征折叠的强度。 折叠集元素个数,表征折叠的强度。

折叠变换——之 总括

折叠变换——之 折叠集

折叠变换——之 折叠方程

4、前向后向 寄存器分配

对节点1、7、8的 中间数据进行寄存器分配

选择R2带来的 恶果

新旧架构对比: 新旧架构对比:寄存器数目

附:系统的架构图

谢谢!

陈运必 08.10.31