使用Zynq_7000AllProgrammableSoC实现图像传感器色彩校正

ZYNQ_嵌入式软件开发

Example: Xapp1078 : Linux / Bare-metal AMP Xapp1079 : Bare-metal / Bare-metal AMP More info Refer to:

/Multi-OS+Support+(AMP+%26+Hypervisor)

FSBL工程根据XPS的XML文档选择需要的BSP驱动,并生 成ps7_init.c文件

相关文档: /support/documentation/user_g uides/ug821-zynq-7000-swdev.pdf

Page 8

Zynq-7000 Bootgen and BIF file format

Bootgen

A standalone tool for creating a bootable image suitable for the Zynq7000 AP SoC processor. The program assembles the boot image by prefixing a header block to a list of partitions. Each partition can be optionally encrypted and authenticated.

Page 3

Zynq-7000 开发工具 ---- XPS

XPS 可实现完整 的配置和定制操 作

管理 Zynq-7000 AP SoC 外设 IO 引脚启动配置和 初始化

器件安全、回读引 导和比特流管理 措施 项目专用配置感 知 无需用户掌握具 体硬件知识 利用可展开的软 件图自动构建一 级引导载入程序

Page 13

Zynq-7000 Power Management

ug821-zynq-7000-swdev

Zynq-7000 All Programmable SoC Software Developers GuideUG821 (v10.0) March 10, 2015Revision HistoryThe following table shows the revision history for this document.Date Version Revision04/01/201510.0Added miscellaneous references throughout the document.Updated BIF File Attributes, page 59Added Bootgen Command Options, page 63.Updated Partition Attribute Bits, page 66.06/04/20149.0Updated Bootgen to remove the -i option in Bootgen Command Options, page 63.Throughout document, added cross-references and updated links in Appendix D,Additional Resources and Legal Notices.Added definitions for RSA and SHA-2.Removed reference to UG652.Changed AP to PS on page 23.04/02/20148.0Initial release for 2014.1.Table of ContentsChapter 1: Introduction to Programming with Zynq-7000 AP SoC Devices Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Architectural Decisions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Operating System (OS) Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Chapter 2: Software Application Development FlowsIntroduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Software Tools Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Bare-Metal Device Driver Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Bare-Metal Application Development . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Linux Application Development . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Additional Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Chapter 3: Boot and ConfigurationOverview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Boot Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Boot Stages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Boot Image Creation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 BootROM Header Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Chapter 4: LinuxIntroduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Git Server and Gitk Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Linux BSP Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 U-Boot. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55Appendix A: Using BootgenIntroduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 BIF File Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 Initialization Pairs and the INT File Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 Encryption Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61 Authentication Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62Bootgen Command Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Image Header Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 Image Header. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67Appendix B: LibXil SKey for Zynq-7000 AP SoC Devices (v2.0)Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 SDK Project File and Folders . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 User-Configurable PS eFUSE Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 User-Configurable PL eFUSE Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 MUX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 AES and User Key Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74 User- Configurable BBRAM Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 MIO Pins Used for PL JTAG Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 MUX Parameter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 AES Key and Related Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 Error Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 Status Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81 Creating an SVF File using XMD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 eFUSE Writing Procedure Running from DDR as an Application . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 eFUSE Driver Compilation Procedure for OCM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 LibXil SKey Library APIs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 BBRAM API Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87Appendix C: LibXil RSA for Zynq-7000 AP SoC Devices (v1.1)LibXil RSA Library Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 SDK Project Files and Folders . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 Macros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89 LibXil RSA APIs and Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89Appendix D: Additional Resources and Legal NoticesSolution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92 Xilinx Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92 Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93Chapter 1 Introduction to Programming withZynq-7000 AP SoC DevicesOverviewThis document summarizes the software-centric information required for designing with Xilinx® Zynq®-7000 All Programmable SoC devices. It assumes that you are:•Experienced with embedded software design•Familiar with ARM® development tools•Familiar with Xilinx FPGA devices, intellectual property (IP cores), development tools, and tool environments.IntroductionThe addition of extensibility of the SoC for both hardware and software programmability imposes new requirements on design flows for both hardware and software.Certain hardware features are unique to Xilinx, such as hardware co-simulation andco-debug functionality that make it possible to verify custom logic implemented onZynq-7000 AP SoC devices or in a logic simulation environment while applications execute on a Zynq-7000 AP SoC processor on a physical board or an emulator.For a step-by-step explanation on designing a Zynq-based embedded system, see thefollowing documents:•Vivado Design Suite Tutorial: Embedded Processor Hardware Design (UG940)[Ref 6].•Vivado Design Suite User Guide: Embedded Processor Hardware Design (UG898) [Ref 11] describes the process of embedded hardware design.•Vivado Design Suite Tutorial: Zynq-7000 All Programmable SoC Embedded Design (UG1165) [Ref 16].VIDEO: See Enabling Smarter Systems for quick-take videos on the Zynq-7000 AP SoC devices.Architectural DecisionsYou must make several architectural decisions before beginning embedded development on applications to run on the Zynq-7000 AP SoC.Because the Zynq-7000 AP SoC devices have dual-core ARM Cortex™-A9 processors, you must determine whether to use Asymmetric Multiprocessing (AMP) or Symmetric Multiprocessing (SMP).The same decision must be made for all embedded software projects: which operating system(s) to use (if any). This introduction defines both AMP and SMP, and provides an assessment of the trade-offs and concerns with each method. Multiprocessing ConsiderationsThe following subsections describe the two multiprocessing considerations. Asymmetric MultiprocessingAsymmetric multiprocessing (AMP) is a processing model in which each processor in a multiple-processor system executes a different operating system image while sharing the same physical memory. Each image can be of the same operating system, but more typically, each image is a different operating system, complementing the other OS with different characteristics:• A full-featured operating system, such as Linux, lets you connect to the outside world through networking and user interfaces.• A smaller, light-weight operating system can be more efficient with respect to memory and real-time operations.A typical example is running Linux as the primary operating system along with a smaller, light-weight operating system, such as FreeRTOS or a bare-metal system, which is described in Chapter 4, Linux, as the secondary operating system.The division of system devices (such as the UART, timer-counter, and Ethernet) between the processors is a critical element in system design. In general:•Most devices must be dedicated to their assigned processor.•The interrupt controller is designed to be shared with multiple processors.•One processor is designated as the interrupt controller master because it initializes the interrupt controller.Communication between processors is a key element that allows both operating systems to be effective. It can be achieved in many different ways, including inter-processor interrupts, shared memory, and message passing.Symmetric MultiprocessingSymmetric multiprocessing (SMP) is a processing model in which each processor in a multiple-processor system executes a single operating system image. The scheduler of the operating system is responsible for scheduling processes on each processor.This is an efficient processing model when the selected single operating system meets the system requirements. The operating system uses the processing power of multiple processors automatically and is consequently transparent to the end user. Programmers can:•Specify a specific processor to execute a process•Handle interrupts with any available processor•Designate one processor as the master for system initialization and booting other processorsOperating System (OS) ConsiderationsBare-Metal SystemBare-metal refers to a software system without an operating system. This software system typically does not need many features (such as networking) that are provided by an operating system. An operating system consumes some small amount of processor throughput and tends to be less deterministic than simple software systems. Some system designs might not allow the overhead and lack of determinism of an operating system. As processing speed has continued to increase for embedded processing, the overhead of an operating system has become mostly negligible in many system designs. Some designers choose not to use an operating system due to system complexity.Operating System: LinuxLinux is an open-source operating system used in many embedded designs. It is available from many vendors as a distribution, or it can be built from the open-source repositories. Linux is not inherently a real-time operating system, but it has taken on more real-time characteristics.It is a full-featured operating system that takes advantage of the Memory Management Unit (MMU) in the processor, and is consequently regarded as a protected operating system. Linux also provides SMP capabilities to take advantage of multiple processors.Real-Time Operating SystemSome system designers use a Real-Time Operating System (RTOS) from Xilinx third-party partners.An RTOS offers the deterministic and predictable responsiveness required by timing sensitive applications and systems. For information on the latest third party tools, contact your nearest Xilinx office.Zynq-7000 Operating Systems From PartnersYou can choose you own favorite embedded solutions based on past experience, new standards, unique requirements, and legacy designs, as well as corporate agreements. For a detailed list of operating systems supported on Zynq-7000 devices from Xilinx partners, see the Zynq-7000 Ecosystem page.Chapter 2 Software Application Development FlowsIntroductionThe Zynq®-7000 All Programmable (AP) SoC software application development flows let you create software applications using a unified set of Xilinx® tools, and leverage a broad range of tools offered by third-party vendors for the ARM® Cortex™-A9 processors.This chapter focuses on Xilinx tools and flows; however, the concepts are generallyapplicable to third party tools, and the Zynq-7000 AP SoC device solutions incorporatefamiliar components such as an Eclipse-based integrated development environment (IDE) and the GNU compiler toolchain.This chapter also provides an overview of bare-metal and Linux software applicationdevelopment flows using Xilinx tools, which mirror support available for other Xilinxembedded processors, with differences as noted. This chapter also references boot, device configuration, and OS usage within the context of application development flows. Those topics are covered in-depth in other chapters and references to other material.Chapter 2: Software Application Development FlowsFigure 2-1 shows a block diagram of the Zynq-7000 AP SoC processor.Software Tools OverviewThe coupling of ARM-based Processing System (PS) and Programmable Logic (PL) createsunique opportunities to add custom peripherals and co-processors. Custom logicimplemented in the PL can be used to accelerate time-critical software functions, reduce application latency, reduce system power, or provide solution-specific hardware features.The addition of hardware programmability to the hardware and software interface imposes new requirements on design flows. Certain hardware features are unique to Xilinx, such as hardware co-simulation and co-debug functionality that make it possible to verify custom logic implemented on Zynq-7000 AP SoC devices or in a logic simulation environment while applications execute on a Zynq-7000 AP SoC processor on a physical board or an emulator.Figure 2-1: Zynq-7000 AP SoC Processing System High-Level DiagramXilinx provides design tools for developing and debugging software applications for Zynq-7000 AP SoC devices, that include:•Software IDE•GNU-based compiler toolchain•JTAG debugger•Associated utilitiesThese tools let you develop both:•Bare-metal applications that do not require an OS•Applications for the open source Linux OSCustom logic and user software can run various combinations of physical hardware or simulation, with the ability to monitor hardware events. For example:•Custom logic running in hardware or in a simulation tool•User software running on the target or in a software emulator•PL and processor cross-triggering on eventsSoftware solutions are also available from third-party sources that support Cortex-A9 processors, including, but not limited, to:•Software IDEs•Compiler toolchains•Debug and trace tools•Embedded OS and software libraries•Simulators•Models and virtual prototyping toolsThird party tool solutions vary in the level of integration and direct support for Zynq-7000 AP SoC devices. Xilinx does not provide tools that target Kernel development and debug, but those tools can be obtained from third party vendors.The following subsections provide a summary of the available Xilinx development tools. Tools are available on 32- and 64-bit Windows and x86 Linux host computing platforms.Hardware Configuration ToolXilinx provides the Vivado IP integrator which lets you use a block diagram to configure IP that is related to the PL and the Zynq-7000 processor.The Vivado Design Suite IP integrator provides a block diagram for the Zynq-7000 AP SoC wherein you can set Programmable Logic (PL) information in an XML file, INIT files(.h,.c, and .tcl), which are then used by software design tools to create and configure Board Support Package (BSP) libraries, infer compiler options, define JTAG settings, and automate other operations that require information about the hardware.For more information, see the following documents:•Vivado Design User Guide: Embedded Processor Hardware Design (UG898)[Ref 5]•Vivado Design Suite Tutorial: Embedded Processor Hardware Design (UG940) [Ref 6]•Vivado Design Suite User Guide: Using the Vivado IDE (UG893) [Ref 7]•Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator (UG994) [Ref 8]Software Development KitThe Xilinx Software Development Kit (SDK) provides a complete environment for creating software applications targeted for Xilinx embedded processors. It includes a GNU-based compiler toolchain (GCC compiler, GDB debugger, utilities, and libraries), JTAG debugger, flash programmer, drivers for Xilinx IPs and bare-metal board support packages, middleware libraries for application-specific functions, and an IDE for C/C++ bare-metal and Linux application development and debugging. Based upon the open source Eclipse platform, SDK incorporates the C/C++ Development Toolkit (CDT). Features include:•C/C++ code editor and compilation environment•Project management•Application build configuration and automatic makefile generation•Error navigation•Integrated environment for debugging and profiling embedded targets •Additional functionality available using third-party plug-ins, including source code version controlSDK AvailabilitySDK is available as a download with the Vivado Design Suite, and as a standalone application. SDK also includes an application template for creating a First Stage Bootloader (FSBL), as well as a graphical interface for building a boot image.SDK contains a complete help system that describes concepts, tasks, and reference information. See the Xilinx Software Development Kit Help (UG782) [Ref 14], for more information.You can launch SDK from Vivado when you export a hardware definition, as shown in Figure 2-2.System Performance AnalysisThe Xilinx Software Debugger (XSDB) uses a System Performance Monitor (SPM) for debugging.See the following links for more information regarding SPM [Ref 15]: •“Chapter 3” in the Xilinx Software Development Kit (SDK): System Performance (UG1145)•“Chapter 5” in the Xilinx Software Development Kit (SDK): System Performance (UG1145)Also, see System Performance Analysis of an All Programmable SoC (XAPP1219) [Ref 17].Sourcery CodeBench Lite Edition for Xilinx Cortex-A9 Compiler ToolchainSDK includes the Sourcery CodeBench Lite Edition for Xilinx Cortex-A9 compiler toolchain for bare-metal Embedded Application Binary Interface (EABI) and Linux application development.Figure 2-2: Export Hardware for SDK Dialog BoxThe Xilinx Sourcery CodeBench Lite toolchain in SDK contains the same GNU tools, libraries and documentation as the standard Sourcery CodeBench Lite Edition EABI and Linux compiler toolchains, but adds the following enhancements:•Default toolchain settings for the Xilinx Cortex-A9 processors•Bare-metal (EABI) start up support and default linker scripts for the Xilinx Cortex-A9 processors•Vector Floating Point (VFP) and NEON™ optimized librariesAnalysis ToolsVivado Lab ToolThe Vivado IDE has integrated debugging capability. See Vivado Design Suite User Guide: Programming and Debugging (UG908) [Ref 11] for more information.System Generator for DSPThe System Generator™ for DSP tool can be used to develop DSP and data flow-centric, hardware-based coprocessors, working within the MATLAB®/Simulink® environment. System Generator supports rapid simulation of the DSP hardware, reducing overall development time, and automates the generation of co-processors that can be connected to the PS. The SDK co-debug feature lets you run and debug programs running on the processor in SDK, while retaining visibility and control over the hardware under development in System Generator.Bare-Metal Device Driver ArchitectureThe bare-metal device drivers are designed with a layered architecture as shown in Figure 2-3, page 15. The layered architecture accommodates the many use cases of device drivers while at the same time providing portability across operating systems, toolsets, and processors.The layered architecture provides seamless integration with:• A Layer 2 (RTOS Adapter) an abstract device driver interface that is full-featured and portable across operating systems•Processors Layer 1 (Device Driver)• A direct hardware interface for simple use cases or those wishing to develop a custom device driverThe following subsections describe the layers.Figure 2-3: Bare-Metal Drivers ArchitectureLayer 2 (RTOS Adapter)Layer 2 is an adapter between an RTOS and a device driver. It converts a Layer 1 device driver to an interface that matches the requirements of the driver model for an RTOS. Unique adapters might be necessary for each RTOS.Adapters typically:•Communicate directly to the RTOS as well as the Layer 1 interface of the device driver •Reference functions and identifiers specific to the RTOS. This layer is therefore not portable across operating systems•Can use memory management•Can use RTOS services such as threading and inter-task communication•Can be simple or complex depending upon the RTOS interface and requirements for the device driverLayer 1 (Device Driver)Layer 1 is an abstract device driver interface that shields you from potential changes to the underlying hardware. It is implemented with macros and functions and designed to allow you to use all features of a device. The device driver is independent of operating systems and processors, making it highly portable.This interface typically has:•Consistent API that gives you an “out-of-the-box” solution. The abstract API helps isolate the your project from hardware changes.•Lack of RTOS or processor dependencies makes the device driver highly portable •Run-time error checking such as assertion of input arguments that provides the ability to compile away asserts•Device feature support•Support for device configuration parameters to handle FPGA-based parameterization of hardware devices•Support for multiple instances of a device while managing unique characteristics on a per instance basis•Polled and interrupt-driven I/O•Non-blocking function calls to aid complex applications• A potentially large memory footprint•Buffer interfaces for data transfers as opposed to byte interfaces. This makes the API easier to use for complex applications.•No direct communication to Layer 2 adapters or application software, by using asynchronous callbacks for upward communicationDirect Hardware InterfaceThe interface that is contained within the Layer 1 device driver is a direct hardware interface. It is typically implemented as macros and manifest constants, and is designed so you can create a small applications or create a custom device driver. This interface typically has:•Constants that define the device register offsets and bit fields•Simple macros that provide access to the hardware registers• A small memory footprint•Little to no error checking•Minimal abstraction so the API typically matches the device registers. The API is therefore less isolated from hardware device changes.•No support of device configuration parameters•Support of multiple instances of a device with base address input to the API•No, or minimal state•Polled I/O only•Blocking functions for simple use cases•Byte interfaces typically providedBare-Metal Application DevelopmentXilinx software design tools facilitate the development of embedded software applications for many runtime environments.Xilinx embedded design tools create a set of hardware platform data files that include:•An XML-based hardware description file describing processors, peripherals, memory maps, and additional system data• A bitstream file containing optional Programmable Logic (PL) programming data• A block RAM Memory Map (BMM) file•PS configuration data used by the Zynq-7000 AP SoC First Stage Bootloader (FSBL). The bare-metal Board Support Package (BSP) is a collection of libraries and drivers that form the lowest layer of your application.The runtime environment is a simple, semi-hosted and single-threaded environment that provides basic features, including boot code, cache functions, exception handling, basic file I/O, C library support for memory allocation and other calls, processor hardware access macros, timer functions, and other functions required to support bare-metal applications.Using the hardware platform data and bare-metal BSP , you can develop, debug, and deploy bare-metal applications using SDK.Figure 2-4 is an overview flowchart for bare-metal application development.To develop bare-metal applications using SDK, typical steps include:1.Importing Hardware Platform Information 2.Creating Bare-Metal BSP 3.Creating Bare-Metal Application 4.Building the Application Project5.Programming the Device and Running the Application6.Debugging the Application7.Adding Custom IP Driver Support8.Deploying the ApplicationThe following subsections summarize these SDK development flow steps. See the SDK online help, for more details and examples of SDK tool usage.Figure 2-4: Bare-Metal Application Development Overview。

基于Zynq—7000的多种以太网实现方案

基于Zynq—7000的多种以太网实现方案作者:刘佳钱瑞杰李洋来源:《中国科技纵横》2017年第09期摘要:Zynq是Xilinx公司推出的第一个可扩展处理平台,将双核ARMCortex A9处理器与可编程逻辑架构结合,充分体现软硬件协同设计。

以太网是当今通信领域广泛应用的接口,在Zynq中提供了两路千兆以太网控制器,结合MIO、EMIO、AXI、PL等资源,可提供多种以太网实现方案。

关键词:Zynq可扩展处理平台;软硬件协同设计;以太网中图分类号:TP391.41 文献标识码:A 文章编号:1671-2064(2017)09-0040-021 引言随着技术的发展,SOC受到了更多人的关注和推行,Xilinx公司的Zynq作为该领域的领跑者,已被运用到许多场合。

Zynq-7000 系列基于 Xilinx 的可扩展处理平台结构,在单芯片内集成了具有丰富特点的双核 ARM Cortex A9处理器系统(Processing System,PS)和 Xilinx可编程逻辑(Programmable Logic,PL)。

其中,Cortex A9 双核处理器是整个架构的核心,外部存储器接口、及丰富的外设资源都挂载在 ARM上,PL可看做完全可编程的外设。

本文基于以太网接口的大量使用,充分考虑到不同应用场景接口形态的差异,如光口以太网、电口以太网。

结合Zynq所具备的丰富设计资源,提出了基于Zynq-7000的多种以太网实现方案。

2 方案原理Zynq-7000内部有很多常见的I/O外设和存储器接口,是PS的重要组成部分。

这些外设包括GPIO、USB控制器、SPI控制器、UART控制器、千兆以太网控制器等。

这些外设除具备通用功能外,还针对Zynq-7000做了改动。

使其能很好的支持PS+PL的架构,灵活使用PL。

Zynq-7000中还提出了两个新概念,MIO(Multiuse I/O)和EMIO(Extendable Multiplexed I/O)。

XilinxZYNQ-7000平台简介

XilinxZYNQ-7000平台简介平台介绍Zynq7000是赛灵思公司(Xilinx)推出的⾏业第⼀个可扩展处理平台Zynq系列。

旨在为视频监视、汽车驾驶员辅助以及⼯⼚⾃动化等⾼端嵌⼊式应⽤提供所需的处理与计算性能⽔平。

在2010年4⽉硅⾕举⾏的嵌⼊式系统⼤会上,赛灵思发布了可扩展处理平台的架构详情,这款基于⽆处不在的ARM处理器的SoC可满⾜复杂嵌⼊式系统的⾼性能、低功耗和多核处理能⼒要求。

赛灵思可扩展处理平台芯⽚硬件的核⼼本质就是将通⽤基础双ARMCortex-A9MPCore 处理器系统作为“主系统”,结合低功耗28nm⼯艺技术,以实现⾼度的灵活性、强⼤的配置功能和⾼性能。

由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的⼀致性,同时也⽅便⽇后本系列新产品的命名。

Zynq-7000系列的可编程逻辑完全基于赛灵思7系列FPGA架构来设计,可确保28nm系列器件的IP核、⼯具和性能100%兼容。

最⼩型的Zynq-7000、Zynq-7010和Zynq-7020均基于专门针对低成本和低功耗优化的Artix-7系列;较⼤型的Zynq-7030和Zynq-7040器件基于包括4⾄12个10.3Gbps收发器通道,可⽀持⾼速⽚外连接的中端Kintex-7系列。

所有四款产品均采⽤基于2个12位1MspsADC(模数转换器)模块的新型模拟混合信号模块。

Zynq®-7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上⾼度集成 CPU、DSP、ASSP 以及混合信号功能。

Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗性价⽐最⾼的全⾯可扩展的 SoC 平台,可充分满⾜您的独特应⽤需求。

ZYNQ7000开发平台用户手册说明书

文档版本控制目录文档版本控制 (2)一、开发板简介 (6)二、AC7Z020核心板 (8)(一)简介 (8)(二)ZYNQ芯片 (9)(三)DDR3 DRAM (11)(四)QSPI Flash (14)(五)时钟配置 (16)(六)电源 (17)(七)结构图 (18)(八)连接器管脚定义 (19)三、扩展板 (23)(一)简介 (23)(二)CAN通信接口 (24)(三)485通信接口 (24)(四)千兆以太网接口 (25)(五)USB2.0 Host接口 (27)(六)USB转串口 (28)(七)AD输入接口 (29)(八)HDMI输出接口 (30)(九)MIPI摄像头接口(仅AX7Z020使用) (32)(十)SD卡槽 (33)(十一)EEPROM (34)(十二)实时时钟 (34)(十三)温度传感器 (35)(十四)JTAG接口 (36)(十五)用户LED灯 (36)(十六)用户按键 (37)(十七)扩展口 (38)(十八)供电电源 (40)(十九)底板结构图 (41)芯驿电子科技(上海)有限公司 基于XILINX ZYNQ7000开发平台的开发板(型号: AX7Z020B )2022款正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ZYNQ7000 FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

核心板使用XILINX 的Zynq7000 SOC 芯片的解决方案,它采用ARM+FPGA SOC 技术将双核ARM Cortex-A9 和FPGA 可编程逻辑集成在一颗芯片上。

另外核心板上含有2片共512MB 高速DDR3 SDRAM 芯片和1片256Mb 的QSPI FLASH 芯片。

在底板设计上我们为用户扩展了丰富的外围接口,比如2路CAN 通信接口,2路485通信接口,2路XADC 输入接口, 1路千兆以太网接口,1路USB2.0 HOST 接口,1路HDMI输出接口,Uart 通信接口,SD 卡座,40针扩展接口等等。

无线应用AMP与SMP的区别以及赛灵思Zynq 7000的应用

无线应用AMP与SMP的区别以及赛灵思Zynq 7000

的应用

随着无线数据吞吐量的爆炸式增长,数字信号处理技术和无线电设备在改进方面面临着巨大压力。

目前的重点放在4G LTE。

4G网络正在世界各地大规模部署。

而且现在我们看到5G网络的早期研发工作也已经展开,其目标

是在4G网络的基础上将数据容量再提升上千倍。

这种新兴的技术发展给系

统厂商提出了不断发展变化的新要求他们必须提升系统集成度和系统性能,

降低系统材料清单(BOM)成本,提高设计灵活性,并加速产品上市进程等。

传统ASIC器件支持的硬件解决方案虽然可以实现功耗和成本目标,但偶生工程成本(NRE)极高、灵活性差且产品上市进程非常缓慢。

为了满足这

些要求并应对这些挑战,赛灵思向行业推出了All Programmable SoC架构,并将其成功实现在Zynq-7000产品系列中。

Zynq-7000器件采用赛灵思SoC架构并通过硬件、软件和I/O可重编程功能可实现更大的系统级差异化、更高的集成度和灵活性(图1)。

Zynq-7000

器件自2011年12月推出以来,已广泛应用于通信、数据中心、汽车、工业、航空航天与国防等众多市场领域。

对通信市场(尤其是无线应用领域)而言,Zynq-7000带来了独特的优势:其集成式可编程逻辑(PL)专门针对数字信

号处理进行了精心优化;其ARM Cortex A9处理子系统(PS)能够高效实现。

基于Zynq的视频实时拼接系统

∗基金项目:四川省教育厅科学研究重点项目(18ZA0088);四川省大学生创新创业训练计划项目(S201910621118)0引言随着生产生活和科学技术的进步,数码摄像设备得到了广泛地普及与应用。

但是由于数码摄像设备自身物理条件的限制,普通数码摄像设备获取视频的视野范围较小,超广角镜头或者鱼眼镜头又会对图像产生畸变[1],不能满足实际的应用需求。

利用单一摄像头捕捉多张视频画面合成宽视野图像的办法不仅费时费力,而且获得的全景图像的质量一般不佳。

视频拼接技术很好地解决了这一问题。

所谓视频拼接就是将几个存在内容相关性的窄视野视频的每一帧图像进行拼接融合处理,得到一幅宽视野的甚至是全景的视频图像。

视频拼接本质上就是图像拼接,但由于其对于实时性的要求很高,使得在该领域的技术实践更需要关注平台的处理性能和算法的复杂性。

目前市面上普遍采用基于ARM 、DSP 、FPGA 的嵌入式平台方案,以及多通道图像采集拼接形成全景的通用计算机平台方案来实现视频拼接。

这些实现方案存在一定的缺陷,基于ARM 的实现方案处理能力较弱,无法进行复杂视频算法;基于DSP 的实现方案处理速度比FPGA慢[2];基于FPGA 的实现方案灵活性较差且成本较高;基于计算机平台的实现方案凭借性能优势获得好的效果,但设备体积庞大、功耗高且价格昂贵[3]。

针对以上问题,本文首先对特征点检测效率表现优异的ORB 算法进行改进,并利用Vivado HLS 工具将改进的视频拼接算法进行硬件加速并部署到Zynq 的PL 中,然后利用Zynq 的PS 搭建嵌入式Linux 系统,进行用户界面开发,实现任务调度,最后提出了一种基于Zynq 平台对多通道视频进行无缝拼接处理的解决方案。

基于Zynq 的视频实时拼接系统∗陈子为,陈龙,朱美吉,苏鲁阳(成都信息工程大学电子工程学院,四川成都610225)摘要:针对目前视频拼接系统实时性不高、拼接效果不理想、成本高等问题,对传统的ORB 算法进行了改进,并采用软硬件协同设计的方法,在Zynq 平台上实现了一款视频实时拼接系统。

AUMO ALINX ZYNQ-7000产品手册说明书

ZYNQ-7000产品手册ZYNQ-7000 Product Guide2023关于我们官方合作伙伴业务范围芯驿电子科技(上海)有限公司,成立于2012年,总部位于上海松江临港科技城,是一家车载智能产品和FPGA 技术方案公司,拥有“AUMO”和“ALINX”两大品牌,其中AUMO 品牌专注车载智能产品,ALINX 品牌专注于FPGA 产品和方案定制。

经历十年发展,公司产品已经远销海外30多个国家。

2018年,公司通过高新技术企业认证,并通过ISO9001质量体系认证;2019年,荣获上海市松江区九亭镇“科技创新奖”;2020年,荣获上海市“专精特新企业“称号;2021年,申请通过上海市科技型中小企业技术创新资金项目,通过了国家级科技型中小企业认定,并通过了高新技术企业认证复审;2022年获得上海市张江国家自主创新示范区专项发展资金并通过“上海市创新型中小企业”认证。

ALINX 是全球的FPGA 芯片龙头企业XILINX 官方合作伙伴,国内FPGA 芯片龙头企业紫光同创官方合作伙伴,同时作为百度AI 合作伙伴,为百度定制了国产AI飞桨系统的Edgeboard 系列边缘设备。

通过多年的研发投入,已经推出100多款FPGA SoM 模组和配套板卡,积累了1000多家企业批量用户,上万个独立开发者,市场占有率遥遥领先。

通过产品+定制化服务的经营方式,ALINX 将继续加大对产品研发和技术研究的投入,不断与垂直行业客户合作,聚焦高端设备领域,协助客户解决行业的技术难题。

主要聚焦于FPGA + AI 解决方案,FPGA 国产化,FPGA 开发套件, ALINX 自有品牌产品。

公司提供的设计解决方案涉及人工智能、自动驾驶、轨道交通、半导体、5G 通信、医疗设备、工业互联、仪器仪表、数据中心、机器视觉、视频图像处理等行业。

紫光同创国内唯一的FPGA 板卡官方合作伙伴,XILINX 官方重要合作伙伴,百度AI合作伙伴。

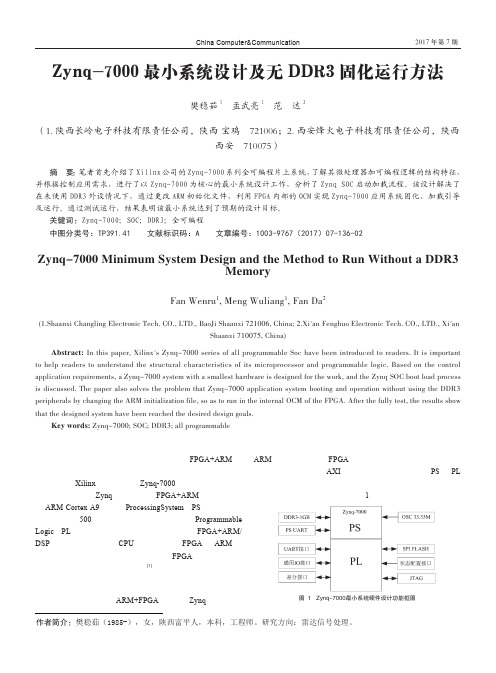

Zynq-7000最小系统设计及无DDR3固化运行方法

图1 Zynq-7000最小系统硬件设计功能框图樊稳茹(1985-),女,陕西富平人,本科,工程师。

研究方向:雷达信号处理。

2017年第7期信息与电脑China Computer&Communication软件开发与应用该最小系统PS部分结合用户应用程序用于实现控制功能,PL部分包括UART接口、时序产生、地址译码、片上存储和外设控制等逻辑功能模块。

主要的功能芯片为X7Z045、MT41K256M16HA、MAX3160E、MAX3096、MAX3045、W25Q128、ADG3308等,为了降低硬件成本,在满足使用需求的条件下,该最小系统设计时取消了图1中虚线框中的DDR3存储器。

2 基本启动配置流程分析Zynq是一个可扩展处理平台,简单地说就是有个FPGA 做外设的A9双核处理器,所以它的启动流程与FPGA完全不同,而与ARM处理器类似。

Zynq支持JTAG、NAND、Parallel NOR、QSPI以及SD卡等启动方式。

Zynq有效利用了片上的CPU来帮助配置,在没有外部JTAG的情况下,处理器系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置,内部的启动存储区(BootROM)和芯片配置单元可实现Zynq从BootROM主动启动或者从JTAG被动启动[2]。

与其他XILINX 7系列的器件不同的是,Zynq并不支持从PL端直接进行启动配置,Zynq的启动配置是分多级进行的,配置过程最少需要两步,但通常是按如下三个阶段进行。

阶段0(Stage0):简称BootROM,控制着整个芯片的初始化过程。

该部分代码是不可修改的,处理器核在上电或者热启动时自动执行这部分代码,并对外部的NAND、NOR、SD等外设控制器进行初始化,同时还负责将阶段1的启动镜像(FSBL镜像)加载到OCM(Zynq片上一个256K的RAM,但在FSBL运行前只能使用其中的192K,所以FSBL要小于192K),然后运行FSBL,FSBL镜像来源由板上MIO[5:3]引脚选择的启动方式决定。

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用

如何使用Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCVg p应用2013年9月11日© Copyright 2013 XilinxOpenCV简介机(p)机开源计算机视觉(OpenCV) 被广泛用于开发计算机视觉应用–包含2500多个优化的视频函数的函数库–专门针对台式机处理器和GPU进行优化–用户成千上万–无需修改即可在Zynq器件的ARM处理器上运行但是–利用OpenCV实现的高清处理经常受外部存储器的限制–存储带宽会成为性能瓶颈–存储访问会限制功耗效率Zynq All-programmable SOC是实现嵌入式计算机视觉应用的极好方法–性能高、功耗低实时计算机视觉应用计算机视觉应用实时分析功能高级驾驶员安全辅助车道或行人检测安防监视敌我识别高速物体检测用于工厂自动化的机器视觉非侵入式医疗成像技术肿瘤检测实时视频分析处理基于帧的基于像素的Pixel based 4Kx2K 特征处理与决策图像处理与特征提取Image processing and FeatureextractionF11080p F2 F3720p480…..480p每像素数百次运算每特性数10000次运算800万次处理x每帧100次运算= 数百亿次运算每秒处理数1000个特征= 数百万次运算实时视频分析的异构实现基于帧的基于像素的图像处理与特征Pixel based 4Kx2K特征处理与判定提取Image processing and Featureextraction F11080pF2F3软件域(ARM)硬件域(FPGA)720p480…..480p每像素数百次运算每特性数10000次运算800万次处理x 每帧100次运算= 数百亿次运算每秒处理数1000个特征= 数百万次运算赛灵思实时图像分析的实现:Zynq All Programmable SoC Programmable SoCFrame based Feature processing and 基于像素的图像处理与特征Pixel based 4Kx2KFeature processing and decision making提取基于帧的特征处理与判定Image processing and FeatureextractionF11080pF2F3720p480…..480p每像素数百次运算每特性数10000次运算1000800万次处理x 每帧100次运算= 数百亿次运算每秒处理数个特征= 数百万次运算Vivado:提高OpenCV应用的效率高清视频算法(每秒约1帧)的C语言仿真–高清视频(每小时1 帧)的RTL仿真实时FPGA实现方案高达60fpsZynq 视频参考设计架构DDR3DDR3外部存储器处理系统DDR 存储控制器SD 卡双核Cortex-A9硬化的外设S_AXI_GP 32b 位S_AXI_HP 64 位AXI4S AXI 互联AXI4 Stream IP 核HDMIHDMI视频输入Xylon 显示控制器HLS 生成的流水线AXI VDMA使用64位高性能端口实现对外部存储器的视频访问使用32位通用端口实现控制寄存器访问使用AXI4-Stream 实现的视频流以IP 为中心的设计流程更快速的IP生成与集成基于C 语言的IP 创建用户首选的系统集成环境C 、C++ 或SystemCDSP 系统生成器(System Generator)C 函数库•浮点math.h •定点VHDL V il •视频VHDL 或Verilog 以及软件驱动Vivado IP 集成器IP 子系统赛灵思IP 第三方IP Vivado RTL 集成用户IP在FPGA 设计中使用OpenCV纯集成的O CVO CV 图像文件读取OpenCV 应用OpenCV 应用OpenCV 参考加速的OpenCV 应用图像文件读取(OpenCV)(OImage penCV)OpenCV2AXIvideo 实时视频输入实时视频输入O CV 函数链AXIvideo2Mat模块O CV 函数链AXIvideo2Mat模块OpenCV HLS 视频库函数链Mat2AXIvideo可综合的OpenCVHLS 视频库函数链Mat2AXIvideo可综合的图像文件写入(OpenCV)AXIvideo2OpenCV 图像文件写入实时视频输出实时视频输出(OpenCV)DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)12345SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线集成的OpenCV 应用DDR3处理系统DDR 存储控制器DDR3DDR3 外部存储器实时视频输入12345SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设p HDMIHDMIXylon显示AXI VDMAAXI 互联实时视频输出视频输入y 控制器HLS 生成的流水线OpenCV 参考/软件执行DDR3图像文件读取处理系统DDR 存储控制器DDR3DDR3外部存储器12345(OImage penCV)OpenCV2AXIvideo SD卡双核Cortex-A9AXIvideo2MatCortex A9硬化的外设HLS 视频库函数链Mat2AXIvideoHDMIHDMIXylon 显示AXI VDMAAXI 互联AXIvideo2OpenCV图像文件写入视频输入y 控制器HLS 生成的流水线(OpenCV)OpenCV 参考/系统测试DDR3图像文件读取处理系统DDR 存储控制器DDR3DDR3外部存储器(OImage penCV)OpenCV2AXIvideo 12SD卡双核Cortex-A9AXIvideo2MatCortex A9硬化的外设HLS 视频库函数链Mat2AXIvideoHDMIHDMIXylon 显示AXI VDMAAXI 互联AXIvideo2OpenCV图像文件写入视频输入y 控制器HLS 生成的流水线(OpenCV)加速的OpenCV 应用DDR3处理系统DDR 存储控制器DDR3DDR3 外部存储器实时视频输入12SD卡双核Cortex-A9AXIvideo2Mat视频库函数链Cortex A9硬化的外设HLS Mat2AXIvideoHDMIHDMI视频输入Xylon显示AXI VDMAAXI 互联实时视频输出y 控制器HLS 生成的流水线OpenCV设计流程OpenCV模块A1)在台式机上开发OpenCV应用2)无需修改即可在ARM内核上运行OpenCV应OpenCV模块B用3)使用I/O函数抽象FPGA部分O CV 4)用可综合代码代替OpenCV函数调用5)运行HLS以生成FPGA加速器OpenCV模块C6)用FPGA加速器调用代替可综合代码调用OpenCV模块DOpenCV 应用的软硬划分opencv2AXIvideo OpenCV 模块AAXIvideo2HLSOpenCV 模块BHLS 模块BO CV HLS 模块C同步OpenCV模块C HLS2AXIvideoOpenCV 模块DAXIvideo2opencv综合OpenCV设计中的权衡OpenCV图像处理是基于存储器帧缓存而构建的–访问局部性较差-> 小容量高速缓存性能不足–架构比较复杂(出于性能考虑)-> 功耗更高–似乎足以满足很多应用的要求•分辨率或帧速率低•在更大的图像中对需要的特征或区域进行处理基于视频流的架构能提供高性能和低功耗–链条化的图像处理函数能减少外部存储器访问针对视频优化的行缓存和窗缓存比处理器高速缓存更简单–针对视频优化的行缓存和窗口缓存比处理器高速缓存更简单–可使用HLS中的数据流优化来实现–需要将代码转换为可综合的代码HLS视频库OpenCV函数不能直接通过HLS进行综合O C S–动态内存分配–浮点–假设图像在外部存储器中修改HLS视频库用于替换很多基本的OpenCV函数–与OpenCV具有相似的接口和算法–主要针对在FPGA架构中实现的图像处理函数–包含专门面向FPGA的优化•定点运算而非浮点运算•片上的行缓存和窗口缓存–不必精确到比特位赛灵思HLS 视频库2013.2AXI4-Stream IO 函数视频数据建模Li b ff ClWi d ClOpenCV 接口函数cvMat2AXIvideo AXIvideo2cvMat cvMat2hlsMat hlsMat2cvMat I lI 2AXI id AXI id 2I lI I lI 2hl M t hl M t2I lI AXIvideo2MatMat2AXIvideoLinebuffer Class Window Class 视频函数Duplicate MaxS Remap IplImage2AXIvideo AXIvideo2IplImage IplImage2hlsMat hlsMat2IplImage CvMat2AXIvideo AXIvideo2CvMat CvMat2hlsMathlsMat2CvMat AbsDiff AddSEqualizeHist Mean Resize AddWeighted Erode Merge Scale And FASTX MinSet Avg Filter2DMinMaxLoc Sobel AvgSdv GaussianBlur MinS Split Cmp HarrisMul SubRS CmpSHoughLines2NotSubS CornerHarris IntegralPaintMask SumCvtColor InitUndistortRectifyMap Range Threshold DilateMaxReduceZero如需了解函数的详情,敬请阅读HLS 用户指南UG 902视频库函数#include “hls video h”包含在hls 命名空间内的C++代码。

MicroBlaze如何与ZynqSoC和平共存

MicroBlaze如何与ZynqSoC和平共存赛灵思Zynq-7000 All Programmable SoC已具有很强的板载处理能力。

但是Zynq应用处理单元(APU)中强大的双Cortex-A9处理器和相关外设的存在并不妨碍您在同一封装中添加一个或多个MicroBlaze处理器,只要能让应用受益就好。

为什么要给处理功能已经很强大的解决方案添加MicroBlaze呢?首先就是可靠性的问题。

单线程会大幅提高可靠性。

您可以针对计算密集型任务为每个Cortex-A9都布置一个线程,而且能根据需要为其它线程实例化任何数量的MicroBlaze处理器。

其次,您可将任何杂务交给MicroBlaze去完成,让处理功能强大的Cortex-A9去执行最需要它的工作,充分发挥其用武之地,从而节省数个关键的工作周期。

下面这个例子能反映以上两种情况。

设想一下,一个任务需要长期高强度计算,同时还要监控用户输入。

这里,MicroBlaze可管理用户输入(频率较低、计算强度不高),并写入APU 存储器空间,这样APU闲置时(也就是完成了处理任务时)就能看看接下来需要处理什么信息。

一旦您决定在基于Zynq的设计中添加一个MicroBlaze处理器,马上就会发现一些问题。

首要问题就是APU如何与MicroBlaze通信,哪些处理器系统(PS)资源可供MicroBlaze使用。

包括ZC702和Zedboard等在内的许多开发板将许多外设直接映射到与处理系统相连的引脚。

可编程逻辑(PL)中,这些引脚不能直接访问MicroBlaze。

处理系统还包含多种不同定时器和中断资源。

有什么办法能从MicroBlaze领域访问这些资源吗?PS与PL之间的接口处理器系统和可编程逻辑紧密结合,这意味着Cortex-A9、窥探控制单元(SCU)、PS外设、时钟管理及其它功能与可编程逻辑之间存在多个紧密的集成连接。

事实上,PS和PL之间共有6种不同类型的互联,您可将这些互联类型彼此结合使用。

Xilinx Zynq 7000-总结

用鼠标点击配置界面上方的Main、Device Initialization、STDIO Connection、

Profile Options、Debugger Options和Common标签,查看这些标签界面下的,配 置内容。

点击运行配置界面下方的“RUN”按钮,运行程序。

23

主要内容

AXI_GP

四个通用接口(两主两从),每个位宽为32,可访问PS的DDR3控制器、PS的片上 RAM资源和其他从设备

AXI_ACP

用于PL的一个加速一致性主端口。提供快速访问CPU,可选的与L1或L2缓存一致 性

7

Zynq7000平台简介

Zynq-7000系统的互联资源

8

Zynq7000平台简介

在SDK主界面左侧的Project Explorer窗口下,右键选中peripheral_tests_0条目,点击 鼠标右键出现浮动菜单,在浮动菜单内选择Run As->Run Configurations…

出现运行配置界面。在该配置界面下,选择Xilinx C/C++ELF选项,点击鼠标右键,出 现浮动菜单,选择New。生成新的运行配置界面。

12

Zc702基本系统的建立和运行

Zc702 基本系统的建立

选择board为ZC702,next 去掉默认添加的IP, BTNs_5Bits、LEDs_8Bits 和SWs_8Bits,next 向导流程完成后,可以选择Generate Bitstream,来 获得下载到PL的位流码文件

5

Zynq7000平台简介

Zynq-7000系统的逻辑资源:PL

PL资源

Artix7 : 7z010、7z020 Kintex7:7z030、7z045、7z100

Zynq-7000“FPGA+ARM”架构的数字图像处理系统设计

敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第7期43Z y n q7000 F P G A+A R M 架构的数字图像处理系统设计王咏星,张国兵,宋俊霞(北京轩宇空间科技有限公司,北京100190)摘要:针对目前数字图像高帧频㊁高分辨率㊁大数据量的特点,本系统选取有丰富逻辑资源㊁具有高速并行运算能力和可重构能力的Z y n q7000系列产品,其 F P G A+A R M 的体系架构提高了数字图像处理系统前端图像的采集速度㊁方便了中端图像处理以及后端的显示㊂本文介绍了基于Z y n q7000的C a m e r a l i n k图像输入与采集㊁C a m e r a l i n k图像传输与存储和C a m e r a L i n k图像显示的数字图像处理系统的设计,并且详细介绍了各部分功能涉及的关键技术㊂经验证,本系统实时性高㊁体积小㊁性能稳定,实现了大数据量的图像采集与传输,目前已应用在实际的项目中㊂关键词:Z y n q7000;F P G A;A R M;图像处理系统中图分类号:T P274文献标识码:AD e s i g n o f D i g i t a l I m a g e P r o c e s s i n g S y s t e m P l a t f o r m B a s e d o n Z y n q7000F PG A+A R M A r c h i t e c t u r eW a n g Y o n g x i n g,Z h a n g G u o b i n g,S o n g J u n x i a(B e j i n g S u n W i s e S p a c e T e c h n o l o g y,B e j i n g100190,C h i n a)A b s t r a c t:I n v i e w o f t h e c h a r a c t e r i s t i c s o f h i g h f r a m e f r e q u e n c y,h i g h r e s o l u t i o n a n d l a r g e a m o u n t o f d a t a o f d i g i t a l i m a g e,t h e s y s t e m s e-l e c t s Z y n q7000s e r i e s p r o d u c t s w i t h r i c h l o g i c a l r e s o u r c e s,h i g h s p e e d p a r a l l e l c o m p u t i n g a b i l i t y a n d r e c o n f i g u r a b l e a b i l i t y.I t s"F P G A +A RM"a r c h i t e c t u r e i m p r o v e s t h e a c q u i s i t i o n s p e e d a t t h e f r o n t-e n d o f d i g i t a l i m a g e p r o c e s s i n g s y s t e m,f a c i l i t a t e s t h e i m a g e p r o c e s s i n g a t t h e m i d d l e-e n d a n d t h e d i s p l a y a t t h e b a c k-e n d.T h e d e s i g n o f d i g i t a l i m a g e p r o c e s s i n g s y s t e m b a s e d o n Z y n q7000f o r C a m e r a L i n k i m a g e i n p u t a n d a c q u i s i t i o n,C a m e r a L i n k i m a g e t r a n s m i s s i o n a n d s t o r a g e,a n d C a m e r a L i n k i m a g e d i s p l a y,a n d t h e k e y t e c h n o l o g i e s i n-v o l v e d i n e a c h f u n c t i o n a r e i n t r o d u c e d i n d e t a i l.I t h a s b e e n p r o v e d t h a t t h e s y s t e m h a s h i g h r e a l-t i m e p e r f o r m a n c e,s m a l l s i z e a n d s t a b l e p e r f o r m a n c e,a n d h a s r e a l i z e d t h e i m a g e a c q u i s i t i o n a n d t r a n s m i s s i o n o f l a r g e a m o u n t o f d a t a.I t h a s b e e n a p p l i e d i n p r a c t i c a l p r o j e c t a t p r e s e n t. K e y w o r d s:Z y n q7000;F P G A;A RM;i m a g e p r o c e s s i n g s y s t e m0引言近年来数字图像技术在工业生产㊁军事㊁生物医学㊁航空航天和通信等方面受到了极大的重视㊂随着集成电路工艺的高速发展,F P G A可编程逻辑器件在规模日益增大的同时成本也在逐渐下降,其中X i l i n x Z y n q7000系列产品就是一种全可编程片上系统(A l l P r o g r a mm a b l e S y s-t e m o n C h i p),它将A R M C o r t e x A9处理器和F P G A可编程逻辑资源进行集成,具有硬件和软件均可重新编程的特点,软硬件协同工作提高了设计的灵活性㊂数字图像处理的数据量大,对实时性要求严格,因此实时图像处理系统必须具有强大的运算能力,本系统就是基于Z y n q7000系列产品设计,并利用A X I(A d v a n c e d e X t e n s i b l e I n t e r f a c e)总线实现了A R M处理器与F P G A 的数据交换,即通过P S和P L软硬件协同工作㊂1系统结构及工作原理图像源产生的L V D S串行高速图像信号经过C a m e r-a L i n k芯片D S90C R286M T D后,按照C a m e r a L i n k接口协议转换成并行T T L信号,并将T T L信号输入至F P G A 接口㊂F P G A使用Z y n q7000系列的x c7z100f f g9002器件,在P L端进行采集与控制,在此过程中P L端将通过A X I总线将图像数据存储到D D R中,P S端在接收到图像中断信号时开始读取D D R中的图像数据,判断图像帧号是否连续,是否存在丢图现象,并将结果通过串口发送至上位机,同时P S将C a m e r a L i n k图像通过千兆以太网发送至上位机,上位机将图像显示出来㊂因此该数字图像处理系统主要分为三大部分,分别为基于Z y n q7000的44M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第7期w w w .m e s n e t .c o m .c nC a m e r a L i n k 图像输入与采集模块㊁C a m e r a L i n k 图像传输与存储模块㊁C a m e r a L i n k 图像显示㊂数字图像处理系统如图1所示㊂图1 数字图像处理系统图2 系统关键部分实现本系统接收帧频为50H z ㊁图像大小为1280ˑ960的C a m e r a L i n k 图像,针对数据量大㊁对实时性要求高的系统进行了设计与实现㊂2.1 C a m e r a L i n k 图像输入与采集模块C a m e r a L i n k 接口是由国家半导体试验室(N a t i o n a lI n s t r u m e n t s ,N I )于2000年推出的一种为解决视频数据输出和采集之间速度匹配问题的通信接口㊂它有三种传输模式:B a s e 模式㊁M e d i u m 模式和F u l l 模式㊂本系统只需使用一个C a m e r a L i n k 芯片,采用B a s e 模式㊂选用D S 90C R 286M T D C a m e r a L i n k 接口芯片,该芯片接收4对串行L V D S 差分数据信号和1对串行L V D S 差分时钟信号,输出28位数据信号和1位时钟信号,这28位数据包括24位图像数据和4位图像数据同步信号(L V A L ㊁F V A L 和D V A L ㊁S pa r e )㊂C a m e r a L i n k 图像采集就是根据C a m e r a L i n k 接口协议采集图像信息,图2为C a m e r a L i n k 图像输入的时序图㊂当检测到图像帧信号的下降沿(I m g _f v a l _n e g )或者接收完一幅图大小的b u r s t 长度的有效数据(b u r s t _d o w n )之后,开始设置D D R 的地址,并且将F I F O 中的数清除,紧接着根据L V A L ㊁F V A L 和D V A L 信号开始向F I F O 中写入数据(在此过程中加入行保护,确保每行写入固定的有效数据),当检测到图像帧信号的下降沿时,继续向F I F O 中写入16个填充数,写完后状态机重新回到I D L E 状态,等待接收下一幅图㊂在此过程中,第一幅图的接收用I m g _f v a l _n e g 信号触发,其余图用b u r s t _d o w n 信号触发,图3为图像接口时序的状态机图㊂图2 C a m e r a L i n k图像输入时序图图3 图像接口时序的状态机图2.2 C a m e r a L i n k 图像传输与存储模块Z y n q 7000芯片内部,P S 和P L 之间通过G P (通用接口)和H P (高性能接口)等多种A X I 接口进行实时数据交互㊂A X I 协议包含多种协议:A X I ㊁A X I _L i t e 和A X I 4_S t r e a m ㊂其中,A X I 4协议是基于b u r s t 的传输,适用于高性能㊁高带宽的系统设计㊂本系统分别使用了一个A X I _H P 端口和一个A X I _G P 端口完成C a m e r a L i n k 图像的传输㊂A X I _H P 端口通过一个互联矩阵A X I I n t e r c o n n e c t 0连接外设的主从设备,实现大数据量的传输,同时外设可通过A X I I n t e r -c o n n e c t 0访问A X I _H P 接口,进而访问D D R ;A X I _G P 端口通过一个互联矩阵A X I I n t e r c o n n e c t 1连接外设寄存器,传输数据量小的信息㊂图4为系统传输结构框图㊂接收图像时,P L 通过B a s e 模式访问D D R ,D D R 型号为M T 41K 256M 16R E 125,容量为1G B ,本系统使用2片16位D D R 3芯片构成32位的数据宽度㊂接收与采集模块将接收到的C a m e r a L i n k 图像数据写入到D D R 相应敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第7期45图4系统传输结构框图地址中㊂D D R开辟2片地址用于链接数据的乒乓存储,当P S接收到P L中断时,表示一幅图已经接收完成,便在D D R给定的地址中提取图像数据进行分析㊂向D D R中写入图像数据流程图如图5所示㊂当检测到设置地址标志寄存器为 1 时(s e t_b a s e_a d d r==1 b1),开始设置基地址,b u r s t长度计数器清零;当F I F O中的数据大于254个时(f i f o_c o u n t>=9 d254),开始向D D R中写入数据(f i f o_o u t_e n<=1 b1);当写够一个b u r s t长度的数据时(m00_a x i_b r e a d y==1 b1),b u r s t长度计数器加1(b u r s t_c n t <=b u r s t_c n t+1 b1),若s e t_b a s e_a d d r==1 b0,继续判断(m00_a x i_b r e a d y==1 b1),若是则继续加1,若s e t_ b a s e_a d d r==1 b1,则返回继续设置新的基地址,将b u r s t 长度计数器清零㊂2.3C a m e r a L i n k图像显示为了进一步测试接收图像是否正确,本系统设计了C a m e r a L i n k图像显示功能,使得测试结果更加简明直观㊂当P S接收到C a m e r a L i n k图像接收中断信号时,根据约定地址从D D R中取出图像数据,对图像的连续性进行判断,判断图像是否丢帧,通过串口将判断结果发送给上位机㊂同时通过千兆以太网将C a m e r a L i n k图像数据发送给上位机,上位机从串口接收到图像大小参数,从而对图像进行显示㊂3系统测试针对本系统的功能与性能测试,专门设计了一套测试设备,该测试设备对应本系统的C a m e r a L i n k图像输入模块设计了C a m e r a L i n k图像发送模块㊂C a m e r a L i n k图像发送模块模拟C a m e r a L i n k图像源,生成大小为1280ˑ960的黑白渐变图像,每个时钟生成两个像素,每个像素为一个字节,并且用帧号替代最后一个像素,F P G A输出图5向D D R中写入图像数据流程图的图像数据和时钟信号通过线路驱动器D S90C R285M T D X将其转换成串行的L V D S信号输入到F P G A中,经过C a m e r a L i n k图像采集㊁传输与存储模块后,P S端将接收到的图像数据通过网口发送给上位机,上位机根据从串口收到的图像信息将图像显示出来㊂经过2小时的连续测试,C a m e r a L i n k图像发送模块以20m s的帧频持续发送图像,图像均未出现丢帧现象,误码率为0,可证明该系统功能正确㊁性能稳定㊂图6和图7分别为上位机测试界面和C a m e r a L i n k接收图像㊂图6上位机测试界面50M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第7期w w w .m e s n e t .c o m .c n合柑橘的外观形状,采用圆形边界框代替传统矩形边界框,并以此改进了边框回归损失函数,不仅降低了运算量,还提升了柑橘检测精度㊂通过对比实验及嵌入树莓派的验证可知,S l i m Y O L O v 4算法具有内存开销小㊁检测精度高的特点,能够满足柑橘采摘的实际需要㊂未来,还将尝试加入更多的影响因素来完善此算法,并将其应用于柑橘采摘的机器人中㊂参考文献[1]卢军,桑农.变化光照下树上柑橘目标检测与遮挡轮廓恢复技术[J ].农业机械学报,2014,45(4):681,60.[2]岳有军,田博凯,王红君,等.基于改进M a s k R C N N 的复杂环境下苹果检测研究[J ].中国农机化学报,2019,40(10):128134.[3]H E K M ,G K I O X A R I G ,G I R S H I C K R ,e t a l .M a s k R C N N[C ]//P r o c e e d i n gs o f t h e 2017I E E E I n t e r n a t i o n a l C o n f e r e n c e o n C o m p u t e r V i s i o n .P i s c a t a w a y:I E E E ,2017:29802988.[4]B o c h k o v s k i y A ,W a n g C Y ,L i a o H Y M.Y O L O v 4:o pt i m a l s p e e d a n d a c c u r a c y o f o b j e c t d e t e c t i o n [J ].C o m pu t e r V i s i o n a n d P a t t e r n R e c o gn i t i o n ,2020,17(9):198215.[5]HA N K ,WA N G Y ,T I A N Q ,e t a l .G h o s t N e t :M o r e f e a t u r e sf r o m c h e a p o p e r a t i o n s [C ]//P r o c e e d i n gs o f t h e I E E E /C V F C o n f e r e n c e o n C o m p u t e r V i s i o n a n d P a t t e r n R e c o g n i t i o n ,2020:15801589.[6]Z h e n g Z ,W a n g P ,L i u W ,e t a l .D i s t a n c e I o U L o s s :F a s t e r a n d B e t t e r L e a r n i n g f o r B o u n d i n g B o x R e gr e s s i o n [C ]//A A A I C o n f e r e n c e o n A r t i f i c i a l I n t e l l i ge n c e ,2020.[7]S h u L ,L u Q ,H a if a ng Q ,e t a l .P a th a g g r e ga t i o n n e t w o r k f o r i n s t a n c e s e g m e n t a t i o n [C ]//I E E E C o n f e r e n c e o n C o m pu t e r V i s i o n a n d P a t t e r n R e c o g n i t i o n .S a l t L a k e C i t y:I E E E ,2018:87598768.[8]S a n d l e r M ,H o w a r d A ,Z h u M ,e t a l .M o b i l e n e t v 2:I n v e r t e dr e s i d u a l s a n d l i n e a r b o t t l e n e c k s [C ]//I E E E C o n f e r e n c e o nC o m p u t e r V i s i o n a n d P a t t e r n R e c o g n i t i o n .S a l t L a k e C i t y:I E E E ,2018:45104520.[9]L i u G ,N o u a z e J C ,T o u k o P L ,e t a l .Y O L O T o m a t o :A R o -b u s t A l g o r i t h m f o r T o m a t o D e t e c t i o n b a s e d o n Y O L O v 3[J ].S e n s o r s ,2020,20(7).[10]R e d m o n J ,F a r h a d i A.Y O L O v 3:a n i n c r e m e n t a l i m pr o v e -m e n t [C ]//I E E E C o n f e r e n c e o n C o m pu t e r V i s i o n a n d P a t -t e r n R e c o gn i t i o n ,2018:8995.韩进(教授),主要研究方向为嵌入式计算机控制㊁计算机系统结构㊁电子电路;舒媛(硕士研究生),主要研究方向为嵌入式系统技术㊁物联网软件技术㊂通信作者:韩进,s h n k 123@163.c o m㊂(责任编辑:薛士然 收稿日期:2021-02-22)图7 C a m e r a L i n k 接收图像4 结 语本文面向实时高速数字图像的采集和处理,运用模块化设计思想,基于Z y n q 7000数字图像处理系统实现了数字图像高速输入与采集㊁存储与传输和显示功能,并且设计了简易的验证平台㊂经过验证,本系统实时性高㊁体积小㊁性能稳定,可以实现大数据量的图像采集与传输,目前已应用在实际的项目中㊂参考文献[1]刘宏,符意德.基于Z y n q 芯片的图像处理系统平台设计[J ].计算机与现代化,2015(8):4347.[2]王珂.基于Z Y N Q 的高速图像采集处理平台设计与验证[D ].济南:山东大学,2016.[3]黄志超.基于C a m e r a l i n k 标准的D S P +F P G A 数字图像处理系统设计[J ].科技与管理,2012(7):152153.[4]陈炎斌,金钢.基于C a m e r a _L i n k 标准的高速实时数字图像处理系统设计[J ].现代科学仪器,2010(6):6163.[5]刘应盼.基于Z Y N Q 的图像采集处理系统设计与实现[D ].西安:西安电子科技大学,2019.[6]焦再强.基于Z y n q 7000的嵌入式数字图像处理系统设计与实现[D ].太原:太原理工大学,2012.[7]高媛,商远波.一种基于C a m e r a L i n k 的数字图像处理系统[J ].制导与引信,2017(38):2932.[8]杨晓安,罗杰,苏豪,等.基于Z y n q 7000高速图像采集与实时处理系统[J ].电子科技,2014(7):151154.[9]郭钊.嵌入式图像并行处理系统的研究与应用[D ].兰州:兰州理工大学,2014.通信作者:王咏星,78233164@q q.c o m ㊂(责任编辑:薛士然 收稿日期:2021-01-26)。

Zynq-7000 All Programmable SoC工业自动化方案

P r o g r a m m a b l e解 决 方 案 ,以应 对 高 赛 灵 思 与其 联 盟 汁 划 成 员 QDE S YS 以太 网套件结 合使 用 ,开发 出业 界一

级 运 动 控 制 、实 时 工 业 网 络 、机 器 公 司 提 供 了 基 于 Z y n q . 7 0 0 0 Al l 流的双 核锁步 马达控 制应 用的企 业 。 视 觉 以及 其 他 新 一 代 工 业 自动 化 应 P r o g r a mma b l e S o C智能 驱动 平 台 的 该 应 用 将 帮 助 设 计 者 实 现 其 系 统 的 用 的 挑 战。 赛 灵 思 以 Z y n q - 7 0 0 0 Al 高性能运 动控 制应用 ,可 以实 现千 兆 I l E C6 1 5 0 8功能安全认证 。

随 着设 备综合效 率 ( OE E)的 模 型 ( C OM)接 口的支持下 ,设计 人 计 ,可加 速工业 嵌入式 控制 系统 的设 不 断提 高 ,工业 自动化 市场需 要实现 员能对运动系统进行深入分析和控制 , 计与 实现进程 。该平 台非常适 合要 求 S P解决方 案而 言实 单芯 片高性能 马达控 制和 工业 网络功 更高生产 力 ,降低总拥 有成本 ,同时 相对于传 统 的 AS 还 需要提 高安 全性和 系统功 能 。要满 现了性能的提 升。 足上述 要求 ,系统 的计 算性能 必须 更 能的设 计。赛灵思提 供 Z y n q - 7 0 0 0 A l l

P r o g r a mma b l e S o C为 核 心 的系统 开 位 以太 网紧密 集成 网络 、采用 创新型

赛 灵 思 与 其 联 盟 成 员共 同 推 出

发软 / 硬 件技 术 ,不 仅能 加 速设 计生 低 E MI 功率调制 方案 的高级 马达和运 的 新 Z y n q 一 7 0 0 0 Al l P og r r a mma b l e 产 力 ,同时还 可通 过单 芯片系统 集成 动控制 。在面 向 Wi n d o ws 应用 的图形 S o C智能驱 动器平 台提供 了必要 的硬 提升 系统 的性能和安全性 。 用户 界面 ( GU I )和 强大 的组 件 对 象 件 、设计 工具 、马达 、I P核和 参考 设

在Zynq SoC上实现裸机(无操作系统)软件应用方案

在Zynq SoC上实现裸机(无操作系统)软件应用方

案

Zynq™-7000 All Programmable SoC在单个器件上实现了ARM 处理功能与FPGA逻辑独特的组合,因此需要双重的配置过程,同时需要考虑处理器系统和可编程逻辑。

工程师会发现,其配置顺序与传统的赛灵思FPGA稍有差别。

尽管如此,方法仍是相似的,生成引导镜像和完成配置存储器编程的难度不大。

虽然标准的FPGA配置实践一般只需要FPGA bit文件,但是如果您想最大限度地利用Zynq SoC的优势,还需要添加另一种配置文件,即软件可执行与可链接格式(ELF)文件。

FPGAbit文件用于定义设计中可编程逻辑部分的行为,而ELF文件则是处理系统将要执行的软件程序。

下面让我们来看看如何在Zynq SoC上实现裸机(无操作系统)软件应用。

配置概览

在Zynq SoC中,处理系统(PS)处于主控地位,因此负责配置器件。

zynq-7000简介

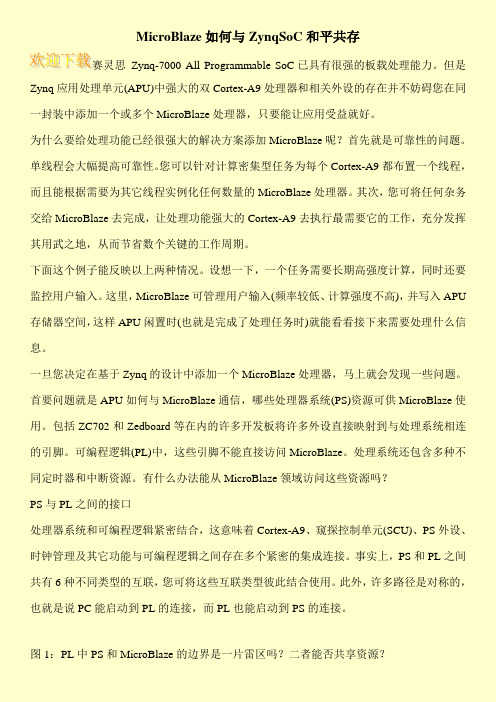

赛灵思Zynq-7000 可扩展处理平台(EPP)将双 ARM Cortex-A9 MPCore 处理器系统与可编程逻辑和硬 IP 外设紧密集成在一起,提供了灵活性、可配置性和性能的完美组合。

围绕其刚刚推出的可扩展处理平台(EPP),赛灵思在今年3月发布了基于Zynq -7000新系列的首批器件。

采用 28 nm制造工艺, Zynq-7000嵌入式处理平台系列的每款产品均采用带有NEON及双精度浮点引擎的双核 ARM Cortex-A9 MPCore 处理系统,该系统通过硬连线完成了包括L1,L2 缓存、存储器控制器以及常用外设在内的全面集成。

(图 1)。

尽管 FPGA 厂商此前已推出过带硬核或软核处理器的器件,但 Zynq-7000 EPP 的独特之处在于它由ARM 处理器系统而非可编程逻辑元件来进行控制。

也就是说,处理系统能够在开机时引导(在FPGA 逻辑之前)并运行各个独立于可编程逻辑之外的操作系统。

这样设计人员就可对处理系统进行编程,根据需要来配置可编程逻辑。

利用这种方法,软件编程模式将与全功能标准 ARM 处理器片上系统(SoC)毫无二致。

过去设计师需要对 FPGA 逻辑进行编程以运行片上处理器。

那就意味着如果想要使用器件,必须得是 FPGA 设计师。

但现在使用 Zynq-7000 EPP,则完全不必担心这一问题。

图 1 ——不同于以往在 FPGA 架构中嵌入 MPU ,赛灵思全新 Zynq-7000 EPP 系列使用ARM 处理器而非可编程逻辑来进行控制。

图1中文字:Multi Gigabit Transceivers 多个千兆位收发器新产品系列消除了延迟和从头设计芯片的风险,这意味着系统设计团队可以利用其先进的高级软硬件编程多功能性简便快速创建创新型片上系统,而这是其他任何半导体器件都无法实现的。

这样,Zynq -7000 EPP 能够为广大的创新者带来无法比拟的益处,无论是专业的硬件、软件、系统设计师或仅是单纯的“制造商”,他们都可以探讨处理能力与编程逻辑结合的可能性,进而创建出从未想象过的创新应用。

(最新整理)Zynq7000可编程逻辑资源PL

用于芯片-芯片接口的低功耗模式优化。

高级的预发送、后加重,以及接收器线性CTLE,以及判决反馈均衡

(Decision Feedback Equalization,DFE),包括用于额外余量的自适

应均衡。

10

2021/7/26

可编程逻辑资源

XADC(模拟-数字转换器)

双12比特1Msps模拟-数字转换器(ADC)。 最大17个灵活和用户可配置模拟输入。 片上或者外部参考选择。 片上温度(±4℃最大误差)和供电(±1%最大误差)传感器。 连续JTAG访问ADC测量。

2021/7/26

可编程逻辑资源

--可编程逻辑资源功能

所有Slice中间25-50%也使用LUT作为分布式的64位RAM或

者32位移位寄存器(SRL32)或者两个SRL16。

现代综合工具利用了这些高性能逻辑、算术和存储器特性。

Zynq-7000内的LUT可以配置为一个带有1个输出的6输入

LUT(64位ROM)或者带有独立输出和公共地址/逻辑输入

反馈分频器M(通过配置或者之后通过DRP编程),作为一个乘法 器。这是由于在送到相位比较器的其它输入之前,将VCO的输出频 率进行分频。必须合理地选择D和M的值,以确保VCO工作在它指 定的频率范围内。

16

2021/7/26

可编程逻辑资源功能

--时钟管理

VCO有8个等间距的输出相位(0º,45 º,90 º,135 º,180 º,

9

2021/7/26

可配置的I/O

可编程逻辑资源

高性能SelectIO技术。

集成在封装内的高频去耦合电容,用于扩展的信号完整性。

数控阻抗,能在三态下用于最低功耗,高速I/O操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

检测器测量到的信号功率可表达为:

P=0∞

∫I(众多开发人员来说,现在用赛灵思FPGA 或Zynq-7000 All Programmable SoC 这样的可编程逻辑器件来实现自动白平衡校正可能会是一个全新的挑图1 “标准观察者”的光谱响应

适应”或者“色彩恒常性”。

但是,如果相机不具备针对不同光源进行调整或自动补偿的功能,获得的色彩就会发生变化。

而相机对这种情况进行校正的行为,就称为白平衡校正。

图1右侧的等式分别用于描述光源的光谱、场景中各种物质的反射特性以及检测器的光谱敏感度。

这三者共同决定最终的色彩测量。

因此即便是采用相同的检测器,测量结果还混合在一起。

只要满足下列条件,就有可能实现白平衡,或者说将固有的反射特性R(λ)与光源的光谱I(λ)分离。

●采用启发法,比如光源上的空间频率限制,或者先验性地知道物体的色彩。

例如,在日光下拍摄场景时,可以预计光源的光谱特性将在整个图像上保持恒定。

与此相反,如果将图像投影到白屏幕上,光源的光谱图2b 作为R、G、B输入对应的R分量输出

图2a R、G、B测量值与映射预期值的对比图3 典型图像传感器流水线

这种方法的优势在于相对简单,易于实现,仅使用三个并行乘法器,并将其作为数字图像传感器或图像传感器流水线(ISP)的一部分:

在实际实现中,使用RGB色域替代LMS域来调整通道增益。

一种颜色(以白色为代表)通常用相等的R、G、B值来表示。

但是,针对某种色彩调整感知视椎细胞反应或R、G、B值,不能保证其它色彩也得到如实表达。

基于伽马校正和色彩校正矩阵的解决方案相比并没有明显的质量改进。

大

白平衡校正使用的两种最简单的算法是灰度世界算法和白点算法。

这两种方法均使用RGB色域。

图4 在镜头校正前不同光源下的传感器图像白炽灯

日光冷白荧光灯 暖光荧光灯

或皮肤颜色检测有助于相机识别有预期色调的图像内容。

这样只需要对有已知和预期的色调的像素进行白平衡校正。

颜色校正就是将这些像素的颜的部分是一个反馈环路,包括:

●

图像统计模块,用于逐帧采集各域的统计数据;

●

嵌入式驱动程序和应用软件,

图5 不同光源下的色彩校正,镜头校准图像

日光冷白荧光灯

暖光荧光灯

白炽灯

●色彩校正模块,用于逐像素地执行色彩转换。

我们将该ISP实现为Zynq视频和成像套件(ZVIK)1080x60相机图像处理参考设计的组成部分。

算法详解

为校准传感器的颜色,我们使用现成的颜色观察箱(X-Rite Macbeth 心,然后计算出与每个色标的RGB预

期值(Re、Ge、Be)对应的平均RGB三

模拟退火算法的作用是求出一个

能够返回标量的误差函数的最小值。

●RGB色域中预期三元色和转换后三

元色之间的绝对差和:

●YUV色域中预期三元色和转换后三

元色之间的方差和:

●YUV色域中预期三元色和转换后三

元色之间的绝对差和:

其中U’和V’对应的是R’G’

到YUV色域的值。

与此类似,

也可设置用于L*u*v*或是 L*a*b*

图6 CIE色域中不同温度下的光源

图7 捕获到的未校正的场景(左图)和经白平衡校正过的场景(右图)

其中H k(X,Y)是与已知

{k=1,2,3,4}有关的预先计算出的基准二维直方图,H(x,y)是实时测量的

为避免逐帧色调陡变

准化相似值按时间进行平滑处理

们采用简单的低通

其中0<C<1,用于控制

的脉冲响应。

C值越小,图7是自然光和荧光灯照明条件场景采用实时白平衡算法实现的,可以看出感知的图像质量和色。