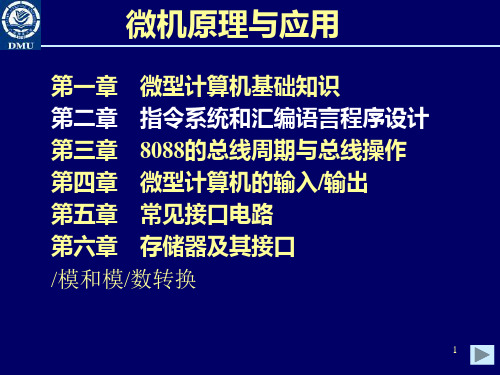

学习课件微机原理与接口技术

合集下载

微机原理与接口技术课件PPT

汇编语言的优点

汇编语言具有高效、可移植性、 可维护性等优点,适用于编写操 作系统、编译器等关键软件。

汇编语言的缺点

汇编语言编写复杂,容易出错, 且可移植性较差,需要针对不同 的计算机体系结构进行修改。

高级语言

01

高级语言的定义

高级语言是一种抽象程度更高的 编程语言,它使用更接近自然语 言的语法和语义。

实验提供参考。

THANKS FOR WATCHING

感谢您的观看

串行接口的数据传输速率比并行 接口慢,但只需要一根数据线, 因此成本较低。

03

串行接口的常见标准包括RS-232 、RS-422和USB。

04

中断控制器

中断控制器是微机中的一 种重要组件,它负责管理 计算机系统中断的处理。

中断控制器可以管理硬件 设备的中断请求,例如键 盘、鼠标和计时器等。

ABCD

并行接口通常用于连接打印机、磁盘驱动器等高速设备, 因为这些设备需要快速传输大量数据。

并行接口的常见标准包括ECP、EPP和USB。

串行接口

01

串行接口是一种数据传输方式, 它通过单个数据线逐位传输数据 。

02

串行接口通常用于连接鼠标、调 制解调器等低速设备,因为这些 设备不需要快速传输大量数据。

语音识别和图像处理

利用微机原理与接口技术,可以实现语音识 别和图像处理等功能,提高办公自动化水平 。

在家用电器中的应用

1 2 3

智能家居控制

微机原理与接口技术可以用于智能家居控制,实 现家用电器的远程控制和自动化控制。

电视和音响设备控制

通过微机原理与接口技术,可以实现电视和音响 设备的智能控制,提供更加便捷和智能的娱乐体 验。

微机原理与接口技术精品PPT课件

存储器芯片容量=单元数×存储器接收到从CPU给出的有效地址到完成一次读出和写 入数据所需要的时间。

3.功耗

MOS型存储器的功耗小于相同容量的双极性存储器, CMOS器件功耗低,速度慢;HMOS的存储器件在速度、 功耗、容量方面进行了折衷。

11:42

12

4.可靠性

11:42

8

二、存储器组织

16位微机系统配置两个存储体,分别连接数据总线 D7~D0和D15~D8,一次数据总线传送16位数据;

32位微机系统配置4个存储体,分别连接数据总线 D7~D0,D15~D8, D23~D16及D31~D24,一次数 据总线传送32位数据;

Pentium以上微机系统配置8个存储体,分别连接64 位数据总线。

容量大小:受到地址总线位数的限制。8086系统,20条地址 总线,可以寻址内存空间为1M字节;80386系统,32条地址总 线,可以寻址4G字节。

存放内容:系统软件(系统引导程序、监控程序或者操作系

统中的ROM BIOS等)以及当前要运行的应用软件。

11:42

2

(1)RAM随机存取存储器(Random Access Memory)

指存储器对电磁场和温度变化等的抗干扰能力,以及高速使 用时的正确存取能力。

5.寿命

Flash Memory寿命大于EEPROM,EEPROM寿命大于 EPROM。

6.价格

存储器本身的价格、附加电路的价格。SRAM的价格高, 但速度快;DRAM相对廉价,但是速度较慢。

11:42

13

§5-2 随机存取存储器RAM

DRAM运行速度较慢,SRAM比DRAM要快2~5倍,一般, PC机的标准存储器都采用DRAM组成。

11:42

3.功耗

MOS型存储器的功耗小于相同容量的双极性存储器, CMOS器件功耗低,速度慢;HMOS的存储器件在速度、 功耗、容量方面进行了折衷。

11:42

12

4.可靠性

11:42

8

二、存储器组织

16位微机系统配置两个存储体,分别连接数据总线 D7~D0和D15~D8,一次数据总线传送16位数据;

32位微机系统配置4个存储体,分别连接数据总线 D7~D0,D15~D8, D23~D16及D31~D24,一次数 据总线传送32位数据;

Pentium以上微机系统配置8个存储体,分别连接64 位数据总线。

容量大小:受到地址总线位数的限制。8086系统,20条地址 总线,可以寻址内存空间为1M字节;80386系统,32条地址总 线,可以寻址4G字节。

存放内容:系统软件(系统引导程序、监控程序或者操作系

统中的ROM BIOS等)以及当前要运行的应用软件。

11:42

2

(1)RAM随机存取存储器(Random Access Memory)

指存储器对电磁场和温度变化等的抗干扰能力,以及高速使 用时的正确存取能力。

5.寿命

Flash Memory寿命大于EEPROM,EEPROM寿命大于 EPROM。

6.价格

存储器本身的价格、附加电路的价格。SRAM的价格高, 但速度快;DRAM相对廉价,但是速度较慢。

11:42

13

§5-2 随机存取存储器RAM

DRAM运行速度较慢,SRAM比DRAM要快2~5倍,一般, PC机的标准存储器都采用DRAM组成。

11:42

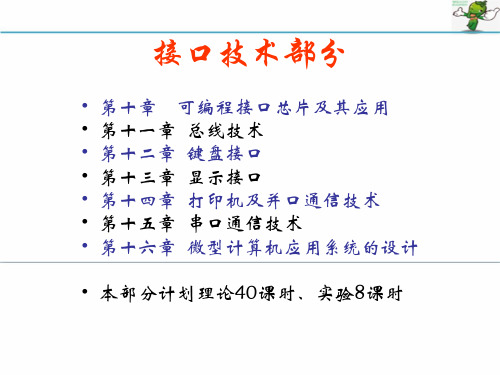

微机原理与接口技术PPT课件(共16章)10可编程接口芯片及其应用

返回本章目录

10.1 可编程并行接口芯片8255A

10.1.1 8255A的结构及引脚功能

8255A内部结构如图10.1所示,其中包括三个8位并行 数据I/O端口,两个工作方式控制电路,一个读/写控制逻辑电 路和一个8位数据总线缓冲器。各部分功能介绍如下:

1.三个8位并行I/O端口PA、PB、PC。 PA口:具有一个8位数据输出锁存/缓冲器和一个8位数据输入锁存

计数器 0号

计数器 1号

控制 寄存器

计数器 2号

图10.19 8253的内部结构

CLK0 GATE0 OUT0

2、PC口的置位/复位控制字:可以对PC口各位进行按位操作,以实现某些 控制功能。对控制寄存器写入一个置位/复位控制字,即可把PC口的某一位 置“1”或清“0”,而不影响其他位的状态。该控制字的格式和定义如图 10.15(b)所示。其中D7是标识位,D7=0表示本字是置位/复位控制字;D6-D4 未用,一般置成000;D3~D1用来确定对PC口的哪一位进行置位/复位操作; D0用于对由D3-D1确定的位进行置“1”或清“0”。

开始

开始

PC口位操作,置 STB,启动外围设备

外围设备不空,等待

PC口采样外围设备状态

N RDY=1 Y

从8255A输入数据

C口采样外围设备状态 外围设备不空,等待

N RDY=1 Y

数据写入8255A,并锁存

PC口位操作,产生STB脉冲

(a)读操作流程图

(b) 写操作流程图

返回本章目录

10.1.3.1 8255A工作方式1

器。可编程为8位输入或8位输出或8位双向输入且输出。 PB口:具有一个8位数据输入/输出、锁存/缓冲器和一个8位数据

10.1 可编程并行接口芯片8255A

10.1.1 8255A的结构及引脚功能

8255A内部结构如图10.1所示,其中包括三个8位并行 数据I/O端口,两个工作方式控制电路,一个读/写控制逻辑电 路和一个8位数据总线缓冲器。各部分功能介绍如下:

1.三个8位并行I/O端口PA、PB、PC。 PA口:具有一个8位数据输出锁存/缓冲器和一个8位数据输入锁存

计数器 0号

计数器 1号

控制 寄存器

计数器 2号

图10.19 8253的内部结构

CLK0 GATE0 OUT0

2、PC口的置位/复位控制字:可以对PC口各位进行按位操作,以实现某些 控制功能。对控制寄存器写入一个置位/复位控制字,即可把PC口的某一位 置“1”或清“0”,而不影响其他位的状态。该控制字的格式和定义如图 10.15(b)所示。其中D7是标识位,D7=0表示本字是置位/复位控制字;D6-D4 未用,一般置成000;D3~D1用来确定对PC口的哪一位进行置位/复位操作; D0用于对由D3-D1确定的位进行置“1”或清“0”。

开始

开始

PC口位操作,置 STB,启动外围设备

外围设备不空,等待

PC口采样外围设备状态

N RDY=1 Y

从8255A输入数据

C口采样外围设备状态 外围设备不空,等待

N RDY=1 Y

数据写入8255A,并锁存

PC口位操作,产生STB脉冲

(a)读操作流程图

(b) 写操作流程图

返回本章目录

10.1.3.1 8255A工作方式1

器。可编程为8位输入或8位输出或8位双向输入且输出。 PB口:具有一个8位数据输入/输出、锁存/缓冲器和一个8位数据

微机原理与接口技术-周荷琴第4版ppt课件

2、存储器

功能:存放程序和数据。

SRAM RAM DRAM

存储器

内存(主存) 外存(辅存)

ROM

ROM

EPROM E2PROM

软盘、U盘

硬盘(移动硬盘)

• AMD Athlon II X2 240/盒装 本周劲热排 行第3位

• 参考价格: ¥380(全国) • 接口类型:Socket AM3(938) • 生产工艺:45纳米 • 主频:2.8GHz • 二级缓存:L2=2×1M • 核心数量:双核

4、十六进制表示法 基数为16,用0 - 9 、A - F 十五个字符来数值,逢十六 进一。 各位的权值为 16i 。

二进制表示数值方法如下:

n NH= ± Ki * 16i

i=-m

其中:K = 0 - 9 、A - F i

例:(56D.3)H = 5 * 162 + 6 * 161 + 13 * 160 + 3 * 16-1

I/O设备

输入设备

输出设备

键盘 鼠标 扫描仪、数码相机

显示器 打印机 绘图仪

(2)、I/O接口:连接外设备和系统总线,完成信号 转换、数据缓冲、与CPU进行信号联络等工作。

显示器卡:完成显示器与总线的连接。 声卡:完成声音的输入/输出。 网卡:完成网络数据的转换。 扫描卡:连接扫描仪到计算机。 调制解调器卡:模拟信号与数字信号相互转换。 键盘接口、打印机接口等。 232接口:串行数据接口。

运算规则:

加法运算:

0+0 = 0 0+1 = 1 1+0 = 1 1+1 =10 (逢二进一) 减法运算:

0-0 = 0 10-1 =1 (借位) 1-0 = 1 乘法运算:

微机原理与接口技术PPT课件

(2)如果要对其他段寄存器所指出的存储区 进行直接寻址,则本条指令前必须用前缀指出 段寄存器名。

21018H 21019H

AA 数 BB 据

段

8

三、直接寻址

• 操作数的存储区是在DS段以外的段中,则应 在指令中指定段跨越前缀:

• MOV BX, ES:[2000H] 设ES=3000H,则指令执行后是将32000H

• 操作数的寻址方式有以下几种:

•

立即数寻址

寄存器寻址

直接寻址

寄存器间接寻址

寄存器相对寻址

基址加变址寻址

相对的基址加变址寻址

• 例:指令形式:

MOV AX, 0000H; AX← 0000H

助记符 目的操作数 源操作数

4

一、立即数寻址

• 操作数紧跟在操作码的后面,与操作码一起放在码段

区域,立即数可以为8位,也可以为16位。

设SS=3000H,BP=2000H, COUNT=1050H

有效地址为: EA=2000H+1050H=3050H

物理地址: 堆栈段=30000H+3050H=33050H

存储器

M

10000H 8B 代

10001H 86 码

10002H

段

AH AL BB AA

33050H 33051H

AA 堆 BB 栈

代码:8B 07

设 DS=2000H,BX=5000H CS=1000H,IP=0000H

物理地址: 代码段:CS000H 8B 代

10001H 07 码

10002H

段

数据段:DS ×16+BX=25000H

AH AL

BB AA

25000H 25001H

微机原理与接口技术PPT教学课件

二、存储器容量

存储容量是衡量微型计算机中存储能力的 一个指标,它包括内存容量和外存容量。内存 容量分最大容量和装机容量,外存容量是指磁 盘机和光盘机等容量。

③ 各种服务性程序,如机器的调试、故障检查和 诊断程序、杀毒程序等。

④ 各种数据库管理系统,如SQL Sever、Oracle、 Foxpro等。

2020/12/11

13

1.1 微型计算机及其特点

应用软件是用来为用户解决某种应用问题 的程序及相关的文件和资料。常见应用软件主 要有以下几种: ① 用于科学计算方面的数学计算软件包、统计软 件包。 ② 文字ห้องสมุดไป่ตู้理软件包(如WPS、Office )。 ③ 图像处理软件包(如Photoshop、动画处理软 件3DS MAX)。 ④ 各种财务管理软件、税务管理软件、工业控制 软件、辅助教育等 。

一、微型计算机系统

微型计算机系统由硬件(Hardware)系统和 软件(Software)系统两大部分组成。

硬件系统是指微机的物理实体,由电子部件 和机电装置组成,包括主机箱内的MPU、RAM、 ROM、I/O接口、系统总线及控制电路、外围硬 件设备等。

具体由五大功能部件组成,即:运算器、控 制器、存储器、输入设备和输出设备。其中运算 器和控制器统称为微处理器(MPU)或中央处理 器(Contol Processing Unit,CPU)。

通过本章学习内容,会对微型计算 机概况有一个较全面的了解,为后续 内容的学习指明方向。

2020/12/11

3

1.1 微型计算机及其特点

1.1.1 微型计算机系统简介

一、微型计算机系统

微型计算机系统简称为MCS(micro computer system),它以微型计算机为核心, 再配备以相应的外围设备、辅助电路和电源 (统称硬件)及指挥微型计算机工作的系统软 件,便构成了一个完整的系统。

存储容量是衡量微型计算机中存储能力的 一个指标,它包括内存容量和外存容量。内存 容量分最大容量和装机容量,外存容量是指磁 盘机和光盘机等容量。

③ 各种服务性程序,如机器的调试、故障检查和 诊断程序、杀毒程序等。

④ 各种数据库管理系统,如SQL Sever、Oracle、 Foxpro等。

2020/12/11

13

1.1 微型计算机及其特点

应用软件是用来为用户解决某种应用问题 的程序及相关的文件和资料。常见应用软件主 要有以下几种: ① 用于科学计算方面的数学计算软件包、统计软 件包。 ② 文字ห้องสมุดไป่ตู้理软件包(如WPS、Office )。 ③ 图像处理软件包(如Photoshop、动画处理软 件3DS MAX)。 ④ 各种财务管理软件、税务管理软件、工业控制 软件、辅助教育等 。

一、微型计算机系统

微型计算机系统由硬件(Hardware)系统和 软件(Software)系统两大部分组成。

硬件系统是指微机的物理实体,由电子部件 和机电装置组成,包括主机箱内的MPU、RAM、 ROM、I/O接口、系统总线及控制电路、外围硬 件设备等。

具体由五大功能部件组成,即:运算器、控 制器、存储器、输入设备和输出设备。其中运算 器和控制器统称为微处理器(MPU)或中央处理 器(Contol Processing Unit,CPU)。

通过本章学习内容,会对微型计算 机概况有一个较全面的了解,为后续 内容的学习指明方向。

2020/12/11

3

1.1 微型计算机及其特点

1.1.1 微型计算机系统简介

一、微型计算机系统

微型计算机系统简称为MCS(micro computer system),它以微型计算机为核心, 再配备以相应的外围设备、辅助电路和电源 (统称硬件)及指挥微型计算机工作的系统软 件,便构成了一个完整的系统。

微机原理与接口技术 ppt课件

SI

它支持间接寻址、变址寻址、基址 指示数据段(段默认)或其他

加变址寻址等多种寻址

段(段超越)中源操作数的偏

移地址

目的变址(Destination Index) 串操作时用作目的变址寄存器,

DI 寄存器。它支持间接寻址、变址寻 指示附加段(段默认)中目的 址、基址加变址寻址等多种寻址 操作数的偏移地址

堆栈向低地址方向生成。数据每次进栈时堆栈指针 SP向低地址方向移动(减2);反之,数据出栈时, SP向高地址方向移动(加2)

(2)BP、BX都被称为基址指针,但两者用法不同。BP 只能寻址堆栈段(段缺省),不允许段跨越;BX可以寻 址数据段(段缺省),也可以寻址附加段(段跨越)。

(3)由于大多数算术和逻辑运算中又可以使用BP、SP和 变址寄存器,因而也将这4个寄存器归入通用寄存器组。 使用中应该注意这4个寄存器只能用于16位的存取操作

2.总线接口部件BIU

(1) BIU的功能: 1) BIU从主存取指令送到指令队列缓冲器 2) CPU执行指令时,总线接口单元要配合 EU从指定的主存单元或外设端口中取数据, 将数据传送给EU或把EU的操作结果传送 到指定的主存单元或外设端口中 3) 计算并形成访问存储器的20位物理地址

第2章 微处理器

微处理器,又称中央处理单元(Central Processing Unit,CPU)是采用大规模(LSI)或超大 规模集成电路(VLSI)技术制成的半导体芯片。它 将控制单元,寄存器组,算术逻辑单元(ALU)及 内部总线集成在芯片上,组成具有运算器和控制器 功能的部件。

2.1 8086微处理器的结构

(3)BIU的特点:

2) 地址加法器是用来产生20位存储器物理地址 的。物理地址的计算公式为: • 物理地址(20位)= 段基址(16位)×16+ 偏移地 址(16位) {由寻址方式计算出的有效地址EA(Effective Address) }

微机原理与接口技术课件

255(00H--FFH),即一个字节的地址值。端口间接

寻址DX的取值范围为0-65535(0000H—FFFFH),

很明显当端口地址超出255时,只能先将地址送给 DX,然后再用DX间接寻址。

例3.8: IN AX,41H

;41H为端口直接寻址

OUT DX,AL ;DX为端口间接寻址

转移指令的寻址方式

例3.6:(以下第二操作数为基址变址寻址方式) MOV AX,[BX+SI]

MOV BX,DS:[BP+SI] MOV BP,[BX+DI] MOV DX,[BP][DI] ;另一种书写格式

5 相对基址变址寻址方式

• 存储器操作数的内存偏移地址部分是由某一个基 址寄存器的内容加上某一个变址寄存中的内容再 加上一个相对偏移量的寻址方式叫基址变址寻址 方式,即EA=BR+IR+n。写在汇编指令中的BR 只能为BX或BP,IR只能为SI或DI,所以它们只有 四种组合:BX+SI+n、BX+DI+n、BP+SI+n、 BP+DI+n,若用到BP则默认相对SS段,其它则 默认相对DS段。相对偏移量可以是常数、常量、 常数表达式以及变量名等。

3.2.1.3 存储器寻址方式

• 指令中操作数是操作对象在内存中的存放地址的寻址方式 叫存储器寻址方式,操作对象实质上是内存地址所对应的 存储单元中的内容。前面已讲过内存的地址是由段地址及 段内偏移地址确定的,段地址的确定实质上是确定用哪个 段寄存器,段寄存器除非在指令中特别指定(即段超越, 用段寄存器名加“:”),其它情况下均为默认的,默认情 况如表3.1所示(括号内代表可以使用的段超越)。

第三章 寻址方式及指令系统

3.1基本概念

3.2寻址方式

操作数的寻址方式 转移指令的寻址方式

微机原理与接口技术课件

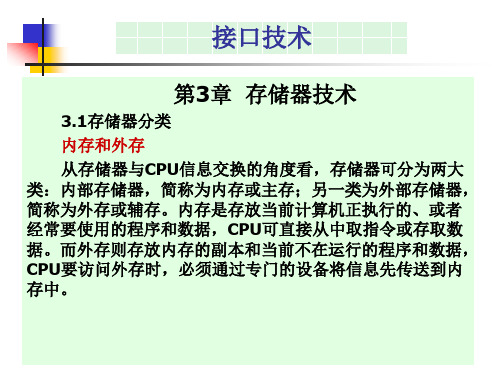

接口技术

第3章 存储器技术

3.1存储器分类 内存和外存 从存储器与CPU信息交换的角度看,存储器可分为两大 类:内部存储器,简称为内存或主存;另一类为外部存储器, 简称为外存或辅存。内存是存放当前计算机正执行的、或者 经常要使用的程序和数据,CPU可直接从中取指令或存取数 据。而外存则存放内存的副本和当前不在运行的程序和数据, CPU要访问外存时,必须通过专门的设备将信息先传送到内 存中。

非易失性RAM(IRAM)

组合ROM CREEM

接口技术

第3章 存储器技术

3.1存储器分类 半导体存储器分类

1. RAM (1)双极型RAM。存取速度高,常常高于Cache。 (2)MOS RAM。集成度高、功耗低、价格低。有(SRAM)、 (DRAM)、组合(IRAM)和非易失性RAM(NVRAM)。 SRAM:集成度高于双极型但低于DRAM;不需要刷新电路。 DRAM:用单管线路组成,集成度高;功耗低于SRAM;价格低; 需要刷新电路;存取速度高于SRAM。 IRAM:附有刷新电路的DRAM。大容量内存一般都用IRAM。 NVRAM(Non Volatile RAM):是SRAM和EEPROM的合成体。 用来存储一些重要信息,用于掉电保护。

3.4 Cache 地址映象

由主存地址映像到Cache地址称为地址映像。 (1)直接映像法。 每个主存块只与一个缓存块相对应,映射关系:i=j mod C 其中i为缓存块数,j为主存块号,C为缓存块数,等于2c,映射的 结果表明每个缓存块对应若干个主存块。 实现简单,只需利用主存地址的某些位直接判断,即可确定所需字 块是否在缓存中。

接口技术

第3章 存储器技术

3.5 存储器接口技术 静态RAM:COMS RAM 62256

第3章 存储器技术

3.1存储器分类 内存和外存 从存储器与CPU信息交换的角度看,存储器可分为两大 类:内部存储器,简称为内存或主存;另一类为外部存储器, 简称为外存或辅存。内存是存放当前计算机正执行的、或者 经常要使用的程序和数据,CPU可直接从中取指令或存取数 据。而外存则存放内存的副本和当前不在运行的程序和数据, CPU要访问外存时,必须通过专门的设备将信息先传送到内 存中。

非易失性RAM(IRAM)

组合ROM CREEM

接口技术

第3章 存储器技术

3.1存储器分类 半导体存储器分类

1. RAM (1)双极型RAM。存取速度高,常常高于Cache。 (2)MOS RAM。集成度高、功耗低、价格低。有(SRAM)、 (DRAM)、组合(IRAM)和非易失性RAM(NVRAM)。 SRAM:集成度高于双极型但低于DRAM;不需要刷新电路。 DRAM:用单管线路组成,集成度高;功耗低于SRAM;价格低; 需要刷新电路;存取速度高于SRAM。 IRAM:附有刷新电路的DRAM。大容量内存一般都用IRAM。 NVRAM(Non Volatile RAM):是SRAM和EEPROM的合成体。 用来存储一些重要信息,用于掉电保护。

3.4 Cache 地址映象

由主存地址映像到Cache地址称为地址映像。 (1)直接映像法。 每个主存块只与一个缓存块相对应,映射关系:i=j mod C 其中i为缓存块数,j为主存块号,C为缓存块数,等于2c,映射的 结果表明每个缓存块对应若干个主存块。 实现简单,只需利用主存地址的某些位直接判断,即可确定所需字 块是否在缓存中。

接口技术

第3章 存储器技术

3.5 存储器接口技术 静态RAM:COMS RAM 62256

微机原理与接口技术优秀课件

存器以及存储单元都集成在一个芯片中,体积特别小 功耗低,一般为几十毫瓦(mW)

第5章 微机的存储系统

5.2 半导体存储器的基本知识

5.2.2 半导体存储器芯片的结构

地

AB 地

址

址 译 码

锁

和

存

驱

动

存储体

读写控制 CB

I/O

控 DB

制

电

路

第5章 微机的存储系统

5.2 半导体存储器的基本知识

5.2.2 半导体存储器芯片的结构

只读 可编程只读存储器PROM

存

存储器 可擦除可编程只读存储器EPROM ROM 电可擦可编程只读存储器EEPROM

储

快闪存储器Flash Memory

器

磁表面 存储器

磁盘存储器 磁带存储器

硬盘 软盘

光介质存储器

第5章 微机的存储系统

5.1 存储器概述

5.1.1 存储器的分类——按信息的可保存性分类

➢ 价格/位——常用每字节或每MB成本表示,即C=价格/容量

➢ 可靠性——通常用平均无故障工作时间(Mean Time Between Failures,简称MTBF)即两次故障之间的平均时间来衡量。

第5章 微机的存储系统

5.1 存储器概述

5.1.3 存储系统的概念

存储系统由存放程序和数据的各类存储设备及相关软件构成。

➢ 辅助存储器——又称外部存储器,主要用来存放当前暂时不 参加运算的程序和数据,通常CPU不直接访问辅存。

➢ 高速缓冲存储器(Cache)——用于弥补计算机内部各器件之间 的速度差异。主要采用双极型(TTL)半导体存储器件。

第5章 微机的存储系统

5.1 存储器概述

第5章 微机的存储系统

5.2 半导体存储器的基本知识

5.2.2 半导体存储器芯片的结构

地

AB 地

址

址 译 码

锁

和

存

驱

动

存储体

读写控制 CB

I/O

控 DB

制

电

路

第5章 微机的存储系统

5.2 半导体存储器的基本知识

5.2.2 半导体存储器芯片的结构

只读 可编程只读存储器PROM

存

存储器 可擦除可编程只读存储器EPROM ROM 电可擦可编程只读存储器EEPROM

储

快闪存储器Flash Memory

器

磁表面 存储器

磁盘存储器 磁带存储器

硬盘 软盘

光介质存储器

第5章 微机的存储系统

5.1 存储器概述

5.1.1 存储器的分类——按信息的可保存性分类

➢ 价格/位——常用每字节或每MB成本表示,即C=价格/容量

➢ 可靠性——通常用平均无故障工作时间(Mean Time Between Failures,简称MTBF)即两次故障之间的平均时间来衡量。

第5章 微机的存储系统

5.1 存储器概述

5.1.3 存储系统的概念

存储系统由存放程序和数据的各类存储设备及相关软件构成。

➢ 辅助存储器——又称外部存储器,主要用来存放当前暂时不 参加运算的程序和数据,通常CPU不直接访问辅存。

➢ 高速缓冲存储器(Cache)——用于弥补计算机内部各器件之间 的速度差异。主要采用双极型(TTL)半导体存储器件。

第5章 微机的存储系统

5.1 存储器概述

chap41微机原理与接口技术课件课件

探索系统时钟的原理及其在计算机中的作用。

时序控制

了解时序控制的概念和应用,确保计算机的正确运行。

中断控制与异常处理

中断控制

异常处理

学习中断控制的原理和处理方法,实现系统的响应能力。 了解异常处理的概念和应用,确保系统的稳定性。

总线技术及其应用

1 总线结构

2 总线应用

深入了解计算机总线的结构和工作原理。

中断控制

学习单片机中断处理和优先级设 置。

IO口设计及应用

探索IO口的设计和在单片机应用 中的应用。

操作系统基础知识介绍

1 进程管理

学习操作系统中进程的创建和管理。

2 内存管理

了解操作系统中内存的分配和回收。

3 文件系统

深入研究操作系统中文件的组织和访问方法。

微机原理与接口技术

这个课件将带您深入了解微机原理与接口技术,从基础知识到嵌入式系统的 设计和应用。

微机基础知识介绍

1

内存管理

2

深入研究内存的结构和管理,优化系统性

能。

3

CPU结构

学习CPU的架构和工作原理,理解计算机的 核心。

输入输出设备

了解各种输入输出设备的接口及其应用。

系统时钟与时序控制

时钟原理

探讨总线应用的各种场景和案例。

DMA技术及其应用

1

DMA原理

学习直接内存访问(DMA)的工作原理。

2Hale Waihona Puke DMA应用探索DMA在过程控制和数据传输中的广泛应用。

嵌入式系统概述及应用

概述

深入理解嵌入式系统的概念和应用领域。

应用

探讨嵌入式系统在各行各业中的应用案例。

单片机概述及应用

指令集介绍

了解单片机的指令集和编程原理。

时序控制

了解时序控制的概念和应用,确保计算机的正确运行。

中断控制与异常处理

中断控制

异常处理

学习中断控制的原理和处理方法,实现系统的响应能力。 了解异常处理的概念和应用,确保系统的稳定性。

总线技术及其应用

1 总线结构

2 总线应用

深入了解计算机总线的结构和工作原理。

中断控制

学习单片机中断处理和优先级设 置。

IO口设计及应用

探索IO口的设计和在单片机应用 中的应用。

操作系统基础知识介绍

1 进程管理

学习操作系统中进程的创建和管理。

2 内存管理

了解操作系统中内存的分配和回收。

3 文件系统

深入研究操作系统中文件的组织和访问方法。

微机原理与接口技术

这个课件将带您深入了解微机原理与接口技术,从基础知识到嵌入式系统的 设计和应用。

微机基础知识介绍

1

内存管理

2

深入研究内存的结构和管理,优化系统性

能。

3

CPU结构

学习CPU的架构和工作原理,理解计算机的 核心。

输入输出设备

了解各种输入输出设备的接口及其应用。

系统时钟与时序控制

时钟原理

探讨总线应用的各种场景和案例。

DMA技术及其应用

1

DMA原理

学习直接内存访问(DMA)的工作原理。

2Hale Waihona Puke DMA应用探索DMA在过程控制和数据传输中的广泛应用。

嵌入式系统概述及应用

概述

深入理解嵌入式系统的概念和应用领域。

应用

探讨嵌入式系统在各行各业中的应用案例。

单片机概述及应用

指令集介绍

了解单片机的指令集和编程原理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据流驱动的计算机结构

当指令具有所需数据、且输出端没有数据时就可执 行。

主处理机

控制通道

数据通道

磁盘存储器

高速数据总线 数据流处理机 存储器

Dataflow Image Processing System

10

2. 系统组成

主机 硬件系统

CPU 存储器 输入/输出接口 总线

外设

微机系统

系统软件

软件系统 应用软件

36

1. 无符号数的算术运算

加法运算

1+1=0(有进位)

减法运算

0-1=1(有借位)

乘法运算

除法运算

37

乘除运算例

00001011×0100

=00101100B

00001011÷0100=00000010B 即:商=00000010B

余数=11B

38

2. 无符号数的表示范围:

0 ≤ X ≤ 2n-1

[+0]反=00000000

[-0]反 =11111111 即:数0的反码也不是唯一的。

54

补码

定义:

若X>0, 则[X]补= [X]反= [X]原

若X<0, 则[X]补= [X]反+1

55

[例]

X= – 52= – 0110100

[X]原=10110100 [X]反=11001011 [X]补= [X]反+1=11001100

程序存储,共享数据,顺序执行 属于顺序处理机,适合于确定的算法和数值数据的 处理。 与存储器间有大量数据交互,对总线要求很高; 执行顺序有程序决定,对大型复杂任务较困难; 以运算器为核心,处理效率较低; 由PC控制执行顺序,难以进行真正的并行处理。

9

不足:

典型的非冯 • 诺依曼机结构

算术运算和逻辑运算 运算中的溢出

ቤተ መጻሕፍቲ ባይዱ

机器数的表示及运算 基本逻辑门及译码器

3

一、微型计算机系统

微型机的工作原理 微机系统的基本组成

4

存储程序原理

将计算过程描述为由许多条指令按一定顺序组 成的程序,并放入存储器保存

指令按其在存储器中存放的顺序执行;

由控制器控制整个程序和数据的存取以及程序 的执行。

偶校验

加上校验位后 编码中‚1‛的个数为偶数。

上例若以偶校验传送,则为 41H。

34

三、无符号二进制数的运算

算术运算

无符号数 二进 制数的运算 有符号数

35

逻辑运算

主要内容

无符号二进 制数的算术运算

无符号数的表达范围 运算中的溢出问题 无符号数的逻辑运算 基本逻辑门和译码器

• • • •

A

Y7

45

三、机器数(有符号数)的运算

46

计算机中符号数的表示

机器数

计算机中的数据

构成:

符号位 + 真值

“ 0” “ 1”

表示正 表示负

47

[例]

+52 = +0110100 = 0 0110100

符号位 真值

-52 = -0110100 = 1 0110100

符号位

真值

17

内存储器的分类

随机存取存储器(RAM)

按工作方 式可分为

只读存储器(ROM)

18

输入/输出接口

接口是CPU与外部设备间的桥梁

CPU

I/O

接口

外 设

19

接口的分类

串行接口 并行接口 数字接口 输入接口

输出接口

模拟接口

20

接口的功能

数据缓冲寄存; 信号电平或类型的转换;

实现主机与外设间的运行匹配。

B

32

ASCII码

西文 字符的编码,一般用7位二进 制码表示。

D7位为校验位,默认情况下为0。

要求:

理解校验位的作用 熟悉0---F的ASCII码

33

ASCII码的奇偶校验

奇校验

加上校验位后编码中‚1‛的个数为奇数。 例:A的ASCII码是41H(1000001B)

以奇校验传送则为 C1H(11000001B)

21

软件系统

软件:

为运行、管理和维护计算机系统或为实现某一功能 而编写的各种程序的总和及其相关资料。 操作系统 编译系统 网络系统 工具软件

系统软件

软件

应用软件

22

二、计算机中的数制和编码

数制和编码的表示 各种计数制之间的相互转换

23

1. 常用计数法

十进制(D) 二进制(B) 十六进制(H)

58

符号数的表示范围

对8位二进制数:

原码: -127 ~ +127

反码: -127 ~ +127 补码: -128 ~ +127

59

2. 符号二进制数与十进制的转换

对用补码表示的二进制数:

1)求出真值

2)进行转换

60

[例]:补码数转换为十进制数

[X]补=0 0101110B

正数

所以:真值=0101110B X=+46

-0=1 0000000 即:数0的原码不唯一。

51

反码

对一个机器数X:

若X>0 ,则 [X]反=[X]原

若X<0, 则 [X]反= 对应原码的符号位不变, 数值部分按位求反

52

[例]

X= -52 = -0110100

[X]原=1 0110100

[X]反=1 1001011

53

0的反码:

11

微处理器

微处理器简称CPU,是计算机的核心。

主要包括: 运算器 控制器

寄存器组

12

存储器

定义:

用于存放计算机工作过程中需要操作的数据 和程序。

13

有关内存储器的几个概念

内存单元的地址和内容 内存容量

内存的操作

内存的分类

14

内存单元的地址和内容

内存按单元组织 每单元都对应一个地址,以方便对单元的寻址

若运算结果超出这个范围,则产生溢出。

对无符号数:运算时,当最高位向更高位 有进位(或借位)时则产生 溢出。

39

[例]:

最高位向前有进位,产生溢出

40

3. 逻辑运算

与、或、非、异或 掌握:

与、或、非门逻辑符号和逻辑关系(真值表);

与非门、或非门的应用。

41

“与”、“或”运算

‚与‛运算:

56

0的补码:

[+0]补= [+0]原=00000000

[-0]补= [-0]反+1=11111111+1

=1 00000000

对8位字长,进位被舍掉

57

特殊数10000000

对无符号数:(10000000)B=128

在原码中定义为: -0

在反码中定义为: -127

在补码中定义为: -128

单元内容

38F04H

内存地址

10110110

15

内存容量

内存容量:

所含存储单元的个数,以字节为单位

内存容量的大小依CPU的寻址能力而定

实地址模式下为CPU地址信号线的位数

16

内存操作

读:

将内存单元的内容取入CPU,原单元内容不改变;

写:

CPU将信息放入内存单元,单元中原来的内容被覆盖。

次高位向最高位有进位,而最高位向前无进位,产生 溢出。 (事实上,两正数相加得出负数,结果出错)

65

结束语:

第1章难点:

补码的概念及其运算

66

第2章

微处理器与总线

67

主要内容:

微处理器的功能和结构

8088/8086微处理器

特点

主要引线功能和内部结构

内部寄存器 实地址模式下的存储器寻址 总线时序

68

总线

一、微处理器及8088/8086CPU

69

1. 微处理器

运算器 微处理器 控制器 内部寄存器

70

2. 程序和指令

程序:

具有一定功能的指令的有序集合

指令:

由人向计算机发出的、能够为计算机所识别的命令。

71

3. 指令执行的一般过程

取指令 指令译码 读取操作数

执行指令

存放结果

取指部件,分析部件,执行部件

5

冯 • 诺依曼计算机体系结构

存储器

输入设备

运算器

输出设备

控制器

6

冯 • 诺依曼机的工作过程

内存中的程序 CPU 取出 指令1 指令2 分析 获取操作数 执行 存放结果

程序计 数器PC

地址

┇

指令n

┇

操作数

7

冯 • 诺依曼机的工作过程

取一条指令的工作过程:

将指令所在地址赋给程序计数器PC; PC内容送到地址寄存器AR,PC自动加1; 把AR的内容通过地址总线送至内存储器,经地址译码器译码, 选中相应单元。