基于FPGA的FIR滤波器的程序设计(8阶)

基于FPGA的FIR滤波器的设计

MATI AB 的 功 能 和 Smuik块 与 Al r i l n t a的 DS e P

Bie ul r块 和 Al r d t a的 知 识 产 权 (P Me a oe功 能 e I ) gC r

使 用 D P器件 实现 虽然 简单 ,但 由于程序顺 序 执行 , S

执行 速度较 慢 。随着 数字 技术 的应 用 日益 广泛 ,以现

基 于 F GA 的 F昕

( 京 科 技 大 学 ,北 京 1 0 8 ) 北 0 0 3

摘 要 : 介 绍 有 限 脉 冲 响 应 ( I 数 字 滤波 器理 论 及 常 见 实 现 方 法 的基 础 上 , 出 了 一 种基 于 F GA 的高 效 实 在 F R) 提 P 现 方 案 。 方 案 借 助 F GA 滤 波 器 芯 片 和 Qu ru I 件 、 PB i e 软 件 对 该 方 案 进 行 了 仿 真 验 证 。 真 该 P atsI 软 DS ul r d 仿 实 验结 果 表 明 : 种 F R 滤波 器 的实 现 方 法 运 算 速 度 快 、 时性 好 , 性 能 优 于 传 统 的 F R滤 波 器 设 计方 法 。 此 I 实 其 I

些。

2 F R滤波 器 的设计 方法 I

目前 F R滤 波器 的实现 方法 有 3 , 别利 用单 I 种 分

片通 用数字 滤波 器集 成 电路 、D P器 件或 可编程 逻辑 S

器件 实现 。 片通 用数 字滤 波器集 成 电路使 用方便 , 单 但 由于字 长和 阶数 的规格 较少 , 能完全 满足 实际需要 。 不

迅 速 普及 和 发展 ,器件 集 成 度 和速 度 都 在高 速增 长 F GA 既具有 门阵列 的高逻辑 密 度和 高可靠 性 ,又具 P

基于FPGA与Matlab的最优FIR数字滤波器设计

图 1 直 接 l F R 滤 波 器 结 构 型 I

- 4

从 滤波器的系统函数可知它是恒稳定 的, 需要反馈 , 不 只要 加 权

.

∞

| 。

: : \

系 数 hi hN 1 i0 ≤N一 ) I (= (一 一) ≤i ) ( 1, R滤 波 器 就具 有 严格 的线 性 相 位 。一 F 般 而 言, 常用 的 FR滤 波 器 是线 性 相 位 的 , 滤 波 器 的 系 数 满 足某 种对 I 即

三 、 R 滤 波器 的 F FI PGA设 计 与 实 现

曲 ∑ ( ) : 一

其 中 xng 输 入 采 样 序 列 ,(是 滤 波 器 系 数 , () hi ) L是 滤 波 器 的 系 数 长度 ,() 示 滤 波器 的 输 出 序 列 。也 可 以用 卷 积 来 表示 输 出序 列 y ) y 表 n ( n 与 xn、( 的关 系 。 ( hn ) )

^p I 目 ,l i奢 l 31参数 提取 设 计 指 标 如下 : . 通 带 类 型: 陷波 通 带衰 减 :.1 B O0d 采 样频 率:.k z 75 h 通 带 边 频率 1 7 kz和 215 h . 5h 5 .7 k z

陷 波 频率 :.7 k z 1 5h 8 阶 数: 8 6

102 3 0 2)

要 】I 滤波器是一种被广泛应用的基本 的数字信号处理部件, FR 针对常用的软 、 硬件方法设计实现 FR 滤波器存在 的问题, 出采用 I 提

M a小 的 切 比 雪 夫等 波 纹 逼 近 方 法. 计 并 在 F GA 上 高速 并 行 实现, 格 线性 相 位 FR 滤 波 器 的 方案 。 d 设 P 严 I

滤 波 器设 计 工 具 箱 (l r eintobx 。faol 以设 计 几 乎所 有 的 ied g o ft s lo ) dt 可 基 本 的 常规 滤 波 器 , 括 缶 和 . 的 各 种 设计 方 法 。它 操 作 简 单 , 便 包 i r 方 灵活。

基于FPGA的FIR滤波器设计

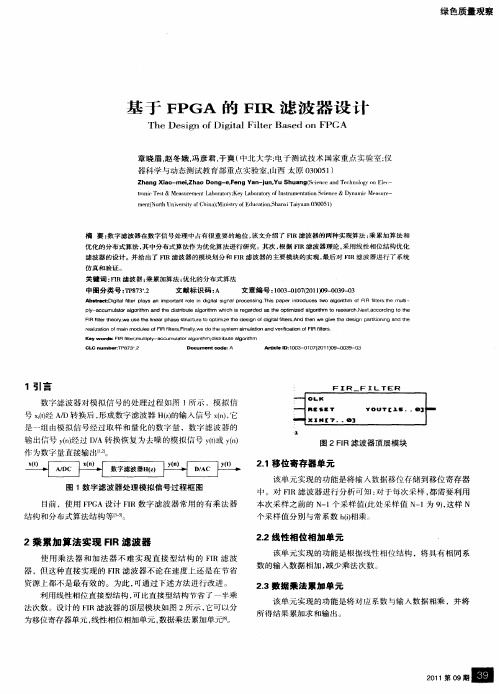

该单元 实现 的功能是将输人数据 移位 存储到移位寄存器

中 。对 FR滤 波 器 进 行 分 析 可 知 : 于 每 次 采 样 , 需 要 利 用 I 对 都 本 次 采 样 之 前 的 N 1 采 样 值 ( 处 采样 值 N 1 9, 样 N 一个 此 一 为 )这

号 xt AD转换后 , 成数 字滤波 器 Hz的输入信 号 x )它 经 / ( ) 形 ( ) (, n

是 一 组 由模 拟 信 号 经过 取 样 和 量 化 的数 字 量 ,数 字 滤 波 器 的

1

输 出信号 y ) ( 经过 DA转换恢 复为去噪的模拟信号 y) yn n / (或 () t

r l a i f an m o ls o I I r ial , e ( h y tm i uat n a d v ii in o I ie s eai t z on o i due fF R t s Fn l w m e y 3 t e s se sm I i n er c o fF R ft r o o f at l a g i m ; srb t l r h l orh ditiu e ago i m t t

me t ot iesto hn) nsq o u ain h n i aya 30 1 n( rhUnvri f ia; i ,f ct , ax i n0 0 5 ) N y C Mi t Ed oS T u

摘 要: 数字 滤波 器在数 字信 号处理 中占有很 重要 的地位 , 该文介 绍 了 FR滤 波 器的两种 实 现算法 : I 乘累 加算 法和

Zh n a me,h o Do g- ,e g Ya j nYuSh ngs’ feadT cn lg nEe— a gXio- i a n eF n n-u , ua (( l n eh o y lc Z i c P o 0

基于FPGA乘法器的FIR滤波器系统设计

基于FPGA乘法器的FIR滤波器系统设计FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据设计者的需求和要求进行编程,实现各种数字电路功能。

FIR (Finite Impulse Response)滤波器是一种常用的数字滤波器,其特点是能够对输入信号的有限长度的响应进行滤波处理。

本文将介绍基于FPGA乘法器的FIR滤波器系统设计。

首先,介绍FIR滤波器的原理。

FIR滤波器是一种线性时不变系统,其输出信号由输入信号的加权和组成。

FIR滤波器的输入经过一串系数的加权运算后,得到滤波器的输出。

FIR滤波器的传输函数为:H(z) = b0 + b1*z^(-1) + b2*z^(-2) + ... + bn*z^(-n)其中,bi是滤波器的系数,n是滤波器的阶数,z为单位延迟。

FIR 滤波器的输出信号可以表示为:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)其中,x是输入信号,y是输出信号。

FIR滤波器的阶数决定了滤波器的性能,阶数越高,滤波器的频率响应越陡峭。

接下来,介绍基于FPGA乘法器的FIR滤波器系统设计。

FPGA乘法器是FPGA中的一种硬件资源,通常用于实现乘法运算。

FPGA乘法器的乘法操作可以并行地执行,可以大大提高FIR滤波器的运算速度。

在设计基于FPGA乘法器的FIR滤波器系统时,首先需要确定FIR滤波器的阶数和系数。

根据滤波器的需求,可以选择不同的阶数和系数。

然后,根据FIR滤波器的传输函数,可以将其转化为差分方程形式。

差分方程形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)然后,将差分方程形式转化为数据流形式。

数据流形式中的每一步计算只涉及到少量的数据,可以并行地执行。

数据流形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(0)接下来,需要将数据流形式转化为硬件电路。

基于FPGA的FIR滤波器设计

基于FPGA 的FIR 滤波器设计一 、设计目的为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《《FPGA 系统设计与应用》几门课程融合在一起开设的FPGA 综合实验课程设计。

本次完成的是利用FPGA 来完成FIR 滤波器的设计、程序设计和实验调试任务。

二、设计要求(1)基本要求利用所学知识,采用VHDL 语言完成FIR 滤波器的设计仿真。

要求用VHDL 编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MATLAB 和QUARTUSII 两种仿真)并对其结果比较。

具体设计指标如下: (1)采样频率S F =80KHz ;(2)截止频率KHz F C 10=;(3)输入序列为10位(最高位为符号位); (4)窗口类型为kaiser 窗,β=0.5 ; (5)滤波器长度为16 ; (6)输出结果保留10位。

(2)提高部分根据所学知识,设计出一个具有频率控制功能DDS ,要求输出频率分别为10KHz 和100KHz ,将输出的两路数字信号进行叠加,并通过所设计的FIR 滤波器进行滤波,将滤波输出的数字信号通过D/A 转换电路输出波形,并用示波器观察输出波形,并完成测试结果分析。

结构框图如图1-1所示。

图2-1 整体结构框图三、设计原理3.1 FIR 滤波器由线性系统理论可知,在某种适度条件下,输入到线性系统的一个冲击完全可以表征系统。

当我们处理有限的离散数据时,线形系统的响应(包括对冲击的响应)也是有限的。

若线性系统仅是一个空间滤波器,则通过简单地观察它对冲击的响应,我们就可以完全确定该滤波器。

通过这种方式确定的滤波器称为有限冲击响应(FIR)滤波器。

3.2 线性FIR 滤波器原理FIR 滤波器响应(简称FIR )系统的单位脉冲响应()h n 为有限长序列,系统函数()H z 在有限z 平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。

基于FPGA的FIR数字滤波器设计与实现

基于FPGA的FIR数字滤波器设计与实现作者:单文军周雪纯李文华来源:《现代电子技术》2013年第14期摘要:简要介绍了FIR数字滤波器的结构特点和基本原理,提出基于FPGA和DSP Builder的FIR数字滤波器的基本设计流程和实现方案。

在Matlab/Simulink环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明其数字滤波器的滤波效果良好。

通过SignalCompiler把模型转换成VHDL语言加入到FPGA的硬件设计中,从QuartusⅡ软件中的虚拟逻辑分析工具SignalTapⅡ中得到数字滤波器实时的结果波形图,结果符合预期。

关键词: FPGA; DSP Builder; FIR数字滤波器; ModelSim功能仿真中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)14⁃0123⁃04Design and implementation of FIR digital filter based on FPGASHAN Wen⁃jun, ZHOU Xue⁃chun, LI Wen⁃hua(China Flight Test Establishment,Xi’an 710089, China)Abstract: The structure feature and the basic principle of FIR digital filter is introduced briefly. The basic design process and implementation scheme of the FIR digital filter based on FPGA and DSP Builder is proposed in this paper. FIR model is structured with DSP Builder module in the Matlab/Simulink environment. The FIR digital filter is designed according to the FDATool. The system level simulation and ModelSim function simulation were completed. The simulation results show that the filter has excellent effect. The model is converted to VHDL language through SingalCompiler and added to FPGA hardware design. The real⁃time waveform graph of the FIR digital filter was received by the virtual logic analysis tool SignalTapⅡ in QuartusⅡ. The results conform to the expected requirement.Keywords: FPGA; DSP Builder; FIR digital filter; ModelSim function simulation在信息信号处理过程中,数字滤波器是信号处理中使用最广泛的一种方法。

基于FPGA的FIR数字滤波器的设计与实现

基于FPGA的FIR数字滤波器的设计与实现作者:杨国庆来源:《现代电子技术》2008年第19期摘要:介绍了基于FPGA的FIR数字滤波器的设计与实现,该设计利用Matlab工具箱设计窗函数计算FIR滤波器系数,并通过VHDL层次化设计方法,同时FPGA与单片机有机结合,采用C51及VHDL语言模块化的设计思想及进行优化编程,有效实现了键盘可设置参数及LCD显示。

结果表明此实现结构能进一步完善数据的快速处理和有效控制,提高了设计的灵活性、可靠性和功能的可扩展性。

关键词:FPGA;滤波器;VHDL;窗函数;模块化;可扩展性中图分类号:TN713文献标识码:B文章编号:1004373X(2008)1918403Design and Realization of FIR Digital Filter Based on FPGAYANG Guoqing(Tianjin Institute of Urban Construction,Tianjin,300384,China)Abstract:This paper introduces a design and realization of FIR digital filter based on FPGA.The design uses window function of Matlab toolbox to calculate FIR filter coefficient.Through VHDL level of design,FPGA and MCU organic integration,C51 and VHDL used modular design and optimize programming,the effective realization of the keyboard can also set the parameters and LCD display,the results show that this structure can be further improved to achieve the rapid data processing and effective control,the design flexibility,reliability and extendibility function are improved as well.Keywords:FPGA; filter;VHDL;window function;modulization;extendibility1 引言数字滤波是通信、语音与图像处理、模式识别和谱分析等应用中的一种基本的处理部件,它可以满足滤波器对幅度和相位特性的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。

基于FPGA的FIR滤波器设计与仿真

数字滤波器; 分布 式 算 法 ;P A FG 中图分 类 号 T 3 1 P 1 文 献标 志 码 A

滤波器需 要执行 无 限数量 卷 积 , 能得 到较 好 的 幅度特性 , 相位 特性 其 是非线性 的 ; I 波器 由有 限个 采样 值 组 成 , 构 成 的系 统总 是稳 FR滤 其 定 的 , 易于实现 线性相 位 …. 且 由于 在语音 信 号处 理 、 图像 处理 、 数字 通信等传 输过程 中不能有 明显 的相位失真 , FR滤波器在 满足一定 而 I 对称条件 下可 以实现 I I R滤波器 难 以实 现 的线 性相 位 , 因而得 到广泛

特 别适合如 FR、丌 等数 字信号处 理任务 . I F 利用 F G P A可 以重 复配置 高精 度的 FR滤波器 , 用 V D I 使 H L硬件 描述语 言改变滤 波器 的系数和

阶数 , 能实 现大 量 的卷 积运 算算 法 J 结合 M xls 具软 件 的辅 并 . apu 工

案速 度 快 、 时性 好 、 省 硬 件 资 源 , 实 节 具 有重 要 的 工程 应 用价 值 . 关 键 词

实 现数字化 是 控 制 系统 的重 要发 展 方 向 , 而数 字 信 号处 理 已在

通信 、 语音 、 图像 、 自动控 制 、 达 、 事 、 空 航 天等 领 域 广 泛应 用 . 雷 军 航 数 字信号 处 理 方 法 通 常 涉 及 变 换 、 波 、 谱 分 析 、 码 解 码 等 处 滤 频 编 理¨. 数字滤 波是数 字信号处 理重 要 环节 , 它能 满 足滤 波器 对幅度 和 相 位特性 的严格 要 求 , 克服 模 拟 滤 波器 所 无 法解 决 的 电压 和 温度 漂 移 以及噪声 等 问题 , 而有 限冲激 响应 FR滤 波器在设计 任意 幅频 特性 I 的同时能够保证 严格 的线性相 位特性 . 数 字滤波器 根 据其 冲激 响应 函数 的 时域 特性 , 分 为无 限 长 冲 可

基于FPGA的FIR数字滤波器设计概要

基于FPGA的FIR数字滤波器设计摘要:文章介绍了CSD编码和流水线技术,将它们运用到VHDL语言编程中,设计了一个16阶8位输入17位输出的线性相位结构FIR数字滤波器,仿真结果符合要求。

最后比较了两种方法的使用在硬件资源和系统处理速度上的优缺点。

有限冲激响应(FIR数字滤波器和无限冲激响应(IIR数字滤波器广泛应用于数字信号处理系统中。

IIR数字滤波器方便简单,但它相位的非线性,要求采用全通网络进行相位校正,且稳定性难以保障。

FIR滤波器具有很好的线性相位特性,使得它越来越受到广泛的重视。

This article introduces CSD coding and production line technique, will they use to VHDL language programming, design of a 16th order 8-bit input 17 output of linear phase FIR digital filters, structural simulation results accord with the requirement. Last two methods were compared, the use of the system hardware resources and processing speed on the advantages and disadvantages. Finite impulse response (FIR digital filters and infinite impulse response (IIR digital filters widely used in digital signal processing system. IIR digital filter convenience simple, but it phase of the nonlinear requirements adopts full ventilation network phase calibration, and stability difficulty safeguards. FIR filters have very good linear phase characteristic, making it more and more extensive attention.关键词:FIR数字滤波器;线性相位;CSD编码;流水线技术1.引言数字滤波在图像处理、语音识别和模式识别等数字信号处理中占有重要地位。

基于FPGA的FIR滤波器的设计

0 引 言

在现代 信号 处理 和 电子 应用 技 术 领 域 , 统 的设 系 计 正朝 着高 速 、 时 的方 向发展 。而 滤波 器 主 要 作 为 实 系统 的前端 部分 , 信 号 进行 预 处 理 。滤 波 性 能 的优 对

劣直接 影响 着下一 级 的信号 处理 , 因此 , 性能 的滤 波 高 器在 系统 中 占据着 重要 位 置 。 F R滤波器 由于具有严 格 的线性 相位 特性 以及 易 I 于实 现等 特 点 在 数 字 信 号 处 理 中被 广 泛 应 用 。 目前 F R滤波 器 主要有 三种实 现 方式 l : I _ 第一 种 , 用 DS 1 ] 采 P

中图分类号 : 73 TN 1 文 献标 识码 : B

De in o I F l rBa e n F sg fF R i e s d o PGA t

ZHENG h n — i g Z e gbn

( pt o e t o i En i e r g,S a x i e s t fTe h o o y,Ha z o g 7 3 0 , h n ) De . fEl cr n c gn ei n hni Un v r i o c n l g y n h n 2 0 3 C ia

fr a c n s ad r eo re a eti rci blyo rjcs Or nea dl s rwae sucsh scra pat a it f oet. n e h r n c i p

Ke r s PGA ; R i e ; y wo d :F FI f t r VHDL; l DA l o ih a g rt m

维普资讯

—

—

_

2 8 月2 日 5 笙一 0 年5 5 第2卷 3 0  ̄ 一

基于FPGA的FIR滤波器设计

—

s j — q u a n 一 1 2 =r o u n d ( s j/ m a x ( s j ) ) ( 2 ( b i n l o n g 一 1 ) 一

1 ) ) :

量化 完 成 后 , 还 需 要把 参 数 写成 文 件 , 等待 F P G A的调 用 。 M A T L A B中把测 试文 件写 成文 件如 下 :

f i d o u t = f o p e n( ’ r e s u l t . t x t ’ , ’ w ’ ) : % o p e n r e s u l t f i l e

an d wai t f o r wri t e

1 基本流 程

一

f o r i = l : l e n g t h ( s jq u a n 一 1 2 )

2 1 5 0 0 6;

摘 要 介 绍 了基 于 F P G A芯片进 行 F I R 滤 波 器的设 计过 程 , 具体 涉及 到 M A T L A B 对F I R滤波 器 的仿真 、数据 的量化 和 生成 ; F P G A对 F I R滤 波器 的设 计 、仿真 和数 据 生成 , 最后 形 成 F P G A和 M A T L A B 联 合设 计 F I R滤 波器 。 关键词 F G P A; F I R; M A T L A B 中图 分类 号 : T N 9 1 1 文 献标 识码 : A 文 章编 号 : 1 6 7 1 — 7 5 9 7( 2 0 1 4 )0 3 — 0 0 3 4 - 0 1

w n: 表 示滤 波器 的截 至频 率 。

P O R T(

rs t :I N s t d

基于fpga的滤波器设计与实现

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的一种工具,它可以通过剔除或增强信号中的特定频率分量来改变信号的特性。

而基于FPGA的滤波器是一种利用可编程逻辑器件FPGA来实现滤波功能的方法。

本文将介绍基于FPGA的滤波器的设计与实现过程。

二、滤波器的基本原理滤波器主要通过改变信号的频谱特征来实现滤波效果。

它可以分为两类:低通滤波器和高通滤波器。

低通滤波器通过剔除高频分量,保留低频分量;高通滤波器则相反,剔除低频分量,保留高频分量。

滤波器的设计需要根据具体的需求选择合适的滤波器类型和参数。

三、基于FPGA的滤波器设计与实现基于FPGA的滤波器设计与实现可以分为以下几个步骤:1. 确定滤波器类型和参数:根据实际需求,选择合适的滤波器类型和参数。

例如,如果需要设计一个低通滤波器,需要确定截止频率和滤波器阶数等参数。

2. 数字滤波器设计:将滤波器的模拟设计转化为数字滤波器的设计。

常见的数字滤波器设计方法有FIR滤波器设计和IIR滤波器设计。

FIR滤波器是一种无反馈的滤波器,具有线性相位特性;IIR滤波器则具有反馈结构,可以实现更高阶的滤波器。

3. 将数字滤波器转化为FPGA可实现的结构:将数字滤波器转化为FPGA可实现的结构,可以采用直接形式实现、级联形式实现或者管线化实现等方法。

其中,直接形式实现是最简单直观的方法,但其硬件资源占用较多;级联形式实现可以减少硬件资源的占用,但增加了延迟;管线化实现则可以兼顾硬件资源和延迟。

4. 使用HDL语言进行FPGA设计:使用HDL语言,如VHDL或Verilog,进行FPGA设计。

根据设计的结构和功能,编写相应的HDL代码。

在编写代码时,需要注意代码的可重用性和可维护性,以便后续的设计和调试。

5. 硬件验证和性能优化:完成HDL代码后,进行FPGA的硬件验证和性能优化。

通过仿真和验证,确保设计的正确性和稳定性。

同时,可以根据实际需求对硬件进行优化,如减小资源占用、降低功耗等。

FPGA实现FIR抽取滤波器的设计

FPGA实现FIR抽取滤波器的设计之蔡仲巾千创作FIR(fini te impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在包管任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,系统稳定。

因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

在工程实践中,往往要求对信号处理要有实时性和灵活性,而已有的一些软件和硬件实现方式则难以同时达到这两方面的要求。

随着可编程逻辑器件的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采取FPGA器件来实现FIR滤波器。

1 FIR滤波器工作原理在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不管采取乘累加方法还是分布式算法设计FIR 滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。

FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

2 16阶滤波器结构在滤波过程中实现抽取,对于抽取率为N的抽取滤波器而言,当进来N个数据时滤波器完成1次滤波运算,输出1次滤波结果。

抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。

在数字系统中采取拙取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。

采样数据与滤波器系数在控制电路的作用下,分别对应相乘并与前一个乘积累加,经过多次(有多少阶就要多少次)反复的乘累加最后输出滤波结果,将相同系数归类,16阶滤波器公式:乘法器的数量减少一半,但加法器的数量增多了,但相对乘法运算来说,加法运算所占用的资源少的多,运算的速度也快得多。

基于FPGA的FIR数字滤波器的设计和实现

基于FPGA的FIR数字滤波器的设计和实现摘要:本文基于FPGA平台实现了一种FIR数字滤波器,通过对滤波器的设计与实现过程的详细介绍,展示了FPGA在数字滤波器中的应用优势。

首先介绍了数字滤波器的原理及其在信号处理中的重要性,并对FPGA及其特点进行了概述。

接着,详细介绍了FIR滤波器的原理以及其在FPGA上的实现步骤,分析了滤波器设计中需要考虑到的各种因素。

最后,通过实验验证了FPGA上实现的FIR滤波器的性能,并对优化策略进行了讨论。

关键词:FPGA,FIR滤波器,数字信号处理,性能优化1. 引言数字滤波器是现代信号处理的重要组成部分,通过选择性地传递或抑制输入信号的特定频率组成部分,对信号进行处理和改善。

FIR滤波器是数字滤波器中最常用的一种类型,具有线性相位特性、稳定性较强以及易于实现等优势。

而FPGA作为一种可编程逻辑器件,具有灵活性高、可重构性强等特点,成为实现数字滤波器的理想平台。

2. FIR滤波器的原理FIR滤波器是一种线性时不变系统,其输出仅和当前输入值以及过去若干个输入值有关。

该滤波器的输出可以通过输入信号的线性加权和来计算,其中,每个输入值的加权系数通过FIR 滤波器的系数来确定。

FIR滤波器的系数决定了它对不同频率分量的响应,从而实现了信号的滤波目的。

3. FIR滤波器在FPGA上的实现步骤(1)选择合适的FPGA平台和开发工具,如Xilinx FPGA平台和Vivado开发工具。

(2)根据所要设计的滤波器的需求,确定其采样频率、截止频率和滤波器类型等参数,并进行系统级设计。

(3)根据所选参数,设计FIR滤波器的传递函数,并确定滤波器的阶数和系数。

(4)通过数学运算或者通过滤波器设计软件生成滤波器的差分方程。

(5)根据生成的差分方程,使用HDL(HardwareDescription Language)进行滤波器的编写。

(6)进行FPGA的综合、布局与布线、下载与验证,完成滤波器的硬件实现。

一种基于FPGA的分布式FIR数字滤波器设计

i m F R p s ii f t scr u t o x mp e t i e n i h o g f h U r h o I lw a sd gt l r ic i fre a l ,i lme t n t r u h o e L T,a d r n h h f rg s r F — t f o l ai e s mp o t d e dt e s i e it . i a t e n n h it b td a g rt m i lt d n h e ut h w t a e o t l tu t r al f ciey a p id i i l s a y t e d s u e l o h i s i r i s mu ae ,a d t e rs l s o h t h p i s t ma sr cu ec l ef t l p l n w r e s e v e e sain dg t in r c s ig mo u e tt ii s a p o e sn d l ,w i h h s u e il r g a o l a gl h c a s d o F ed P o r mma l t ra a d r e o r e f c iey f b e Gae A r y h r wae r s u c s ef t l e v

基于FPGA的FIR滤波器系统的设计

针对 F R滤 波器 电路 系 统 , 计 了一个 与 之 I 设 专 门配套 的 串 口通 信 软 件 , 软件 能 读 取 串 口数 该 据 , 把 串 口数 据保 存在 以 D T为 后 缀名 的文 件 并 A

个滤 波 系数 , 这些 滤波 系数 来 生成 FR低 通滤 用 I

波器 。

2 FR滤波器 系统硬 件设计 I

F r f r ,% 1. fn ,of) pi ( d ’ 60\ ’ce ; n i

FR滤波器 硬件 电路 主要 由 A D转换 器 、 P I / F—

F l e r ) c s( d ; o i

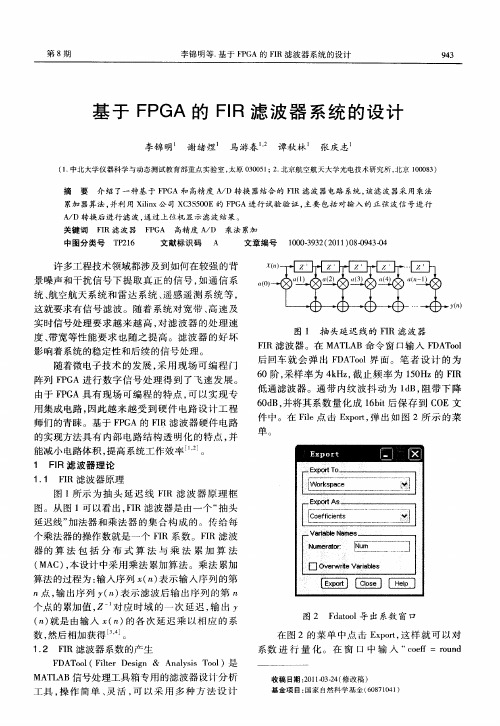

图 2 F a o 导 出 系数 窗 口 dt l o

在 图 2的 菜单 中 点击 E p r 这 样 就 可 以对 x ot , 系 数 进 行 量 化 。 在 窗 口 中 输 入 “ of ce f=ru d o n

1 2 FR滤波器 系数 的产 生 。 I

F A ol Fl r D s n & A a s ro )是 D T o ( ie ei t g nl i r 1 ys 0

正弦信号进行 A D转换 , / 然后送至 F G P A内部进

一

步处 理 。本 设 计 中采 用 了 A D公 司 的 高性 能

A D转 换 芯 片 A 7 9 , D 6 1每 秒 可 采 样 2 / D 6 1 A 79 5 万 次具有 1 bt 8 i的线性度 ,8位 的串行 数据 输 出 , l 采用 2 7 . V或 5 V单 电源 供 电。与 A I 司推 出 D公 l i 6b t和 1 i 单 端 到 差 分 A C 驱 动 器 8 bt的 D A A 9 11配 合 使 用 , D 4 4 — D 44 - A A 9 11与 A 7 9 D 6 1的 外 围电路连 接 如 图 4 5所 示 , D 4 4 — 、 A A 9 11是一 款 低功耗 、 噪声 差分 驱 动器 。它 采 用易 于 使用 的 低

基于FPGA的心电FIR滤波器的设计

X(n1

r1

Z1

r‘

r

h( o)

h( 1)

h( 2 )

t

',

J

y( n )

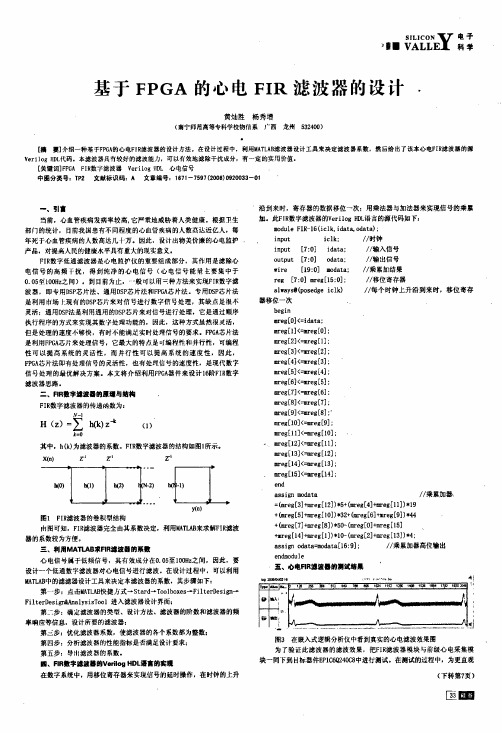

图l FI R滤波器的卷积型结构

由图可知.FI R滤波器完全由其系数决定,利用MATLAB来求解FI R滤波

器的系数较 为方便。

三、利用MATI AB求FI R滤波器的系t

心电信号属于低频信号,其有效成分在0 .05 至l OOHz之间.因此.要

在 字系统中,用移位寄存器来实现信号的延时操作,在时钟的上升

沿到来时,寄存器的数据移位一次:用乘法器与加法器来实现信号的乘累

加。此FI R数字滤波器的Ve r i l og HDL语言的源 代码如下:

modu l e FI R一16( i clk,i data, odat a) ;

i nput

i c l k:

0.0 5至l OOHz 之间) 。到目前为止,一般可以用i 种方法来实现FI R数字滤

波器,即专用DSP芯片法、通用DSP芯片法和FPGA芯片法。专用DSP芯片法

是 利用 市场 卜. 现有 的 DSP芯 片来 对 信号 进行 数字 信号 处 理, 其缺 点是 很不

灵活;通用DSP法是利用通用的DSP芯片来对信号进行处理。它是通过顺序

设计一个低通数字滤波器对心电信号进行工 具来决 定本 滤波器 的系 数, 其步骤 如下 :

第一步:点击MATLAB快捷方式一s t ar d—T001 box es—Fi I t er Des i gn—

Fi l t e r Oesi gr “t Anal ysi sTool 进入滤 波器设计界 面;

信号处理的最优解决方案。本文将介绍利用FPGA器件来设计16 阶FI R数字

基于FPGA的系数可调FIR滤波器设计

l e a j s bec e ce t w r u o f ce t a j sme t i du t l o f ins eep t r ad d pi o f ins du t n n ie tc e ins du t n.Ad p n a i f v i i a—

so e c e ce t , a he c n tt ts o f ce t lo — p t b e mo e s Th a r s f l o u a l i h n e t t r o f i n s nd t n o siu e c e i n s o k u a l d l. i i e dd e s o o k— p t be s c a g d o a a tt e d fe e tfle e u ss I h spa e ,af u — r e le d l t o rfle o e te s d sg e d p h ifr n trr q e t. n t i p r o ro d rf trmo e h f u trpr p riswa e in d i i wi i

Ab ta t sr c :Ac odn ot edf rn ii l in l rc sigrq et wokn so einp oe t o I l r t n c rigt h iee t gt g a o e s e u s,t id fd s rjcs fF R ft ho — f d as p n g i e wi

陈 虹 , 崔 葛瑾

( 东华 大学 信 息科 学与 技术 学 院 , 上海 205 ) 00 1

摘 要 : 据 不 同的数 字信 号 处理要 求 , 出了两种 滤波 系数 在 线 实时调 整 FR 滤波 器 的设 计 方 案 : 根 提 I 自 适应调 整 和直接 设 定调整 。 滤波 系数 自适应 调整 利 用控 制 算 法对 滤波 器的 实 际输 出信 号和期 望信 号的

fir滤波器 阶数设计

fir滤波器阶数设计fir滤波器阶数设计一、引言在信号处理中,滤波器是一种常用的工具,它能够通过滤除不需要的频率成分来改善信号质量。

而fir滤波器是一种常见的数字滤波器,其特点是具有线性相位和稳定性,因此被广泛应用于音频处理、图像处理等领域。

本文将探讨fir滤波器中阶数的设计问题。

二、fir滤波器简介fir滤波器是一种非递归滤波器,其输出仅依赖于输入信号的当前和过去的样本。

fir滤波器的频率响应可以通过其阶数来控制。

阶数越高,滤波器的频率特性越陡峭,滤波器的截止频率越精确。

因此,阶数的选择是fir滤波器设计中的重要问题。

三、阶数设计方法1. 理论法理论法是fir滤波器阶数设计中常用的方法之一。

根据滤波器的要求,可以通过一些数学模型或公式计算出所需的阶数。

然后根据阶数设计fir滤波器。

2. 经验法经验法是根据设计者的经验和实际需要来确定fir滤波器的阶数。

设计者可以根据实际应用的需求,通过试验和调整的方式选择合适的3. 自适应法自适应法是一种根据信号的特性来动态调整fir滤波器阶数的方法。

通过对输入信号进行分析,可以根据信号的频率特性和动态变化情况来自适应地调整阶数,以满足实时信号处理的需求。

四、阶数设计考虑因素在fir滤波器阶数设计时,需要考虑以下因素:1. 频率响应要求:根据滤波器的截止频率和通带要求,确定所需的阶数。

2. 计算复杂度:阶数越高,计算复杂度越大。

因此在实际应用中需要在满足要求的前提下尽量降低阶数,以提高计算效率。

3. 过渡带宽宽度:过渡带宽宽度越窄,滤波器的阶数需要越高,以保证频率响应的平坦度和截止频率的精确性。

4. 系统延迟:fir滤波器具有线性相位,因此系统延迟与阶数成正比。

在某些应用中,需要考虑系统延迟对信号处理的影响。

五、实例分析以音频处理为例。

假设我们需要设计一个fir滤波器,用于去除音频信号中的高频噪声。

根据音频信号的特性及噪声频率范围,我们可以确定所需的截止频率和通带要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目基于FPGA的FIR滤波器的程序设计课程设计任务书题目基于FPGA的FIR滤波器的程序设计专业、班级学号姓名主要内容、基本要求、主要参考资料等:主要内容:要求学生使用硬件描述语言(Verilog 或者 VHDL)设计基于FPGA的FIR 滤波器的源程序。

FIR滤波器的阶数为8;FIR滤波器的类型为低通,截止频率可以自行设计;FIR滤波器的系数可借助Matlab FDA tool 给出。

基本要求:1、学会quartusII的使用,掌握FPGA 的程序设计方法。

2、学会 MATLAB 的使用,掌握Matlab FDA tool的使用。

3、掌握硬件描述语言语法。

4、程序设计完成后要求在quartusII中实现功能仿真。

主要参考资料:1、周润景.基于QuartusⅡ的FPGA/CPLD数字系统设计实例[M].电子工业出版社.2007,82、褚振勇. FPGA设计及应用(第三版)[M].西安电子科技大学出版社.2012,43、陈怀琛.MATLAB及在电子信息课程中的应用[M].北京:电子工业出版社.2008,1完成期限:2015.6.21—2015.6.28指导教师签名:课程负责人签名:2015年6月18日基于FPGA的FIR滤波器的程序设计摘要在现代通信领域中,FIR数字滤波器以其良好的线性特性被广泛使用,属于数字信号处理的基本模块之一。

在实践中,往往要求对信号处理有实时性和灵活性,而已有的一些软件和硬件的实现方式则难以同时到达这两方面的要求。

随着可编程逻辑器件和EDA技术的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR滤波器。

本设计利用MATLAB软件中Matlab FDA tool设计一个FIR低通滤波器,导出所设计滤波器的系数,再利用QuartusⅡ软件,Verilog语言编写程序。

程序设计完成后在quartusII中实现功能仿真。

关键词Matlab FPGA FIR低通滤波器目录中文摘要 (I)1 概论 (2)1.1 课题的目的和意义 (2)1.2 FPGA技术的发展及应用 (3)1.3 FPGA软件设计工具Quartus II (4)2 FIR数字滤波器的设计方法理论部分 (5)2.1 引言 (5)2.2 FIR数字滤波器的基础 (5)2.3 数字滤波器的设计原理 (7)2.4 Matlab直接FDAtool设计方式解析 (8)2.5 FDAtool设计模板及设计结果图 (9)3 FIR数字滤波器的设计方法程序分析部分 (12)3.1 QuartusⅡ及Verilog HDL介绍 (12)3.2 实际滤波器程序设计(8阶FIR数字低通滤波器) (13)3.2.1 VerilogHDL的实现 (13)3.2.2 quartusII中功能仿真 (17)4 总结 (17)参考文献 (19)附录 (20)1 概论1.1 课题的目的和意义数字滤波器是一个离散时间系统(按预定的算法,将输入离散时间信号要求的输出离散时间信号的转换为所特定功能装置)。

应用数字滤波器处理模拟信号时,首先须对输入模拟信号进行限带、抽样和模数转换。

数字滤波器输入信号的抽样率应大于被处理信号带宽的两倍,其频率响应具有以抽样频率为间隔的周期重复特性,且以折叠频率即1/2抽样频率点呈镜像对称。

为得到模拟信号,数字滤波器处理的输出数字信号须经数模转换、平滑。

数字滤波器具有高精度、高可靠性、可程控改变特性或复用、便于集成等优点。

数字滤波器在语言信号处理、图像信号处理、医学生物信号处理以及其他应用领域都得到了广泛应用。

它涉及到的领域很广,如通信系统,系统控制,生物医学工程,机械振动,遥感遥测,地质勘探,故障检测,电力系统,航空航天,自动化仪器等。

数字滤波器的好坏对相关的众多工程技术领域影响很大,一个好的数字滤波器会有效的推动众多的工程技术领域改造和学科发展。

所以对数字滤波器的工作原理,硬件结构和实现方法进行研究具有一定的意义。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件。

与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能, FPGA允许无限次的编程。

1.2 FPGA技术的发展及应用FPGA正处于高速发展时期,新型芯片的规模越大,成本也越来越低,低端的FPGA已逐步取代了传统的数字元件,高端的FPGA将会成为今后竞争的主流。

自1985年问世以来,FPGA从集成电路与系统家族一个不起眼的小角色逐渐成为电子设计领域的重要器件。

它极大地提高了设计灵活性并缩短了产品上市时间,在通信、工业控制、航空领域中广泛应用。

FPGA行业集中度很高,几家美国公司掌握着行业的“制空权”。

特别是在航空航天及军工等特殊领域,美国等少数国家对先进的技术保持封锁。

因此,发展国内FPGA产业不是要不要的问题,而是怎么发展的问题。

国内IC企业介入FPGA的时间并不长,多数公司还处于学习阶段。

Altera公司和Xilinx公司为代表的FPGA厂商,除了在FPGA产品线上不断推陈出新之外,也在不懈地提高开发软件的设计能力,他们的软件产品在很多方面一点也不逊色于专业的EDA厂商,所以从这个角度来说,FPGA厂商也是EDA 公司。

这里的代表性产品就是Altera公司的Quartus II开发软件和Xilinx公司的ISE开发软件。

Altera的FPGA开发工具已经经历了四代。

从最初的基于DOS的A+Plus,发展到Max+Plus,1991年推出基于Windows的开发工具Max+Plus II。

Max+Plus II在FPGA设计工具里是一个划时代的产品,它提供了一种与结构无关的图形化设计环境,功能强大,使用方便。

设计者无须精通器件内部的复杂结构,而只需要使用自己熟悉的设计输入工具(如原理图或者HDL语言)把自己的设计输入到计算机中,Max+Plus II就会自动把这些设计转换成最终结构所需的格式,用户只要把最后生成的配置数据通过下载电缆下载到芯片中,即完成了所有的工作。

Quartus II是Altera公司在2001年推出的第四代开发工具,是一个集成化的多平台设计环境,能够直接满足特定设计需要,在FPGA和CPLD设计各个阶段都提供了工具支持,并为可编程片上系统(SOPC)提供全面的设计环境,是一个系统级的高效的EDA设计工具。

而且,随着器件结构和性能的不断提高,器件集成度的不断扩大,Altera始终能够同步推出与之相适应的开发工具,满足了设计者的要求,近年来一直保持着一年一个新版本的更新进度。

1.3 FPGA软件设计工具Quartus IIAltera公司和Xilinx公司为代表的FPGA厂商,除了在FPGA产品线上不断推陈出新之外,也在不懈地提高开发软件的设计能力,他们的软件产品在很多方面一点都不逊色于专业的EDA厂商,所以从这个角度来说,FPGA厂商也是EDA 公司。

这里的代表性产品就是Altera公司的Quartus II开发软件和Xilinx公司的ISE开发软件。

Altera的FPGA开发工具已经经历了四代。

从最初的基于DOS的A+Plus,发展到Max+Plus,1991年推出基于Windows的开发工具Max+Plus II。

Max+Plus II在FPGA设计工具里是一个划时代的产品,它提供了一种和结构无关的图形化的设计环境,功能强大,使用方便。

设计者无需精通器件内部的复杂结构,而只需要使用自己熟悉的设计输入工具(如原理图或者HDL语言)把自己的设计输入到计算机中,Max+Plus II就会自动把这些设计转换成最终结构所需的格式,用户只要把最后生成的配置数据通过下载电缆下载到芯片中,即完成了所有的工作。

Quartus II是Altera公司在2001年推出的第四代开发工具,是一个集成化的多平台设计环境,能够直接满足特定的设计需要,在FPGA和CPLD设计各个阶段都提供了工具支持,并为可编程片上系统(SOPC)提供全面的设计环境,是一个系统级的高效的EDA设计工具。

而且,随着器件结构和性能的不断提高,器件集成度的不断扩大,Altera始终能够同步推出与之相适应的开发工具,满足了设计者的要求,近年来一直保持这一年一个新版本的更新进度。

Altera公司的Quartus II软件是一种集编辑,编译,综合,布局布线,仿真与器件编程于一体的集成设计环境。

Quartus II软件支持基于VHDL与Verilog HDL等硬件描述语言的设计和基于图形的设计,内部嵌有VHDL和Verilong HDL 的逻辑综合器,也支持利用第三方的综合工具进行逻辑综合。

进行设计仿真时,既可以利用Quartus II软件自己的仿真工具,也可以利用如ModelSim等第三方仿真工具。

Quartus II软件除了进行基于FPGA的一般的数字系统开发外。

还可以与MATLAB和DSP Builder结合,进行基于FPGA的DSP系统开发;使用内嵌的SOPC Builder 设计工具,配合Nios II IDE 集成开发环境,进行基于Nios II 软核处理器的嵌入式系统开发。

Quartus II 软件的设计流程遵循典型的FPGA 设计流程,包括设计输入,综合,布局布线,时序分析,仿真验证,编程配置等设计步骤,以及与布局布线有关的功耗分析,调试,工程更改管理,与时序分析和仿真验证有关的时序逼近。

2 FIR 数字滤波器的设计方法理论部分2.1 引言数字滤波器的功能一般是用来变换时域或者频域中某些要求信号的属性,滤除信号中某一部分频率分量。