一种用单端口SRAM构成的FIFO的ASIC设计

存储器模块FIFO结构和设计实现

存储器模块FIFO结构和设计实现前言:在现代系统中,为了提高系统的性能,设计者对数据的传输率、数据的传输量,对系统各部分之间的接口部分不同数据输入和接收传输率的匹配有越来越高的要求,FIFO存储器以其合理的价格、使用的方便灵活性以及对速度匹配的应用而成为解决这类问题的理想途径,尤其利用FIFO可以实现快速处理,提高控制的速度,比如我们SPI,IIC或者UART将采集的一组数据送出去,但是这些数据传送都是需要一定时间的,有时为了不耽误数据采集的时间,就可以采集的数据直接先连续的存放在缓冲区内.数据的发送交给另外一个任务去处理.这样就不会耽误数据采集任务的时间来等待每个字节的发送完毕了.因此FIFO存储器在计算机、多媒体和数据通信领域都有着广泛的应用,它的实现具有理论上和实际应用上的双重意义。

正文:存储器模块FIFO的定义及简介:FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端时AD数据采集,另一端时计算机的PCI总线,假设其AD采集的速率为16位 100K SPS,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

FIFO的现状:在大规模集成电路设计中,一个系统包含了很多不相关的时钟信号,当其目标域时钟与源域时钟不同时,因而在这些不同域之间传递数据成为了一个重要问题。

sram 结构

SRAM 结构1. 简介SRAM(Static Random Access Memory)是一种静态随机存取存储器,它是计算机系统中常见的一种存储器类型。

与动态随机存取存储器(DRAM)相比,SRAM具有更快的访问速度和更低的功耗,但也更昂贵。

在计算机中,SRAM被广泛用作高速缓存(Cache)和寄存器文件(Register File),以提供快速访问的能力。

此外,SRAM还可以用于其他应用领域,如 FPGA (Field-Programmable Gate Array)和 ASIC(Application-SpecificIntegrated Circuit)。

2. SRAM 原理2.1 存储单元SRAM由多个独立的存储单元组成。

每个存储单元由一个触发器(Flip-flop)和两个交叉耦合的CMOS传输门构成。

这两个传输门分别负责读取和写入数据。

2.2 存储方式SRAM使用双稳态触发器来实现数据的持久性存储。

每个触发器可以保存一个位(0或1)。

当电源关闭时,数据仍然保持在触发器中,因此不需要周期性地刷新操作。

2.3 写操作写操作将数据从输入端写入到SRAM的存储单元中。

写操作包括两个步骤:地址传输和数据传输。

首先,将要写入的存储单元的地址传输到SRAM中。

地址传输使用行地址和列地址来确定具体的存储单元。

然后,将数据传输到SRAM中,通过写使能信号(Write Enable)控制写入操作。

当写使能信号为高电平时,数据被写入到存储单元中。

2.4 读操作读操作从SRAM的存储单元中读取数据并输出到输出端。

读操作也包括两个步骤:地址传输和数据输出。

首先,将要读取的存储单元的地址传输到SRAM中。

然后,通过读使能信号(Read Enable)控制读取操作。

当读使能信号为高电平时,SRAM将选定的存储单元中的数据输出到输出端。

3. SRAM 架构3.1 单端口 SRAM最简单的SRAM架构是单端口SRAM。

FIFO存储器读写数据的方法、装置、芯片及介质与流程

FIFO存储器读写数据的方法、装置、芯片及介质与流程概述FIFO存储器,全称为先进先出存储器(First-In-First-Out Memory),是一种数据存储和检索的设备。

相比传统的随机存取存储器(RAM),FIFO存储器的最大特点是采用先进先出的数据读写方式。

本文将详细介绍FIFO存储器的读写数据方法、装置、芯片及介质与流程。

读写数据的方法FIFO存储器的读写数据方法主要包括以下几种:1. 写入数据FIFO存储器的写入数据方法如下:•将待写入的数据按照先后顺序放入写入端口。

•根据FIFO存储器的容量,判断写入端口是否已满。

如果已满,则需要等待写入操作完成后再进行下一次写入。

•若写入端口未满,将数据写入FIFO存储器,并将写入指针指向下一个位置。

2. 读取数据FIFO存储器的读取数据方法如下:•将读取指针指向待读取的数据位置。

•根据FIFO存储器的容量,判断读取指针是否已到达最后一个位置。

如果是,则需要等待写入操作完成后,再进行下一次读取。

•若读取指针未到达最后一个位置,从FIFO存储器中读取数据,并将读取指针指向下一个位置。

3. 清空数据FIFO存储器的清空数据方法如下:•将写入指针和读取指针同时指向FIFO存储器的初始位置。

装置和芯片FIFO存储器的实现需要特定的装置和芯片。

以下介绍几种常见的FIFO存储器装置和芯片:1. SRAMSRAM(Static Random Access Memory)是使用静态电荷存储数据的一种非易失性存储器。

它是实现FIFO存储器的常见芯片之一。

SRAM具有快速的读写速度和低功耗的特点,因此被广泛应用于FIFO存储器中。

2. SDRAMSDRAM(Synchronous Dynamic Random Access Memory)是一种同步动态随机访问存储器,也可以作为FIFO存储器的芯片之一。

SDRAM通过在存储数据前进行时序控制,提高了数据的读写速度和可靠性。

asic设计方法知识点

asic设计方法知识点ASIC(Application Specific Integrated Circuit,专用集成电路)是根据特定应用需求进行设计的芯片。

它经过专门的设计和验证,以实现特定功能或任务。

本文将介绍ASIC设计方法的相关知识点,包括设计流程、设计方法和验证技术。

一、设计流程ASIC设计流程是按照一定的步骤进行的,主要包括需求分析、体系结构设计、逻辑设计、物理设计和验证。

下面将对这些步骤进行详细介绍。

1. 需求分析在需求分析阶段,设计人员需要明确ASIC的功能需求和性能指标。

他们与客户进行沟通,并根据客户所述需求进行详细分析。

在这个阶段,定义ASIC的输入输出接口和芯片的整体功能。

2. 体系结构设计体系结构设计是确定ASIC内部模块之间的关系和功能分配。

在这个阶段,设计人员将高层次的功能分解为多个模块,并定义它们之间的通信方式和数据交换。

还可以选择合适的处理器和外围设备。

3. 逻辑设计逻辑设计将体系结构设计的模块进行电路层次的设计。

在这个阶段,设计人员采用HDL(Hardware Description Language)编写硬件描述语言代码,然后进行逻辑综合和布局布线。

逻辑综合将HDL代码转化为逻辑网表,布局布线则将逻辑网表转化为物理布局。

4. 物理设计物理设计主要包括布局、布线和时序优化。

在设计布局时,需要确定各模块的相对位置和布局规则,以满足尺寸和性能要求。

布线阶段用于确定模块之间的互连路径,以及时序优化以确保设计的正确性和性能。

5. 验证验证是整个设计流程中非常重要的一步,确保ASIC设计满足规格要求。

验证可以包括功能仿真、时序仿真、形式验证和硬件验证等。

在验证阶段,设计人员需要使用专业的仿真和验证工具对设计进行验证,并解决可能出现的问题。

二、设计方法ASIC设计方法包括全定制设计、半定制设计和可编程逻辑设计。

下面将分别介绍这三种方法。

1. 全定制设计全定制设计是一种从零开始的设计方法,它提供了最大的灵活性和性能优化。

一种可实现同步双口SRAM功能的同步单口SRAM及其实现方法[发明专利]

![一种可实现同步双口SRAM功能的同步单口SRAM及其实现方法[发明专利]](https://img.taocdn.com/s3/m/b12d393d50e2524de4187e1e.png)

专利名称:一种可实现同步双口SRAM功能的同步单口SRAM 及其实现方法

专利类型:发明专利

发明人:朱哲,金传恩

申请号:CN200310118493.0

申请日:20031219

公开号:CN1555063A

公开日:

20041215

专利内容由知识产权出版社提供

摘要:本发明涉及集成电路领域,并具体的公开了一种可实现同步双口SRAM功能的同步单口SRAM及其实现方法。

本发明的同步单口SRAM包括:一个普通的同步单口静态随机存储器本体(1),并且还包括一个多输入多输出端的映射逻辑电路模块(2),所述映射逻辑电路模块(2)包含有用于连接上述同步单口静态随机存储器本体(1)各个信号端的端口,同时该映射逻辑电路模块(2)还包含有用于连接同步双口静态随机存储器所适用之信号端的端口,该映射逻辑电路模块(2)在上述同步单口静态随机存储器本体(1)和对应于同步双口静态随机存储器的各信号端口之间进行映射连接。

申请人:北京中星微电子有限公司

地址:100083 北京市海淀区学院路35号世宁大厦15层

国籍:CN

更多信息请下载全文后查看。

利用SRAM设计一个FIFO

利用SRAM设计一个FIFO为了设计一个能存储1200字以上的FIFO,可以首先确定所需的存储单元数量,然后根据这个数量创建一个SRAM存储器。

一个基本的SRAM存储单元通常包括一个存储位置和一个辅助逻辑电路,以实现存储和读取操作。

每个存储单元通常能存储一个字。

假设每个存储单元存储一个字节,那么我们需要1200个存储单元来存储1200字节。

为了充分利用SRAM的存储容量并降低功耗,我们可以采用一种叫做双端口SRAM(Dual-Port SRAM)的设计。

这种设计允许多个访问者同时存取SRAM,从而提高效率。

在这里,我们可以利用一个端口用于写入新的数据,另一个端口用于从FIFO中读取数据。

一个简单的FIFO设计可以基于一个循环缓冲区实现。

该缓冲区可以使用一个指针来指示当前写入位置,和一个指针来指示当前读取位置。

写入操作会将数据写入到当前写入位置,并将写入指针向前移动一个位置。

读取操作会读取当前读取位置的数据,并将读取指针向前移动一个位置。

以下是一个基于SRAM的FIFO设计示例:1.创建一个包含1200个SRAM存储单元的存储器。

2. 定义一个用于写入的指针(write_ptr)和一个用于读取的指针(read_ptr),初始值均为0。

3.定义一个存储器控制电路,用于实现对SRAM的读写操作。

4. 当有新数据需要写入时,将数据写入到当前write_ptr指向的存储单元,并将write_ptr向前移动一个位置(如果已经到达最后一个存储单元,则返回到第一个存储单元)。

5. 当需要读取数据时,从当前read_ptr指向的存储单元读取数据,并将read_ptr向前移动一个位置(如果已经到达最后一个存储单元,则返回到第一个存储单元)。

通过以上设计,我们就可以实现一个能存储1200字节以上数据的FIFO。

在实际应用中,还需要根据具体需求来设计一些额外的控制逻辑,以确保正确的数据读写和FIFO操作的一致性。

基于单口Memory的同步FIFO设计

基于单口Memory的同步FIFO设计使用单口RAM实现FIFO,其实很简单,其中的重点就是区分出读写,读写如果同时启动,你肯定会思考单口RAM肯定会出问题,毕竟单口RAM只有一个口,肯定不能实现同时读写,那么怎么解决这个问题呢。

有两种办法:第一种办法就是采用两个单口RAM,这样就可以了,两个单口RAM分开奇偶,相当于乒乓的意思,然后再加一个REG,这就相当于把读写分开了那么就可能分为以下几种情况:①同时读写:读写同时为奇,这种情况就是在当前一拍,将写数据存入REG 中,并将REG_VALID拉高告诉FIFO我下一拍要写数据,并在当前拍从奇数的FIFO中读取数据,那么下一拍如果再此发生同时读写,那么此时的同时读写就为偶,这一拍发生的情况就是将前一拍REG中的数据写入FIFO,然后将REG 中数据更新新数据,然后将REG_VALID再拉高,告诉偶数FIFO下一拍要写数据了,并同时从偶数FIFO中取出要读的数据。

其实核心观点就是用两个单口RAM一个REG,用来区分最难的读写同时发生的情况,通过将RAM分为奇偶再加一个REG寄存器用来缓存,这就使不能同时读写的情况给解决了。

如果同时读写,且奇偶不同,那这种情况就更容易解决了,当前拍写数据的模块将数据写入REG,读模块的读出数据,然后下一拍将REG再写入单口RAM,和之前同时读写同时为奇偶的情况很相似。

②不同时读写:这种情况就是你只要写就先将数据写入REG,然后拉高VALID下一拍将REG中的数据写入单口RAM,如果读就直接读出数据。

通过这种方式就完美的解决了单口RAM没办法同时操作RAM的情况。

代码如下第二种情况就是针对单口RAM 的位宽进行变化,比如FIFO 的读写数据位宽为8Bit ,那么就针对RAM 的位宽设置为FIFO 位宽的两倍,外部加两个同等位宽的读写寄存器,通过将读写寄存器与外界读写和读写寄存器与RAM 的交互实现FIFO 的功能,比如对于同时读写的情况,在时钟上按2拍完成一次寄存器与RAM数据的交互,比如第一拍完成读,第二拍完成写,对于外界的接口而言数据是源源不断的从寄存器出来的,从而实现了单口RAM实现FIFO的功能,这种情况只适用于对FIFO连续读写的情况下才能使用,不连续读写总有一次会把其设置成同时读写的情况。

利用SRAM设计一个FIFO.

292练习十二利用 SRAM 设计一个 FIFO在本练习中,要求同学利用练习十一中提供的 SRAM 模型,设计 SRAM 读写控制逻辑, 使 SRAM 的行为对用户表现为一个 FIFO (先进先出存储器。

1 设计要求:本练习要求同学设计的 FIFO 为同步 FIFO,即对 FIFO 的读/写使用同一个时钟。

该 FIFO 应当提供用户读使能(fiford和写使能(fifowr输入控制信号,并输出指示FIFO 状态的非空 (nempty 和非满 (nfull信号, FIFO 的输入、输出数据使用各自的数据总线:in_data 和2 FIFO 接口的设计思路FIFO 的数据读写操作与 SRAM 的数据读写操作基本上相同,只是 FIFO 没有地址。

所以用 SRAM 实现 FIFO 的关键点是如何产生正确的 SRAM 地址。

我们可以借用软件中的方法, 将 FIFO 抽象为环形数组, 并用两个指针:读指针(fifo_rp 和写指针(fifo_wp控制对该环形数组的读写。

其中,读指针 fifo_rp指向下一次读操作所要读取的单元,并且每完成一次读操作, fifo_rp加一;写指针 fifo_wp则指向下一次写操作时存放数据的单元,并且每完成一次写操作, fifo_wp加一。

由fifo_rp和 fifo_wp的定义易知 , 当 FIFO 被读空或写满后, fifo_rp和 fifo_wp将指向同一单元, 但在读空和写满之前 FIFO 的状态是不同的,所以如果能区分这两种状态,再通过比较 fifo_rp和 fifo_wp就可以得到 nempty 和 nfull 信号了。

下图为 FIFO 工作状态的示意。

N单元内有数据单元内无数据一般情况再写即满再读即空在得到 nfull 和 nempty 信号后,就需要考虑如何应用这两个信号来控制对 FIFO 的读写,使得 FIFO 在被写满后不能再写入,从而防止覆盖原有数据,并且在被读空后也不能再进行读操作,防止读取无效数据。

一种低功耗异步FIFO在ASIC中的设计

F IFO ) 存储器模块的实现方案 。为适应 大量的视频数据猝发传输设计一种宽为 36 位 、 深为 256 的异步 F IFO, 基于低功耗 设计 思想 , 使用格雷码地址编码以有效抑制亚稳态 , 增加了门控时钟电路 。 该模块已经过测试验证 , 并与音视频模块和 PC I桥 集成 后流片 , 可以工作在最大 197MH z的 频率下 , 完全符合设计要求 。 该桥芯片可以支持 4 路 D 1 画质 ( 704 视频数据稳定采集 。 关键词 : 专用集成电路 ( A SIC); 异步 F I FO; 格雷码 ; 低功耗 中图分类号 : TP302. 2 文献标志 码 : A 576 分辨率 ) 实时音

[ 5] [ 4]

。图 3 描述了一个比较

典型的异步 F IFO 的抽象结构。

图 2 电路亚稳态的形成

经过决断时间后 , 输出端 Q 将会稳定到高电平 1 或低电平 0 。在图 2 中, 基于 27 MH z的 CLK27 时

图 3 异步 F IFO 的抽象结构

第 1期

范小虎 , 等 : 一种低功耗异步 FIFO 在 A S I C 中的设计

[ 3]

, 在实际的设计中还采用了地址指针

[ 11 - 12]

增加一位状态位的方式 判断空满 :

, 同时根据设计的需求

引入了 Sptr与 Fptr , 用如下 V erilog HDL 关键代码来 gray_ w syn< = rptr_gray ; / /W rite synchronization gray_rsyn< = w ptr_gray; / /Read synchronization Sptr< = wptr ; / / Sptr has one clk period lag to Syn chronize Assign fptr [ ASIZE ] = wptr [ ASIZE ] ^ 1∀b1 ; / /Other b its are equa l to W ptr . ## Assign Em pty= ( sptr_gray= = g ray_rsyn)? 1∀ b1 : 1∀ b0 ; Assign F ull= ( fptr_gray= = g ray_w syn) ? 1∀ b1 : 1∀b0 。 另外 , 为了适应大规 模视频数据 的猝发传 输, C lifford E. Cu mm in gs的同步方案的读写延迟使控制 器不能及时获得空满状态, 我们在其基础上又增添了 异步计数器来支持高效率的猝发传输。除了在 C lr 或空满状态时, 用如下方式来计算计数器中的数值: if( sptr_gray= = g ray_rsyn) cnt< = sptr- rptr ; / / nptr 。 如此就可以依据计数器中的数值设置水位

FIFO SRAM单粒子效应的测试系统设计

FIFO SRAM单粒子效应的测试系统设计刘永灿;潘滨;李爱平【摘要】With the development of aviation and aerospace industry, devices’anti-irradiation performance is becoming more and more important.Therefore, the application testing of the anti-irradiation index has become more critical. Based on FPGA and NI controller, an data acquisition and test system with four channels was designed in this paper.The system was used to monitor SEU effects and SEL effects in FIFO SRAM’s single event experiment. The sampling rate can reach 50MH Z, and the read-write frequency of device can reach 10Mbytes. The system realized the remote monitoring of FIFO SRAM’s single event experiment. In the process of monitoring SEU, both memory’s SEU effects and read-write pointer’s SEU effects were monitored. Thereliability of this system was verified in actual single event effects test.%随着航空航天事业的发展,器件的抗辐照性能变得越来越重要,因此对抗辐照指标的应用测试已显得至关重要。

基于SRAM和DRAM结构的大容量FIFO的设计与实现

基于SRAM 和DRAM 结构的大容量FIFO的设计与实现1 引言FIFO(First In First Out)是一种具有先进先出存储功能的部件,在高速数字系统当中通常用作数据缓存。

在高速数据采集、传输和实时显示控制领域中,往往需要对大量数据进行快速存储和读取,而这种先进先出的结构特点很好地适应了这些要求,是传统RAM无法达到的。

许多系统都需要大容量FIFO作为缓存,但是由于成本和容量限制,常采用多个FIFO芯片级联扩展,这往往导致系统结构复杂,成本高。

本文分别针对Hynix公司的两款SRAM和DRAM器件,介绍了使用CPLD进行接口连接和编程控制,来构成低成本、大容量、高速度FIFO的方法。

该方法具有通用性,可以方便地移植到与其他RAM器件相连的应用中去。

2 基于SRAM的设计与实现SRAM结构芯片HY64UD16322A静态随机存取存储器SRAM(Static Random Access Memory)是一种非常重要的易失性存储器,它的速度非常快,并且能在快速读取和刷新时保持数据完整性。

本系统SRAM器件采用Hynix公司的HY64UD16322A。

HY64UD16322A是高速、超低功耗32Mbit SRAM,内部具有2097152个16 bit字容量。

采用了CMOS制造工艺、TTL 电平接口以及三态输出,具有较大的输入电压和温度范围。

同时HY64UD16322A支持DPD(Deep Power Down)模式,保证其在待机模式下功耗进一步降低。

系统硬件设计整个系统采用CPLD作为控制核心器件。

CPLD选用Altera公司的MAX7128AETC100-5。

MAX7128基于Altera公司第二代MAX 乘积项结构,是采用CMOS EEPROM技术制造的EPLD,它集成了2500个可用门,128个宏单元以及100个I/O引脚。

图1是HY64UD16322A内部结构以及与CPLD接口设计的系统连接图。

一种SRAM单双端口转换电路的设计与实现

一种SRAM单双端口转换电路的设计与实现王天楚,贺祥庆(清华大学 微电子学研究所,北京 100084)摘 要: 介绍了一种用于单端口SRAM的单双端口转换电路。

利用该转换电路,可以使单端口SRAM实现双端口SRAM的功能。

这种转换电路将外部两个端口的信号进行转换和优先权分配,使外部两个端口的并行操作在内部用单端口SRAM依次完成。

这样,从外部看来,单端口SRAM就具有了双端口SRAM的全部功能。

用这种转换电路生成的双端口SRAM与相同容量的传统双端口SRAM相比,面积显著减少。

基于SM IC0.13 m标准CMOS工艺,设计了转换电路。

后仿真结果显示,该转换电路实现了预期功能。

关键词: 转换电路;单端口;双端口;SRAM中图分类号: T P333.5 文献标识码: A文章编号:1004 3365(2008)04 0544 04A Single to Dual Port Converter for S RAMWANG T ianchu,H E Xiangqing(I nstitu te of M icr oelec tr onics,T sing hua Univ ersity,Be ij ing100084,P.R.China)Abstract: A single to dual po rt co nv erter fo r SR AM w as pr oposed,which conver ted sig nals betw een tw o ex ter nal po rts and carr ied out prio rit y assignment,so that par allel operat ions o f the tw o ex ternal por ts could be ex ecuted in t ur n by int ernal sing le port SR AM.W ith t his converter,sing le po rt SR AM could be used as dual por t SRA M.Co mpar ed to co nv ent ional dual por t SR AM,the new dual po rt SRA M using this co nv erter occupied a much smaller chip ar ea.T his conver ter w as desig ned based on SM IC s0.13 m st andard CM OS t echnolog y.Results fro m po st lay out simulatio n show ed that the conver ter had fulfilled t he anticipated function.Key words: Convert er;Sing le por t;Dual po rt;SRA MEEACC: 1290B1 引 言双端口SRAM与单端口SRAM相比,其应用范围更加广泛。

一种基于ASIC的高速异步FIFO设计

一种基于ASIC的高速异步FIFO设计丁彬勇;白雪飞;黄鲁【期刊名称】《微型机与应用》【年(卷),期】2011(030)022【摘要】分析了异步FIFO的结构和关键技术,在与利用格雷码作为异步FIFO指针编码对比的基础上,提出了一种采用移位码编码方式的FIFO,不仅减小了亚稳态出现的概率,也简化了电路结构,降低了电路面积和功耗,在此基础上也缩短了电路的关键路径,工作频率明显提升。

根据仿真和综合结果显示,本文设计的FIFO工作性能稳定可靠。

%This paper analysis the structure and key technology of asynchronous FIFO. Compared with the method of using Gray code as the pointer of asynchronous FIFO, the paper presents a method that shift code is instead of gray code. This new design has the following advantages. Firstly, the probability of occurrence in metastability is reduced. Secondly, the circuit structure, area and the pow- er consumption are more simple, small and lower. Also, the key path of the circuit is shortened. The result is the circuit's working frequency is improved significantly. The results of simulation and synthesis shows that this FIFO is stable and reliable.【总页数】4页(P21-23,27)【作者】丁彬勇;白雪飞;黄鲁【作者单位】中国科学技术大学电子科学与技术系集成电路实验室,安徽合肥230027;中国科学技术大学电子科学与技术系集成电路实验室,安徽合肥230027;中国科学技术大学电子科学与技术系集成电路实验室,安徽合肥230027【正文语种】中文【中图分类】TN492【相关文献】1.一种新结构异步FIFO的ASIC设计 [J], 周磊;朱礼安;苏俊杰;丁晓磊;赵梅;顾皋蔚;朱恩2.基于DDR2 SDRAM的高速大容量异步FIFO的设计与实现 [J], 徐欣;周舟;李楠;孙兆林3.高速视频系统中一种异步FIFO缓存设计 [J], 房国志;王康4.一种低功耗异步FIFO在ASIC中的设计 [J], 范小虎;杨波;孙涛5.一种高可靠性高速可编程异步FIFO的设计 [J], Niu Bo;Zhao Hongliang因版权原因,仅展示原文概要,查看原文内容请购买。

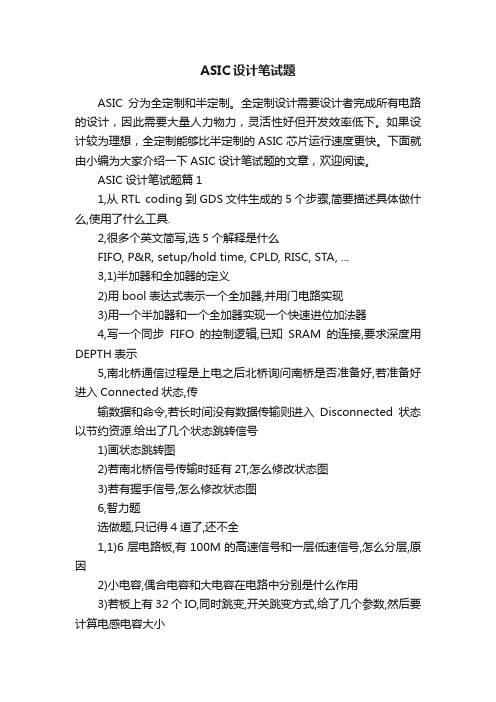

ASIC设计笔试题

ASIC设计笔试题ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

下面就由小编为大家介绍一下ASIC设计笔试题的文章,欢迎阅读。

ASIC设计笔试题篇11,从RTL coding到GDS文件生成的5个步骤,简要描述具体做什么,使用了什么工具.2,很多个英文简写,选5个解释是什么FIFO, P&R, setup/hold time, CPLD, RISC, STA, ...3,1)半加器和全加器的定义2)用bool表达式表示一个全加器,并用门电路实现3)用一个半加器和一个全加器实现一个快速进位加法器4,写一个同步FIFO的控制逻辑,已知SRAM的连接,要求深度用DEPTH表示5,南北桥通信过程是上电之后北桥询问南桥是否准备好,若准备好进入Connected状态,传输数据和命令,若长时间没有数据传输则进入Disconnected状态以节约资源.给出了几个状态跳转信号1)画状态跳转图2)若南北桥信号传输时延有2T,怎么修改状态图3)若有握手信号,怎么修改状态图6,智力题选做题,只记得4道了,还不全1,1)6层电路板,有100M的高速信号和一层低速信号,怎么分层,原因2)小电容,偶合电容和大电容在电路中分别是什么作用3)若板上有32个IO,同时跳变,开关跳变方式,给了几个参数,然后要计算电感电容大小2,给出一个组合时序程序,已知几个波形,画其他信号的波形(组合逻辑,时序有posedge和negedge,参数还互相嵌套,非常烦杂)2)3)问不记得了,没做3,a. caching 和 pre-fetch都是提高数据访问效率的方法,简述其含义。

b. 说明cache的两种写回方式。

c. 在嵌入式中,以上两种方法分别可以被用在下面哪个功能中BIU 和DMA。

4,M种颜色的球放入n个盒子中,每个盒子中球的个数和颜色不定,有一个m种颜色的色盘,设计一种数据结构,从n个盒子中拿出最小数量的盒子,填满色盘。