PT_Unit_4(primetime)

precision time protocol原理

precision time protocol原理

精密时钟协议(Precision Time Protocol,简称PTP)是一种用

于在计算机网络中实现精确时间同步的协议。

该协议旨在提供亚微秒级别的同步精度,并具有较高的可用性和可靠性。

PTP的工作原理如下:

1. 主从架构:PTP网络中有一个主时钟(Master)和多个从时

钟(Slave)。

主时钟通过广播时间戳的信息给从时钟,从时

钟通过接收和处理主时钟的时间戳信息来实现同步。

2. 时间戳传递:主时钟周期性地向从时钟发送时间戳包,时间戳包中包含主时钟的时间信息。

从时钟接收到时间戳包后,将其中的时间信息与自身的时间进行比较,并将差异作为补偿因子,用于调整自身的时钟。

3. 延迟补偿:PTP通过测量主时钟和从时钟之间的延迟,并将其补偿,以消除网络传输引起的时钟偏差。

在时间戳包中,主时钟使用两个时间戳:发送时间戳和接收时间戳,通过计算这两个时间戳的差值,可以获得网络延迟。

4. 时钟校正:PTP通过迭代算法进行时钟校准。

从时钟接收到时间戳包后,将时间戳与自身的时间进行比较,计算时间差值,并将其作为补偿因子用于调整自身的时钟。

这个过程逐步迭代,直到达到所需的同步精度。

5. 精度控制:PTP通过定义时钟运行速度、传输延迟和测量误差等参数,以及根据网络条件动态调整时钟校准延迟等方式,

来控制同步的精度。

总结来说,PTP通过周期性的时间戳传递、延迟补偿和时钟校准等机制,实现计算机网络中的精确时间同步。

PrimeTime_的基本概念

PrimeTime_的基本概念PrimeTime 的基本概念⼀、定义设计环境在对设计作时序分析之前,必须要定义好设计环境以使得在那些情况下满⾜限制条件。

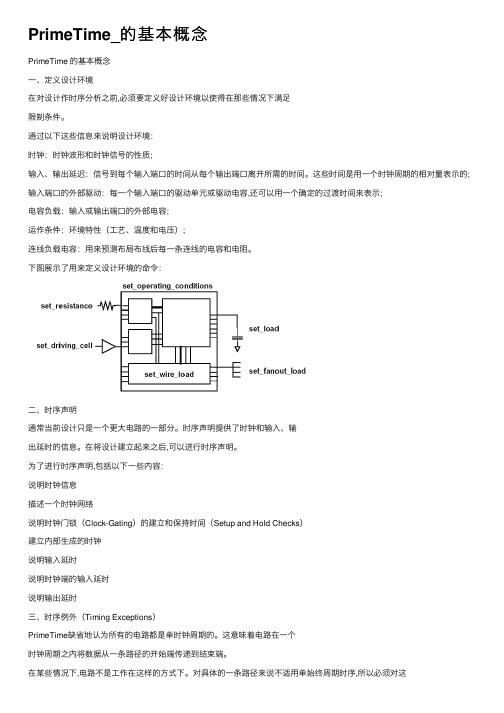

通过以下这些信息来说明设计环境:时钟:时钟波形和时钟信号的性质;输⼊、输出延迟:信号到每个输⼊端⼝的时间从每个输出端⼝离开所需的时间。

这些时间是⽤⼀个时钟周期的相对量表⽰的;输⼊端⼝的外部驱动:每⼀个输⼊端⼝的驱动单元或驱动电容,还可以⽤⼀个确定的过渡时间来表⽰;电容负载:输⼊或输出端⼝的外部电容;运作条件:环境特性(⼯艺、温度和电压);连线负载电容:⽤来预测布局布线后每⼀条连线的电容和电阻。

下图展⽰了⽤来定义设计环境的命令:⼆、时序声明通常当前设计只是⼀个更⼤电路的⼀部分。

时序声明提供了时钟和输⼊、输出延时的信息。

在将设计建⽴起来之后,可以进⾏时序声明。

为了进⾏时序声明,包括以下⼀些内容:说明时钟信息描述⼀个时钟⽹络说明时钟门锁(Clock-Gating)的建⽴和保持时间(Setup and Hold Checks)建⽴内部⽣成的时钟说明输⼊延时说明时钟端的输⼊延时说明输出延时三、时序例外(Timing Exceptions)PrimeTime缺省地认为所有的电路都是单时钟周期的。

这意味着电路在⼀个时钟周期之内将数据从⼀条路径的开始端传递到结束端。

在某些情况下,电路不是⼯作在这样的⽅式下。

对具体的⼀条路径来说不适⽤单始终周期时序,所以必须对这些缺省的时序假设作例外说明。

否则,时序分析将不能反映真实电路的⼯作情况。

主要有以下⼀些内容:单时钟周期(缺省)路径延时限制设置失败(False)路径设置最⼤和最⼩路径延时设置多时钟周期路径路径说明⽅法有效地说明例外情况例外情况的优先级报告例外情况忽略例外情况去除例外声明四、报告的⽣成在定义了时序声明和例外情况之后,可以⽣成时序分析报告,有助于定位设计中的违规之处。

在进⾏时序分析的时候,PrimeTime会跟踪电路中所有的路径,然后根据电路说明、库、声明和例外情况计算设计的延时。

Primetime时序分析流程与方法

PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有多哥时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境- 建立搜索路径(search path)和链接路径(link path)- 读入设计和库- 链接顶层设计- 建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)- 定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)- 说明输入、输出端口的延时3、说明时序例外情况(timing exceptions)- 多周期路径(multicycle paths)- 不合法路径(false paths)- 说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告- 检查时序- 生成约束报告- 生成路径时序报告开始先建立目录并将PrimeTime本身所带的一个例子拷到新建的目录下,在下面的内容中将要用到这个例子。

模板-使用PrimeTime,PX进行功耗分析

使用PrimeTime,PX进行功耗分析使用PrimeTime PX进行功耗分析一、工具介绍PrimeTime是synopsys开发的一款专门的静态时序分析软件,PrimeTime PX是集成在软件中的一个工具,可以用来对Design Compilier(DC)综合后的V文件进行功耗分析。

PrimeTime的一个特点就是它对功耗的分析比DC给出的功耗信息要精确得多,所以一般采用PTPX进行功耗分析。

PTPX可以进行两种模式的功耗分析:l 平均功耗分析(Averaged Power Analysis) 在这种模式下,动态翻转速率可以是默认值或者是用户自定义的,也可以由HDL的仿真文件提供。

进行平均功耗分析时可以使用两种格式的激励文件,分别是SAIF和VCD。

l 基于时序的功耗分析(Time-Based Power Analysis) 在这种模式下,为了获得精确的与时序有关的功耗信息,必须要有仿真文件提供激励。

Time-Based支持VCD、VPD以及fsdb格式的激励。

特别是对于VCD文件来说,可以支持RTL级别的仿真文件或者是Gate级别的仿真文件。

对于RTL Level的VCD文件要使用read_vcd –rtl或者是read_vcd –zero_delay命令,否者会被识别成Gate Level的仿真文件。

二、PTPX工具进行功耗分析流程使用PTPX进行功耗分析之前,要准备如下文件:l 逻辑综合后的.V文件 l 静态时序分析的.sdc文件 l有功耗信息的.db文件 l RTL的仿真文件.VCD 2.1.V文件、.sdc文件以及.db文件的获得在使用DC完成对工程的综合后,会得到一个如下图所示的V文件(以本实验室综合所用工程rfid2016_v2为例,V文件存放在/rfid2016_v2/flow/syn/result目录下):图2-1 .V文件存放目录 V文件里面的内容如下:图2-2 综合后.V文件内容接下来获取.sdc文件,PTPX用到的.sdc文件和DC用到的.sdc文件一致。

EDA技术_Synopsys公司STA工具PrimeTime介绍

PT进行时序分析的流程 进行时序分析的流程

EDA技术实验 技术实验

设置设计环境

设置查找路径和链接路径

The search_path variable specifies a list of directory paths thatPrimeTime uses to find the designs, libraries, and other files. The link_path variable specifies a list of libraries that PrimeTime uses to link designs

pt_shell> create_generated_clock -multiply_by 2 -duty_cycle 60 -source [get_pins CLK] [get_pins foo1]

2010-12-29

16

ASIC设计中心

PrimeTime命令 命令

EDA技术实验 技术实验

时序分析命令

set_operating_conditions set_case_analysis read_sdf read_parasitics set_driving_cell set_load set_wire_load_model set_multicycle_path set_false_path set_disable_timing

pt_shell>set_case_analysis 1 test_mode pt_shell>remove_case_analysis test_mode

2010-12-29

7

ASIC设计中心

synopsys prime time范例

synopsys prime time范例Prime Time(PT)是Synopsys的签收品质(sign-off quality)的静态时序分析工具。

静态时序分析(STA)无疑是设计流程中最重要的一步,它决定了设计是否在所要求的速度下工作,PT分析设计中的时序延迟并标注出必须改正的违例。

PT是一个不在DC工具套件中集成的单独的工具,它是一个和DC 并行工作的单独的工具。

PT与DC有一致的命令,它们生成类似的报告,并支持共同的文件格式。

此外PT也能生成DC用于综合和优化的时序断言,PT的命令行界面是基于称为Tcl为工业标准语言。

与DC 的内部STA引擎相比,PT更快,占用的内存更少,并且还有其他的一些特色。

Prime Time环境一经调用,PT就寻找名为“.synopsys_pt.setup”的文件并默认包括它。

这个文件包含了定义PT使用的设计环境的必要设置变量,示例如下:变量serach_path定义了一个列表,它包含了当查找库和设计时需要查看的目录;变量link_path定义了一个库列表,它包含用于连接设计的单元。

Tcl提供了大部分的基本程序结构——变量、运算符、表达式、控制流、循环和过程等。

另外,Tcl也支持大多数的UNIX命令,是PT中的脚本语言。

本节简要介绍Tcl的一些基础语法。

使用set命令定义变量并给它们赋值,例如:set clock_name clkset_clock_preiod 20值可以是数字或字符串——Tcl不区分数值型变量和字符串型变量。

在算数场合,它自动使用数字值。

上例中,社变量clock_name 为字符串clk,设变量clock_period为数值20。

通过在变量名前加$来引用变量。

如果在变量名前没有加$,那么Tcl将其视为字符串。

create_clock$clock_name-period 20-waveform[0 10]通过expr命令进行算数运算。

这个有用的技术提供了贯穿于整个脚本的全局参数化的方法。

EDA技术Synopsys公司STA工具PrimeTime介绍ppt课件

ASIC设计中心

PrimeTime命令

EDA技术实验

1 设计输入

PT不能读取RTL源文件,它是静态分析引擎, 只能读取映射后的设计,包括db、verilog、 vhdl等格式的文件。 pt_shell> read_db –netlist_only <filename>.db

2018/11/15 2 ASIC设计中心

PT

EDA技术实验

PT是Synopsys的sign-off quality的STA 工具,是一个单点的全芯片、门级静态时 序分析器。 PrimeTime工作在设计的门级层次,并 且和Synopsys其它工具整合得很紧密。

2018/11/15

3

ASIC设计中心

2018/11/15

7

ASIC设计中心

PT进行时序分析的流程

EDA技术实验

进行时序分析:

在作好以上准备工作的基础上,可以对电路 进行静态时序分析,生成constraint reports 和path timing reports。

2018/11/15

8

ASIC设计中心

PrimeTime的用户界面

读入设计(和库文件) 链接顶层设计 对必要的操作条件进行设置,这里包括了线上负载 的模型、端口负载、驱动、以及转换时间等

2018/11/15

5

ASIC设计中心

PT进行时序分析的流程

EDA技术实验

指定时序约束(timing constraints)

定义时钟周期、波形、不确定度(uncertainty)、延 时(latency) 指明输入输出端口的延时等

PT

EDA技术实验

基本特点和功能:

建立和保持时间的检查(setup and hold checks) 时钟脉冲宽度的检查 门控时钟检查(clock-gating checks) recovery and removal checks unclocked registers 未约束的时序端点(unconstrained timing endpoints) multiple clocked registers 组合反馈回路(combinational feedback loops) 基于设计规则的检查,包括对最大电容、最大传输时间、 最大扇出的检查等。

PrimeTime

--Set and Remove a False Path Exception

• 建立和删除伪路径例外 1.申明一个伪路径from pin g1/CP to g13/D: pt_shell> set_false_path -from g1/CP -to g13/D 2.指出设计的时序例外: pt_shell> report_exceptions ... From To Setup Hold Ignored -------------------------------------------------g1/CP g13/D FALSE FALSE ... 3.删除例外: pt_shell> reset_path -from g1/CP -to g13/D pt_shell> report_exceptions //查看报告

pt_shell> all_fanout -from g1/CP -endpoints_only 3.重置伪路径 pt_shell> reset_path -from g1/CP(伪路径的设置与重置的方式要对应,否则无法重 置,如此处若用 pt_shell> reset_path -from g1/CP -to g13/D 重置,则无效,因为建 立为路径是用的是-from) 4.通过组合逻辑设置更特殊的伪路径: pt_shell> set_false_path -setup \ -from g1/CP -through g9/Z -to g13/D 5.重置时序例外 pt_shell> reset_path -from g1/CP pt_shell> report_exceptions 例外的设置命令可以是reset_path命令的子集,但reset_path命令不可以是例外设置 命令的子集

PrimeTime 时序分析流程和方法

PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有xx时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境-建立搜索路径(search path)和链接路径(link path)-读入设计和库-链接顶层设计-建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)-定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)-说明输入、输出端口的xx3、说明时序例外情况(timing exceptions)-多周期路径(multicycle paths)-不合法路径(false paths)-说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告-检查时序-生成约束报告-生成路径时序报告开始先建立目录并将PrimeTime本身所带的一个例子拷到新建的目录下,在下面的内容中将要用到这个例子。

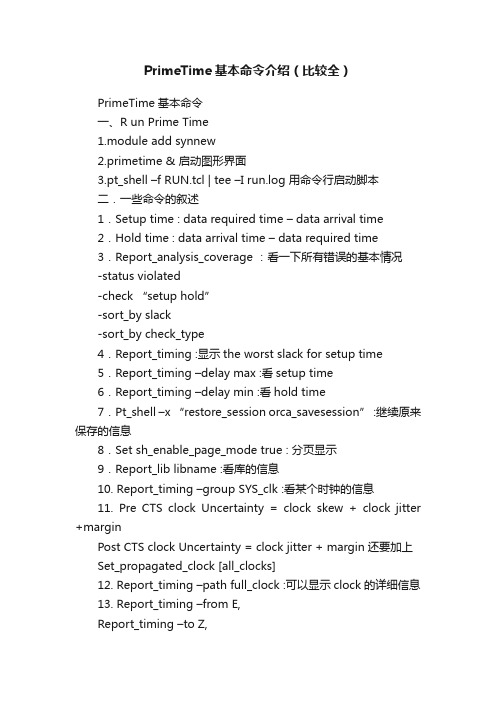

PrimeTime基本命令介绍(比较全)

PrimeTime基本命令介绍(比较全)PrimeTime基本命令一、R un Prime Time1.module add synnew2.primetime & 启动图形界面3.pt_shell –f RUN.tcl | tee –I run.log 用命令行启动脚本二.一些命令的叙述1.Setup time : data required time – data arrival time2.Hold time : data arrival time – data required time3.Report_analysis_coverage :看一下所有错误的基本情况-status violated-check “setup hold”-sort_by slack-sort_by check_type4.Report_timing :显示the worst slack for setup time5.Report_timing –delay max :看setup time6.Report_timing –delay min :看hold time7.Pt_shell –x “restore_session orca_savesession” :继续原来保存的信息8.Set sh_enable_page_mode true : 分页显示9.Report_lib libname :看库的信息10. Report_timing –group SYS_clk :看某个时钟的信息11. Pre CTS clock Uncertainty = clock skew + clock jitter +marginPost CTS clock Uncertainty = clock jitter + margin还要加上Set_propagated_clock [all_clocks]12. Report_timing –path full_clock :可以显示clock的详细信息13. Report_timing –from E,Report_timing –to Z,Report_timing –from G –to FF4/D :显示详细路径的信息14. Report_port –input_delay –output_delay inoutpad,Report_port –input_delay inputpadReport_port –ouput_delay outputpad: 看port的信息15. Report_timing –input_pins :可以看到net的delay16. Report_lib –timing_arcs libname cellname:看库单元的时序信息17. Report_cell –connections –verbose Instance_name :看单元的信息28. Report_timing –max_paths 2 –nworst 2 :可以看两条path 的两个最坏的timing,default为1。

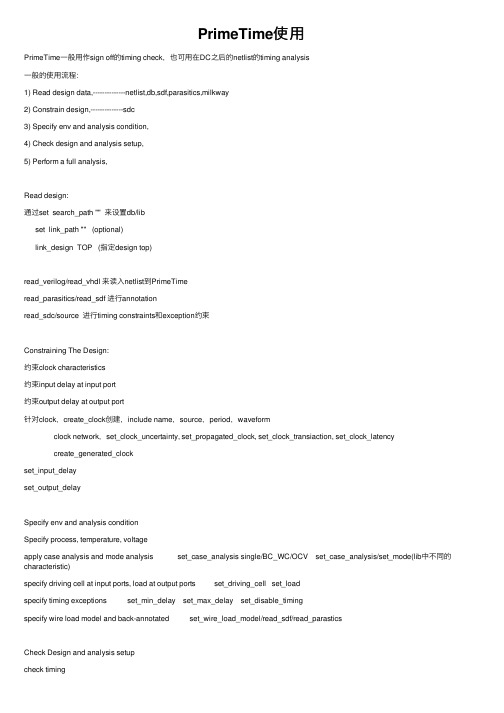

PrimeTime使用

PrimeTime使⽤PrimeTime⼀般⽤作sign off的timing check,也可⽤在DC之后的netlist的timing analysis⼀般的使⽤流程:1) Read design data,--------------netlist,db,sdf,parasitics,milkway2) Constrain design,--------------sdc3) Specify env and analysis condition,4) Check design and analysis setup,5) Perform a full analysis,Read design:通过set search_path "" 来设置db/libset link_path "" (optional)link_design TOP (指定design top)read_verilog/read_vhdl 来读⼊netlist到PrimeTimeread_parasitics/read_sdf 进⾏annotationread_sdc/source 进⾏timing constraints和exception约束Constraining The Design:约束clock characteristics约束input delay at input port约束output delay at output port针对clock,create_clock创建,include name,source,period,waveformclock network,set_clock_uncertainty, set_propagated_clock, set_clock_transiaction, set_clock_latencycreate_generated_clockset_input_delayset_output_delaySpecify env and analysis conditionSpecify process, temperature, voltageapply case analysis and mode analysis set_case_analysis single/BC_WC/OCV set_case_analysis/set_mode(lib中不同的characteristic)specify driving cell at input ports, load at output ports set_driving_cell set_loadspecify timing exceptions set_min_delay set_max_delay set_disable_timingspecify wire load model and back-annotated set_wire_load_model/read_sdf/read_parasticsCheck Design and analysis setupcheck timingreport_designreport_portreport_netreport_libreport_path_groupreport_clockreport_wire_loadPerforming a Full Analysisreport_timing -delay_type/-from/-to/-through/-rise_through/-rise_fromreport_constraintreport_analysis_coveragereport_delay_calculationPrimeTime中的Design Objects,可以使⽤get命令, set_input_delay 2.3 [get_ports IN*]cell---------instance in the design, include reference hierarchical blocks and library cell lib_cell--------cells in technology librarylib_pin-------pins in library cellsnet----------nets in current designpin-----pins of lower-level cells in the design, can be input/ output/ inoutport-------ports of current design, can be input/ output/ inoutpath group----Timing reports organized by path group。

pt静态时序分析流程

pt静态时序分析流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!PT(PrimeTime)是一种常用的静态时序分析工具,用于验证集成电路设计的时序性能。

Primetime对于PLL时钟设置

对于PLL,会被认为是黑盒子,时钟穿越不过.所以需要对pll创建qtm模型,再在输出端create_generated_clock;或者在pll输出端create clock,设置source latency。

create_clock -name SCLK -p 20[get_ports Sclk]create_clock -name PCLK -p 8[get_ports Pclk]create_generated_clock -name PCLKX8 -multiply_by 8 -source [get_attribute [get_clocks PCLK] sources] [get_pins PLL/pllx8]create_generated_clock -name sclk_gate -divide_by 1 -combinational -source [get_attribute [get_clocks SCLK] sources] [get_pins NAND2/Y]create_generated_clock -name clk_div2 -divide_by 2 -source [get_attribute [get_ports sclk_gate] sources][get_pins DIV/clk_div2]create_generated_clock -name clk_div4 -divide_by 4 -source [get_attribute [get_ports sclk_gate] sources][get_pins DIV/clk_div4]create_generated_clock -name clk_div8 -divide_by 8 -source [get_attribute [get_ports sclk_gate] sources][get_pins DIV/clk_div8]之只所以在门控时钟后面generated clock,因为到nand2的输出端有2条时钟路径。

EDA工具课程之PrimeTime

Company Logo

五、PrimeTime命令简介

虚假路径

set_false_path [-from from_list] [-through through_list] [-to to_list] pt_shell> set_false_path -from ff12 -to ff34 pt_shell> set_false_path -from ff1/CP -through {U1/Z U2/Z} -through {U3/Z U4/C} -to ff2/D pt_shell> foreach_in_collection clk1 [all_clocks] { foreach_in_collection clk [remove_from_collection [all_clocks] [get_clocks $clk1]] { set_false_path -from [get_clocks $clk1] -to [get_clocks $clk2]

pt_shell> set_clock_latency 1.2 -rise [get_clocks CLK1]

Company Logo

五、PrimeTime命令简介

时钟转换 set_clock_transition [-rise][-fall] [-min] [-max] transition clock_list

Company Logo

二、PrimeTime简介

PT和DC的STA的不同 1、目的不同 DC主要是为了综合,所以它的时序约束都是以苛刻的估算为主, 可以不区分什么分析类型,但PT主要是为了验证它的约束,主要以 来依赖于实际提取数据一提取的多数文件为主,必须区分什么操作 条件以及相应的什么分析类型策略。 2、级别不同 DC的综合是针对block的,所以它的时序约束也是针对预估的 block的时序要求来编写的,所以它是局部电路的时序约束。但PT 主要是针对系统的静态时序分析,所以它的时序约束主要是针对系 统的性能规格来编写,具有强制性和参照性。

PrimeTime使用说明(中文)

PrimeTime使⽤说明(中⽂)摘要:本⽂介绍了数字集成电路设计中静态时序分析(Static Timing Analysis)和形式验证(Formal Verification)的⼀般⽅法和流程。

这两项技术提⾼了时序分析和验证的速度,在⼀定程度上缩短了数字电路设计的周期。

本⽂使⽤Synopsys 公司的PrimeTime进⾏静态时序分析,⽤Formality进⾏形式验证。

由于它们都是基于Tcl(Tool Command Language)的⼯具,本⽂对Tcl也作了简单的介绍。

关键词:静态时序分析形式验证 PrimeTime Formality Tcl⽬录第⼀章绪论 (1)1.1 静态时序分析1.2 时序验证技术第⼆章PrimeTime简介 (3)2.1 PrimeTime的特点和功能2.2 PrimeTime进⾏时序分析的流程2.3 静态时序分析中所使⽤的例⼦2.4 PrimeTime的⽤户界⾯第三章Tcl与pt_shell的使⽤ (6)3.1 Tcl中的变量3.2 命令的嵌套3.3 ⽂本的引⽤3.4 PrimeTime中的对象3.4.1 对象的概念3.4.2 在PrimeTime中使⽤对象3.4.3 针对collection的操作3.5 属性3.6 查看命令第四章静态时序分析前的准备⼯作 (12)4.1 编译时序模型4.1.1 编译Stamp Model4.1.2 编译快速时序模型4.2 设置查找路径和链接路径4.3 读⼊设计⽂件4.4 链接4.5 设置操作条件和线上负载4.6 设置基本的时序约束4.6.1 对有关时钟的参数进⾏设置4.6.2 设置时钟-门校验4.6.3 查看对该设计所作的设置4.7 检查所设置的约束以及该设计的结构第五章静态时序分析 (18)5.1 设置端⼝延迟并检验时序5.2 保存以上的设置5.3 基本分析5.4 ⽣成path timing report5.5 设置时序中的例外5.6 再次进⾏分析第六章 Formality简介 (22)6.1 Formality的基本特点6.2 Formality在数字设计过程中的应⽤6.3 Formality的功能6.4 验证流程第七章形式验证 (27)7.1 fm_shell命令7.2 ⼀些基本概念7.2.1 Reference Design和Implementation Design 7.2.2 container7.3 读⼊共享技术库7.4 设置Reference Design7.5 设置Implementation Design7.6 保存及恢复所作的设置7.7 验证第⼋章对验证失败的设计进⾏Debug (32)8.1 查看不匹配点的详细信息8.2 诊断程序8.3 逻辑锥8.3.1 逻辑锥的概念8.3.2 查看不匹配点的逻辑锥8.3.3 使⽤逻辑锥来Debug8.3.4 通过逻辑值来分析第⼀章绪论我们知道,集成电路已经进⼊到了VLSI和ULSI的时代,电路的规模迅速上升到了⼏⼗万门以⾄⼏百万门。

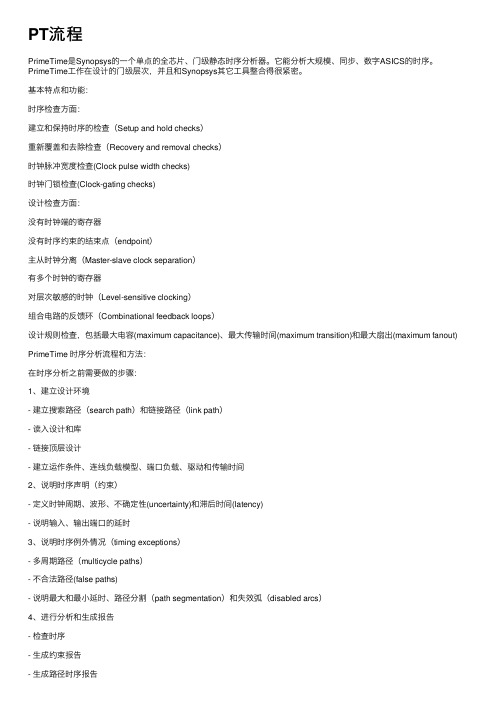

PT流程——精选推荐

PT流程PrimeTime是Synopsys的⼀个单点的全芯⽚、门级静态时序分析器。

它能分析⼤规模、同步、数字ASICS的时序。

PrimeTime⼯作在设计的门级层次,并且和Synopsys其它⼯具整合得很紧密。

基本特点和功能:时序检查⽅⾯:建⽴和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查⽅⾯:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有多个时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最⼤电容(maximum capacitance)、最⼤传输时间(maximum transition)和最⼤扇出(maximum fanout) PrimeTime 时序分析流程和⽅法:在时序分析之前需要做的步骤:1、建⽴设计环境- 建⽴搜索路径(search path)和链接路径(link path)- 读⼊设计和库- 链接顶层设计- 建⽴运作条件、连线负载模型、端⼝负载、驱动和传输时间2、说明时序声明(约束)- 定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)- 说明输⼊、输出端⼝的延时3、说明时序例外情况(timing exceptions)- 多周期路径(multicycle paths)- 不合法路径(false paths)- 说明最⼤和最⼩延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进⾏分析和⽣成报告- 检查时序- ⽣成约束报告- ⽣成路径时序报告开始先建⽴⽬录并将PrimeTime本⾝所带的⼀个例⼦拷到新建的⽬录下,在下⾯的内容中将要⽤到这个例⼦。

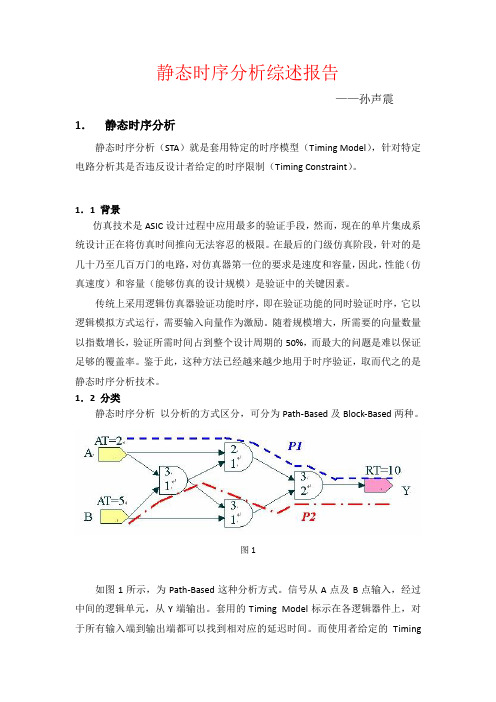

静态时序分析综述报告以及primetime简介

静态时序分析综述报告——孙声震1.静态时序分析静态时序分析(STA)就是套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

1.1 背景仿真技术是ASIC设计过程中应用最多的验证手段,然而,现在的单片集成系统设计正在将仿真时间推向无法容忍的极限。

在最后的门级仿真阶段,针对的是几十乃至几百万门的电路,对仿真器第一位的要求是速度和容量,因此,性能(仿真速度)和容量(能够仿真的设计规模)是验证中的关键因素。

传统上采用逻辑仿真器验证功能时序,即在验证功能的同时验证时序,它以逻辑模拟方式运行,需要输入向量作为激励。

随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,而最大的问题是难以保证足够的覆盖率。

鉴于此,这种方法已经越来越少地用于时序验证,取而代之的是静态时序分析技术。

1.2 分类静态时序分析以分析的方式区分,可分为Path-Based及Block-Based两种。

图1如图1所示,为Path-Based这种分析方式。

信号从A点及B点输入,经过中间的逻辑单元,从Y端输出。

套用的Timing Model标示在各逻辑器件上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的TimingConstraint为:1. 信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2. 信号B到达电路输入端的时间点为5(AT=5)。

3. 信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

针对P1及P2 两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑器件之后,由于有2单位的延迟时间,所以信号到达这个器件输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

使用PrimeTimePX进行功耗分析

使用PrimeTimePX进行功耗分析PTP某可以进行两种模式的功耗分析:l平均功耗分析(AveragedPowerAnalyi)在这种模式下,动态翻转速率可以是默认值或者是用户自定义的,也可以由HDL的仿真文件提供。

进行平均功耗分析时可以使用两种格式的激励文件,分别是SAIF和VCD。

l基于时序的功耗分析(Time-BaedPowerAnalyi)在这种模式下,为了获得精确的与时序有关的功耗信息,必须要有仿真文件提供激励。

Time-Baed支持VCD、VPD以及fdb格式的激励。

特别是对于VCD文件来说,可以支持RTL级别的仿真文件或者是Gate级别的仿真文件。

对于RTLLevel的VCD文件要使用read_vcd–rtl或者是read_vcd–zero_delay命令,否者会被识别成GateLevel的仿真文件。

二、PTP某工具进行功耗分析流程使用PTP某进行功耗分析之前,要准备如下文件:l逻辑综合后的.V文件l静态时序分析的.dc文件l有功耗信息的.db文件lRTL的仿真文件.VCD2.1.V文件、.dc文件以及.db文件的获得在使用DC完成对工程的综合后,会得到一个如下图所示的V文件(以本实验室综合所用工程rfid2022_v2为例,V文件存放在/rfid2022_v2/flow/yn/reult目录下):图2-1.V文件存放目录V文件里面的内容如下:图2-2综合后.V文件内容接下来获取.dc文件,PTP某用到的.dc文件和DC用到的.dc文件一致。

最后是.db文件,与.dc文件一样,.db文件也是综合时用到的.db文件。

需要注意的是这些db文件必须是具有功耗信息的。

2.2.VCD文件的获取.VCD文件指的是ValueChangeDump,VCD是IEEE1364标准中定义的一种ASCII文件,是通用的文件格式。

它主要包含了头信息,变量的预定义和变量值的变化信息。

正是因为它包含了信号的变化信息,就相当于记录了整个仿真的信息,我们可以用这个文件来再现仿真,也就能够显示波形。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4-4

Check for design rule and timing violations in the design

report_constraint -all_violators

n

To handle large problems use a divide and conquer method:

Simultaneous min/max Timing Models Advantages of analysis

Case analysis Creating Quick Timing Mode and its Application

On-Chip Variation Creating Quick Timing Mode and its Application

Use group_path to group paths of interest

4-5

group_path -name INPUTS -from [all_inputs] group_path -name OUTPUTS -to [all_outputs] report_constraint -all_violators report_timing -max_paths 5 -path short report_timing -group CLK

Agenda: Day One

DAY 1

4-1

Unit

Topic

Lab

1

Introduction to Static Timing Analysis

2

Advanced Clock Constraints

3

Timing Exceptions Advanced Timing Analysis Techniques

Simultaneous Min-Max Analysis

4-6

Using user defined path groups Creating Quick Timing Mode and its Application

Simultaneous min-max Timing Models Advantages of analysis

D Q

FF1

Organize paths for reports

A CLK

D Q

FF2

Байду номын сангаас

Z

Synopsys 37038-000-S13

Advanced Timing Analysis Techniques PrimeTime Workshop

Grouping Technique: Use group_path

l

l

n

With logic transitions:

l

PrimeTime uses only the specified transitions when timing through that particular cell

Synopsys 37038-000-S13

Advanced Timing Analysis Techniques PrimeTime Workshop

l

Divide paths into smaller groups with common specifications, analysis issues or solutions

An example of grouping timing paths

1 2 3

Input ports to registers Register to register Register to output ports

l

Use specific SDF, operating conditions and technology libraries for min and max calculations

n

Min-max values can also be specified for:

l l l l

Input and output delays Wire load models Clock attributes Driving cell and loads

Synopsys 37038-000-S13

Advanced Timing Analysis Techniques PrimeTime Workshop

What is Min-Max Analysis?

n

4-7

You can perform setup and hold analysis simultaneously

4

Synopsys 37038-000-S13

Advanced Timing Analysis Techniques PrimeTime Workshop

Unit Objectives

After completing this unit you should be able to:

n

4-2

State the command to create user defined path groups State 3 commands which can be used for simultaneous min-max analysis State 2 commands useful for case analysis State the command used for bottleneck analysis State the steps for an efficient static timing analysis methodology

Case analysis Creating Quick Timing Mode and its Application

On-Chip Variation Creating Quick Timing Mode and its Application

An efficient STA methodology Models Advantages of Timing

Advanced Timing Analysis Techniques PrimeTime Workshop

Synopsys 37038-000-S13

Case Analysis

4-9

Using user defined path groups Creating Quick Timing Mode and its Application

n

In this example, PrimeTime will:

l l

Calculate min delays for hold time analysis using cba_core_min Calculate max delays for setup time analysis using cba_core_max

4-8

pt_shell> set_operating_conditions -analysis_type bc_wc \ -min MIN -max MAX

… .or… .

pt_shell> read_sdf -analysis_type bc_wc ba_design.sdf

n

The read_min_max_lib command:

n

4-10

Case analysis allows you to perform timing analysis using logic constants or logic transitions on ports or pins With logic constants:

l

n

PrimeTime propagates the constant forward through the netlist PrimeTime automatically disables appropriate timing arcs based on the logic constant By default, constants do not propagate across sequential cells

Example Using Case Analysis

a

test_scan_in

4-11

D TI TE CP

Q

d e

b clk

test_scan_enable

D TI TE CP

Q

Setup and hold constraints disabled from clock to test input pin

Synopsys 37038-000-S13

Advanced Timing Analysis Techniques PrimeTime Workshop

How Do You Setup Min-Max Analysis?

pt_shell> read_min_max_lib -min cba_core_min.db \ -max cba_core_max.db -name min_max.db pt_shell> set link_path “* min_max.db” ; link_design

An efficient STA methodology Models Advantages of Timing

Synopsys 37038-000-S13

Advanced Timing Analysis Techniques PrimeTime Workshop

What is Case Analysis?

4-3

Simultaneous min-max Timing Models Advantages of analysis