VHDL试卷

EDA技术与VHDL期末考试试卷

一、单项选择题:(20分)1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__________。

DA .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

DA. 综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D. 综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的信号赋值语句,其信号更新是___C____。

A. 按顺序完成;B. 比变量更快完成;C. 在进程的最后完成;D. 都不对。

5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___________。

BA. 器件外部特性;B. 器件的内部功能;C. 器件的综合约束;D. 器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现________。

AA. 时序逻辑电路B. 组合逻辑电路C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_________。

B①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤B. ②③④C. ②⑤⑥D. ①④⑥8.下列标识符中,__________是不合法的标识符。

VHDL试卷6套

番茄花园一、 填空题( 分 每空格 分)、一个完整的 语言程序通常包含 实体( ) , 构造体( ), 配置( ), 包集合( )和 库( ) 各部分。

、在一个实体的端口方向说明时,输入使用 表示,那么构造体内部不能再使用的输出是用 表示;双向端口是用 表示;构造体内部可再次使用的输出是用 表示;、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

语言可以有以下 种形式的子结构描述语句: 语句结构; 语句结构和 结构。

、 的客体,或称数据对象包括了常数、 变量 和 信号 。

、请列出三个 语言的数据类型,如实数、位等。

位矢量 , 字符 , 布尔量 。

、设 为 为 为 为 的运算结果是“ , 的运算结果是“ 。

、构造体的描述方式包括三种,分别是 寄存器传输( )描述方法或称数据流 ; 构造体的结构描述方式 和 构造体的行为描述方式 。

、传统的系统硬件设计方法是采用自上而下( )的设计方法,利用硬件描述语言( )的硬件电路设计方法采用自下而上( )的设计方法。

(× )传统的系统硬件设计方法是采用自下而上( )的设计方法,利用硬件描述语言番茄花园( )的硬件电路设计方法采用自上而下( )的设计方法、 可以采用层次化的设计,一个高层的结构体中可以调用低层的实体 (√ )、一个 程序中仅能使用一个进程( )语句。

( × ) 可以使用多个进程语句。

、 语言的预算操作包括了逻辑运算符、关系运算符、乘法运算符等,它们三者的优先级是相同的。

( × ) 逻辑运算符 关系运算符 乘法运算、试举出两种可编程逻辑器件 、 。

、 程序的基本结构包括 库 、 程序包 、 实体和 结构体 。

、 标识符合法吗? 不合法 。

标识符合法吗? 不合法 。

标识符合法吗? 不合法 。

、信号的代入通常用 ,变量用 。

、表示‘ ’‘ ’;两值逻辑的数据类型是 (位) ,表示‘ ’‘ ’‘ 等九值逻辑的数据类型是 (标准逻辑),表示空操作的数据类型是 。

VHDL参考试题

一、选择题(共10分,每题2分)1.在一个VHDL设计中Idata是一个信号,数据类型为std_logic_vector,试指出下面赋值语句错误的是__ ___。

A. idata <= “00001111”;B. idata <= b”0000_1111”;C. idata <= X”AB”;D. idata <= B”21”;2.在VHDL语言中,下列对时钟边沿检测描述中,错误的是__ ___。

A. if clk’event and clk = ‘1’ thenB. if falling_edge(clk) thenC. if clk’event and clk = ‘0’ thenD. if clk’stable and not clk = ‘1’ then3.请指出Altera Cyclone系列中的EP1C6Q240C8这个器件是属于_____A. ROMB. CPLDC. FPGAD.GAL4.状态机编码方式中,其中一位热码编码占用触发器较多,但其实现比较适合_____的应用。

A. FPGAB. CPLDC. PALD.GAL5.进程中的信号赋值语句,其信号更新是_______。

a)按顺序完成;b)比变量更快完成;c)在进程的最后完成;d)都不对。

二、EDA名词解释(共10分,每题2分)1.ASIC2.FPGA3.VHDL4.EDA5.SOC三、程序补充题(共10分,每空1分)下面程序是一个10线-4线优先编码器的VHDL描述,试补充完整。

LIBRARY __________ ;USE IEEE._____________________.ALL;ENTITY coder ISPORT ( din : IN STD_LOGIC_VECTOR(____________________);output : __________ STD_LOGIC_VECTOR(3 DOWNTO 0) );END coder;ARCHITECTURE behav OF _____________ ISSIGNAL SIN : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS (___________)BEGINIF (din(9)='0') THEN SIN <= "1001" ;__________________ THEN SIN <= "1000" ;ELSIF (din(7)='0') THEN SIN <= "0111" ;ELSIF (din(6)='0') THEN SIN <= "0110" ;ELSIF (din(5)='0') THEN SIN <= "0101" ;ELSIF (din(4)='0') THEN SIN <= "0100" ;ELSIF (din(3)='0') THEN SIN <= "0011" ;ELSIF (din(2)='0') THEN SIN <= "0010" ;ELSIF (din(1)='0') THEN SIN <= "0001" ;ELSE _______________ ;________________END PROCESS ;_______________;END behav;四、程序改错题(共15分)仔细阅读下列程序,改正程序中的错误并说明该程序的功能。

VHDL程序练习题(含答案)

VHDL程序填空题(一)在下面横线上填上合适的VHDL关键词,完成2选1多路选择器的设计。

LIBRARY IEEE;USE IEEE。

STD_LOGIC_1164.ALL;1 MUX21 ISPORT(SEL:IN STD_LOGIC;A,B:IN STD_LOGIC;Q:OUT STD_LOGIC );END MUX21;2 BHV OF MUX21 ISBEGINQ<=A WHEN SEL=’1’ ELSE B;END BHV;(二)在下面横线上填上合适的语句,完成BCD—7段LED显示译码器的设计。

LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164。

ALL;ENTITY BCD_7SEG ISPORT(BCD_LED :IN STD_LOGIC_VECTOR(3 DOWNTO 0);LEDSEG :OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END BCD_7SEG;ARCHITECTURE BEHA VIOR OF BCD_7SEG ISBEGINPROCESS(BCD_LED)3IF BCD_LED="0000” THEN LEDSEG<=”0111111”;ELSIF BCD_LED=”0001” THEN LEDSEG<="0000110”;ELSIF BCD_LED=”0010" THEN LEDSEG<= 4 ;ELSIF BCD_LED=”0011" THEN LEDSEG<=”1001111";ELSIF BCD_LED=”0100" THEN LEDSEG<="1100110";ELSIF BCD_LED=”0101" THEN LEDSEG〈="1101101";ELSIF BCD_LED=”0110" THEN LEDSEG〈=”1111101";ELSIF BCD_LED=”0111" THEN LEDSEG〈="0000111";ELSIF BCD_LED="1000" THEN LEDSEG〈=”1111111”;ELSIF BCD_LED="1001” THEN LEDSEG<="1101111”;ELSE LEDSEG<= 5 ;END IF;END PROCESS;END BEHA VIOR;(三) 在下面横线上填上合适的语句,完成数据选择器的设计。

VHDL各年试卷集合

答:迭代的思想是利用问题本身包含的结构特性,用简单的逻辑子网络代替复杂的组合逻 辑网络,实现要求的处理功能。从而最大限度降低了逻辑网络的设计难度,简化了设计过 程,提高系统的性能/价格比。 (2) 常用的迭代技术有时间迭代、空间迭代,也可以是两者的组合。 (1) 时间迭代速度慢,硬件简单。 ( 1) 空间迭代速度快,硬件复杂。 ( 1)

4 / 54

3、假设法 fadd4 是已经描述好的元件

Entity fadd8 is port ( a , b : in std_logic_vector(7 downto 0) ; ci: in std_logic; co: out std_logic; sum: out std_logic_vector (7downto 0)); End fadd8 ; Architecture stru of fadd8 is Component fadd4 port ( a , b: in std_logic_vector(3 downto 0) ; ci: in std_logic; co: out std_logic; sum: out std_logic_vector (3 downto 0) ); End component; Signal carry_out : std_logic ; Begin U1: fadd4 port map( a( 3 downto 0), b(3 downto 0), ci, carry_out, sum(3 downto 0); U2: fadd4 port map( a( 7 downto 4), b(7 downto 4), carry_out, co, sum(7 downto 4); End stru;

1 1 0 0 0

C1

vhdl期末考试题库及答案

vhdl期末考试题库及答案VHDL期末考试题库及答案一、选择题1. VHDL是一种用于电子设计自动化的硬件描述语言,主要用于描述什么?A. 软件程序B. 硬件电路C. 数据库D. 操作系统答案:B2. 在VHDL中,哪个关键字用于定义一个进程?A. processB. procedureC. functionD. package答案:A3. 下列哪个不是VHDL的预定义数据类型?A. bitB. integerC. realD. boolean答案:A4. VHDL中,哪个属性用于获取信号的稳定值?A. 'stable'B. 'event'C. 'quiet'D. 'transaction'答案:A5. 在VHDL中,以下哪个是合法的信号赋值语句?A. signal a : integer := 5;B. signal a : integer is 5;C. signal a <= 5;D. signal a : integer = 5;答案:C二、简答题1. 简述VHDL中的并发语句和顺序语句的区别。

答案:并发语句用于描述多个独立操作同时发生,如进程和并行块;顺序语句描述操作的顺序执行,如if语句、case语句等。

2. 解释VHDL中的时序仿真和功能仿真的区别。

答案:时序仿真考虑了信号的时序特性,如延迟和时间,用于验证设计在实际工作条件下的行为;功能仿真则不关心时序,只验证设计的功能正确性。

三、编程题1. 编写一个VHDL程序,实现一个简单的二进制加法器。

答案:```vhdlentity adder isport(A, B : in bit_vector(1 downto 0);Sum : out bit_vector(1 downto 0);Carry : out bit);end entity adder;architecture behavior of adder isbeginprocess(A, B)begincase A iswhen "00" => Sum <= "00"; Carry <= '0';when "01" => Sum <= "01"; Carry <= '0';when "10" => Sum <= "01"; Carry <= '0';when "11" => Sum <= "10"; Carry <= '1';end case;end process;end architecture behavior;```四、论述题1. 论述在VHDL中使用测试平台(testbench)的重要性。

EDA-(VHDL版)考试试卷汇总

一、单项选择题:(20分)1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为D 。

A .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

DA.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的信号赋值语句,其信号更新是___C____。

A. 按顺序完成;B.比变量更快完成;C.在进程的最后完成;5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述BA.器件外部特性;B. 器件的内部功能;C.器件的综合约束;D.器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现AA. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化B①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤B. ②③④C. ②⑤⑥D. ①④⑥8.下列标识符中,__________是不合法的标识符。

VHDL期末考试卷

component dff

port(d:in std_logic;

clk:in std_logic;

q:out std_logic);

end component;

第1页(共2页)

signal q_temp:std_logic_vector(4 downto 1);

5.过程调用语句有两种方式:____________和_____________。

6.函数参数(形参)的数据类型只能是_______和________;参数的端口模式只能是_____。

7. VHDL中的重载有两种:_____________和______________。

8. clk的下降沿描述方法为:_________________________。

一、填空题:(每题1分,共20分)

1.在std_logic类型中,_____、_____和_____三种值不能够被综合所支持。

2. MOD和REM运算只能够用于________类型数据的运算。

3.变量是一种局部量,只能在______语句、_____语句以及_______语句中的说明部分进行说明。

4.在结构体中,并行处理语句包括5种:__________、__________、__________、__________、__________。

END display_decoder;

3.编写异步置位/复位的D触发器程序。要求S为置位端(低电平有效),R为复位端(低电平有效),CP为时钟脉冲(上升沿有效),Q和QB为输出。(15分)

第2页(共2页)

二、简答题:(每题5分,共20分)

1.在VHDL中,一个设计实体由哪几部分组成?其中哪些是必须的?

VHDL合肥工业大学期末试题(含答案)2008-2009A

合肥工业大学2009/2010 学年第一学期末考试试题答案及评分标准(A卷)一、填空题(20分,每空格1分)1、一个完整的VHDL语言程序通常包含实体(entity),构造体(architecture),配置(configuration),包集合(package)和库(library) 5各部分。

2、在一个实体的端口方向说明时,输入使用in表示,那么构造体内部不能再使用的输出是用 out 表示;双向端口是用 inout 表示;构造体内部可再次使用的输出是用 buffer 表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句: BLOCK 语句结构; PROCESS 语句结构和SUBPROGRAMS 结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0为'0', D1为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3的运算结果是“0010”,D3 & D2 & D1 & D0的运算结果是“0100”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

二、判断对错并给出判断依据(20分,每小题5分,判断对错2分,给出正确答案3分)1、传统的系统硬件设计方法是采用自上而下(top down)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自下而上(bottom up)的设计方法。

(×)传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自上而下(top down)的设计方法3、一个VHAL程序中仅能使用一个进程(process)语句。

VHDL试卷6套

填空题(20分,每空格1 分)1、一个完整的VHDL语言程序通常包含实体(entity ) , 构造体(architecture ),酉己置 (configuration ),包集合(package)禾和库(library ) 5 各部分。

2、在一个实体的端口方向说明时,输入使用in表示,那么构造体内部不能再使用的输出是用out 表示;双向端口是用in out 表示;构造体内部可再次使用的输出是用buffer表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句:BLOCK 语句结构;PROCESS语句结构和SUBPROGRAMS结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0 为'0', D1 为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3 的运算结果是“ 0010”,D3 & D2 & D1 & D0 的运算结果是“ 0100 ”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

1、传统的系统硬件设计方法是采用自上而下(top down )的设计方法,利用硬件描述语言(HDL的硬件电路设计方法采用自下而上 (bottom up)的设计方法。

(X )传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL 的硬件电路设计方法采用自上而下(top down )的设计方法2、VHDL可以采用层次化的设计,一个高层的结构体中可以调用低层的实体(V )3、一个VHAL程序中仅能使用一个进程(process )语句。

VHDL合肥工业大学期末试题(含答案)2007-2008A

合肥工业大学2007/2008 学年第一学期末考试试题答案及评分标准(A卷)一、填空题(20分,每空格1分)1、VHDL是否区分大小写?不区分。

2、digital_ _8标识符合法吗?不合法。

12_bit标识符合法吗?不合法。

signal标识符合法吗?不合法。

3、结构体有三种描述方式,分别是数据流、行为、和结构化。

4、请分别列举一个常用的库和程序包library ieee 、use ieee.std_logic_1164.all 。

5、一个信号处于高阻(三态)时的值在VHDL中描述为‘Z’。

6、将一个信号width定义为一个4位标准逻辑向量为signal width : std_logic_vector(3 downto 0) 。

7、/=是不相等操作符,功能是在条件判断是判断操作符两端不相等。

8、设D0为'0', D1为'1', D2为'1', D3为'0', D3 & D2 & D1 & D0的运算结果是“0110”,(D3 or D2)and(D1 and not D0)的运算结果是:‘1’。

9、赋值语句是(并行/串行)并行执行的,if语句是(并行/串行)串行执行的。

10、请列举三种可编程逻辑器件: EEPROM 、 GAL 、 FPGA 。

二、简答(20分,每小题5分)1、简述VHDL程序的基本结构。

程序包(2)实体(3)结构体(5)若答出配置也可加1分2、简述信号与变量的区别。

信号延时赋值,变量立即赋值(2)信号的代入使用<=,变量的代入使用:=;(4)信号在实际的硬件当中有对应的连线,变量没有(5)3、简述可编程逻辑器件的优点。

●集成度高,可以替代多至几千块通用IC芯片–极大减小电路的面积,降低功耗,提高可靠性(1)●具有完善先进的开发工具–提供语言、图形等设计方法,十分灵活–通过仿真工具来验证设计的正确性(2)●可以反复地擦除、编程,方便设计的修改和升级(3)●灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间(4)●保密性好(5)4、试比较moore状态机与mealy状态机的异同。

VHDL试卷6套

一、填空题(20分,每空格1分)1、一个完整的VHDL语言程序通常包含实体(entity),构造体(architecture),配置(configuration),包集合(package)和库(library) 5各部分。

2、在一个实体的端口方向说明时,输入使用in表示,那么构造体内部不能再使用的输出是用 out 表示;双向端口是用 inout 表示;构造体内部可再次使用的输出是用 buffer 表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句: BLOCK 语句结构; PROCESS 语句结构和SUBPROGRAMS 结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0为'0', D1为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3的运算结果是“0010”,D3 & D2 & D1 & D0的运算结果是“0100”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

1、传统的系统硬件设计方法是采用自上而下(top down)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自下而上(bottom up)的设计方法。

(×)传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自上而下(top down)的设计方法2、VHDL可以采用层次化的设计,一个高层的结构体中可以调用低层的实体(√)3、一个VHAL程序中仅能使用一个进程(process)语句。

vhdl 试题

一、填空题1. 在VHDL中最常用的IEEE标准库是std_logic_1164数据包。

VHDL是一种硬件描述语言。

3. 可编程控制器所使用的软件主要是Alter公司的Quartus_软件进行开发设计和仿真。

4. 可编程控制器是针对PLD的可编程使用HDL语言,其中PLD的意思是_ 可编程逻辑器件_,HDL的意思是____硬件描述语言___________。

VHDL中,下降沿的描述语言是___clk'event and clk='0'(下降沿)clk'event and clk='1'(上升沿)____________。

6. 实体的关键字是___Entity________,变量的关键字是___Port____________。

PLA是同时对__与____和“或”阵列,而PAL只对__与_______进行变成。

8. 两位逻辑变量的取值有四个,分别是___“00”“01”“10”“11”__________________(要求用程序中的书写格式表示)。

9. 在可VHDL语言中,‘Z’表示______高阻抗_______状态,‘-’表示______忽略________________。

10. 调用标准程序包的调用语句是____use ieee.std_logic_1164.all_____________________________________。

process语句中必须加上敏感信号_________列表,以__End process;____________结束。

12. 信号的赋值用___<=______,变量的赋值用____:=______。

VHDL程序的基本结构由库、程序包、__实体________、__结构体______和配置等部分组成。

14. 可编程控制器是针对PLD的可编程使用HDL语言,其中PLD的意思是__可编程逻辑器件______,HDL的意思是____硬件描述语言_________。

VHDL试题

VHDL试题1.结构体的三种描述⽅式:-⾏为描述-数据流描述-结构化描述2.⼀般将⼀个完整的VHDL程序称为设计实体3. VHDL设计实体的基本结构由库、程序包、实体、结构体和配置组成。

4.VHDL不区分⼤⼩写。

5.常⽤的库:library ieee ,程序包:use ieee.std_logic_1164.all6.VHDL程序的基本结构⾄少应包括实体、结构体和对库的引⽤声明。

7.在VHDL程序中使⽤的⽂字、数据对象、数据类型都需要事先声明。

8. VHDL的实体由实体声明和结构体组成。

VHDL的实体声明部分指定了设计单元的输⼊出端⼝或引脚,它是设计实体对外的⼀个通信界⾯,是外界可以看到的部分。

VHDL的结构体⽤来描述实体的逻辑结构和逻辑功能,它由VHDL语句构成,是外界看不到的部分。

9.端⼝⽅向模式:IN(输⼊)、OUT(输出<构造体内部不能再使⽤>)、INOUT(双向)、BUFFER (缓冲<构造体内部可再使⽤>)10.VHDL的标识符名必须以(字母开头),后跟若⼲字母、数字或单个下划线构成,但最后不能为(下划线),不能连续两个下划线相连。

11. 为信号赋初值的符号是(:=);程序中,为变量赋值的符号是(:=),为信号赋值的符号是(<=)12. VHDL的数据类型包括标量类型、复合类型、存储类型和⽂件类型请列出3个VHDL语⾔的数据类型,如实数、位等。

位⽮量,字符,布尔量,整数,字符串,时间,错误等级,⾃然数,正整数。

13. VHDL的操作符包括逻辑、算术、关系和并置四类14.可编程逻辑器件:CPLD、FPGA、GAL、PLA、PAL(早期)CPLD(复杂可编程逻辑器件):基于乘机项技术构造的可编程逻辑器件,不需要配置外部程序寄存芯⽚FPGA(现场可编程门阵列):基于查找表技术构造的可编程逻辑器件,需要配置外部程序寄存芯⽚15.VHDL客体或数据对象:常量、信号、变量(可被多次赋值)、⽂件。

EDA技术(VHDL)试卷及答案

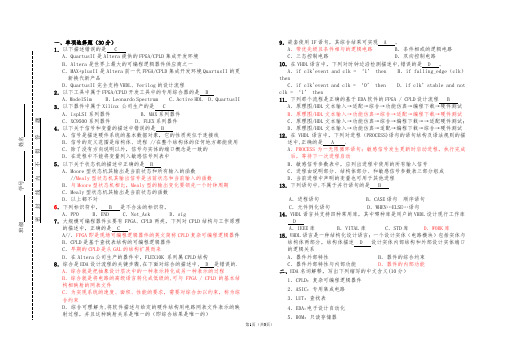

班级 学号 姓名密 封 线 内 不 得 答 题一、单项选择题(30分) 1.以下描述错误的是 CA .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境B .Altera 是世界上最大的可编程逻辑器件供应商之一C .MAX+plusII 是Altera 前一代FPGA/CPLD 集成开发环境QuartusII 的更新换代新产品D .QuartusII 完全支持VHDL 、Verilog 的设计流程2.以下工具中属于FPGA/CPLD 开发工具中的专用综合器的是 BA .ModelSimB .Leonardo SpectrumC .Active HDLD .QuartusII 3.以下器件中属于Xilinx 公司生产的是 CA .ispLSI 系列器件B .MAX 系列器件C .XC9500系列器件D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 BA .信号是描述硬件系统的基本数据对象,它的性质类似于连接线B .信号的定义范围是结构体、进程 //在整个结构体的任何地方都能使用C .除了没有方向说明以外,信号与实体的端口概念是一致的D .在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 BA .Moore 型状态机其输出是当前状态和所有输入的函数//Mealy 型状态机其输出信号是当前状态和当前输入的函数B .与Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期C .Mealy 型状态机其输出是当前状态的函数D .以上都不对6.下列标识符中, B 是不合法的标识符。

A .PP0B .ENDC .Not_AckD .sig7.大规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是 C 。

A//.FPGA 即是现场可编程逻辑器件的英文简称CPLD 复杂可编程逻辑器件 B .CPLD 是基于查找表结构的可编程逻辑器件 C .早期的CPLD 是从GAL 的结构扩展而来D .在Altera 公司生产的器件中,FLEX10K 系列属CPLD 结构8.综合是EDA 设计流程的关键步骤,在下面对综合的描述中, D 是错误的.A .综合就是把抽象设计层次中的一种表示转化成另一种表示的过程B .综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件C .为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束D .综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)9.嵌套使用IF 语句,其综合结果可实现 A 。

vhdl期末考试试题及答案

vhdl期末考试试题及答案VHDL期末考试试题一、选择题(每题2分,共20分)1. VHDL是一种用于描述______的硬件描述语言。

A. 软件程序B. 硬件电路C. 数据结构D. 操作系统2. 在VHDL中,以下哪个关键字用于定义实体的端口?A. entityB. portC. endD. begin3. VHDL中,以下哪个语句用于定义信号的初始值?A. initialB. defaultC. initial_valueD. none of the above4. 以下哪个是VHDL中的基本数据类型?A. integerB. realC. stringD. array5. 在VHDL中,以下哪个关键字用于定义进程?A. processB. procedureC. functionD. block6. VHDL中,以下哪个属性用于获取信号的稳定值?A. 'stableB. 'eventC. 'last_valueD. 'delayed7. 在VHDL中,以下哪个语句用于实现条件语句?A. ifB. caseC. selectD. when8. 以下哪个是VHDL中用于描述时序逻辑的语句?A. processB. concurrentC. sequentialD. none of the above9. VHDL中,以下哪个关键字用于定义常量?A. constantB. variableC. signalD. type10. 在VHDL中,以下哪个属性用于获取信号的上升沿?A. 'eventB. 'last_eventC. 'rising_edgeD. 'falling_edge二、简答题(每题5分,共20分)1. 解释VHDL中的实体和结构体的区别。

2. 描述VHDL中进程的工作原理。

3. 什么是VHDL中的并发语句,它们有什么特点?4. 解释VHDL中的信号和变量的区别。

(完整版)EDA-(VHDL版)考试试卷汇总

一、单项选择题:(20分)1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为D 。

A .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

DA.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的信号赋值语句,其信号更新是___C____。

A. 按顺序完成;B.比变量更快完成;C.在进程的最后完成;5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述BA.器件外部特性;B. 器件的内部功能;C.器件的综合约束;D.器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现AA. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化B①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤B. ②③④C. ②⑤⑥D. ①④⑥8.下列标识符中,__________是不合法的标识符。

试卷 vhdl 湖南科技大学

简答题20分填空题10分选择题10分程序分析题3题30分编程题3题30分1.课本中第八章中逻辑电路设计,是考试重点,一些程序和类似程序会在考试中以程序分析题和编程题形式出现。

(以课本及上课PPT为参考)2.除了第八章外,例1-1 例1-2 例5-2 例5-5例6-8 例6-9 例6-10 例6-12 例6-13,这些程序也很经典,1.VHDL 的全称是什么?利用它设计硬件电路有哪些优点?答:VHDL 的全称Very High Speed Integrated Circuit Hardware Description Language(超高速集成电路硬件描述语言,利用VHDL 设计硬件电路具有以下特点:(1)设计文件齐全、方法灵活、支持广泛(2)系统硬件描述能力强(3)VHDL 语言可以与工艺无关编程(4)VHDL 语言标准、规范、易于共享和复用2.一个完整的VHDL语言程序由哪几个部分构成,每个部分作用是什么。

答:一个完整的VHDL语言程序由库,包集合,实体,构造体和配置五个部分组成。

库包含若干个包集合,确定程序所需要调用的函数,数据类型等;包集合内存有具体函数,数据类型的定义;实体说明系统的端口与类属参数;构造体完成系统内部逻辑关系与具体电路的实现;配置则说明实体与构造体的连接关系,通过配置,同一实体可搭配不同构造体。

3.简述VHDL语言构造体的描述方式及各自特点。

答:行为描述,RTL描述方式,结构描述方式。

行为描述主要是对系统数学模型的描述,一般进行仿真难以进行逻辑综合;RTL描述主要是对系统内部构造与逻辑关系的描述,可以进行逻辑综合;结构描述大量使用模块化描述方式,采用component语句,block语句,便于实现积木化结构,能够进行逻辑综合。

4.VHDL 语言中客体的概念及使用范围VHDL 语言中可以赋予一个值的对象称为客体;客体主要包括三种:信号、常数、变量;信号和常数为全局量,变量为局部量5.请从申明格式、赋值符号、赋值生效时间、作用范围等方面对信号和变量进行比较分析。

EDA技术与VHDL期末考试试卷

EDA技术与VHDL期末考试试卷一、单项选择题:(20分)二、1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__________。

D三、A .瘦IP B.固IP C.胖IP D.都不是四、五、2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

D六、A. 综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;七、B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;八、C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;九、D. 综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

十、十一、3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

十二、A. FPGA全称为复杂可编程逻辑器件;十三、B. FPGA是基于乘积项结构的可编程逻辑器件;十四、C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;十五、D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

十六、十七、4.进程中的信号赋值语句,其信号更新是___C____。

十八、A. 按顺序完成;十九、B. 比变量更快完成;二十、C. 在进程的最后完成;二十一、D. 都不对。

5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___________。

B二十二、A. 器件外部特性;二十三、B. 器件的内部功能;二十四、C. 器件的综合约束;二十五、D. 器件外部特性与内部功能。

二十六、二十七、6.不完整的IF语句,其综合结果可实现________。

A二十八、A. 时序逻辑电路 B. 组合逻辑电路二十九、C. 双向电路 D. 三态控制电路三十、三十一、7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_________。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL试卷2009/2010 学年第一学期末考试试题答案及评分标准(A卷)一、填空题(20分,每空格1分)1、一个完整的VHDL语言程序通常包含实体(entity),构造体(architecture),配置(configuration),包集合(package)和库(library) 5各部分。

2、在一个实体的端口方向说明时,输入使用in 表示,那么构造体内部不能再使用的输出是用out 表示;双向端口是用 inout 表示;构造体内部可再次使用的输出是用 buffer 表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句: BLOCK 语句结构; PROCESS 语句结构和SUBPROGRAMS结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0为'0', D1为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3的运算结果是“0010”, D3 & D2 & D1 & D0的运算结果是“0100”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

20分,每小题5分,判断对错2分,给出正确答案3分)1、传统的系统硬件设计方法是采用自上而下(top down)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自下而上(bottom up)的设计方法。

(×)传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自上而下(top down)的设计方法2、VHDL可以采用层次化的设计,一个高层的结构体中可以调用低层的实体(√)13、一个VHAL程序中仅能使用一个进程(process)语句。

(×)可以使用多个进程语句。

4、VHDL语言的预算操作包括了逻辑运算符、关系运算符、乘法运算符等,它们三者的优先级是相同的。

(×)逻辑运算符<关系运算符<乘法运算10分)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;以上库和程序包语句有无错误?有,有的话请在原程序相应位置改正。

(2)entity rom isport(addr: in std_logic_vector(0 to 3);2ce: in std_logic;data:out std_logic_vector(7 downto 0) ;);end rom;以上port语句有无错误?有,有的话请在原程序相应位置改正。

(4)architecture behave of rom isbeginprocess(ce,addr)beginif ce='0' then (6)case addr is when "0000"=>data<="10001001";when "0001"=>3data<="10001010";when "0010"=>data<="10001011";when "0011"=>data<="10001100";when "0100"=>data<="10001101";when "0101"=>data<="10001110";when "0110"=>data<="10001111";when "0111"=>data<="10010000";when "1000"=>data<="10010001";when "1001"=>data<="10010010";when "1010"=>data<="10010011";when "1011"=>data<="10010100";when "1100"=>data<="10010101";when "1101"=>4data<="10010110";when "1110"=>data<="10010111";when others=>|data<="10011000"; | end case;(8)elsedata<="00000000";end if;end process;(10)end behave;以上architecture中有哪些错误?请在原程序相应位置改正。

50分)1、请补全以下二选一VHDL程序(本题10分)Entity mux isport(d0,d1,sel:in bit;q:out BIT );5(2)end mux;architecture connect of MUX is (4)signal tmp1, TMP2 ,tmp3:bit;(6)begincale:blockbegintmp1<=d0 and sel;tmp2<=d1 and (not sel)tmp3<= tmp1 and tmp2;q <= tmp3;(8)end block cale;end CONNECT ;(10)672、编写一个2输入与门的VHDL 程序,请写出库、程序包、实体、构造体相关语句,将端口定义为标准逻辑型数据结构(本题10分)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;(2) ENTITY nand2 ISPORT (a ,b:IN STD_LOGIC;(4) y:OUT STD_LOGIC);(6)END nand2; ARCHITECTURE nand2_1 OF nand2 IS (8)BEGIN y <= a NAND b; --与y <=NOT( a AND b);等价 (10)END nand2_1;3、根据下表填写完成一个3-8线译码器的VHDL 程序(16分)。

& a b yLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder_3_to_8 ISPORT (a,b,c,g1,g2a,g2b:IN STD_LOGIC;y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); (2)END decoder_3_to_8;ARCHITECTURE rtl OF decoder_3_to_8 IS SIGNAL indata:STD_LOGIC_VECTOR (2 DOWNTO 0); (4)8BEGINindata <= c & b & a;(6)PROCESS (indata,g1,g2a,g2b)BEGINIF (g1 = '1' AND g2a = '0' AND g2b = '0' ) THEN (8)CASE indata ISWHEN "000"=> y <= "11111110";WHEN "001" => y <= "11111101";WHEN "010" => y <= "11111011"; (10)WHEN "011" => y <= "11110111";WHEN "100" => y <= "11101111";WHEN "101" => y <= "11011111";WHEN "110" => y <= "10111111"; (12)WHEN "111" => y <= "01111111";WHEN OTHERS=> y <= "XXXXXXXX";END CASE;ELSEy <= "11111111";(14)END IF;END PROCESS; (16)END rtl;4、三态门电原理图如右图所示,真值表如左图所示,请完成其VHDL程序构造体部分。

(本题14分)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY tri_gate ISPORT(din,en:IN STD_LOGIC;dout : OUT STD_LOGIC); END tri_gate ;ARCHITECTURE zas OF tri_gate IS BEGINP ROCESS (din,en)BEGINIF (en=‘1') THEN dout <= din;ELSE dout <= ‘Z’;END IF;END PROCESS ; END zas ;2008/2009 学年第一学期末考试试题答案及评分标准(A卷)一、填空题(20分,每空格1分)1、试举出两种可编程逻辑器件 CPLD 、FPGA 。

2、VHDL程序的基本结构包括库、程序包、实体和结构体。