微电子器件基础题

微电子学基础考核试卷

B.高压测试

C.高速开关测试

D.热循环测试

10.以下哪些技术被用于微电子器件的互连技术?()

A.铝互连

B.铜互连

C.金互连

D.硅互连

11.下列哪些因素会影响集成电路的功耗?()

A.电压

B.频率

C.电路设计

D.制造工艺

12.以下哪些属于CMOS工艺的优点?()

A.低功耗

B.高集成度

C.宽工作电压范围

3. NMOS晶体管在_______电平下导通,而PMOS晶体管在_______电平下导通。

4.微电子器件的_______测试是用来检测器件在高温条件下的性能稳定性。

5.金属-氧化物-半导体(MOS)结构中,金属通常指的是_______。

6.在微电子器件设计中,_______是指电路中电流流动的路径。

D.硼磷硅玻璃

6.数字集成电路的逻辑功能测试主要包括()

A.功能测试

B.真值表测试

C.边沿测试

D.状态机测试

7.以下哪些是功率MOSFET的特点?()

A.高电压

B.高电流

C.低导通电阻

D.高开关频率

8.下列哪些是集成电路封装的作用?()

A.保护芯片

B.电气连接

C.散热

D.防止信号干扰

9.半导体器件的可靠性测试中,以下哪些测试方法可以用来评估器件的寿命?()

D.易于与BiCMOS工艺兼容

13.下列哪些是微电子器件设计中考虑的安全因素?()

A.电磁兼容性

B.静电放电

C.过压保护

D.短路保护

14.以下哪些技术被用于提高集成电路的散热性能?()

A.散热片

B.热管

C.热电冷却器

电子科技大学微电子器件 (习题解答)

s Emax

qND

在

x

xi2 处,E3

Emax

q

s

NA xp

,

由此得:xp

s Emax

qNA

(2) 对于无 I 型区的PN结,

xi1 0,

xi2 0,

E1

q

s

ND (x

xn ),

E3

q

s

NA(x

xp )

在

x

0 处,电场达到最大, Emax

q

s

ND xn

q

s

NA xp

E

Emax

E1

E3

x

0

表面上,两种结构的 Emax 的表达式相同,但由于两种结构 的掺杂相同,因而Vbi 相同(即电场曲线与横轴所围面积相同), 所以两种结构的 xn、xp与 Emax 并不相同。

WB

dWB dVCE

0 NBdx

IC VA

WB

VA 0 NBdx

N

B

(WB

)

dWB dVCE

对均匀基区,VA

WB dWB dVCE

式中,dWB dxdB , VCE VCB VBE

因

VBE

保持不变,所以 dVCE

dVCB ,

于是:VA

WB dxdB dVCB

1

xdB

2s N

2DB n

,

将n

106 s 及 WB 、DB

之值代入,得: 0.9987。

7、

b

WB2 2DB

2

1

1

1.1251011(s)

8、以 NPN 管为例,当基区与发射区都是非均匀掺杂时, 由式(3-33a)和式(3-33b),

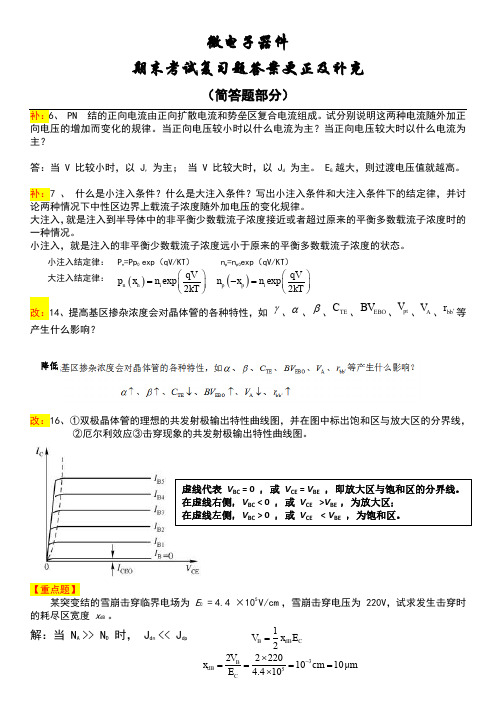

微电子器件 简答题 答案更正

微电子器件

期末考试复习题答案更正及补充

(简答题部分)

主?

答:当 V 比较小时,以 J r 为主; 当 V 比较大时,以 J d 为主。

E G 越大,则过渡电压值就越高。

补:7 、 什么是小注入条件?什么是大注入条件?写出小注入条件和大注入条件下的结定律,并讨论两种情况下中性区边界上载流子浓度随外加电压的变化规律。

大注入,就是注入到半导体中的非平衡少数载流子浓度接近或者超过原来的平衡多数载流子浓度时的一种情况。

改:14、提高基区掺杂浓度会对晶体管的各种特性,如 γ、α、β、

TE C 、EBO BV 、pt V 、A V 、bb r '等

产生什么影响?

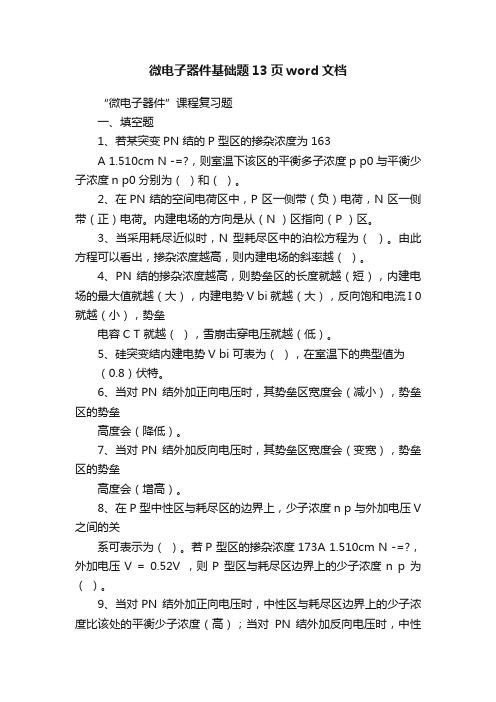

改:16、①双极晶体管的理想的共发射极输出特性曲线图,并在图中标出饱和区与放大区的分界线,

②厄尔利效应③击穿现象的共发射极输出特性曲线图。

【重点题】

某突变结的雪崩击穿临界电场为 E C = 4.4 ×105 V/cm ,雪崩击穿电压为 220V ,试求发生击穿时

的耗尽区宽度 x dB 。

解:当 N A >> N D 时, J dn << J dp

降低

虚线代表 V BC = 0 ,或 V CE = V BE ,即放大区与饱和区的分界线。

在虚线右侧,V BC < 0 ,或 V CE >V BE ,为放大区;

在虚线左侧,V BC > 0 ,或 V CE < V BE ,为饱和区。

B dB

C 3B dB 5C 12

2222010cm 10μm 4.410V x E V x E -=⨯====⨯。

微电子器件复习题

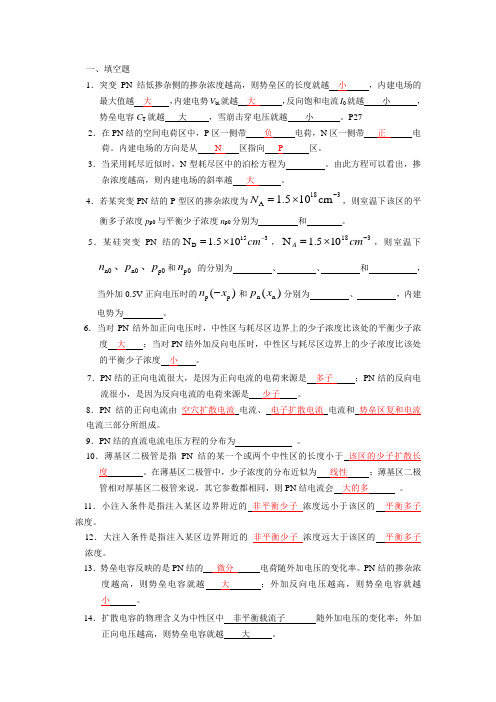

一、填空题1.突变PN 结低掺杂侧的掺杂浓度越高,则势垒区的长度就越 小 ,建电场的最大值越 大 ,建电势V bi 就越 大 ,反向饱和电流I 0就越 小 ,势垒电容C T 就越 大 ,雪崩击穿电压就越 小 。

P272.在PN 结的空间电荷区中,P 区一侧带 负 电荷,N 区一侧带 正 电荷。

建电场的方向是从 N 区指向 P 区。

3.当采用耗尽近似时,N 型耗尽区中的泊松方程为 。

由此方程可以看出,掺杂浓度越高,则建电场的斜率越 大 。

4.若某突变PN 结的P 型区的掺杂浓度为183A 1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为 和 。

5.某硅突变PN 结的153D N 1.510cm -=⨯,31810.51N -⨯=cm A ,则室温下n0n0p0n p p 、、和p0n 的分别为 、 、 和 ,当外加0.5V 正向电压时的p p ()n x -和n n ()p x 分别为 、 ,建电势为 。

6.当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度 大 ;当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度 小 。

7.PN 结的正向电流很大,是因为正向电流的电荷来源是 多子 ;PN 结的反向电流很小,是因为反向电流的电荷来源是 少子 。

8.PN 结的正向电流由 空穴扩散电流 电流、 电子扩散电流 电流和 势垒区复和电流 电流三部分所组成。

9.PN 结的直流电流电压方程的分布为 。

10.薄基区二极管是指PN 结的某一个或两个中性区的长度小于 该区的少子扩散长度 。

在薄基区二极管中,少子浓度的分布近似为 线性 ;薄基区二极管相对厚基区二极管来说,其它参数都相同,则PN 结电流会 大的多 。

11.小注入条件是指注入某区边界附近的 非平衡少子 浓度远小于该区的 平衡多子 浓度。

12.大注入条件是指注入某区边界附近的 非平衡少子 浓度远大于该区的 平衡多子 浓度。

微电子器件 (附答案) (第三版)

kT ln ND= NA

q

ni2

=q 1.6 ×10−19 C,= εS 1.045×10−12 F cm ,

代入 | Emax |中,得:| Em= ax | 1.52 ×104 V cm

shanren

0.757 V,

8、(1)

N

I

P

−xi1 − xn −xi1 0 xi2

xi2 + xp

在 N型区,= dE1 dx

shanren

6、

ND2

ND1

由平衡时多子电流为零

Jn

=

qDn

dn dx

+

qµn nE

=

0

得: E =− Dn ⋅ 1 ⋅ dn =− kT ⋅ 1 ⋅ dn =− kT ⋅ d ln n

µn n dx

q n dx

q dx

∫ Vbi

= − ND1 Edx ND2

= kT ln n | q

ND1 ND2

− Emax

+

E

(

x)

= q N

εs

D

x

当 x = xn 时,E(x) = 0,因此

Emax

=

−q

εs

ND xn ,于是得:

E ( x=)

q

εs)

ND

(0 ≤ x ≤ xn )

shanren

(2-5a)

3、

(1)

Vbi

= kT ln N q

A ND ni2

= 0.026× ln

5 ×1032 2.25 ×1020

2

=

3.40×10−5 cm

shanren

4、

微电子器件基础题13页word文档

微电子器件基础题13页word文档“微电子器件”课程复习题一、填空题1、若某突变PN 结的P 型区的掺杂浓度为163A 1.510cm N -=?,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为()和()。

2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。

内建电场的方向是从(N )区指向(P )区。

3、当采用耗尽近似时,N 型耗尽区中的泊松方程为()。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越()。

4、PN 结的掺杂浓度越高,则势垒区的长度就越(短),内建电场的最大值就越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小),势垒电容C T 就越(),雪崩击穿电压就越(低)。

5、硅突变结内建电势V bi 可表为(),在室温下的典型值为(0.8)伏特。

6、当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度会(降低)。

7、当对PN 结外加反向电压时,其势垒区宽度会(变宽),势垒区的势垒高度会(增高)。

8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可表示为()。

若P 型区的掺杂浓度173A 1.510cm N -=?,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为()。

9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(高);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(低)。

10、PN 结的正向电流由(空穴扩散Jdp )电流、(电子扩散电流Jdn )电流和(势垒区复合电流Jr )电流三部分所组成。

11、PN 结的正向电流很大,是因为正向电流的电荷来源是(多子);PN 结的反向电流很小,是因为反向电流的电荷来源是(少子)。

12、当对PN 结外加正向电压时,由N 区注入P 区的非平衡电子一边向前扩散,一边(复合)。

微电子器件课程复习资料题

1、若某突变PN 结的P 型区的掺杂浓度为163A 1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为(316105.1-⨯=cm N A )和(314105.1-⨯=cm N A )。

2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。

内建电场的方向是从(N )区指向(P )区。

[发生漂移运动,空穴向P 区,电子向N 区]3、当采用耗尽近似时,N 型耗尽区中的泊松方程为(D S E u q dx d ε=→)。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越(大)。

4、PN 结的掺杂浓度越高,则势垒区的长度就越(小),内建电场的最大值就越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小)[P20],势垒电容C T 就越( 大 ),雪崩击穿电压就越(小)。

5、硅突变结内建电势V bi 可表为(2ln iD A bi n N N q KT v =)P9,在室温下的典型值为(0.8)伏特。

6、当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度会(降低)。

7、当对PN 结外加反向电压时,其势垒区宽度会(增大),势垒区的势垒高度会(提高)。

8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可表示为()exp()(0KTqv p p p n x n =-)P18。

若P 型区的掺杂浓度173A 1.510cm N -=⨯,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为(3251035.7-⨯cm )。

9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(大);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(小)。

10、PN 结的正向电流由(空穴扩散)电流、(电子扩散)电流和(势垒区复合)电流三部分所组成。

(完整版)电子科技大学微电子器件习题

第二章PN结填空题1、若某突变PN结的P型区的掺杂浓度为N A=1.5×1016cm-3,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为()和()。

2、在PN结的空间电荷区中,P区一侧带()电荷,N区一侧带()电荷。

内建电场的方向是从()区指向()区。

3、当采用耗尽近似时,N型耗尽区中的泊松方程为()。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越()。

4、PN结的掺杂浓度越高,则势垒区的长度就越(),内建电场的最大值就越(),内建电势V bi就越(),反向饱和电流I0就越(),势垒电容C T就越(),雪崩击穿电压就越()。

5、硅突变结内建电势V bi可表为(),在室温下的典型值为()伏特。

6、当对PN结外加正向电压时,其势垒区宽度会(),势垒区的势垒高度会()。

7、当对PN结外加反向电压时,其势垒区宽度会(),势垒区的势垒高度会()。

8、在P型中性区与耗尽区的边界上,少子浓度n p与外加电压V之间的关系可表示为()。

若P型区的掺杂浓度N A=1.5×1017cm-3,外加电压V= 0.52V,则P型区与耗尽区边界上的少子浓度n p为()。

9、当对PN结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度();当对PN结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度()。

10、PN结的正向电流由()电流、()电流和()电流三部分所组成。

11、PN结的正向电流很大,是因为正向电流的电荷来源是();PN结的反向电流很小,是因为反向电流的电荷来源是()。

12、当对PN结外加正向电压时,由N区注入P区的非平衡电子一边向前扩散,一边()。

每经过一个扩散长度的距离,非平衡电子浓度降到原来的()。

13、PN结扩散电流的表达式为()。

这个表达式在正向电压下可简化为(),在反向电压下可简化为()。

14、在PN结的正向电流中,当电压较低时,以()电流为主;当电压较高时,以()电流为主。

《微电子器件》题集

《微电子器件》题集一、选择题(每题2分,共20分)1.下列哪种材料常用于制造微电子器件中的晶体管?A. 硅(Si)B. 铜(Cu)C. 铝(Al)D. 铁(Fe)2.在CMOS逻辑电路中,哪种类型的逻辑门在输入为高电平时导通?A. NAND门B. NOR门C. AND门D. OR门3.以下哪个参数描述的是二极管的电流放大能力?A. 击穿电压B. 反向电流C. 电流放大系数D. 截止频率4.在集成电路制造中,哪种工艺步骤用于定义晶体管和其他元件的几何形状?A. 氧化B. 扩散C. 光刻D. 金属化5.MOSFET器件中,栅极电压对沟道电流的控制是通过什么机制实现的?A. 欧姆定律B. 量子隧穿效应C. 电场效应D. 热电子发射6.下列哪项技术用于减小集成电路中的寄生电容和电阻?A. SOI技术B. BICMOS技术C. CMOS技术D. TTL技术7.在半导体存储器中,DRAM与SRAM相比,主要缺点是什么?A. 成本高B. 速度慢C. 需要定期刷新D. 功耗高8.下列哪种类型的二极管常用于微波电子器件中?A. 肖特基二极管B. 光电二极管C. 变容二极管D. 整流二极管9.集成电路的特征尺寸越小,通常意味着什么?A. 集成度越低B. 性能越差C. 功耗越高D. 制造成本越高10.在半导体工艺中,哪种掺杂技术用于形成P-N结?A. 离子注入B. 扩散C. 外延生长D. 氧化二、填空题(每空2分,共20分)1.在CMOS逻辑电路中,当输入信号为低电平时,PMOS晶体管处于______状态,而NMOS晶体管处于______状态。

2.二极管的正向电压超过一定值时,电流会急剧增加,这个电压值称为二极管的______电压。

3.在集成电路制造中,______步骤用于形成晶体管的栅极、源极和漏极。

4.MOSFET器件的沟道长度减小会导致______效应增强,从而影响器件的性能。

5.DRAM存储单元由一个晶体管和一个______组成。

微电子笔试(笔试和面试题)有答案

微电子笔试(笔试和面试题)有答案第一部分:基础篇(该部分共有试题8题,为必答题,每位应聘者按自己对问题的理解去回答,尽可能多回答你所知道的内容。

若不清楚就写不清楚)。

1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。

模拟信号,是指幅度随时间连续变化的信号。

例如,人对着话筒讲话,话筒输出的音频电信号就是模拟信号,收音机、收录机、音响设备及电视机中接收、放大的音频信号、电视信号,也是模拟信号。

数字信号,是指在时间上和幅度上离散取值的信号,例如,电报电码信号,按一下电键,产生一个电信号,而产生的电信号是不连续的。

这种不连续的电信号,一般叫做电脉冲或脉冲信号,计算机中运行的信号是脉冲信号,但这些脉冲信号均代表着确切的数字,因而又叫做数字信号。

在电子技术中,通常又把模拟信号以外的非连续变化的信号,统称为数字信号。

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD 等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2、你认为你从事研发工作有哪些特点?3、基尔霍夫定理的内容是什么?基尔霍夫电流定律:流入一个节点的电流总和等于流出节点的电流总和。

基尔霍夫电压定律:环路电压的总和为零。

欧姆定律: 电阻两端的电压等于电阻阻值和流过电阻的电流的乘积。

4、描述你对集成电路设计流程的认识。

模拟集成电路设计的一般过程:1.电路设计依据电路功能完成电路的设计。

2.前仿真电路功能的仿真,包括功耗,电流,电压,温度,压摆幅,输入输出特性等参数的仿真。

微电子器件基础知识单选题100道及答案解析

微电子器件基础知识单选题100道及答案解析1. 微电子器件的核心是()A. 晶体管B. 电容器C. 电阻器D. 电感器答案:A解析:晶体管是微电子器件的核心。

2. 以下哪种材料常用于半导体制造?()A. 铜B. 硅C. 铝D. 银答案:B解析:硅是常用于半导体制造的材料。

3. 半导体中的载流子主要包括()A. 电子和质子B. 电子和空穴C. 正离子和负离子D. 中子和电子答案:B解析:半导体中的载流子主要是电子和空穴。

4. PN 结的主要特性是()A. 单向导电性B. 双向导电性C. 电阻不变性D. 电容不变性答案:A解析:PN 结的主要特性是单向导电性。

5. 场效应管是()控制型器件。

A. 电流B. 电压C. 电阻D. 电容答案:B解析:场效应管是电压控制型器件。

6. 双极型晶体管是()控制型器件。

A. 电流B. 电压C. 电阻D. 电容答案:A解析:双极型晶体管是电流控制型器件。

7. 集成电路的集成度主要取决于()A. 芯片面积B. 晶体管数量C. 制造工艺D. 封装技术答案:B解析:集成电路的集成度主要取决于晶体管数量。

8. 以下哪种工艺常用于芯片制造?()A. 蚀刻B. 锻造C. 铸造D. 车削答案:A解析:蚀刻工艺常用于芯片制造。

9. 微电子器件的性能参数不包括()A. 电流放大倍数B. 输入电阻C. 输出电阻D. 重量答案:D解析:重量不是微电子器件的性能参数。

10. 增强型MOS 管的阈值电压()A. 大于0B. 小于0C. 等于0D. 不确定答案:A解析:增强型MOS 管的阈值电压大于0 。

11. 耗尽型MOS 管的阈值电压()A. 大于0B. 小于0C. 等于0D. 不确定答案:B解析:耗尽型MOS 管的阈值电压小于0 。

12. 半导体中的施主杂质提供()A. 电子B. 空穴C. 质子D. 中子答案:A解析:半导体中的施主杂质提供电子。

13. 半导体中的受主杂质提供()A. 电子B. 空穴C. 质子D. 中子答案:B解析:半导体中的受主杂质提供空穴。

电子科技大学微电子器件习题

第二章PN结填空题1、若某突变PN结的P型区的掺杂浓度为N A=1.5×1016cm-3,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为()和()。

2、在PN结的空间电荷区中,P区一侧带()电荷,N区一侧带()电荷。

内建电场的方向是从()区指向()区。

3、当采用耗尽近似时,N型耗尽区中的泊松方程为()。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越()。

4、PN结的掺杂浓度越高,则势垒区的长度就越(),内建电场的最大值就越(),内建电势V bi就越(),反向饱和电流I0就越(),势垒电容C T就越(),雪崩击穿电压就越()。

5、硅突变结内建电势V bi可表为(),在室温下的典型值为()伏特。

6、当对PN结外加正向电压时,其势垒区宽度会(),势垒区的势垒高度会()。

7、当对PN结外加反向电压时,其势垒区宽度会(),势垒区的势垒高度会()。

8、在P型中性区与耗尽区的边界上,少子浓度n p与外加电压V之间的关系可表示为()。

若P型区的掺杂浓度N A=1.5×1017cm-3,外加电压V= 0.52V,则P型区与耗尽区边界上的少子浓度n p为()。

9、当对PN结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度();当对PN结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度()。

10、PN结的正向电流由()电流、()电流和()电流三部分所组成。

11、PN结的正向电流很大,是因为正向电流的电荷来源是();PN结的反向电流很小,是因为反向电流的电荷来源是()。

12、当对PN结外加正向电压时,由N区注入P区的非平衡电子一边向前扩散,一边()。

每经过一个扩散长度的距离,非平衡电子浓度降到原来的()。

13、PN结扩散电流的表达式为()。

这个表达式在正向电压下可简化为(),在反向电压下可简化为()。

14、在PN结的正向电流中,当电压较低时,以()电流为主;当电压较高时,以()电流为主。

微电子器件工艺流程考核试卷

8.离子注入技术的优点包括______、______和______。

9.微电子器件的热管理主要包括______、______和______等方面。

10.提高微电子器件集成度的关键技术之一是______技术的应用。

四、判断题(本题共10小题,每题1分,共10分,正确的请在答题括号中画√,错误的画×)

D.外部环境温度

20.微电子器件在制造过程中,以下哪些措施可以减少缺陷的产生?()

A.提高工艺控制水平

B.使用高质量材料

C.改善设备条件

D.加强环境控制

(请注意,以上题目仅为示例,实际考试题目应根据教学大纲和课程内容进行设计。)

三、填空题(本题共10小题,每小题2分,共20分,请将正确答案填到题目空白处)

1.微电子器件制造中,通常使用的光刻技术是基于______原理。

2.在微电子器件中,PN结的形成是通过______过程实现的。

3.微电子器件的绝缘层主要材料是______。

4.金属-氧化物-半导体(MOS)结构中,氧化物的主要作用是______。

5.刻蚀技术可以分为湿法刻蚀和______刻蚀。

6.微电子器件的互联线通常采用______材料制作。

C.修复缺陷

D.改善硅片的表面质量

12.下列哪个过程属于薄膜生长过程?()

A.光刻

B.刻蚀

C.化学气相沉积

D.离子注入

13.以下哪个参数可以反映微电子器件的集成度?()

A.传输速率

B.尺寸

C.驱动能力

D.工作电压

14.下列哪种工艺用于去除微电子器件中的有机污染物?()

A.光刻

微电子器件复习题

一、填空题1.突变PN 结低掺杂侧的掺杂浓度越高,则势垒区的长度就越 小 ,内建电场的最大值越 大 ,内建电势V bi 就越 大 ,反向饱和电流I 0就越 小 ,势垒电容C T 就越 大 ,雪崩击穿电压就越 小 。

P272.在PN 结的空间电荷区中,P 区一侧带 负 电荷,N 区一侧带 正 电荷。

内建电场的方向是从 N 区指向 P 区。

3.当采用耗尽近似时,N 型耗尽区中的泊松方程为 。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越 大 。

4.若某突变PN 结的P 型区的掺杂浓度为183A1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为 和 。

5.某硅突变PN 结的153D N 1.510cm -=⨯,31810.51N -⨯=cm A ,则室温下n0n0p0n p p 、、和p0n 的分别为 、 、 和 ,当外加0.5V 正向电压时的p p ()n x -和n n ()p x 分别为 、 ,内建电势为 。

6.当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度 大 ;当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度 小 。

7.PN 结的正向电流很大,是因为正向电流的电荷来源是 多子 ;PN 结的反向电流很小,是因为反向电流的电荷来源是 少子 。

8.PN 结的正向电流由 空穴扩散电流 电流、 电子扩散电流 电流和 势垒区复和电流 电流三部分所组成。

9.PN 结的直流电流电压方程的分布为 。

10.薄基区二极管是指PN 结的某一个或两个中性区的长度小于 该区的少子扩散长度 。

在薄基区二极管中,少子浓度的分布近似为 线性 ;薄基区二极管相对厚基区二极管来说,其它参数都相同,则PN 结电流会 大的多 。

11.小注入条件是指注入某区边界附近的 非平衡少子 浓度远小于该区的 平衡多子 浓度。

12.大注入条件是指注入某区边界附近的 非平衡少子 浓度远大于该区的 平衡多子 浓度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

“微电子器件”课程复习题一、填空题1、若某突变PN 结的P 型区的掺杂浓度为163A 1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为( )和( )。

2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。

内建电场的方向是从(N )区指向(P )区。

3、当采用耗尽近似时,N 型耗尽区中的泊松方程为( )。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越( )。

4、PN 结的掺杂浓度越高,则势垒区的长度就越(短),内建电场的最大值就越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小),势垒电容C T 就越( ),雪崩击穿电压就越(低)。

5、硅突变结内建电势V bi 可表为( ),在室温下的典型值为(0.8)伏特。

6、当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度会(降低)。

7、当对PN 结外加反向电压时,其势垒区宽度会(变宽),势垒区的势垒高度会(增高)。

8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可表示为( )。

若P 型区的掺杂浓度173A 1.510cm N -=⨯,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为( )。

9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(高);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(低)。

10、PN 结的正向电流由(空穴扩散Jdp )电流、(电子扩散电流Jdn )电流和(势垒区复合电流Jr )电流三部分所组成。

11、PN 结的正向电流很大,是因为正向电流的电荷来源是(多子);PN 结的反向电流很小,是因为反向电流的电荷来源是(少子)。

12、当对PN 结外加正向电压时,由N 区注入P 区的非平衡电子一边向前扩散,一边(复合)。

每经过一个扩散长度的距离,非平衡电子浓度降到原来的( )。

13、PN 结扩散电流的表达式为( )。

这个表达式在正向电压下可简化为( ),在反向电压下可简化为( )。

14、在PN 结的正向电流中,当电压较低时,以(复合)电流为主;当电压较高时,以(扩散)电流为主。

15、薄基区二极管是指PN 结的某一个或两个中性区的长度小于(少子扩散长度)。

在薄基区二极管中,少子浓度的分布近似为(线性)。

16、小注入条件是指注入某区边界附近的(非平衡少子)浓度远小于该区的(平衡多子)浓度,因此该区总的多子浓度中的(非平衡)多子浓度可以忽略。

17、大注入条件是指注入某区边界附近的(非平衡少子)浓度远大于该区的(平衡多子)浓度,因此该区总的多子浓度中的(平衡)多子浓度可以忽略。

18、势垒电容反映的是PN 结的(中性区中的非平衡载流子)电荷随外加电压的变化率。

PN结的掺杂浓度越高,则势垒电容就越(高);外加反向电压越高,则势垒电容就越(低)。

19、扩散电容反映的是PN 结的(势垒区边缘的电离杂质)电荷随外加电压的变化率。

正向电流越大,则扩散电容就越(大);少子寿命越长,则扩散电容就越(大)。

20、在PN 结开关管中,在外加电压从正向变为反向后的一段时间内,会出现一个较大的反向电流。

引起这个电流的原因是存储在(N )区中的(非平衡少子)电荷。

这个电荷的消失途径有两条,即(反向电流的抽取)和(自身的复合)。

21、从器件本身的角度,提高开关管的开关速度的主要措施是()和( )。

22、PN 结的击穿有三种机理,它们分别是( )、( )和( )。

23、PN 结的掺杂浓度越高,雪崩击穿电压就越( );结深越浅,雪崩击穿电压就越( )。

24、雪崩击穿和齐纳击穿的条件分别是( )和( )。

25、晶体管的基区输运系数是指(基区中到达集电结的少子)电流与(从发射结刚注入基区的少子)电流之比。

由于少子在渡越基区的过程中会发生(复合),从而使基区输运系数(小于1)。

为了提高基区输运系数,应当使基区宽度(减小)基区少子扩散长度。

26、晶体管中的少子在渡越(基区)的过程中会发生(复合),从而使到达集电结的少子比从发射结注入基区的少子(少)。

27、晶体管的注入效率是指(在发射结正偏,集电结零偏的条件下从发射区注入基区的少子)电流与(总的发射极电流)电流之比。

为了提高注入效率,应当使(发射)区掺杂浓度远大于(基)区掺杂浓度。

28、晶体管的共基极直流短路电流放大系数α是指发射结(正)偏、集电结(零)偏时的(集电极)电流与(发射极)电流之比。

29、晶体管的共发射极直流短路电流放大系数β是指(发射结)结正偏、(集电极)结零偏时的(集电极)电流与(基极)电流之比。

30、在设计与制造晶体管时,为提高晶体管的电流放大系数,应当( )基区宽度,( )基区掺杂浓度。

31、某长方形薄层材料的方块电阻为100Ω,长度和宽度分别为300μm 和60μm ,则其长度方向和宽度方向上的电阻分别为(500)和( )。

若要获得1K Ω的电阻,则该材料的长度应改变为(600um )。

32、在缓变基区晶体管的基区中会产生一个(加速场),它对少子在基区中的运动起到(加速)的作用,使少子的基区渡越时间(减少)。

33、小电流时α会(随电流的减小而下降)。

这是由于小电流时,发射极电流中(势垒区复合电流占发射结电流)的比例增大,使注入效率下降。

34、发射区重掺杂效应是指当发射区掺杂浓度太高时,不但不能提高(注入效率),反而会使其(下降)。

造成发射区重掺杂效应的原因是(发射区禁带变窄)和(俄歇复合增强)。

35、在异质结双极晶体管中,发射区的禁带宽度( )于基区的禁带宽度,从而使异质结双极晶体管的( )大于同质结双极晶体管的。

36、当晶体管处于放大区时,理想情况下集电极电流随集电结反偏的增加而(不变)。

但实际情况下集电极电流随集电结反偏增加而(增加),这称为(基区宽度调变)效应。

37、当集电结反偏增加时,集电结耗尽区宽度会(变宽),使基区宽度(变窄),从而使集电极电流(增大),这就是基区宽度调变效应(即厄尔利效应)。

38、I ES 是指(集电极与基)结短路、(发射)结反偏时的(发射)极电流。

39、I CS 是指(发射极与基)结短路、(集电)结反偏时的(集电)极电流。

41、I CBO 是指(发射)极开路、(集电)结反偏时的(集电)极电流。

41、I CEO 是指(基)极开路、(集电)结反偏时的(发射极穿透到集电)极电流。

42、I EBO 是指(集电)极开路、(发射)结反偏时的(发射)极电流。

43、BV CBO 是指(发射)极开路、(集电)结反偏,当( )∞→时的V CB 。

44、BV CEO 是指(基)极开路、(集电)结反偏,当( )∞→时的V CE 。

45、BV EBO 是指(集电)极开路、(发射)结反偏,当( )∞→时的V EB 。

46、基区穿通是指当集电结反向电压增加到使耗尽区将(基区)全部占据时,集电极电流急剧增大的现象。

防止基区穿通的措施是(增加)基区宽度、(增加)基区掺杂浓度。

47、比较各击穿电压的大小时可知,BV CBO ( )BV CEO ,BV CBO (》)BV EBO 。

48、要降低基极电阻bb r ',应当(增大)基区掺杂浓度,( )基区宽度。

49、无源基区重掺杂的目的是( )。

50、发射极增量电阻r e 的表达式是( )。

室温下当发射极电流为1mA 时,r e =( )。

51、随着信号频率的提高,晶体管的ωα、ωβ的幅度会( ),相角会( )。

52、在高频下,基区渡越时间b τ对晶体管有三个作用,它们是:( )、( )和( )。

53、基区渡越时间b τ是指( )。

当基区宽度加倍时,基区渡越时间增大到原来的( )倍。

54、晶体管的共基极电流放大系数ωα随频率的( )而下降。

当晶体管的ωα下降到( )时的频率,称为α的截止频率,记为( )。

55、晶体管的共发射极电流放大系数ωβ随频率的( )而下降。

当晶体管的ωβ下降到021β时的频率,称为β的( ),记为( )。

56、当βf f >>时,频率每加倍,晶体管的ωβ降到原来的( );最大功率增益pmax K 降到原来的( )。

57、当( )降到1时的频率称为特征频率T f 。

当( )降到1时的频率称为最高振荡频率M f 。

58、当ωβ降到( )时的频率称为特征频率T f 。

当pm a x K 降到( )时的频率称为最高振荡频率M f 。

59、晶体管的高频优值M 是( )与( )的乘积。

60、晶体管在高频小信号应用时与直流应用时相比,要多考虑三个电容的作用,它们是( )电容、( )电容和( )电容。

61、对于频率不是特别高的一般高频管,ec τ中以( )为主,这时提高特征频率T f 的主要措施是( )。

62、为了提高晶体管的最高振荡频率M f ,应当使特征频率T f ( ),基极电阻bb r '( ),集电结势垒电容TC C ( )。

63、对高频晶体管结构上的基本要求是:( )、( )、( )和( )。

64、N 沟道MOSFET 的衬底是( )型半导体,源区和漏区是( )型半导体,沟道中的载流子是( )。

65、P 沟道MOSFET 的衬底是( )型半导体,源区和漏区是( )型半导体,沟道中的载流子是( )。

66、当GS T V V =时,栅下的硅表面发生( ),形成连通( )区和( )区的导电沟道,在DS V 的作用下产生漏极电流。

67、N 沟道MOSFET 中,GS V 越大,则沟道中的电子就越( ),沟道电阻就越( ),漏极电流就越( )。

68、在N 沟道MOSFET 中,T 0V >的称为增强型,当GS 0V =时MOSFET 处于( )状态;T 0V <的称为耗尽型,当GS 0V =时MOSFET 处于( )状态。

69、由于栅氧化层中通常带( )电荷,所以( )型区比( )型区更容易发生反型。

70、要提高N 沟道MOSFET 的阈电压V T ,应使衬底掺杂浓度N A ( ),使栅氧化层厚度T ox ( )。

71、N 沟道MOSFET 饱和漏源电压Dsat V 的表达式是( )。

当DSDsat V V ≥时,MOSFET 进入( )区,漏极电流随DS V 的增加而( )。

72、由于电子的迁移率n μ比空穴的迁移率p μ( ),所以在其它条件相同时,( )沟道MOSFET 的Dsat I 比( )沟道MOSFET 的大。

为了使两种MOSFET 的Dsat I 相同,应当使N 沟道MOSFET 的沟道宽度( )P 沟道MOSFET 的。

73、当N 沟道MOSFET 的GS T V V <时,MOSFET ( )导电,这称为( )导电。