DSP复习资料

DSP 复习资料

DSP 复习资料:1、DSP(digital singnal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

2、DSP芯片一般具有如下主要特点:在一个指令周期内可以完成一次乘法和一次加法;可以并行执行多个操作;快速的中断处理和硬件I/O支持;存储器采用哈佛结构;主要用于信号处理。

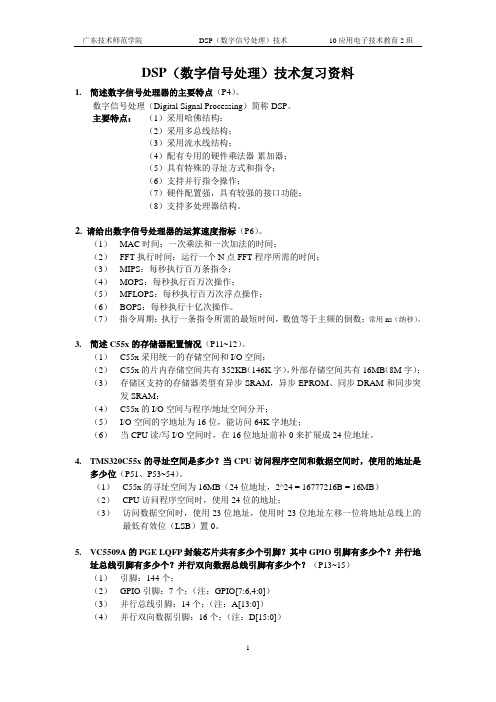

3、一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等组成。

4、按数据格式分为定点DSP和浮点DSP两类。

按数据的定点格式工作的DSP芯片称为定点DSP;按数据的浮点格式工作的DSP芯片称为浮点DSP。

其中C2x、C24x称为C2000系列,主要用于数字控制系统; C54x、C55x称为C5000系列,主要用于功耗低、便于携带的通信终端; C62x、C64x和C67x称为C6000系列,主要用于高性能复杂的通信系统,如移动通信基站。

5、链接命令文件(·cmd文件)指定存储器的结构和段的定位,有MEMORY和SECTIONS两条指令。

MEMORY伪指令用来定义目标系统的存储器配置空间,包括对存储器各部分命名,以及规定它们的起始地址和长度。

SECTIONS伪指令用来指定链接器将输入段组合成输出段方式,以及输出段在存储器中的位置,也可用于指定子段。

6、DSP系统中流水线操作是各指令以机器周期为单位相差一个时钟周期,连续并行工作的情况。

其本质是DSP多条总线彼此独立地同时工作,使得同一条指令在不同机器周期内占用不同总线资源。

同时,不同指令在同一机器周期内占用不同总线资源。

DSP复习资料

7、简答SARAM和DARAM的联系和区别

区别前者1个机器周期内只能被访问1次后者1个机器周期内能被访问2次,可同时进行读操作和写操作。

联系都可当数据存储器和程序存储器使用

第三章

1、数的定标是指定点DSP芯片处理小数时,由程序员来确定一“小数点”的位置。

SXM的中文名称是符号扩展模式位;当SXM=1时,设置符号扩展模式,即高24位扩展为符号位。用指令表示SSBXSXM;当SXM=0时,设置符号不扩展模式,即高24位用0填充;用指令表示RSBXSXM

4、DSP芯片的乘法运算,常需要用到舍入处理方法书上p47

方法是在低16位的最高位加1,然后将低16位清除,将高16位作为结果。(将该数加0.5,之后再将小数部分去除,即舍入处理方法,也称上取整。)

{*SWWSR=0X2000

}

(3)P108为什么要用volatile类型的数据?

答:对程序进行编译时,代码优化器会避免存储区访问而删除一些语句,为了保留这些语句,可以使用volatile关键字可确保编译器不会对这些变量进行优化。

3、P112申明一个函数是中断函数,要使用中断关键字interrupt(怎么考??)

5、简答C语言程序代码优化有几种方法?其中并行指令属于那种优化方法?并举一例并行指令

算法优化编译优化函数优化属于编译优化ST||LD特点:单字单周期

第六章

1、小题DSP的内部存储器类型可分为随机存取存储器(RAM)和只读存储器(ROM)。其中RAM又可以分为两种类型:单寻址RAM(SARAM)和双寻址RAM(DARAM)。

中断程序没有参数传递,即使说明,也将被忽略

4、小题pragma指令告诉编译器如何处理函数。常用的pragma指令有

DSP复习资料

DSP复习资料1、DSP 芯⽚的结构?答:DSP 是改进的哈佛结构 (80C51是哈佛结构)。

冯.诺依曼结构与哈佛结构的区别是地址空间和数据空间分开与否。

冯诺依曼结构数据空间和地址空间不分开,哈佛结构数据空间和地址空间是分开的。

哈佛结构的特点:使⽤两个独⽴的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存;使⽤独⽴的两条总线,分别作为CPU 与每个存储器之间的专⽤通信路径,⽽这两条总线之间毫⽆关联。

改进的哈佛结构,其结构特点为:使⽤两个独⽴的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存,以便实现并⾏处理;具有⼀条独⽴的地址总线和⼀条独⽴的数据总线,利⽤公⽤地址总线访问两个存储模块(程序存储模块和数据存储模块),公⽤数据总线则被⽤来完成程序存储模块或数据存储模块与CPU 之间的数据传输,改进的哈佛结构在哈佛结构的基础上⼜加以改进,即使得程序代码和数据存储空间之间也可以进⾏数据的传送。

TMS320LF2407A 采⽤改进的哈佛结构,芯⽚内部具有六条16位总线,即程序地址总线(PAB )、数据读地址总线(DRAB )、数据写地址总线(DWAB )、程序读总线(PRDB )、数据读总线(DRDB )、数据写总线(DWEB ),其程序存储器总线和数据存储器总线相互独⽴,⽀持并⾏的程序和操作数寻址,因此CPU 的读/写可在同⼀周期内进⾏,这种⾼速运算能⼒使⾃适应控制、卡尔曼滤波、神经⽹络、遗传算法等复杂控制算法得以实现。

结构⽰意图如下:2、什么是流⽔线技术?DSP 是不是具有流⽔线技术(pipeline) ?答:流⽔线技术是将各指令的各个步骤重叠起来执⾏,⽽不是⼀条指令执⾏完成之后,才开始执⾏下⼀条指令。

计算机在执⾏⼀条指令时,总要经过取指、译码、取数、执⾏运算等步骤,需要若⼲个指令周期才能完成。

流⽔线技术是将各指令的各个步骤重叠起来执⾏,⽽不是⼀条指令执⾏完成之后,才开始执⾏下⼀条指令。

DSP复习资料.pdf

3、DSP有哪几种分类方式,可将DSP芯片分成哪几类?答:DSP有三种分类方式:按基础特性分类、按数据格式分类和按用途分类。

按基础特性可分为静态DSP芯片和一致性DSP芯片;按数据格式可分为定点DSP芯片和浮点DSP芯片;按照用途可分为通用型DSP芯片和专用型DSP芯片。

7、冯·诺伊曼结构和哈佛结构的主要区别是什么?与前者相比,哈佛结构有何优势?答:1)主要区别:冯·诺伊曼结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线。

哈佛结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线。

2)哈佛结构优势哈佛结构可独立编址和访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,极大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

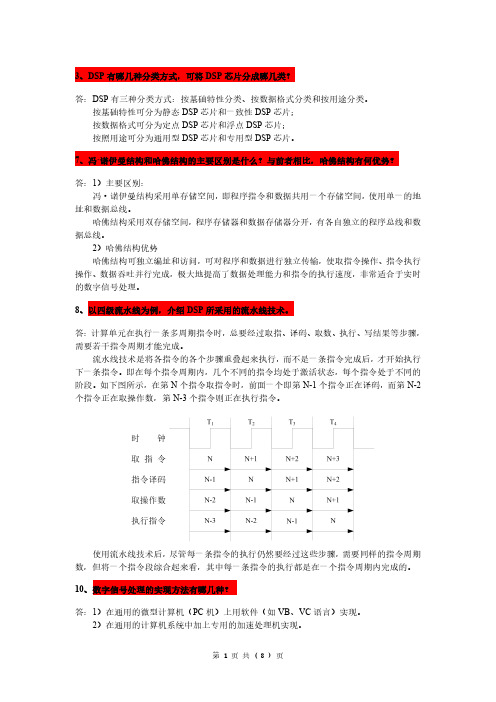

8、以四级流水线为例,介绍DSP所采用的流水线技术。

答:计算单元在执行一条多周期指令时,总要经过取指、译码、取数、执行、写结果等步骤,需要若干指令周期才能完成。

流水线技术是将各指令的各个步骤重叠起来执行,而不是一条指令完成后,才开始执行下一条指令。

即在每个指令周期内,几个不同的指令均处于激活状态,每个指令处于不同的阶段。

如下图所示,在第N个指令取指令时,前面一个即第N-1个指令正在译码,而第N-2个指令正在取操作数,第N-3个指令则正在执行指令。

使用流水线技术后,尽管每一条指令的执行仍然要经过这些步骤,需要同样的指令周期数,但将一个指令段综合起来看,其中每一条指令的执行都是在一个指令周期内完成的。

10、数字信号处理的实现方法有哪几种?答:1)在通用的微型计算机(PC机)上用软件(如VB、VC语言)实现。

2)在通用的计算机系统中加上专用的加速处理机实现。

3)用单片机(如MCS-51、96系列等)实现。

4)用FPGA等产品实现数字信号处理算法。

5)用通用的可编程DSP芯片实现。

DSP复习资料

DSP复习资料DSP复习资料填空题:1、TL公司的DSP产品主要有TMS320C2000、TMS320C5000和TMS320C6000系列。

2、程序计数器的值可以通过复位操作、顺序执行指令、分支转移、累加器转移、块重复、子程序调用、从累加器调用子程序,中断操作来改变。

3、COFF目标文件都包含以下三种形式的段,分别是.text文本段、.data数据段、.bass保留空间。

4、DSP的寻址方式有七种分别是立即寻址、绝对寻址、累加器寻址、直接寻址、间接寻址、存储器映像寄存器寻址、堆栈寻址。

5、DSP芯片的开发工具可以分为代码生成工具和代码调试工具两类。

6、子段有两种,用.sect命令建立的是已初始化段,用.usect命令建立的是未初始化段。

7、DROM为1,片内ROM配置程序和存储空间,ST1的CPL为1表示选用堆栈指针SP的直接寻址方式;ST1的C16等于1表示ALU 工作在双精度算式(填0或1)8、DSP具有两个40 位的累加器A和B,累加器A的32-39位是保护位。

9、TMS320C54x DSP的内部总存储空间为192K字,分成了3个可选择的存储空间分别是64K程序存储空间、64K数据存储空间、64K的I/O存储空间。

10、TMS320C54x有4组地址总线分别是PAB、CAB、DAB和EAB总线。

11、链接器对段的处理主要头通过MEMORY 和SECTIONS的两个命令来完成。

12、DSP有3个16位寄存器作为状态控制寄存器,分别是ST0、ST1和PMST。

13、TMS320C54x的三类串行口分别是标准同步串行口、缓冲串行口、时分多路串行口。

14、DSP的内部存储器类型可分为RAM和ROM,其中RAM可以定义为两个类型单寻址RAM(SARAM)和双寻址RAM(DARAM)。

15、在数字信号处理器寻址指令系统中,D mad为16位立即数,表示数据存储器地址,P mad表示程序存储器地址。

DSP期末复习资料_图文(精)

DSP期末复习资料2.DSP芯片的特点:哈佛结构:将程序空间和数据空间分开,可同时取指令和取操作数;(重要)多总线结构:一个机器周期可以多次访问程序空间和数据空间,其内部有P、C、D、E 4个总线;(重要)流水线结构:DSP执行一条指令需要取指、译码、取操作数和执行等几个阶段;(重要)多处理单元:算术逻辑运算单元、辅助寄存器、累加器、硬件乘法器等;特殊的DSP指令、指令周期短、运算精度高、硬件配置强。

3.TMS320系列DSP可分为:C2000(16位/32位定点DSP,主要运用控制领域)、C5000(16位定点DSP,用于高性能、低功耗的中高档应用场合)、C6000(32位DSP,高性能)系列。

4. TMS320C54X的主要特性:⑴多总线结构(1条程序总线、3条数据总线、4条对应地址总线);⑵192K字节可寻址空间(64K字程序存储器、64K字数据存储器以及64K字I/O空间);⑶片内有单寻址RAM(SRAM)和RAM(DRAM存储器。

5.TMS320VC5416-160有1个CPU、6. C54X的总线结构:C54X片内有8条16位主总线、4条程序/数据总线和4条相应的地址总线。

7.当处理器复位时,复位和中断向量都映像到程序空间的FF80h。

8.累加器A和B的差别在于:累加器A的31~16位可用于乘法器的一个输入。

9.桶形移位器的移位数可用一个立即数、状态寄存器ST1的累加器移位方式ASM或者T寄存器中最低的6位数值来定义。

10.指数编码器可以在单个周期内执行EXP指令,求的累加器中数据的指数值,并以2的补码形式存放在T寄存器中,可以用11.C54XCPU有3个状态寄存器:状态寄存器0(ST0)、状态寄存器1(ST1)、处理工作方式状态寄存器(PMST)。

12.C54X中断可分为可屏蔽中断和非屏蔽中断。

所有的软件中断都是非屏蔽的。

13.定时中断的周期:CLKOUT*(TDDR+1)*(PRD+1)14. C54X片内有一个主机接口(HPI)。

DSP复习资料

答:流水线作业就是使取址、译码、取操作数和执行指令等操作重叠执行。 3. 什么是哈佛总线?P1

答:哈佛总线就是程序空间和数据空间分开,分别由各自的地址总线和数据总线; 它可以同时完成获取指令和数据读取操作。 4. 2812 的 SPI 和 SCI 接口的主要异同?

EALLOW; PieVectTable.TINT0=&cpu_timer0_isr; GpioMuxRegs.GPAMUX.all=0x0000; GpioMuxRegs.GPADIR.all|=0x0001; EDIS; InitCpuTimers(); ConfigCpuTIMER(&CpuTimer0,100,2000000); StartCpuTimer0; IER|=M_INT1; PieCtrlRegs.PIEIER1.bit.INTx7=1; EINT; ERTM; for(;;) { GpioDataRegs,GPATOGGLE.bit.GPIOA0=1; CpuTimer0.InterruptCount==CpuTimer0.InterruptCount ; } } interrupt void cpu_timer0_isr(void) { CpuTimer0.InterruptCount++; PieCtrlRegs.PIEACK.all= PIEACK_GROUP1; } 15. 拨码键盘地址 0x88000,LED 显示器地址 0x88001,编程实现:拨码为 1,相应灯亮;反 之则灭。 答:#include “DSP2812x_Device.h” #include “DSP2812x_Examples.h” void InitsysCtrl(void); void main(void) { InitsysCtrl(); DINT; IER=0x0000; IFR=0x0000; unsigned int temp; while(1) { temp=*(int*)0x88000; *(int*)0x88001=temp; } } void InitsysCtrl(void) { EALLOW;

dsp复习资料

一,Dsp 的硬件结构:⑴1组程序总线(PB),3组数据总线(CB,DB,EB),4组地址总线(PAB,CAB,DAB,EAB).⑵40位算术逻辑单元alu{C16=0工作在双精度算术运算方式,C16=1工作在双16位方式}ALU 溢出后状态寄存器ST0的OVM=1时,用32位最大正数007FFFFFFFH 或最大负数FF80000000H 加载累加器,溢出后溢出标志位OVA 或OVB=1直到复位!⑶1个40位桶行移位寄存器,⑷2个独立40位ACCA 和ACCB{ACCA 和ACCB 差别在于A 的31~16位可以用途乘法器的一个输入}.⑸17X17并行乘法器与40位的专用加法器相连,用于MAC 运算.⑹比较/选择/存储单元(CSSU)用于加法比较运算,⑺指数单元EXP(40位),⑻有16bit 状态寄存器ST0,ST1和工作方式状态寄存器PMST.二,存储结构:①哈佛结构(ROM 和RAM 分开),②三个独立64kb,ROM,RAM,I/O 空间,程序空间通过PMST 的MP/MC\和OVLY 控制,MP 控制使用内部存储器,MP=0,4000H-EFFFH 程序存储空间定义为外部存储器,FF00H-FEFFH 为内部,FF00H-FFFFH 为内部ROM 存储器,工作方式为微型计算机,MP=1,4000H-FFFFH 全部定义为外部存储器,工作方式为处理器模式.当OVLY=0时,0000H~3FFFH 全部定义为外部程序存储空间,程序空间不使用内部RAM,此时内部RAM 只作为数据存储器使用,OVLY=10000H~007FH 保留,程序无法使用,0080H~3FFFH 定义为内部DARAM,即内部RAM 被映射到程序存储空间和数据存储空间.③片上外设:2个通用I/O,XF(外部标志输出信号.控制外设工作)和BIO(控制分支转移信号,监测外部状态).BIO=0时执行转移指令.④定时器:4位预分频器和16位减法计数器组成,定时设定寄存器TIM(16bit)→0024H,复位/定时TIM 装入PRD(定时寄存器→0025H,存放定时常数)寄存器的值,然后减1计数,TIM 减到0后产生TINT 中断,TCR(定时控制寄存器→0026H)用来控制定时器的控制位和状态位,包括定时分频TDDR,预标定时计数器PSC,控制位TRB 和TSS 等.周期=时钟T*(TDDR+1)*(PRD+1).⑤时钟发生器:内部振荡器和锁相环PLL{⑴硬件配置PLL,通过[CLKMD1,CLKMD2,CLKMD3R 的状态,]⑵软件设置[通过16位的CLKMD →58H 控制]},⑥主机接口HPI:{控制寄存器HPIC,地址寄存器HPIA,数据锁存器HPID,HPI 内存},三,外设接口:软件等待状态寄存器SWWSR →0028H,复位时SWWSR →7FFFH,四,中断:1,可屏蔽中断{INT0-3,串行口中断,定时器中断TINT0-1,DMA 中断(DMAC4,DMAC5).HPINT(HPI 中断)}.2,非可屏蔽中断{外部中断投复位和‾NMI ‾(可用软件中断)}中断标志寄存器IFR 和中断屏蔽寄存器IMR{中断向量地址的计算[中断向量地址是由PMST 寄存器中的IPTR(中断向量指针,9bits)和左移2位后的中断向量序号(中断向量序号为0~31,左移两位后变成7位)所组成]例如INT0的中断序号为16(10H)左移两位后成40H 若IPTR=0001H,则中断地址为00C0H,复位时IPTR 全为1,所以硬件复位后程序总是从0FF80H 执行}.五,指令系统:1,寻址方式{i.立即寻址.[用于初始化(LD#80H,A)].ii.绝对寻址[①数据存储器(dmad)寻址(mvkd exam1,*ar5)②程序存储器(pmad)寻址(mvpd table,*ar2)③端口(pa)寻址(PORTR FIFO,*AR5)④*(1K)寻址(LD *(PN),A))].iii.累加器寻址{是用累加器中的数值作为地址来读写程序存储器,READA Smem,WRITASmen}.iv.直接寻址{ADD @x,A}.v.间接寻址[(寻址范围0~64kb)利用辅助寄存器内容作为地址访问存储器(C54x 有8个16bits 辅助寄存器AR0-AR7)]vi.存储器映像寄存器(MMR))寻址{LDM,MVDM,MVMD,MVMM,POPM,PSHM,STLM,STM}vii.堆栈寻址{PSHD,PSHM,POPD,POPD}.常用缩写{Smem:16位的单寻址操作数,Xmem:16位双寻址操作数,Ymem:16位双寻址操作数,PA:16位立即数,src:源累加器,dst:目的累加器,lk:16位长立即数},六,软件开发过程:.text 文本段,.data 数据段,.bss 保留空间,通常对未初始化变量保存,.sect 建立包含代码和数据的自定义段,.usect 为未初始化变量保留存储空间的自定义段,.word 用来设置一个或多个16位带符号整型常数,.int 设置无符号整型常数.title 后面是双引号的程序名,.end 结束汇编命令,汇编程序举例:㈠堆栈的使用:100单元的堆栈,size .set 100 \stack .usect “stk ”,size\STM #stack+size SP.㈡加减乘,①Z=X+Y-W,SUM:LD @x,A\ADD @y,A\SUB @w,A\STL A,@z.②y=mx+b,ld @m,t\mpy @x,A\add @b,A\stlA,@y.③y=x1*a1+x2*a2,ld @x1,t\mpy @a1,B\ld @a2,t\mpy @x2,b\stlB,@y\sth B,@y+1④y= a i 4i =1x i stm #a,ar1\stm #x,ar2\stm #2,ar3/ld *ar1+,t\mpy *ar2+,A\loopl:ld *ar1+,tMpy *ar2+,b/max A/banz loop,*ar3-㈢数组初始化x[5]=[1,2,3,4,5].data\tbl:.word 1,2,3,4,5\.sect “.vector ”\B START\.bss x,5\.text\START:stm #x,ar5\rpt #4\MVPD TBL,*AR5.㈣设计对称FIR 滤波器(N=8).title “firs5”\.mmregs\.def start\.bss y,1\x_old .usect “data1”,4\x_new .uscet “data2”,A\size .set 4\PA0 .set 0\PA1 .set 1\.data/COEF .word 1*32768/10,2*32768/10\.text/start:ld #y,dp\ssbxfrct\stm #x_new,ar2\stm #x_old+(size-1),ar3\stm #size,bk\stm #-1,ar0\POPTR PA1,#x_new\FIR5: ADD *AR2+0%,*AR3+0%,A\RPTZ B,#(size-1)\FIRS *AR2+0%,*AR3+0%,COEF\STH B,@y\MAR *+AR2(2)%\MAR *AR3+%\MVDD *AR2,*AR3+0%\BD FIR5\POPRTR PA1,*AR2\.end 用线性缓冲法和直接寻址法实现FIR 滤波器:N=5,Y(n)=a0x(n)+a1x(n-1)+a2x(n-2)+a3x(n-3)+a4x(n-4)程序:.title “fir1.asm ”\.mmrges\.def start\.bss y,1\XN .usect “XN ”,1\XNM1 .usect “XNM1”,1\XNM2 .usect “xnm2”,1\xnm3 .Usect “xnm3”,1\xnm4 .usect “xnm4”,1\a0 .usect “a0”,1\a1 .usect “a1”,1\a2 .usect “a2”,1\a3 .usect “a3”,1\a4 .usect “a4”,1\pa0 .set 0\pa1 .set 1\.data\table: .word1*32768/10\.word -3*32768/10\.word 5*32768/10\.word -3*32768/10\.word 1*32768/10\.text\start: ssbxfrct\stm #a0,ar1\rpt #4\mvpd table,ar1+\ld #xn,dp\portr pa1,@xn\fir1:ld @xnm4,t\Mpy @a4,a\ltd @xnm3\mac @a3,a\ltd @xnm2\mac @a2,a\ltd @xnm1,a\mac @a1,a\ltd @xn,a\mac @a0,a\ltha,@y\portw @y,pa0\bd fir1\portrpa1,@xn\.end 循环缓冲区和双操作数寻址方法实现:.title “firs ”\.mmregs\.def start\.bss new_data.1\.bss y,1\xn .usect “xn ”,5\a0 .usect “a0”,5\.data\tsble:.word 1*32768/10\.word 2*32768/10\.word 3*32768/10\.word 4*32768/10\.word 5*32768/10\.text\start:ssbxfrct\stm @a0,ar1\rpt #4\mvpd table,*ar1+\stm #xn+4,ar3\stm #a0+4,ar4\stm 5,bk\stm #-1,ar0\ld ##new_data\fir4:rptz a,#4\mac *ar3+0%,*ar4+0%,a\stha,@y\bd fir4\ldnew_data,bstl b,*ar3+0%\.end。

DSP复习资料

DSP最新考纲1、CPU总线结构基本概念。

2、直接寻址模式的基本寻址方法。

3、存储器映像寄存器包括的主要内容及地址。

4、CCS生成可执行文件的过程及载入可执行文件的方法。

5、片上ROM固化的内容及地址。

6、DSP系统的结构框图。

7、软件等待状态发生器的设置。

8、C语言中I/O端口的访问方法及插入汇编命令的方法。

9、自举的概念。

10、中断向量表地址的计算方法。

11、多路缓冲串口的发送和接收过程。

12、上电复位电路及手动复位电路设计方法。

13、定时器定时时间计算方法:定时周期 = CLKOUT×(TDDR+1)×(PRD+1)14、中断编程过程及方法。

15、布置的作业。

复习:1-01.数字信号处理:答:数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。

1-02.DSP系统的构成:1-03.数字信号处理器的特点:答:数字信号处理器(DSP)是一种特别适合于进行数字信号处理运算的微处理器,主要用于实时快速实现各种数字信号处理的算法。

哈弗结构;多总线结构;流水线结构;多处理单元;特殊的dsp指令;指令周期短;运算精度高;硬件配置高。

1-04.定点DSP:数据采用定点格式工作的DSP芯片。

浮点DSP:数据采用浮点格式工作的DSP芯片。

1-05.54x的特点:答:(1) 改进哈佛结构;(2) 8条总线(1条程序总线,3条数据总线,4条地址总线);(3) 高度专业指令系统;(4) 内核供电电压低。

优点:(1)功耗低;(2)高度并行性。

1-06.1. 总线结构:8条16位总线(1条程序,3条数据,4条地址)(1)PB:传送程序存储器的指令代码和操作数;(2)CB、DB:传送来自数据存储器的操作数;(3)EB传送写入数据存储器操作数;(4)PAB、CAB、DAB、EAB:传送地址信息。

DSP复习资料

第一章:DSP的实现方法:1.用专用的DSP芯片实现2.用通用的可编程DSP芯片实现3.用通用的单片机(如MCS-51、96系列等)实现4.在通用计算机系统中加上专用的加速处理机实现5.在通用的计算机(如PC)上用软件(如C语言)实现DSP系统工作过程1,对输入信号进行带限滤波和抽样;②进行A/D变换,将信号变换成数字比特流;③根据系统要求,DSP芯片对输入信号按照特定算法进行处理;④D/A转换,将处理后的数字样值转换为模拟信号;⑤平滑滤波,得到连续的模拟信号波形。

DSP系统特点:①接口方便②编程方便③稳定性好④精度高⑤可重复性好⑥集成方便DSP系统的设计1.定义系统性能指标2.采用高级语言进行性能模拟3.设计实时DSP应用系统4.借助开发工具进行软硬件调试5.系统集成与独立系统运行DSP芯片的分类按数据格式分——根据DSP芯片工作的数据格式来分类定点DSP芯片:价格较便宜、功耗较低,但运算精度稍低。

浮点DSP芯片:运算精度高,用C语言编程调试方便,但价格稍贵,功耗较大。

DSP系统的运算量1.按样点处理:即DSP算法对每一个输入样点循环一次。

2.按帧处理:针对DSP算法不是每个输入样点循环一次,而是每隔一定的时间间隔(即帧)循环一次。

第二章DSP芯片的基本结构大致分为CPU算术逻辑单元(ALU)、累加器(ACC)、乘累加单元(MAC)移位寄存器、寻址单元等存储器包括片内ROM、Flash、SARAM、DARAM等集成外设和专用硬件电路包括片内串行接口、主机接口、定时器、时钟发生器、锁相环及各种控制电路。

总线用于传送指令和数据;在CPU与存储器、集成外设和专用硬件电路等部分之间。

寻址方式1.程序寻址程序计数器PC:由程序地址产生单元产生。

例如,TMS320C54x 系列DSP芯片的PAGEN。

①包含需要取指的下一条指令所在的程序存储器地址,一般在存储器地址中按顺序产生;②当执行到子函数调用、中断时,将用相应的子函数入口地址或中断ISR入口地址来加载PC;③当执行到跳转语句时,会使用相应的跳转地址来加载PC。

dsp复习资料

dsp复习资料1.简述dsp芯⽚的主要特点。

1.哈佛结构:将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独⽴的存储器,每个存储器独⽴编址、独⽴访问。

2.多总线结构:可以保证在⼀个机器周期内可以多次访问程序空间和数据空间。

3.指令系统的流⽔线操作:DSP芯⽚⼴泛采⽤流⽔线以减少指令执⾏时间,从⽽增强了处理器的处理能⼒。

4.专⽤的硬件乘法器:DSP芯⽚中有专⽤的硬件乘法器,使得乘法累加运算能在单个周期内完成。

5:特殊的DSP指令:(例如)TMS320C54x中的FIRS和LMS指令专门⽤于系数对称的FIR滤波器和LMS 算法。

6.快速的指令周期7.硬件配置强2.结合你的专业⽅向,试举出⼀个dsp具体应⽤实例,并说明为什么要采⽤dsp.DSP芯⽚的⾼速发展,得益于集成电路技术的进步,巨⼤的市场需求信号处理:数字滤波、⾃适应滤波、FFT、频谱分析3. 请描述TMS320C54x的总线结构1个程序总线(PB) 传送从程序存储器来的指令代码和⽴即数3个数据总线(CB DB EB)连接各种元器件4个地址总线(PAB CAB DAB EAB) 传送执⾏指令所需的地址PB ⽤于装载指令代码和⽴即数CB DB ⽤于读取操作数EB ⽤于写⼊操作数地址总线负责其他地址总线的地址存储与装载4. TMS320C54x⽚内存储器⼀般包括哪些种类?如何配置TMS320C54x⽚内存储器。

TMS320C54x芯⽚有随机访问存储器(RAM)和只读存储器(ROM)RAM可分为两种:双访问RAM(DARAM)和单访问RAM(SARAM)⽚内存储空间⼀般包括:64K的程序空间,64K的数据空间和64K的I/O空间,TMS320C54x⽚内存储器可使⽤MP/MC位、OVLY位、DROM位进⾏相对应得配置。

①MP/⾮MC位:如果该位清0,则⽚内ROM映象在程序存储器空间;如果置1,则⽚内ROM不映象在程序存储器空间。

DSP复习资料

1.DSP芯片的特点:采用数据总线和程序总线分离的哈佛结构; 采用多总线结构,可同时进行取指令和多个数据存取操作; 采用流水线技术; 配有专用的硬件乘法-累加器; 具有特殊的DSP指令; 快速的指令周期; 硬件配置强; 支持多处理器结构; 省电管理和低功耗DSP芯片的分类:按基础特性:静态DSP芯片和一致性DSP芯片;按用途通用型DSP芯片和专用型DSP芯片;按数据格式定点DSP和浮点DSP;发展趋势DSP内核结构进一步改善; 存储器构架; SOC; 实时; 嵌入式的趋势2.流水线操作:概念指各条指令以机器周期为单位,相差一个时间周期而连续并行工作的情况。

六个操作阶段预取指P; 取指F;译码D;寻址A;读数R;执行X;引入的好处:减少指令执行时间,增加处理器的处理能力;产生冲突原因及解决方法:一.CPU访问DARAM会发生流水冲突的情况:同时从同一存储块中取指令和读操作数;同时对同一存储块进行写操作和读第二操作数。

CPU可通过写操作延迟一个周期,或通过插入一个空操作来解决流水线冲突;二.流水线允许CPU多条指令同时寻址CPU资源,当一个CPU资源同时被一个以上流水线级访问时,可能导致时序上的冲突,其中,有些冲突可以由CPU通过延迟寻址的方法自动解决,由些需要安排指令或者插入空操作NOP指令加以解决。

利用保护性MMR的指令,自动插入等待周期,也可以避免发生冲突。

3.程序存存储空间的划分和配置:192K字的存储空间: 程序、数据、I/O存储空间;( 1 ) 程序存储空间定义在片内还是片外是由MP\MC和OVL Y决定的。

MP\MC=1称为微处理器模式4000~FFFFH片外存贮器MP\MC=0,称为微计算机模式4000~EFFFH片外存贮器FF00~FFFFH片上存贮器OVL Y为决定0000H~3FFFH程序存贮空间的片外、片外分配控制。

OVL Y=1,0000H~007FH保留,程序无法占用,0080H~3FFFH片内DARAM.OVL Y=0,0000H~3FFFFH片外程序存贮空间。

DSP技术复习资料-完整版

即是longl1存放在AC0,……对应下去。

33.以下的汇编语句实现两个整型数的饱和加法,请编写C语言程序调用该汇编函数,实现整数20000和30000的饱和加法,并在CCS中输出和的值;(相关P209)

18.C55x支持3种类型的寻址方式,分别是绝对寻址模式、直接寻址模式和间接寻址模式;(P69)

19.什么是绝对寻址方式?C55x有几种绝对寻址方式,分别是什么?(P70)

绝对寻址方式:通过在指令中指定一个常数地址完成寻址;

有三种绝对寻址方式:(1)K16绝对寻址方式;(2)K23绝对寻址方式;

(3)I/O绝对寻址方式。

有四种间接寻址方式:(1)AR间接寻址;(2)双AR间接寻址;(3)CDP间接寻址;

(4)系数间接寻址。

22.指令MOV *abs16(#2002h), T2采用的是K16绝对寻址方式。设DPH=03h,该指令的功能是#k16=2002H,CPU从032002H处读取数据装入T2;(P81)

23.指令MOV port(@0), T2采用的是PDP直接寻址方式。设PDP=511,该指令的功能是PDP:Poffset=FF80H,CPU从FF80H读取数据进T2;

11.SATA位是寄存器ST3_55中的第5位,如果SATA=1,则执行A单元ALU的饱和模式;(P50)

12.MPNMC位是寄存器ST3_55中的第6位,该位使能或禁止片上ROM,如果MPNMC=0,则为微计算机模式,使能片上ROM;(P50)

13.VC5509A拥有160K字的片内存储器资源,其中有128K字RAM和32K字ROM。外部扩展存储空间由CE[3:0]组成,其中CE0的首字地址为0000 2000H,CE1的首字地址为00200000 H(P51~52)(P58~59)

DSP复习资料

DSP复习资料1、什么是数字信号处理器(DSP)?DSP 可以分为哪两类?a、数字信号处理器是⼀种专门⽤于实现各种数字信号处理算法的微处理器,通常可分为专⽤DSP和通⽤DSP两类。

b、⽤于实现某些特定数字信号处理功能的DSP 属于专⽤DSP。

什么是DSP?DSP:Digtal Signal Processing 数字信号处理技术典型的微处理器系统根据CPU特点,可以分为:1)通⽤单⽚机(Micro-controller) 8/16bit优点:成本低、体积⼩。

缺点:运算与扩展能⼒较弱。

编程:汇编、C语⾔。

2)PC及其兼容机(Micro-processor)缺点:成本⾼、体积⼤、实时性差。

优点:运算与扩展能⼒强,软件资源丰富。

编程:汇编及多种⾼级语⾔。

3)DSP(Digital Signal Processor)16/32bit特点:运算能⼒相当强、实时性、体积⼩、成本较低、功耗较低编程:汇编、C、C++。

4)专⽤微处理器特点:使⽤简单,灵活性差,主要⽤于⼀些批量⽣产的产品。

如家⽤电器的智能控制、⼯业控制。

DSP: Digtal Signal Processor 数字信号处理器TI公司从80代初推出了全球第⼀款“数字信号处理器”TMS320C010,从此引发了⼀场“数字信号处理”⾰命。

我们现在所说的DSP,如果没有特殊说明,⼀般均指“数字信号处理器”。

2、DSP 芯⽚的主要特点有哪些?DSP 从结构上进⾏了优化,使其更适合于哪类运算,从⽽可以⾼速实现多种不同的数字信号处理算法?DSP的特点:在⼀个指令周期内可完成⼀次乘法和⼀次加法运算程序和数据空间分开,可以同时访问指令空间和数据空间⽚内具有快速RAM,通常可通过独⽴的数据总线在两块中同时访问具有低开销或⽆开销循环及跳转的硬件⽀持快速的中断处理和硬件I/O⽀持具有在单周期内操作的多个硬件地址产⽣器可以并⾏执⾏多个操作⽀持流⽔线操作,使取指令、译码、取操作数和执⾏指令等可以重叠执⾏。

DSP复习资料

1.DSP 概念一为“digital signal processing”指数字信号处理技术,二为“digital signal processor”,指数字信号处理器。

2.数*构成及功能:输入—抗混叠滤波—A/D—数字信号处理—D/A—平滑滤波——输出。

将输入信号x(t)进行抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠;经采样和A/D转换器,将滤波后的信号转换为数字信号x(n);数字信号处理器对x(n)进行处理,得数字信号y(n);经D/A转换器,将y(n)转换成模拟信号;经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

3.数*实现方法1)在通用计算机(PC机)上用软件(如Fortran、C语言)实现,但速度慢,不适合实时数字信号处理,只用于算法的模拟; 2)在通用计算机系统中加入专用的加速处理机实现,用以增强运算能力和提高运算速度。

不适合于嵌入式应用,专用性强,应用受到限制;3)用专用的DSP芯片实现,可用在要求信号处理速度极快的特殊场合,如专用于FFT、数字滤波、卷积、相关算法的DSP芯片,相应的信号处理算法由内部硬件电路实现。

用户无需编程,但专用性强,灵活性差; 4)用通用的可编程DSP芯片实现,具有可编程性和强大的处理能力,可完成复杂的数字信号处理的算法,在实时DSP领域中处于主导地位,兼顾速度和灵活性;5)用基于通用DSP核的ASIC芯片实现。

随着专用集成电路ASIC的广泛使用,可以将DSP的功能集成到ASlC中。

一般说来,DSP核是通用DSP器件中的CPU部分,再配上用户所需的存储器和外设,组成用户的ASIC,灵活性差,只适合某单一运算。

4.数*分类:按基础特性(工作时钟和指令):静态DSP芯片和一致性DSP芯片(TMS320C54x)。

按用途:通用型和专用型。

按数据格式(其精度或动态范围):定点DSP和浮点DSP。

5.哈弗结构特点是将程序和数据存储在不同的存储空间中,每个存储器独立编址,独立访问。

DSP复习资料

DSP原理与应用一、填空题1.按数据格式分类,DSP芯片可分为芯片和芯片。

2.TMS320C54X DSP中,TMS320C54X DSP有A和B两个累加器。

每个累加器的长度为位,分为、、和三部分。

3.为了达到快速进行数字信号处理的目的,DSP芯片一般具有程序和数据分开的总线结构,称为。

4.已知(80H)=10H,(81H)=40H,则先后执行指令LD 80H,16,B和ADD 81H,B两条指令后,B的内容是。

5. IMR为存储器映像寄存器,当要屏蔽某一个中断时,IMR中的相应标志位的值为。

6.HPI有和两种工作模式。

7.DSP芯片的电源分两种即为和,在无法同时加电的情况下,应先对加电。

8.直接寻址中,若CPL=0,则所寻址数据存储器的16位地址是由构成。

9.若缓冲器长度为BK=10,循环缓冲区的基地址为AR1=100h,则执行指令LD*+AR1(8)%,A;两次后,寻址的是地址单元。

二、简答题1.简述流水线操作的基本原理。

2.简述TMS320C54X DSP的堆栈的特点,并简述堆栈寻址入栈和出栈时的工作过程。

3. TMS320C54X DSP的定时器有哪几部分组成?各部分的作用是什么?4.在链接命令文件中,伪指令MEMORY和SECTIONS的作用是什么?5.右图为一个具有自动复位功能的电路,请简述其工作原理。

6. 在堆栈操作中,PC当前地址为4020h,SP当前地址为0013h后,运行PSHM AR7(1字指令)后,PC和SP的值分别是多少?并说明原因。

7. 若用DSP实现8点的FFT运算,采用*AR2+0B进行反向寻址,若初始AR2值为0000H,则AR0的低3位取值应为多少?请写出AR2值最后三位修改的顺序和修改后的AR2的值。

(填入表格的空格内)答:AR0的低3位取值应为二进制值。

8. TMS320C54X DSP的定时器中,若TDDR=0101B,PRD=0018H,试计算定时器的中断频率。

DSP技术复习资料-完整版

D S P技术复习资料-完整版-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIANDSP(数字信号处理)技术复习资料1.简述数字信号处理器的主要特点(P4)。

数字信号处理(Digital Signal Processing)简称DSP。

主要特点:(1)采用哈佛结构;(2)采用多总线结构;(3)采用流水线结构;(4)配有专用的硬件乘法器-累加器;(5)具有特殊的寻址方式和指令;(6)支持并行指令操作;(7)硬件配置强,具有较强的接口功能;(8)支持多处理器结构。

2. 请给出数字信号处理器的运算速度指标(P6)。

(1)MAC时间:一次乘法和一次加法的时间;(2)FFT执行时间:运行一个N点FFT程序所需的时间;(3)MIPS:每秒执行百万条指令;(4)MOPS:每秒执行百万次操作;(5)MFLOPS:每秒执行百万次浮点操作;(6)BOPS:每秒执行十亿次操作。

(7)指令周期:执行一条指令所需的最短时间,数值等于主频的倒数;常用ns(纳秒)。

3.简述C55x的存储器配置情况(P11~12)。

(1)C55x采用统一的存储空间和I/O空间;(2)C55x的片内存储空间共有352KB(146K字),外部存储空间共有16MB(8M字);(3)存储区支持的存储器类型有异步SRAM,异步EPROM、同步DRAM 和同步突发SRAM;(4)C55x的I/O空间与程序/地址空间分开;(5)I/O空间的字地址为16位,能访问64K字地址;(6)当CPU读/写I/O空间时,在16位地址前补0来扩展成24位地址。

4.TMS320C55x的寻址空间是多少?当CPU访问程序空间和数据空间时,使用的地址是多少位(P51、P53~54)。

(1)C55x的寻址空间为16MB(24位地址,2^24 = 16777216B = 16MB)(2)CPU访问程序空间时,使用24位的地址;(3)访问数据空间时,使用23位地址,使用时23位地址左移一位将地址总线上的最低有效位(LSB)置0。

DSP复习资料

DSP复习资料1.美国德州仪器(TI)公司生产的TMS320系列芯片主推C2000系列,C5000系列,C6000系列,试分析这三种系列芯片的典型应用领域。

答:C2000系列面向工业产品控制,低价位;C5000系列面向通信类应用,性能好,低功耗,有利于便携式通信产品及其他仪器的推出;C6000系列面向高档次应用,如多媒体,图像处理及其他超高速处理场合。

2.数字信号处理的硬件实现可分为单片机实现和DSP实现,试对比分析两者各自主要的优点,缺点。

答:单片机:优点:接口性能好;缺点:总线结构是冯·诺依曼结构,系统复杂,特别是乘法运算速度慢;DSP:优点:哈佛总线结构,内部具有硬件乘法器等可以实现某些特定功能,具有很高的并行特性,专门的指令系统;缺点:灵活性差。

3.试分析冯·诺依曼结构与哈佛总线结构各自的特点。

答:冯·诺依曼结构:程序存储和数据存储共用一个存储空间。

编址依靠指令计数器提供的地址来区分是指向数据还是地址,只能串行执行,速度慢,数据吞吐量小;哈佛总线结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,允许直接在程序和数据之间进行信号传递,具有高速运算能力。

4.DSP区别于通用微处理器的重要标志?答:硬件乘法器。

5.简述定点DSP和浮点DSP的区别。

答:在定点DSP中,小数点的位置在一个数据字中是固定的。

而在浮点格式中,一个数据字被分成两部分,分别表示指数和底数,因此它所表示的数据的小数点随着指数的变化而浮动。

浮点格式所能表示的数据范围要比定点格式大得多,在大多数应用中都不需要特别考虑运算的溢出问题。

6. DSP中的地址产生单元-ARAU。

7.名词翻译:ARAU:辅助寄存器算术单元 Auxiliary Registers:辅助寄存器CALU:中央算术逻辑单元 Barrel shifter:桶型移位器Multiplier:硬件乘法器 Accumulator:累加器CSSU:比较、选择和存储单元8.TMS320C2000系列的内部总线结构?答:6条:其中是3条地址线,PAB程序地址总线,DRAB数据读地址总线,DWAB数据写地址总线;其他3条为PRDB程序读总线,DRDB数据读总线,DWEB数据写总线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

10、链接命令文件主要内容是什么? 答:链接器命令文件主要包含如下内容: (1)输入文件名,就是要链接的目标文件和文档库文件,或者是其它的命令文件。如果要 调用另一个命令文件作为输入文件, 此句一定要放在本命令文件的最后, 因为链接器不能从 新调用的命令文件返回。 (2)链接器选项。这些选项既可以用在链接器命令行,也可以编在命令文件中。它们在命 令文件中的使用方法与在命令行中相同。 (3)MEMORY 和 SECTIONS 都是链接器命令,用来指定目标存储器结构和地址分配。如 果链接命令文件中没有 MEMORY 和 SECTIONS 命令 (默认情况) , 则链接器就从地址 0080h 一个段接着一个段进行配置。 12、简述混合编程的三种主要方法。 答:(l)独立编写 C 程序和汇编程序,分开编译或汇编形成各自的目标代码模块,然后用 链接器将 C 模块和汇编模块链接起来 (2)在 C 语言程序中使用汇编程序的变量和常数及函数 (3)直接在 C 语言程序的相应位置嵌入汇编语句。 1、简述汇编语句有哪两种格式。 答:汇编语句有两种格式,一种是常见的助记符格式,另一种是代数指令格式。 1)助记符格式 [标号] [ :] 操作码助记符 [操作数列表] [;注释] 2)代数指令格式 [标号] [ :] 代数指令 [;注释] 4、如何确定操作数是地址还是立即数或间接地址? 答:汇编器允许在操作数前使用前缀来指定操作数(常数、符号或表达式)是地址还是立即 数或间接地址。 1)前缀#。操作数作为立即数。即使操作数是寄存器或地址,也当作立即数处理。此 时,汇编器将地址处理为一个值,而不当做地址处理。 2)前缀*。操作数作为间接地址。汇编器将此操作数作为间接地址对待,它将操作数中 的内容作为地址; 3)前缀@。表示其后的操作数是采用直接寻址或绝对地址寻址的地址。在代数指令中 不能省略,但是在助记符指令中可以省略。 2、TMS320C5000 提供了哪几种数据寻址模式? 答:C5000 共有 7 种有效的数据寻址方式。 1)立即寻址:指令中嵌有固定的数,主要用于初始化。 2)绝对寻址:利用 16 位地址寻址存储单元。 3)累加器寻址:把累加器的内容作为地址。 4)直接寻址:利用数据存储器页指针和堆栈指针寻址。 5)间接寻址:利用辅助寄存器作为地址指针。

第 2 页 共 ( 8 ) 页

5)控制宏扩展列表。 使用一个宏分 3 个过程:定义宏、调用宏和扩展宏。 5、什么是段,段的作用是什么? 答:所谓段,是指连续的占有存储空间的一个数据或代码块。 汇编语言源程序按段组织, 每行汇编语句都从属于一个段, 并由段汇编伪指令表明该段的属 性。一个目标文件中的每一个段都是分开的和各不相同的。段(Sections)是 COFF 格式目 标文件中最重要的概念,也是目标文件中的最小单位。每个目标文件都分成若干个段。 6、汇编程序中,系统默认段有哪些?各段的具体作用是什么? 答:所有的 COFF 格式目标文件都至少包含以下 3 种形式的默认段: .text 段 通常包含可执行代码; .data 段 通常包含初始化数据; .bss 段 通常为未初始化变量保留存储空间。 7、自定义段、子段的含义是什么,如何编写和定义? 答:自定义段也叫做命名段,是由.sect 和.usect 命令建立,需要自己定义段名的段。它们除 了被分开汇编外,其它方面和默认的.text、.data 和.bss 段在使用上相同。另外,不能用不同 的伪指令处理名字相同的段。 子段是大段中的小段。子段可以通过.sect 和.usect 伪指令产生。子段命名的句法为: 基段名: 子段名 当汇编器在基段名后面发现冒号, 则紧跟其后的段名就是子段名。 子段的定位方法和段 相同,既可以单独为其分配存储单元,也可以在相同的基段名下与其他段组合在一起。子段 也有 2 种类型:用.sect 命令建立的初始化段和用.usect 命令建立的段是未初始化段。 8、汇编器对段是如何处理的? 答: 汇编器的任务是在汇编过程中, 根据汇编命令用适当的段将各部分程序代码和数据连在 一起,构成目标文件。汇编器对段的处理功能主要是根据段名,确定汇编语言程序中的各部 分属于哪个特定的段,最终形成几个独立的段。其功能包含两层含义: (1)相同段名放在连续空间; (2)不同段名各自独立。 9、链接器对段是如何处理的? 答:链接器在处理段的时候,有如下两个主要任务: 1)把一个或多个 COFF 目标文件(.obj 文件)中的各种段作为链接器的输入段,经链接后 在一个可执行的 COFF 输出模块中建立各个输出段。 2) 在程序装入时对其重新定位,为各个输出段选定存储器地址。 为完成如上任务,链接器提供了两条命令支持,即: 1)MEMORY 命令。此条命令用来定义目标系统的存储器配置空间,包括对存储器各部 分命名,以及规定它们的起始地址和长度; 2)SECTIONS 命令。此命令告诉链接器如何将输入段组合成输出段,以及将输出段在 存储器中的什么位置。

第 4 页 共 ( 8 ) 页

6)存储器映像寄存器寻址:修改映射像存器中的值,不影响当前数据存储器页指针和 堆栈指针的值。 7)堆栈寻址:用来管理系统堆栈中的操作,即把数据压入和弹出系统堆栈。由标号域、 操作码助记符域、操作数域和注释域组成。 3、什么是立即寻址,什么是绝对寻址,二者的区别是什么? 答:所谓立即寻址,就是指令中包含了立即操作数,操作数紧随操作码存放在程序存储器中 的寻址方式。 如果指令中包含的是寻找操作数的 16 位单元地址,那么称这种寻址方式为绝对寻址。 二者区别是: 立即寻址的操作数随操作码存放在程序存储器中, 故在执行时没有寻找数 据地址的过程,因此运行速度快,而绝对寻址需要根据操作数地址来寻址操作数,故运行速 度慢;立即寻址的操作数需要占用程序存储空间,而绝对寻址则不需要;立即寻址的操作数 不能改变,常用于表示常数和初始化寄存器,而绝对寻址的操作数可以任意改变,常用于非 实时的场合。 5、什么是直接寻址,直接寻址如何形成 16 位数据单元地址? 答:直接寻址就是利用数据页指针 DP 或堆栈指针 SP 寻址。 CPL=0 时,处理器将 DP 的 9 位基地址与指令中的 7 位偏移地址连接起来,形成 16 位 的数据存储空间存储单元的地址。 CPL=1 时,选择 SP 的 16 位基地址加上指令中的 7 位偏移地址,形成 16 位的数据存 储空间存储单元的地址。 6、什么是间接寻址,间接寻址有哪些句法? 答:间接寻址就是利用辅助寄存器(AR0~AR7)作为地址指针进行寻址。间接寻址可 分为单操作数间接寻址和双操作数间接寻址 11、C54x 的中断分为哪几类? 答:总体来说,C54x 中断可以分成可屏蔽中断和非屏蔽中断两大类。 第一类:可屏蔽中断。这些都是可以用软件来屏蔽或开放的中断。 第二类:非屏蔽中断。这些中断是不能够屏蔽的。C54x 对这一类中断总是响应的,并 及时从主程序转移到中断服务程序。C54x 的非屏蔽中断包括所有的软件中断以及两个外部 硬件中断 RS (复位)和 NMI (也可以用软件进行 RS 和 NMI 中断)。 12、C54x 的可屏蔽中断如何实现中断屏蔽与解屏蔽? 答:1)中断屏蔽: ST1 寄存器中的 INTM=l,所有可屏蔽中断被禁止。 2)中断开放:(以下两个条件需要同时满足) (1)ST1 寄存器中的 INTM =0,所有可屏蔽中断开放; (2)当中断屏蔽寄存器(IMR)的任何一位为 l 就会开放相应的中断。 13、C54x 的中断向量地址如何形成?

第 1 页 共 ( 8 ) 页

3)用单片机(如 MCS-51、96 系列等)实现。 4)用 FPGA 等产品实现数字信号处理算法。 5)用通用的可编程 DSP 芯片实现。 5、CCS 开发环境提供了哪些图形显示功能,如何使用? 答:CCS 可以提供 4 类图形显示,即时域/频域图、星座图、眼图和图像显示。 在 CCS 菜单栏中选择 View→Graph 命令,弹出一个图形类型选择级联菜单,选择图像 显示类型并输入相关信息即可使用。 1、简述 DSP 程序调试的三种常用方法。 答:1)利用软件仿真器进行调试。 这种方式不需要目标硬件,只需在 PC 机上就可以运行。它可以仿真 C54x DSP 芯片包 括中断以及输入/输出在内的各种功能,从而可以在非实时条件下完成对用户程序的调试。 2)利用硬件仿真器进行调试。 这种方式需要用户提供带 C54x DSP 芯片的系统级目标板。C54x 的硬件扫描仿真器采 用 JTAG IEEE 1149.1 标准,仿真插头共有 14 个引脚,扫描仿真器通过仿真头将 PC 机中的 用户程序代码下载到目标系统的存储器中, 并在目标系统内实时运行, 这给程序调试带来了 很大的方便。 3)利用评价模块进行调试 C54x 评价模块(EVM 板)是一种带有 DSP 芯片的 PC 机 ISA 插卡。卡上还配置有一 定数量的硬件资源,用户建立的程序,可以在 EVM 板上运行。通过运行,可以评价 DSP 芯片的性能,以确定 DSP 芯片是否满足应用要求。 2、简述汇编伪指令的种类和作用。 答:汇编伪指令是汇编语言程序的一个重要组成部分,一个汇编语言程序中,可能包含多种 汇编伪指令,其作用是为程序提供数据,并且控制汇编的过程。根据其功能可分为如下 8 种伪指令: 1)段定义伪指令; 2)常数初始化伪指令; 3)段程序计数器(SPC)定位伪指令; 4)输出列表格式伪指令; 5)引用其他文件的伪指令; 6)条件汇编伪指令; 7)汇编时符号定义伪指令; 8)其他汇编伪指令。 3、简述汇编宏指令的功能以及使用宏的过程。 答:编译器支持宏语言,允许用户利用宏来创建自己的指令。宏语言的主要功能包括: 1)定义自己的宏和重新定义已存在的宏; 2)简化较长的或较复杂的汇编代码; 3)访问归档器创建的宏库; 4)处理一个宏中的字符串;

使用流水线技术后, 尽管每一条指令的执行仍然要经过这些步骤, 需要同样的指令周期 数,但将一个指令段综合起来看,其中每一条指令的执行都是在一个指令周期内完成的。 10、数字信号处理的实现方法有哪几种? 答:1)在通用的微型计算机(PC 机)上用软件(如 VB、VC 语言)实现。 2)在通用的计算机系统中加上专用的加速处理机实现。

3、DSP 有哪几种分类方式,可将 DSP 芯片分成哪几类? 答:DSP 有三种分类方式:按基础特性分类、按数据格式分类和按用途分类。 按基础特性可分为静态 DSP 芯片和一致性 DSP 芯片; 按数据格式可分为定点 DSP 芯片和浮点 DSP 芯片; 按照用途可分为通用型 DSP 芯片和专用型 DSP 芯片。 7、冯·诺伊曼结构和哈佛结构的主要区别是什么?与前者相比,哈佛结构有何优势? 答:1)主要区别: 冯·诺伊曼结构采用单存储空间, 即程序指令和数据共用一个存储空间, 使用单一的地 址和数据总线。 哈佛结构采用双存储空间, 程序存储器和数据存储器分开, 有各自独立的程序总线和数 据总线。 2)哈佛结构优势 哈佛结构可独立编址和访问,可对程序和数据进行独立传输,使取指令操作、指令执行 操作、数据吞吐并行完成,极大地提高了数据处理能力和指令的执行速度,非常适合于实时 的数字信号处理。 8、以四级流水线为例,介绍 DSP 所采用的流水线技术。 答:计算单元在执行一条多周期指令时,总要经过取指、译码、取数、执行、写结果等步骤, 需要若干指令周期才能完成。 流水线技术是将各指令的各个步骤重叠起来执行, 而不是一条指令完成后, 才开始执行 下一条指令。即在每个指令周期内,几个不同的指令均处于激活状态,每个指令处于不同的 阶段。如下图所示,在第 N 个指令取指令时,前面一个即第 N-1 个指令正在译码,而第 N-2 个指令正在取操作数,第 N-3 个指令则正在执行指令。