实验4 AES IP核的控制模块的设计与仿真以及系统集成与仿真-推荐下载

应用于MCU的低功耗AES_IP核的设计

应用于MCU的低功耗AES_IP核的设计随着物联网和嵌入式系统的快速发展,对于低功耗和高安全性的需求也越来越迫切。

在这个背景下,AES(Advanced Encryption Standard)成为了一种广泛应用的加密算法。

为了满足物联网和嵌入式设备对低功耗的要求,设计一种应用于MCU的低功耗AES_IP核显得尤为重要。

首先,我们需要明确设计目标。

低功耗是设计的首要目标,因为在物联网和嵌入式设备中,能耗是一个至关重要的指标。

因此,我们需要选择并优化合适的算法和电路结构,以降低功耗。

而AES算法本身也具有高安全性的特点,能够满足数据加密的需求。

其次,我们需要考虑如何降低功耗。

首先,通过使用低功耗电路技术,如管脚驱动技术和节能电源管理技术,可以有效降低功耗。

其次,通过优化电路结构和算法实现,减少不必要的计算和存储开销。

另外,还可以采用时钟门控和数据压缩等技术,进一步提高功耗效率。

在设计过程中,我们需要特别关注安全性。

AES算法是一种对称加密算法,具有较高的安全性。

然而,为了保证数据的完整性和机密性,我们需要采取一系列安全措施。

例如,加入数据校验和错误检测机制,以及对密钥进行保护和管理。

最后,我们需要对设计进行验证和测试。

通过使用仿真和测试工具,验证设计的正确性和性能。

同时,还需要进行功耗测试和安全性测试,以确保设计符合预期要求。

综上所述,设计一种应用于MCU的低功耗AES_IP核是一项具有挑战性和重要性的任务。

通过选择合适的算法和电路结构,并采用低功耗电路技术和安全措施,可以实现高效低功耗的AES 加密。

这将为物联网和嵌入式设备的发展提供强大的数据保护和安全性支持。

适用于嵌入式系统的AES加密IP核设计

适用于嵌入式系统的AES加密IP核设计关键词: AES加密;嵌入式系统;IP核设计Rijndael加密算法于2000年被确定为美国高级加密标准AES(Advanced Encryption Standard),现在己是工业界数据加密的通用标准之一。

Rijndael算法无论从理论分析,还是在实践应用都表现出很好的抵抗各种攻击的性能,其安全性是不容置疑的。

随着计算机技术、微电子技术的不断融合,嵌入式系统应用得到了迅猛发展。

近年来嵌入式技术广泛用于解决保密信息的传输、存储和管理方面的问题。

而这些都需要嵌入式系统集成有可靠的加密模块。

现有一些应用中的加密模块还不尽如人意。

本文针对此应用需求设计一种适用于嵌入式系统的加密IP核。

1AES算法1.1AES算法描述密钥密码体制分为流密码和分组密码两种。

分组密码是信息与网络安全中实现数据加密、数字签名、认证及密钥管理的核心体制,具有速度快、易于标准化和便于软硬件实现等特点。

AES采用分组密码的加密方式,其分组长度分为128 bit、192 bit、256 bit三种,AES密码在相同的轮函数作用下,迭代运算次数的不同可达到不同级别的安全强度。

128 bit分组长度的情况下,循环轮数指定为11次,目前还没有可行的算法可以对该模型进行有效攻击[1]。

每一轮处理均为作用在中间结果上的一批运算,该中间结果称为状态,用4×4字节矩阵表示,其中,数据矩阵称为State、密钥矩阵称为Key。

AES加密涉及5种运算,分别是字节代换(SubBytes)、行移变换(ShiftRows)、列混合变换(MixColumns)、密钥加法(AddRoundKey)和密钥扩展(ExpandedKey)。

字节代换是对State每个字节进行独立非线性变换,由字节在GF(28)域中求其乘法逆并外加一个仿射变换完成[2]。

具体实现中广泛使用查表方式完成该步变换(实现该功能单元被称为Sbox),以避免复杂的乘法运算。

集成电路设计仿真验证分享案例

3.关注新兴领域的发展动态,如量子计算、新型存储技术等,为集成电路设计带来新的创新点。

4.加强产学研合作,培养高素质的专业人才,以应对行业快速发展的人才需求。

5.开展跨学科研究,结合材料科学、生物学等领域的新进展,开拓集成电路设计的新方向。

-关键因素:市场需求的快速变化导致设计风险增加,产品上市时间成为竞争的关键。

-问题剖析:如何在不牺牲产品质量的前提下,缩短设计周期,降低开发成本。

3.人才与教育层面的挑战:集成电路设计是高技术含量的领域,对人才的专业知识和技能要求极高。

-主要挑战:行业内高端人才短缺,人才培养周期长,教育与实践之间存在较大差距。

-竞争激烈,企业间在技术、产品、服务等方面展开全方位竞争。

-市场趋势分析:未来市场将继续向高性能、低功耗、智能化方向发展,同时,物联网、人工智能等新兴领域将为集成电路设计带来新的增长点。

七、发展趋势与未来展望

集成电路设计领域在未来将持续引领科技创新,其发展趋势和前景充满机遇与挑战。

发展趋势:

1.技术微型化:随着摩尔定律的持续演进,集成电路的工艺节点将不断缩小,向3纳米甚至更先进的工艺发展。这将极大提升集成电路的性能,降低功耗,但同时也带来了一系列技术挑战,如量子效应、热管理等问题。

回顾集成电路设计领域的发展历程,从20世纪70年代的CMOS技术取代双极型晶体管,到90年代的深亚微米工艺,再到21世纪初的纳米级工艺,设计规模不断扩大,设计复杂度不断上升。当前,集成电路设计已进入16/14纳米甚至更先进的工艺节点,设计方法学也在不断演变,如基于IP核的设计、系统级设计等。

在社会中的实际应用方面,集成电路设计已深入人们生活的方方面面。以智能手机为例,其内部集成了大量的集成电路,用于实现通信、计算、摄影等功能。此外,在人工智能、物联网、大数据等新兴领域,集成电路设计的地位更是至关重要。

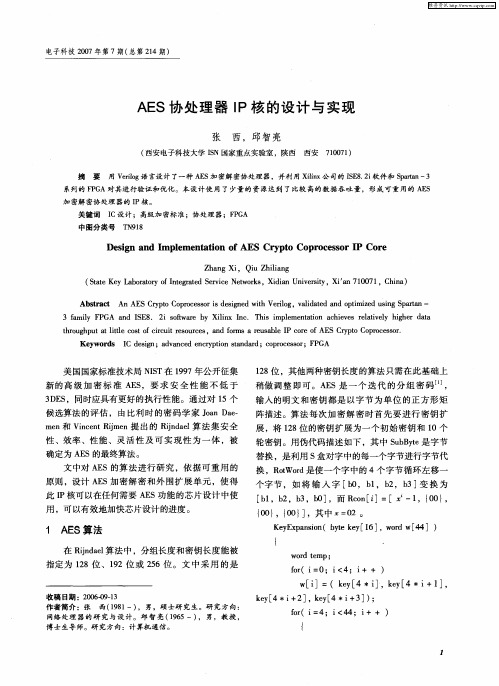

AES协处理器IP核的设计与实现

ky 4 i 2 , e[ i 3 ) e[ + ] ky 4 + ] ;

o (i 4;i 4 fr = < 4;i ++ )

1 A S算法 E

在 Rj a 算法中,分组长度和密钥长度能被 i de n l

指定 为 18位 、12位 或 26位 。文 中采 用 的 是 2 9 5

{

wo d tபைடு நூலகம்mp; r e

.

fr = o (i 0;i 4 ++ ) < ;i

Wi []=(ky 4木 ] ky 4木i ] e[ i , e[ +1 ,

候选算法的评估 ,由比利时 的密码学 家 Ja a. onD e

m n和 Vnet i n提 出 的 Rjd e算 法 集 安 全 e icn j R me i al n 性 、效 率 、性 能 、灵 活 性 及 可 实 现 性 为 一 体 ,被

展 ,将 18 的密钥扩展为一个初始密钥和 l 2位 0个

Ke wo d I d sg ;a v c n r pin sa d r y r s C e i n d a e e c to t a d;c p o e s r PGA n d y n o r c s o ;F

美 国 国家标 准技 术局 NS IT在 19 97年公 开征 集

18 ,其他两种密钥长度的算法只需在此基础上 2位

维普资讯

电子科技 2 0 0 7年第 7期( 总第 2 4期) 1

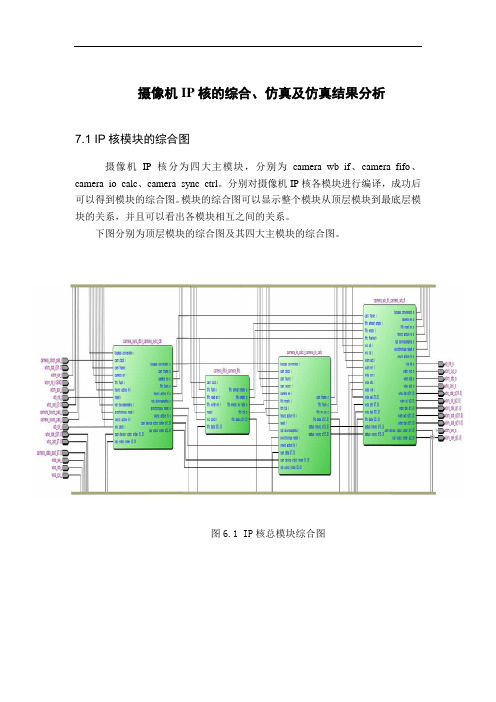

摄像机IP核的综合、仿真及仿真结果分析

摄像机IP核的综合、仿真及仿真结果分析7.1 IP核模块的综合图摄像机IP核分为四大主模块,分别为camera_wb_if、camera_fifo、camera_io_calc、camera_sync_ctrl。

分别对摄像机IP核各模块进行编译,成功后可以得到模块的综合图。

模块的综合图可以显示整个模块从顶层模块到最底层模块的关系,并且可以看出各模块相互之间的关系。

下图分别为顶层模块的综合图及其四大主模块的综合图。

图6.1 IP核总模块综合图图6.2camera_wb_if 模块综合图图6.3 camera_fifo 模块综合图camera_wb_if 模块综合图(局部)图6.4 camera_io_calc综合图(局部)图6.5 camera_sync_ctrl模块综合图7.2 模块的功能说明、仿真及仿真结果分析本论文将分别对摄像机IP核的四大主模块camera_wb_if、camera_fifo、camera_io_calc、camera_sync_ctrl进行功能说明、仿真及仿真结果分析。

camera_wb_if:功能说明:本模块以wishbone总线为核心,为其他三个模块提供公共数据及wishbone主从设备接口,方便各个模块的数据传输、控制,和IP核功能的实现。

仿真结果分析:由于本IP核原采用Xilinx软件开发环境,而该模块调用了Xilinx软件开发环境中的部分模块,导致本模块不能在此次的Quartus ii开发环境中进行仿真。

因此本模块没有进行仿真。

camera_fifo:功能说明:FIFO是先入先出存储器,本模块将来自camera_io_calc 模块的数据进行暂时存储,以便将数据在wishbone主设备的控制下通过camera_wb_if(wishbone总线)模块传输到wishbone从设备中。

仿真图:图6.6仿真结果分析:由上图,可以看出,本模块采用的是双时钟,亦即模块存在异步时钟域,这是FIFO的典型结构。

现代VLSI设计-基于IP核的设计第四版教学设计

现代VLSI设计-基于IP核的设计第四版教学设计介绍现代VLSI(Very Large Scale Integration)设计是电子工程领域中的一个重要分支,指的是使用现代化的电路设计软件和设计流程来实现大规模集成电路的设计。

这种设计方法能够极大地提高电路设计的效率和准确性,同时也可以减少电路设计的成本。

近年来,随着计算机科学的蓬勃发展,IP(Intellectual Property)核的概念也越来越受到关注。

IP核是可重用的、自成体系的设计模块,可以用于较复杂的数字电路设计。

很多公司和团队使用IP核进行更高效、更可靠的VLSI设计。

本教学设计将重点介绍基于IP核的现代VLSI设计方法。

教学目标本教学设计旨在让学生掌握以下技能和知识:1.理解现代VLSI设计的基本概念和设计流程。

2.掌握IP核的设计和使用方法。

3.熟悉IP核库的结构和组成。

4.了解现代FPGA(Field Programmable Gate Array)芯片的原理和应用。

教学内容和方法教学内容本教学设计分为以下几个部分:1.现代VLSI设计概述2.IP核的设计和使用方法3.IP核库的结构和组成4.现代FPGA芯片的原理和应用教学方法本教学设计采用以下教学方法:1.讲授课程内容。

2.分组讨论和演示。

3.实验操作。

对于每个部分的具体教学方法和安排,下面给出详细说明。

1. 现代VLSI设计概述在这个部分,我们将对现代VLSI设计的基本概念和设计流程进行讲授。

主要内容包括:1.电路设计的基本流程。

2.现代VLSI设计的主要特点和优势。

3.现代VLSI设计的主要挑战和解决方案。

这个部分的教学方法是讲授,通过讲解让学生了解现代VLSI设计的基本概念和设计流程。

2. IP核的设计和使用方法在这个部分,我们将介绍IP核的设计和使用方法。

主要内容包括:1.IP核的基本概念和使用场景。

2.IP核的设计方法和过程。

3.IP核的验证和测试方法。

这个部分的教学方法是分组讨论和演示。

现代VLSI设计-基于IP核的设计第四版课程设计

现代VLSI设计-基于IP核的设计第四版课程设计一、背景介绍现代集成电路设计是电子信息工程学科体系中重要的一环,在现代电子信息领域有着广泛的应用。

随着技术的不断进步,集成度的要求越来越高,逐渐从单个器件转向系统级芯片设计,为此,设计人员要对现代VLSI设计有深入的了解和掌握。

本课程设计基于IP核的设计,旨在通过具体的实际案例,提高学生对现代VLSI设计的理解,并学习如何利用常见IP核优化系统性能,达到减少设计成本、提高设计效率、提高设计可维护性的目的。

二、设计目标本次课程设计的主要目标是掌握VLSI设计的基本原理和流程,学习如何使用IP核进行设计,理解如何对电路进行优化。

三、课程内容3.1 VLSI设计基本原理VLSI(Very Large Scale Integration)是指超大规模集成电路。

VLSI设计主要包括从设计到工艺、测试等多个环节,本部分将学习VLSI设计的基本流程、器件结构、工艺和测试方法等基本知识。

3.2 IP核简介IP核(Intellectual Property)是指独立的设计模块,可以被其他不同的电路利用。

IP核的设计和应用可以大大简化电路设计,提高设计效率和可维护性。

本部分将学习IP核的基本原理、分类和应用场景。

3.3 IP核的设计本部分将围绕基于IP核的设计开展实际操作,涉及IP核的设计和应用。

具体包括如何使用Vivado软件进行IP核的设计和如何利用IP核完成特定功能的设计。

3.4 IP核的优化本部分将介绍如何使用IP核进行电路优化,旨在提高系统设计的性能和可靠性。

具体包括如何对IP核进行定制化、如何进行IP核的性能评估以及如何评估系统的功耗等。

四、课程实践本课程设计将通过实践案例学习VLSI设计、IP核的设计与优化。

4.1 实践案例1:基于IP核的数字信号处理系统设计本案例将指导学生利用IP核进行一个简单的数字信号处理系统设计,包括数据输入输出模块、FIR滤波器模块、FFT模块。

ip核的封装与调用实验报告

IP核的封装与调用实验报告1. 背景IP核(Intellectual Property Core)是一种可重用的硬件设计模块,可以嵌入到FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit)芯片中。

IP核的封装与调用是将设计好的IP核打包,并在设计中进行调用的过程。

本实验旨在通过对一个简单的IP核进行封装和调用,加深对IP核概念和使用方法的理解,并掌握相应工具的使用技巧。

2. 分析2.1 IP核封装2.1.1 IP核设计首先,需要设计一个简单的IP核。

本实验选择了一个4位加法器作为示例。

该加法器能够对两个4位二进制数进行相加,并输出一个4位结果。

2.1.2 IP核封装步骤将设计好的IP核进行封装,主要包括以下几个步骤:1.打开Vivado软件,创建一个新项目。

2.在项目中创建一个新工程。

3.添加设计文件:将之前设计好的加法器模块添加到工程中。

4.设置顶层模块:选择加法器模块作为顶层模块。

5.进行综合和实现:生成综合后的网表文件和比特流文件。

6.封装IP核:在IP目录中创建一个新的IP核,将综合后的网表文件和比特流文件添加到IP核中。

7.配置IP核参数:设置输入输出端口、位宽等参数,并生成包含封装信息的XCI文件。

2.2 IP核调用2.2.1 调用环境准备在使用封装好的IP核之前,需要进行一些调用环境的准备工作:1.创建一个新项目。

2.在项目中创建一个新工程。

3.添加设计文件:将需要使用IP核的模块添加到工程中。

4.添加IP核:将之前封装好的加法器IP核添加到工程中。

2.2.2 IP核调用步骤完成调用环境准备后,可以按照以下步骤进行IP核的调用:1.在设计模块中实例化IP核:使用<ip_name>_inst语句实例化加法器IP核,并连接输入输出信号。

2.设置输入信号:根据实际需求设置输入信号的值。

实验四AES算法的实现

实验四AES算法的实现AES(Advanced Encryption Standard)也被称为Rijndael算法,是一种对称密钥加密算法,被广泛应用于各种安全领域。

本实验将介绍AES算法的实现过程和原理。

AES算法采用分组密码的方式进行加密,其中,明文和密钥的长度可以是128位、192位或256位。

AES算法的加密和解密过程,主要包括四个步骤:字节替代、行移位、列混淆和轮密钥加。

下面将一一介绍这些步骤。

第一步是字节替代(SubBytes),该步骤通过S盒(Substitution Box)将每一个字节替换为另一个字节,实现数据的置换。

S盒是一个16×16的字节矩阵,在AES算法中具有固定的值。

字节替代的目的是增加混淆性,使得算法更加安全。

第二步是行移位(ShiftRows),该步骤对每一行进行循环左移操作,使得每一列的字节发生移位。

行移位的目的是使得列与列之间具有更强的混淆性,增加攻击的难度。

第三步是列混淆(MixColumns),该步骤对每一列进行线性变换操作,通过乘积进行矩阵运算。

列混淆的目的是进一步增加数据的混淆性,使得密文与明文之间的关系更加复杂。

第四步是轮密钥加(AddRoundKey),该步骤将每一轮的密钥与明文进行异或操作,实现加密过程中的扩散。

轮密钥加的目的是每一轮中引入不同的密钥,增加密文与密钥之间的关系,提高安全性。

AES算法共有10轮加密(128位密钥)、12轮加密(192位密钥)或14轮加密(256位密钥)。

其中,第一轮为密钥初始加轮,最后一轮没有列混淆操作。

在实现AES算法时1.需要实现字节替代操作时,可以使用S盒进行字节替代;2.需要实现行移位操作时,可以使用循环左移操作;3.需要实现列混淆操作时,可以使用矩阵运算;4.需要实现轮密钥加操作时,可以使用异或操作。

为了提高算法的安全性,还可以采用其他的扩展技术,如混淆技术和迭代技术。

同时,还应该注意选择适当的密钥长度,以满足不同安全需求。

实验4 AES IP核的控制模块的设计与仿真以及系统集成与仿真

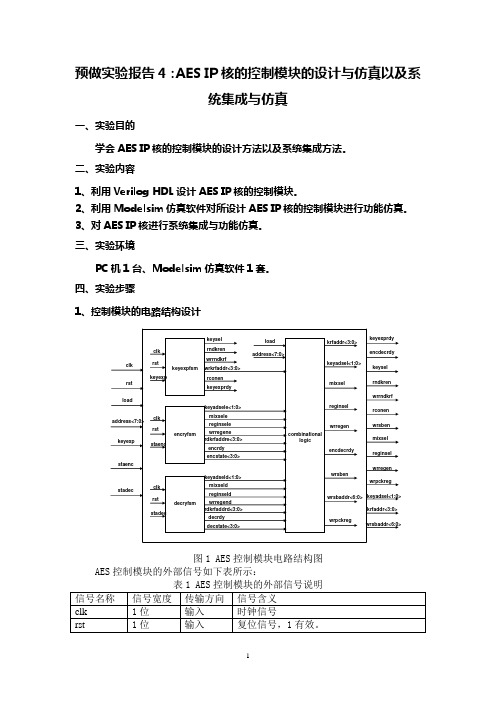

预做实验报告4:AES IP核的控制模块的设计与仿真以及系统集成与仿真一、实验目的学会AES IP核的控制模块的设计方法以及系统集成方法。

二、实验内容1、利用Verilog HDL设计AES IP核的控制模块。

2、利用Modelsim仿真软件对所设计AES IP核的控制模块进行功能仿真。

3、对AES IP核进行系统集成与功能仿真。

三、实验环境PC机1台、Modelsim仿真软件1套。

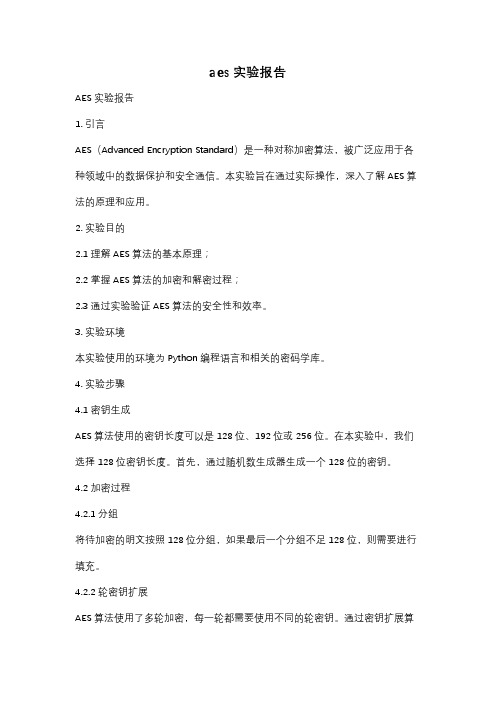

四、实验步骤1、控制模块的电路结构设计图1 AES控制模块电路结构图AES控制模块的外部信号如下表所示:图2 AES加密状态机状态转移图2、建立控制模块的Verilog模型moduleaescontrol(clk,rst,load,address,keyexp,staenc,stadec,keyexprdy,encde crdy,keysel,rndkren,wrrndkrf,krfaddr,rconen,wrsben,wrsbaddr,keyadsel ,mixsel,reginsel,wrregen,wrpckreg);output keyexprdy,encdecrdy,keysel,rndkren,wrrndkrf,rconen;output wrsben,mixsel,reginsel,wrregen,wrpckreg;output [1:0] keyadsel;output [3:0] krfaddr,wrsbaddr;input clk,rst,load,keyexp,staenc,stadec;input[4:0] address;wire [3:0] wrkrfaddr,rdkrfaddre,rdkrfaddrd,encstate,decstate;wire [1:0] keyadsele,keyadseld;wiremixsele,reginsele,wrregene,encrdy,mixseld,reginseld,wrregend,decrdy;assign krfaddr=(encstate != 4'd0)? rdkrfaddre:((decstate != 4'd0)?rdkrfaddrd:wrkrfaddr);assign keyadsel=(encstate != 4'd0)? keyadsele:keyadseld;assign mixsel=(encstate != 4'd0)? mixsele:mixseld;assign reginsel=(encstate != 4'd0)? reginsele:reginseld;assign wrregen=(encstate != 4'd0)? wrregene:wrregend;assign encdecrdy=encrdy & decrdy;keyexpfsmkeyexpfsm(clk,rst,keyexp,keysel,rndkren,wrrndkrf,wrkrfaddr,rconen,ke yexprdy);encryfsmencryfsm(clk,rst,staenc,keyadsele,mixsele,reginsele,wrregene,rdkrfad dre,encrdy,encstate);decryfsmdecryfsm(clk,rst,stadec,keyadseld,mixseld,reginseld,wrregend,rdkrfad drd,decrdy,decstate);assign wrsben=load & ~address[4];assign wrsbaddr=address[3:0];assign wrpckreg=load & address[4] & ~address[3] & ~address[2] & ~address[1] & ~address[0];endmodule3、设计控制模块的测试文件`timescale 1ns / 1nsmodule aescontrol_tb;wire keyexprdy,encdecrdy,keysel,rndkren,wrrndkrf,rconen;wire wrsben,mixsel,reginsel,wrregen,wrpckreg;wire [1:0] keyadsel;wire [3:0] krfaddr,wrsbaddr;reg clk,rst,load,keyexp,staenc,stadec;reg [4:0] address;aescontrolaescontrol(clk,rst,load,address,keyexp,staenc,stadec,keyexprdy,encde crdy,keysel,rndkren,wrrndkrf,krfaddr,rconen,wrsben,wrsbaddr,keyadsel ,mixsel,reginsel,wrregen,wrpckreg);//clock generationinitial clk = 1;always #50 clk = ~clk;initialbegin#20 rst=1;load=0;address=5'd0;keyexp=0;staenc=0;#200 rst=0;load=1;address=5'd0; keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd1; keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd2; keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd3; keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd4; keyexp=0;stadec=0;#100 rst=0;load=1;address=5'd5;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd6;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd7;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd8;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd9;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd10;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd11;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd12;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd13;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd14;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd15;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd16;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd17;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd18;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd19;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd20;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd21;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd22;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd23;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd24;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd25;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd26;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd27;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd28;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd29;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd30;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=1;address=5'd31;keyexp=0;staenc=0;stadec=0;#100 rst=0;load=0;address=5'd0;keyexp=1;staenc=0;stadec=0;#100 rst=0;load=0;address=5'd1;keyexp=0;staenc=0;stadec=0;#1200 rst=0;load=0;address=5'd2;keyexp=0;staenc=1;stadec=0;#100 rst=0;load=0;address=5'd3;keyexp=0;staenc=0;stadec=0;#1200 rst=0;load=0;address=5'd16;keyexp=0;staenc=0;stadec=1;#100 rst=0;load=0;address=5'd17;keyexp=0;staenc=0;stadec=0; #1200 $finish;endendmodule4、将控制模块的设计文件和测试文件输入Modelsim仿真工具,并进行编译和功能仿真。

网络安全协议分析与应用实验4_IPSEC的AH_ESP

《网络安全协议分析与应用》实验报告实验序号: 4 实验项目名称:IPSEC的AH_ESP学号姓名专业班级20网络工程实验地点指导教师实验时间20一、实验目的及要求1. 掌握IPSEC的原理2. 掌握AH,ESP的工作流程二、实验设备(环境)及要求PC机, VC++等,虚拟云平台Windows 7(C:\software\IPsec协议项目\IPsec可执行程序\IPsec-AH-ESP三、实验原理1) 总体工作流程图2) 类关系图四、实验内容与步骤1、IPSecMain_UI1.1 主界面是供用户进行协议、算法、模式的选择,和让用户填写相关的数据,模拟了协商SA的过程。

几个重要的功能点如下:选择了AH,则加密算法这一项就无法选择;同时密钥在选择了算法的同时就随机生成,用户可修改,但位数有限制;如果有未选择的项或未填写的内容,就有对应的提示信息;客户端和服务器端,能真正在不同的机器上相互通信。

1.2 双击打开C:\software\IPsec协议项目\IPsec可执行程序\IPsec-AH-ESP\演示版-IPsec-AH-ESP.exe。

如图1所示图11.3未选择选项,直接点击“过程展示”按钮,提示“未选择协议”。

如图2所示图21.4选择AH算法后,可以选择认证算法如MD5,但是不能选择加密算法,还可以选择工作模式如传输模式,其他保持默认。

如图3所示图31.5选择ESP算法后,既可以选择认证算法如MD5,还可以选择加密算法如DES,同样可以选择工作模式如传输模式,其他保持默认。

如图4所示图42、IPSec_UI2.1 函数调用图。

如图5所示图52.2 功能描述这个类库主要包含了AH协议和ESP协议传输模式和隧道模式的接收和发送过程8个UI界面。

以及socket通信的服务器端和客户端的两个UI界面。

模块标识模块功能AHTrans_Get AH传输模式输入处理AHTrans_Send AH传输模式输出处理AHTube_Get AH隧道模式输入处理AHTube_Send AH隧道模式输出处理ESPTrans_Get ESP传输模式输入处理ESPTrans_Send ESP传输模式输出处理ESPTube_Get ESP隧道模式输入处理ESPTube_Send ESP隧道模式输出处理几个主要功能点如下:在过程展示界面上的上方,显示在主界面上的选择,可以对选择进行修改,单击“修改”按钮可以跳转到相应的界面(注意:这里可能会弹出相关的报错信息,忽略,单击Continue即可);首次进入界面,单击“开始”按钮则开始展示流程图和原始报文,再次单击“开始”按钮,则询问是否重新开始,是,则重新展示过程;单击“下一步”,显示相应的流程,并显示此时的报文变化;单击“接收过程”(或“发送过程”),跳转到该界面逆过程展示界面。

IP核心网网络仿真技术研究的开题报告

IP核心网网络仿真技术研究的开题报告一、选题背景随着互联网的快速发展,IP核心网已经成为下一代网络架构的必然趋势,其核心是以IP(Internet Protocol)为基础的数据通信网络。

在IP 核心网络中,数据包通过路由器经过指定路径传输,在网络中路由器公共部分为核心层,每个接口都能够执行复杂的网络协议,并且用于交换重要的网络流量。

但是随着网络规模的扩大,IP核心网的设计以及性能验证都变得更加复杂,这就需要利用网络仿真的技术进行模拟验证,以确保网络的高效、安全、可靠,同时提高IP核心网的运营效率和准确性。

二、研究内容本研究旨在选用实际的网络站点与节点为研究对象,利用网络仿真技术进行IP核心网网络仿真实验,主要包括以下内容:1.研究不同网络拓扑的性能,找出适合不同规模的IP核心网的网络拓扑结构。

2.对IP核心网的各个子系统进行建模,并对网络的各个节点进行仿真测试,测试节点的稳定性、数据包传输的速度、网络质量等性能。

3.研究不同流量方案下的网络性能,分析流量分布机制对IP核心网网络性能的影响,并针对网络性能指标进行分析和评估。

4.开发基于网络仿真的网络监控工具,以便对IP核心网的状态实时监控,发现网络异常情况并及时处理。

三、研究意义网络仿真技术可以帮助设计者或运营商在实际部署之前,对网络性能进行全面评估,发现和解决网络问题。

IP核心网网络仿真技术的研究可以有效提高IP核心网的性能和稳定性,为网络设计、优化和维护提供技术支持。

同时,通过深入研究IP核心网网络性能,为网络安全保障提供可靠保证,提高网络的可靠性,降低网络故障的发生率。

因此,探究IP核心网网络仿真技术是有很大实际意义的。

四、预期成果本研究预计能借助网络仿真技术,模拟IP核心网的各种测试场景,实现IP核心网的全面性能评估,包括网络拓扑结构、数据包的传输速度、网络质量等方面的指标。

同时,本研究将研究并开发基于网络仿真的网络监控工具,以实现IP核心网的实时监控和异常检测。

aes 实验报告

aes 实验报告AES实验报告1. 引言AES(Advanced Encryption Standard)是一种对称加密算法,被广泛应用于各种领域中的数据保护和安全通信。

本实验旨在通过实际操作,深入了解AES算法的原理和应用。

2. 实验目的2.1 理解AES算法的基本原理;2.2 掌握AES算法的加密和解密过程;2.3 通过实验验证AES算法的安全性和效率。

3. 实验环境本实验使用的环境为Python编程语言和相关的密码学库。

4. 实验步骤4.1 密钥生成AES算法使用的密钥长度可以是128位、192位或256位。

在本实验中,我们选择128位密钥长度。

首先,通过随机数生成器生成一个128位的密钥。

4.2 加密过程4.2.1 分组将待加密的明文按照128位分组,如果最后一个分组不足128位,则需要进行填充。

4.2.2 轮密钥扩展AES算法使用了多轮加密,每一轮都需要使用不同的轮密钥。

通过密钥扩展算法,将初始密钥扩展为多个轮密钥。

4.2.3 轮函数AES算法的核心是轮函数,它包括字节替代、行移位、列混淆和轮密钥加四个步骤。

这些步骤在每一轮中都会被执行。

4.2.4 轮数循环根据密钥长度的不同,AES算法的轮数也不同。

在本实验中,我们选择10轮加密。

4.2.5 输出密文经过多轮加密后,得到最终的密文。

4.3 解密过程解密过程与加密过程相似,只是在轮密钥的使用上有所不同。

解密过程需要使用逆向的轮密钥。

5. 实验结果与分析通过实验,我们得到了AES算法对明文进行加密和解密的结果。

经过比对,我们可以验证加密和解密的正确性。

同时,我们还可以通过实验数据分析AES算法的安全性和效率。

6. 实验结论AES算法是一种安全可靠的对称加密算法,能够有效地保护数据的机密性。

通过本实验,我们深入了解了AES算法的原理和应用,并且掌握了AES算法的加密和解密过程。

7. 实验总结通过本次实验,我们不仅学习了AES算法的基本原理和应用,还通过实际操作加深了对该算法的理解。

AES协处理器IP核的设计与实现

AES协处理器IP核的设计与实现

张西;邱智亮

【期刊名称】《电子科技》

【年(卷),期】2007(000)007

【摘要】用Verilog语言设计了一种AES加密解密协处理器,并利用Xilinx公司的ISE8.2i软件和Spartan-3系列的FPGA对其进行验证和优化.本设计使用了少量的资源达到了比较高的数据吞吐量,形成可重用的AES加密解密协处理器的IP核.【总页数】4页(P1-3,8)

【作者】张西;邱智亮

【作者单位】西安电子科技大学ISN国家重点实验室,陕西,西安,710071;西安电子科技大学ISN国家重点实验室,陕西,西安,710071

【正文语种】中文

【中图分类】TN918

【相关文献】

1.AES/Rijndael算法协处理器设计与实现 [J], 徐志军;周顺;谢波

2.一种CORDIC协处理器核的设计与实现 [J], 邓凌煊;安军社

3.基于FPGA快速AES算法IP核的设计与实现 [J], 李雪梅;欧海文;路而红;童新海

4.基于FPGA的低成本AES IP核的设计与实现 [J], 张新贺;刘鸿雁;唐宏伟

5.面向Avalon总线的AES-128/192/256 IP核的设计与实现 [J], 丁俊;李娜;杨军因版权原因,仅展示原文概要,查看原文内容请购买。

AES加密解密实验报告

AES加密解密实验报告实验目的:了解和学习AES加密算法的原理和实现过程,掌握AES加密解密的方法。

实验原理:AES(Advanced Encryption Standard)高级加密标准,是一种对称加密算法,使用相同的密钥进行加密和解密。

AES加密算法使用数学运算和逻辑操作混合的方式,通过多轮迭代和替代、逆替代、置换等步骤,对数据进行加密和解密操作。

实验材料和方法:材料:计算机、Python编程环境。

方法:通过Python编程环境调用AES库函数,进行AES加密解密实验。

实验步骤:1. 导入AES库函数:在Python编程环境中,导入AES的库函数。

```pythonfrom Crypto.Cipher import AESfrom Crypto.Random import get_random_bytes```2. 生成随机密钥:使用get_random_bytes(函数生成一个长度为16字节的随机密钥。

```pythonkey = get_random_bytes(16)```3. 实例化AES加密对象:使用AES.new(函数,传入随机密钥和加密模式“AES.MODE_ECB”创建AES加密对象。

```pythoncipher = AES.new(key, AES.MODE_ECB)```4. 加密数据:使用encrypt(函数,传入要加密的数据进行加密操作。

```pythonmessage = "This is a secret message.".encodeciphertext = cipher.encrypt(message)```5. 解密数据:使用decrypt(函数,传入密文进行解密操作。

```pythonplaintext = cipher.decrypt(ciphertext)```6. 打印加密和解密结果:使用print(函数,打印加密前后和解密后的数据。

ICP-AES培训讲义课件

ICAP6000系列结构模块

1进样系统:毛细管,泵管,泵夹,蠕动泵,雾化器,雾化室,中心管, 炬管;

辅助部件:点火头,光纤探头其中雾化器为同心雾化器,雾化室为 旋流雾化室,根据样品类型不同,其选用的雾化器,雾化室,中心管, 炬管都有所区别; 2 发生器系统;固态发生器,工作线圈

3 光学检测系统:动画篇\光路.mpg

iCAP6000系列光谱仪操作规程

4、打开软件的”等离子体状态”的”仪器状态”对话框确认 检测器温度显示: 检测器camera:≥ 20℃后再继续驱气5-10分钟,关闭 氩气。 5、退出iTEVA软件,关闭电脑、显示器、打印机。 6、如果长时间不运行的情况下,依次关闭主机电源、稳压器。 7、做好仪器使用记录。

iCAP6000系列光谱仪分析参数设定的一般原则(1)

A、单独分析K、Na等易离解的元素请选择 RF 750-950W,AUX:1.0-1.5 L/min、Pump Rate:40-60r/min Nebulizer30-35psi(0.18-0.20Mpa) B、单独分析As Sb Se Cd等难离解的元素请选择 RF 1150-1350W,AUX:0.5 L/min、Pump Rate:40-60r/min, Nebulizer24-26psi(0.14-0.18Mpa) C、样品中既有难电离和易电离元素及中间元素可按一般水溶 液条件选择。

ICP光谱分析的应用-2

7)动植物及生化样品:包括植物,中药及动物组织,生物化学样品; 8)核工业产品:包括核燃料分析,核材料;

9)食品及饮料:包括食品,饮料.

所有样品的测定分析,主要在于样品的前处理和方法参数的优化 选择

建立ICP光谱分析方法的程序:

1取样和样品保存方法 保证样品不变质,不损失,不污染:比如酸化,低温保存等 2样品处理 采用何种前处理是保证准确测定的关键:须保证处理后样品彻底 性和稳定性

ip核的封装与调用实验报告

ip核的封装与调用实验报告

本次实验主要涉及到IP核的封装与调用,其中包括IP核的设计、封装、生成并添加到可综合库中,以及在Vivado中调用IP核,进行综合实

现的过程。

首先,在Vivado中创建工程,并搭建所需的电路结构。

在本次实验中,我们选择了一个简单的7位加法器电路作为样例,并在其中添加了一

个IP核。

该IP核是用Verilog设计的,实现了一个4位全加器。

设计完

成后,需要进行IP核的封装。

将IP核封装后,需要将其生成并添加到可综合库中。

在生成IP核文

件后,我们需要将其添加到项目的IP核库中,并选择需要综合的文件。

在该过程中,需要将设计文件和IP核文件连接起来,确保能够顺利综合

和实现。

在完成IP核的生成和添加后,我们需要在Vivado中进行调用IP核

并实现综合。

在Vivado中,我们需要首先在综合选项中选择使用IP核,

然后通过管脚和数据输入输出端口将IP核与设计文件连接起来。

在连接

完成后,我们需要对工程进行综合实现,并在综合报告中查看综合的情况。

实验结果表明,IP核的封装和调用是非常重要且必要的。

它可以大

大简化设计开发的过程,提高开发的效率。

同时,通过IP核的封装和调用,我们可以更加方便地进行设计的复用和可扩展性的提高。

总之,IP

核封装和调用技术是数字电路设计中不可或缺的一环。

AES算法在端到端通信加密模块中的实现及应用设计的开题报告

AES算法在端到端通信加密模块中的实现及应用设计的开题报告一、选题背景及研究意义随着互联网技术的普及以及信息安全越来越受到重视,加密算法一直是关注的热点。

其中AES(Advanced Encryption Standard)是最常见的一种加密算法,具有高强度、高效率、易于实现等特点。

在端到端通信中,加密算法可以保护数据的安全性,防止数据被拦截、篡改等。

因此,将AES算法应用于端到端通信加密模块中具有重要的研究意义和应用价值。

二、研究目的本研究旨在探究如何在端到端通信加密模块中实现AES算法并进一步设计实际应用方案。

具体包括以下目的:1. 分析和研究AES加密算法的原理和特点。

2. 探究如何将AES算法应用于端到端通信加密模块中,并设计相应的加密方案。

3. 在实际应用中,探究如何保证加密算法的安全性和高效性。

三、研究内容1. AES加密算法的原理和特点:介绍AES算法的基本原理和加密过程,探究AES算法的优点、弱点和适用场景。

2. 端到端通信加密模块的实现:研究端到端通信加密模块的设计原则和技术方案,包括数据交互流程、加密算法选择、密钥管理策略等。

3. 合理设计AES算法的应用场景:探究在实际应用中如何根据不同的场景选择合适的AES算法实现方式,应用于移动端、物联网设备、云服务器等方面。

4. 解决AES算法的安全性问题:分析AES算法的安全性问题,并提出一些解决方案以确保数据安全性。

四、研究方法本研究采用文献资料查阅法、实验研究法及案例分析法。

1. 文献资料查阅法:通过阅读各类学术论文、期刊、书籍等文献,系统性、全面性地了解AES算法的原理和特点,研究端到端通信加密模块的设计原则和技术方案,并参考真实应用案例。

2. 实验研究法:通过编写代码实现AES算法以及端到端通信加密模块的开发和测试,验证和比较不同算法实现方式的安全性和效率。

3. 案例分析法:参考实际应用的例子,分析在不同场景下如何合理选择AES算法的实现方式并确保数据安全的实际操作过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 2 AES 加密状态机状态转移图 2、建立控制模块的 Verilog 模型 module aescontrol(clk,rst,load,address,keyexp,staenc,stadec,keyexprdy,encdecrdy,keysel, rndkren,wrrndkrf,krfaddr,rconen,wrsben,wrsbaddr,keyadsel,mixsel,reginsel,wr regen,wrpckreg);

wire [3:0] wrkrfaddr,rdkrfaddre,rdkrfaddrd,encstate,decstate; wire [1:0] keyadsele,keyadseld; wire mixsele,reginsele,wrregene,encrdy,mixseld,reginseld,wrregend,decrdy;

keyadsel 2 位

krfaddr

wrsbaddr 7 位

1位

1位

1位

1位

1位

1位

1位

4位

staenLeabharlann =0S0S11S10

S9

输入 输入 输入 输出 输出 输出

输出 输出 输出

输出

输出

输出 输出 输出

输出

输出

输出

staenc=1

S1

S8

密钥扩展使能信号,1 有效。 开始加密使能信号,1 有效。 开始解密使能信号,1 有效。 密钥扩展完成标识信号,1 有效。 加/解密运算完成标识信号,1 有效。 轮密钥选择信号,keysel=0 选择密钥寄存 器中的种子密钥,否则,选择经过密钥扩 展变换的轮密钥。 轮密钥寄存器写使能信号,1 有效。 轮密钥寄存器堆写使能信号,1 有效。 轮常数寄存器写使能信号,1 有效。当有 效时将下一个轮常数写入轮常数寄存器。 向 S 盒写入配置数据的使能信号,1 有效。

wrregen wrpckreg

krfaddr<3:0> wrsbaddr<6:0>

keyexp

staenc

stadec

keyexprdy 1 位

encdecrdy 1 位

keysel

rndkren 1 位

wrrndkrf 1 位

rconen

wrsben

mixsel

reginsel 1 位 wrregen 1 位 wrpckreg 1 位

krfaddr<3:0> keyadsel<1:0>

mixsel reginsel

wrregen

encdecrdy

wrsben

wrsbaddr<6:0> keyadsel<1:0>

wrpckreg

keyexprdy encdecrdy

keysel

rndkren wrrndkrf rconen

wrsben mixsel reginsel

PC 机 1 台、Modelsim 仿真软件 1 套。 四、实验步骤 1、控制模块的电路结构设计

clk

keyexp rst

load

clk address<7:0>

rst

keyexp

staenc

stadec

clk

rst keyexpfsm wrkrfaddr<3:0>

staenc

clk rst stadec

encryfsm

decryfsm

AES 控制模块的外部信号如下表所示:

keysel

rndkren

wrrndkrf

rconen keyexprdy

keyadsele<1:0> mixsele reginsele wrregene

rdkrfaddre<3:0> encrdy encstate<3:0>

keyadseld<1:0> mixseld reginseld wrregend

S2

S7

S3

S4

S5

S6

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术关,系电通,力1根保过据护管生高线0产中不工资仅艺料可高试以中卷解资配决料置吊试技顶卷术层要是配求指置,机不对组规电在范气进高设行中备继资进电料行保试空护卷载高问与中题带资22负料,荷试而下卷且高总可中体保资配障料置各试时类卷,管调需路控要习试在题验最到;大位对限。设度在备内管进来路行确敷调保设整机过使组程其高1在中正资,常料要工试加况卷强下安看2与全22过,22度并22工且22作尽2下可护1都能关可地于以缩管正小路常故高工障中作高资;中料对资试于料卷继试连电卷接保破管护坏口进范处行围理整,高核或中对者资定对料值某试,些卷审异弯核常扁与高度校中固对资定图料盒纸试位,卷置编工.写况保复进护杂行层设自防备动腐与处跨装理接置,地高尤线中其弯资要曲料避半试免径卷错标调误高试高等方中,案资要,料求编5试技写、卷术重电保交要气护底设设装。备备4置管高调、动线中试电作敷资高气,设料中课并3技试资件且、术卷料拒管中试试调绝路包验卷试动敷含方技作设线案术,技槽以来术、及避管系免架统不等启必多动要项方高方案中式;资,对料为整试解套卷决启突高动然中过停语程机文中。电高因气中此课资,件料电中试力管卷高壁电中薄气资、设料接备试口进卷不行保严调护等试装问工置题作调,并试合且技理进术利行,用过要管关求线运电敷行力设高保技中护术资装。料置线试做缆卷到敷技准设术确原指灵则导活:。。在对对分于于线调差盒试动处过保,程护当中装不高置同中高电资中压料资回试料路卷试交技卷叉术调时问试,题技应,术采作是用为指金调发属试电隔人机板员一进,变行需压隔要器开在组处事在理前发;掌生同握内一图部线纸故槽资障内料时,、,强设需电备要回制进路造行须厂外同家部时出电切具源断高高习中中题资资电料料源试试,卷卷线试切缆验除敷报从设告而完与采毕相用,关高要技中进术资行资料检料试查,卷和并主检且要测了保处解护理现装。场置设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。

combinational logic

数据装载使能信号,用于控制输入明/密

文、密钥、S 盒配置数据等,1 有效。

寄存器或 RAM 地址,用于表示明文/密文/

密钥寄存器、S 盒 RAM 单元。

1

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术关,系电通,力1根保过据护管生高线产中0不工资仅艺料可高试以中卷解资配决料置吊试技顶卷术层要是配求指置,机不对组规电在范气进高设行中备继资进电料行保试空护卷载高问与中题带资2负料2,荷试而下卷且高总可中体保资配障料置各试时类卷,管调需路控要习试在题验最到;大位对限。设度在备内管进来路行确敷调保设整机过使组程其高1在中正资,常料要工试加况卷强下安看与全22过,22度并22工且22作尽22下可护都能1关可地于以缩管正小路常故高工障中作高资;中料对资试于料卷继试连电卷接保破管护坏口进范处行围理整,高核或中对者资定对料值某试,些卷审异弯核常扁与高度校中固对资定图料盒纸试位,卷置编工.写况保复进护杂行层设自防备动腐与处跨装理接置,地高尤线中其弯资要曲料避半试免径卷错标调误高试高等方中,案资要,料求编试技5写、卷术重电保交要气护底设设装。备备置管4高调、动线中试电作敷资高气,设料中课并技3试资件且、术卷料中拒管试试调绝路包验卷试动敷含方技作设线案术,技槽以来术、及避管系免架统不等启必多动要项方高方案中式;资,对料为整试解套卷决启突高动然中过停语程机文中。电高因气中此课资,件料电中试力管卷高壁电中薄气资、设料接备试口进卷不行保严调护等试装问工置题作调,并试合且技理进术利行,用过要管关求线运电敷行力设高保技中护术资装。料置线试做缆卷到敷技准设术确原指灵则导活:。。在对对分于于线调差盒试动处过保,程护当中装不高置同中高电资中压料资回试料路卷试交技卷叉术调时问试,题技应,术采作是用为指金调发属试电隔人机板员一进,变行需压隔要器开在组处事在理前发;掌生同握内一图部线纸故槽资障内料时,、,强设需电备要回制进路造行须厂外同家部时出电切具源断高高习中中题资资电料料源试试,卷卷线试切缆验除敷报从设告而完与采毕相用,关高要技中进术资行资料检料试查,卷和并主检且要测了保处解护理现装。场置设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。

rdkrfaddrd<3:0> decrdy decstate<3:0>

load address<7:0>

图 1 AES 控制模块电路结构图

表 1 AES 控制模块的外部信号说明

信号名称 信号宽度 传输方向 信号含义

clk

rst

load

address

1位

1位

1位

8位

输入

输入

输入

输入

时钟信号

复位信号,1 有效。

选择是否进行逆列混合变换,在进行第 19 轮解密变换时为 1,其余时间为 0。 结果寄存器输入数据选择信号。 结果寄存器写使能信号,1 有效。 明文/密文/密钥寄存器的写使能信号,1 有效。 密钥加操作输入数据选择信号,2’b00 选 择外部输入数据,2’b 01 选择列混合变 换的结果,2’b10 选择第 10 轮加密变换 所需的 S 盒输出,2’b11 选择第 10 轮解 密变换所需的 S 盒输出。 轮密钥寄存器堆地址,表示 11 个轮密钥 寄存器的地址。 S 盒配置数据的地址。

2

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术关,系电通,力1根保过据护管生高线产中0不工资仅艺料可高试以中卷解资配决料置吊试技顶卷术层要是配求指置,机不对组规电在范气进高设行中备继资进电料行保试空护卷载高问与中题带资2负料2,荷试而下卷且高总可中体保资配障料置各试时类卷,管调需路控要习试在题验最到;大位对限。设度在备内管进来路行确敷调保设整机过使组程其高1在中正资,常料要工试加况卷强下安看与全22过,22度并22工且22作尽22下可护都能1关可地于以缩管正小路常故高工障中作高资;中料对资试于料卷继试连电卷接保破管护坏口进范处行围理整,高核或中对者资定对料值某试,些卷审异弯核常扁与高度校中固对资定图料盒纸试位,卷置编工.写况保复进护杂行层设自防备动腐与处跨装理接置,地高尤线中其弯资要曲料避半试免径卷错标调误高试高等方中,案资要,料求编试技5写、卷术重电保交要气护底设设装。备备置管4高调、动线中试电作敷资高气,设料中课并技3试资件且、术卷料中拒管试试调绝路包验卷试动敷含方技作设线案术,技槽以来术、及避管系免架统不等启必多动要项方高方案中式;资,对料为整试解套卷决启突高动然中过停语程机文中。电高因气中此课资,件料电中试力管卷高壁电中薄气资、设料接备试口进卷不行保严调护等试装问工置题作调,并试合且技理进术利行,用过要管关求线运电敷行力设高保技中护术资装。料置线试做缆卷到敷技准设术确原指灵则导活:。。在对对分于于线调差盒试动处过保,程护当中装不高置同中高电资中压料资回试料路卷试交技卷叉术调时问试,题技应,术采作是用为指金调发属试电隔人机板员一进,变行需压隔要器开在组处事在理前发;掌生同握内一图部线纸故槽资障内料时,、,强设需电备要回制进路造行须厂外同家部时出电切具源断高高习中中题资资电料料源试试,卷卷线试切缆验除敷报从设告而完与采毕相用,关高要技中进术资行资料检料试查,卷和并主检且要测了保处解护理现装。场置设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。