第1-2讲MOS管特性和CMOS版图基础分析解析

mos管的功能作用讲解

mos管的功能作用讲解1. MOS管的基本概念在电子世界里,MOS管可是个大明星,嘿,别小看它!MOS管,全名金属氧化物半导体场效应晶体管,听起来是不是有点复杂?其实,它就是一个可以控制电流流动的小开关,像是你家里的灯开关一样,但它的作用可大得多哦。

无论是手机、电脑,还是家里的冰箱、洗衣机,几乎所有的电子设备里都离不开它。

这小家伙能帮助设备省电,调节功率,让我们的生活更加智能、方便。

2. MOS管的工作原理2.1 电子“开关”想象一下,MOS管就像是个电子世界里的开关,控制着电流的流动。

它通过电场来控制电流,简单来说,就是用电压来打开或关闭电流,就像你用遥控器控制电视机一样。

这种特性让它在电路中如鱼得水,能够实现各种复杂的功能。

你只需给它一个电压,它就能乖乖地让电流流动或者停止,简直是个小乖乖!2.2 省电高手说到省电,MOS管真是个高手。

由于它在工作时的导通电阻很低,所以即使是大电流,也能轻松应对,避免了能量的浪费。

比如,家里用的LED灯,靠的就是这种神奇的器件,让光线亮得更加节能。

它就像一个勤奋的“守门员”,只在有需要的时候才放电,让我们的钱包也跟着“省省省”!3. MOS管的应用场景3.1 家电中的英雄家电产品中,MOS管的身影随处可见,真的是忙得不可开交。

比如,冰箱的温控系统、洗衣机的马达控制,都是靠它来调节电流的。

想象一下,洗衣机里那一缸水咕噜咕噜地转,背后少不了MOS管的功劳,它在默默为我们分担着电流的“重任”。

就像一位无名英雄,平时不显山露水,一到关键时刻,就发挥出色,让生活变得顺畅。

3.2 电子设备的“护航员”除了家电,MOS管在各类电子设备中也扮演着重要角色。

从手机到电脑,几乎每个小零件都能找到它的身影。

比如,在手机的电源管理中,MOS管帮助调节电压,确保电池不会因为过载而损坏。

这就像是个细心的“保姆”,时刻照顾着设备的安全,保护我们的小宝贝。

4. 未来的无限可能4.1 新技术的引领者随着科技的飞速发展,MOS管的未来可谓是光明无限。

《CMOS集成电路基础》课件

智能传感器和可 穿戴设备的普及

随着智能传感器和可穿戴设 备的普及,CMOS集成电路 将在这些领域发挥重要作用 ,实现更高效、更低功耗的 数据采集和处理。

神经网络和类脑 计算的发展

CMOS集成电路将在神经网 络和类脑计算领域发挥重要 作用,推动人工智能技术的 进一步发展。

系统级芯片的广 泛应用

随着系统级芯片的广泛应用 ,CMOS集成电路将与不同 芯片和模块进行集成,实现 更高效、更低功耗的系

晶圆制备

将高纯度硅材料加工成晶圆, 作为集成电路的基底。

薄膜沉积

在晶圆表面沉积所需厚度的薄 膜,形成各种有源和无源器件

。

光刻与刻蚀

通过光刻技术将设计好的电路 版图转移到晶圆表面,然后进

行刻蚀,形成电路图形。

掺杂与退火

通过掺杂工艺在晶圆中引入不 同元素,形成PN结和导电通

道,并进行退火处理。

03

每个逻辑门电路由NMOS和PMOS晶体管组成,形成反相器或与门、或门等基 本逻辑门。

工作原理

01

CMOS集成电路的工作原理基于 NMOS和PMOS晶体管的开关特 性。当输入信号发生变化时, NMOS和PMOS晶体管会交替导

02 通和截止,从而实现逻辑功能。

CMOS电路的电压摆幅较小,因 此功耗较低。此外,CMOS电路 还具有噪声容限高、抗干扰能力 强等优点。

我们应该如何学习和掌握CMOS集成电路技术

理论与实践结合

在学习过程中,应注重理论与实践相结合 ,通过实验和项目实践加深对理论知识的

理解。

持续学习与更新知识

随着技术的不断进步,应保持持续学习的 态度,关注新技术、新工艺的发展,不断 更新自己的知识储备。

培养问题解决能力

MOS管及简单CMOS逻辑门电路原理图

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用C MOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMO S2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过V DD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMO S器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMO S管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

MOS管MOS管结构原理图解

MOS管MOS管结构原理图解mos管是金属(metal)—氧化物(oxide)—半导体(semiconductor)场效应晶体管,或者称是金属—绝缘体(insulator)—半导体。

MOS管的source和drain是可以对调的,他们都是在P型backgate中形成的N型区。

在多数情况下,这个两个区是一样的,即使两端对调也不会影响器件的性能。

这样的器件被认为是对称的。

双极型晶体管把输入端电流的微小变化放大后,在输出端输出一个大的电流变化。

双极型晶体管的增益就定义为输出输入电流之比(beta)。

另一种晶体管,叫做场效应管(FET),把输入电压的变化转化为输出电流的变化。

FET的增益等于它的transconductance,定义为输出电流的变化和输入电压变化之比。

市面上常有的一般为N 沟道和P沟道,详情参考右侧图片(N沟道耗尽型MOS管)。

而P沟道常见的为低压mos管。

场效应管通过投影一个电场在一个绝缘层上来影响流过晶体管的电流。

事实上没有电流流过这个绝缘体,所以FET管的GATE电流非常小。

最普通的FET用一薄层二氧化硅来作为GATE极下的绝缘体。

这种晶体管称为金属氧化物半导体(MOS)晶体管,或,金属氧化物半导体场效应管(MOSFET)。

因为MOS管更小更省电,所以他们已经在很多应用场合取代了双极型晶体管。

mos管优势1.可应用于放大。

由于场效应管放大器的输入阻抗很高,因此耦合电容可以容量较小,不必使用电解电容器。

2.很高的输入阻抗非常适合作阻抗变换。

常用于多级放大器的输入级作阻抗变换。

3.可以用作可变电阻。

4.可以方便地用作恒流源。

5.可以用作电子开关。

6.在电路设计上的灵活性大。

栅偏压可正可负可零,三极管只能在正向偏置下工作,电子管只能在负偏压下工作。

另外输入阻抗高,可以减轻信号源负载,易于跟前级匹配。

MOS管结构原理图解1、结构和符号(以N沟道增强型为例)在一块浓度较低的P型硅上扩散两个浓度较高的N型区作为漏极和源极,半导体表面覆盖二氧化硅绝缘层并引出一个电极作为栅极。

MOS管介绍解读

MOS管介绍解读MOS管是一种双极性场效应晶体管(FET),也称为MOSFET(金属-氧化物-半导体场效应晶体管)。

它是一种由金属层、氧化物层和半导体层构成的晶体管。

MOS管被广泛用于数字电路、模拟电路和功率放大器等应用中,因为它具有很高的开关速度、较低的功耗和较高的承受电压能力。

MOS管的工作原理是通过控制栅极电压来控制电流的流动。

当栅极电压为零时,MOS管处于关闭状态,没有电流流过。

当栅极电压增加到临界值以上时,MOS管进入开启状态,允许电流流过。

MOS管的导电能力主要取决于栅极电压与漏极电压之间的差异。

当栅极电压较高时,MOS管的导电性较好,电流流过的能力较大。

相反,当栅极电压较低时,MOS管的导电性较差,电流流过的能力较小。

MOS管有两种类型,分别是N沟道MOS管和P沟道MOS管。

它们的区别在于所使用的材料类型和电流流动方向。

N沟道MOS管使用N型半导体材料构成,通过负栅极电压来控制正电流的流动。

P沟道MOS管使用P型半导体材料构成,通过正栅极电压来控制负电流的流动。

这两种类型的MOS管可以用于不同的应用中,具体选择取决于电路设计和所需的电流极性。

与其他晶体管相比,MOS管具有许多优势。

首先,MOS管的开关速度较快,可以实现高频率的信号放大和处理。

其次,MOS管的功耗较低,因为它只需要很小的电压来控制电流流动。

此外,MOS管可以承受较高的电压,使其适用于高功率应用。

另外,MOS管具有良好的线性特性和温度稳定性,可以在不同的工作条件下提供稳定的性能。

MOS管还有一些应用注意事项。

首先,由于MOS管是压阻性器件,它的输入特性受到栅极电容的影响。

因此,在高频应用中,需要注意匹配负载和输入电容,以避免信号衰减和失真。

其次,MOS管还有最大额定电压和最大额定电流。

在设计电路时,需要确保不超过这些限制,以防止损坏MOS管。

最后,MOS管的工作温度范围也需要考虑,因为过高或过低的温度可能会影响性能和寿命。

(完整word版)MOS管原理、MOS管的小信号模型及其参数

MOS管原理、MOS管的小信号模型及其参数MOS管是只有一种载流子参与导电,用输入电压控制输出电流的半导体器件.有N沟道器件和P沟道器件。

有结型场效应三极管JFET(Junction Field Effect Transister)和绝缘栅型场效应三极管IGFET( Insulated Gate Field Effect Transister) 之分。

IGFET也称金属—氧化物-半导体三极管MOSFET(Metal Oxide SemIConductor FET)。

MOS场效应管有增强型(Enhancement MOS 或EMOS)和耗尽型(Depletion)MOS或DMOS)两大类,每一类有N 沟道和P沟道两种导电类型。

MOS管有三个电极:D(Drain) 称为漏极,相当双极型三极管的集电极;G(Gate)称为栅极,相当于双极型三极管的基极;S(Source)称为源极,相当于双极型三极管的发射极.增强型MOS(EMOS)场效应管道增强型MOSFET基本上是一种左右对称的拓扑结构,它是在P型半导体上生成一层SiO2 薄膜绝缘层,然后用光刻工艺扩散两个高掺杂的N型区,从N型区引出电极,一个是漏极D,一个是源极S。

在源极和漏极之间的绝缘层上镀一层金属铝作为栅极G。

P型半导体称为衬底(substrat),用符号B表示。

一、工作原理1.沟道形成原理当Vgs=0 V时,漏源之间相当两个背靠背的二极管,在D、S之间加上电压,不会在D、S间形成电流。

当栅极加有电压时,若0<Vgs<Vgs(th)时(VGS(th)称为开启电压),通过栅极和衬底间的电容作用,将靠近栅极下方的P型半导体中的空穴向下方排斥,出现了一薄层负离子的耗尽层。

耗尽层中的少子将向表层运动,但数量有限,不足以形成沟道,所以仍然不足以形成漏极电流ID。

进一步增加Vgs,当Vgs>Vgs(th)时,由于此时的栅极电压已经比较强,在靠近栅极下方的P型半导体表层中聚集较多的电子,可以形成沟道,将漏极和源极沟通。

cmos门电路的特点_CMOS门电路的工作原理及特性 - 电子技术

cmos门电路的特点_CMOS门电路的工作原理及特性 - 电子技术MOS逻辑门电路是继TTL之后发展起来的另一种应用广泛的数字集成电路。

由于它功耗低、抗干扰能力强、工艺简单,几乎所有的大规模、超大规模数字集成器件都采用MOS工艺。

就其发展趋势看,MOS 电路特别是CMOS电路有可能超越TTL成为占统治地位逻辑器件。

CMOS逻辑门电路是由N沟道增强型MOS管和P沟道增强型MOS管互补而成,通常称为互补型MOS逻辑电路,简称CMOS逻辑电路。

下面以CMOS非门为例介绍CMOS门电路的工作原理及特性。

1、CMOS非门图1 CMOS非门基本电路(1)电路结构及工作原理CMOS非门的基本电路结构如图1所示,其中TP是P沟道增强型MOS 管,TN是N沟道增强型MOS管。

假如TP和TN的开启电压分别为UTP和UTN,则要求VDDUTP+UTN。

当输入为低电平,即ui=0时,TN截止,TP导通,故uo≈VDD,输出高电平。

当输入为高电平,即ui=VDD时,TP截止,TN导通,故uo≈0,输出低电平。

所以该电路实现了非逻辑。

通过以上分析可以看出,在CMOS非门电路中,无论电路处于何种状态,TP、TN中总有一个截止,所以它的静态功耗极低,有微功耗电路之称。

(2)电压传输特性在图1所示的CMOS非门电路中,设VDDUTP+UTN。

,且UTP=UTN,TP 和TN具有同样的导通内阻RON和截止内阻ROFF,则输出电压随输入电压变化的曲线,即电压传输特性如图2所示。

图2 CMOS非门的电压传输特性从图2所示的曲线上可以看出,CMOS非门的电压传输特性不仅有阀值电压UT=1/2VDD的特点,而且曲线转折区的曲率很大,因此更接近于理想的开关特性,从而使CMOS非门电路获得了更大的输入端噪声容限。

2、CMOS与非门电路CMOS与非门电路如图3所示。

驱动管TN1和TN2为N沟道增强型MOS管,两者串联,负载管TP1和TP2为P沟道增强型MOS管,两者并联,负载管整体与驱动管相串联。

MOS管介绍概要PPT课件

预夹断点开始, ID基本不随VDS

极电流。

增加而变化。

.

18

增强型MOSFET的工作原理

.

19

MOSFET的特性曲线

1.漏极输出特性曲线

V V V

DS

GS T

.

20

2.转移特性曲线— VGS对ID的控制特性

ID=f(VGS)VDS=常数 转移特性曲线的斜 率 gm 的大小反映了栅 源电压对漏极电流的控 制作用。 其量纲为 mA/V,称gm为跨导。

VGD=VGS-VDS,比源端耗尽 层所受的反偏电压VGS 大,(如:VGS=-2V, VDS =3V, VP=-9V,则漏端耗尽层受反 偏当V电DS压继续为增-5加V时,,源预端夹耗断尽点向层

受源极反方偏向电伸压长为为预-2夹V断),使区靠。由近于

漏预夹端断的区耗电尽阻层很比大,源使端主厚要,VD沟S 道降落比在源该端区窄,,由此故产VD生S对的强沟电道场

用途:做无触点的、 接通状态的电子开关。

条件:整个沟道都夹断

V V

GS

P

击穿区

当漏源电压增大到

V V 时,漏端PN结

DS

(BR)DS

发生雪崩击穿,使iD 剧增的区域。其值一般为

(20— 50)V之间。由于VGD=VGS-VDS, 故vGS越负,

对应的VP就越小。管子不能在. 击穿区工作。

9

i ②转移特性曲线 Df(VGS)VDSC

输入电压VGS对输出漏极电流ID的控制

iD / v G Q S d D /d iG Q v S g m m s

.

10

结型场效应管的特性小结

N 沟 道 耗

结尽 型型

场

效P 应沟 管道

mos管的解析

MOS管的解析第一部分:介绍MOS管金属-氧化物-半导体场效应晶体管,通常称为MOS管,是一种关键的半导体器件,广泛应用于电子领域。

它在现代电子设备和集成电路中扮演着至关重要的角色。

为了更深入理解MOS管,我们将逐步探讨其结构、工作原理和应用领域。

1.1 结构MOS管通常由金属、氧化物和半导体材料构成。

其基本结构包括两个金属电极,分别被称为源极和漏极,它们与半导体材料之间通过一个绝缘层,即氧化物层,相隔开。

这个结构创造了一个场效应晶体管,通过改变栅极电压,可以控制源极和漏极之间的电流。

1.2 工作原理MOS管的工作原理基于栅极电压的控制。

当栅极施加正电压时,在氧化物层下形成一个电场,将半导体材料中的载流子排斥或吸引到接近漏极或源极的区域。

这种电场效应导致通道的形成或截断,从而控制了电流的流动。

MOS管有两种主要类型:N沟道MOS(NMOS)和P沟道MOS(PMOS),它们分别使用不同的载流子类型。

第二部分:MOS管的应用领域MOS管作为一种强大的电子器件,被广泛用于各种应用领域。

以下是一些主要领域的应用示例:2.1 集成电路MOS管在集成电路(ICs)中扮演着关键的角色。

ICs是现代电子设备的基础,包括计算机、智能手机、芯片卡等。

MOS管的微小尺寸和低功耗特性使其成为高度集成电路的理想选择。

2.2 数模转换MOS管用于模拟信号的数字到模拟转换(ADC)和模拟到数字转换(DAC)。

这些应用包括音频处理、通信系统和传感器技术。

2.3 逻辑电路MOS管用于数字逻辑电路,如门电路、触发器和寄存器。

它们用于执行各种计算和控制任务,是计算机处理和存储信息的核心。

2.4 放大器MOS管也被用作放大器,用于放大电信号,例如音频和射频信号。

这些放大器在音响系统、通信设备和射频通信中发挥着重要作用。

2.5 电源管理MOS管在电源管理电路中用于调整电压和电流,以满足不同设备的电能需求。

这对于延长电池寿命和提高设备效率至关重要。

MOS管电路工作原理及详解

MOS管电路工作原理及详解在电子电路的世界里,MOS 管(MetalOxideSemiconductor FieldEffect Transistor,金属氧化物半导体场效应晶体管)是一种极其重要的元件。

它的性能卓越,应用广泛,从简单的电子设备到复杂的集成电路,都能看到MOS 管的身影。

为了更好地理解和运用MOS 管,我们需要深入探究其电路工作原理。

MOS 管主要有两种类型:增强型和耗尽型。

增强型 MOS 管又分为N 沟道增强型和 P 沟道增强型;耗尽型 MOS 管同样分为 N 沟道耗尽型和 P 沟道耗尽型。

在实际应用中,增强型 MOS 管更为常见。

先来说说 N 沟道增强型 MOS 管的结构。

它由一块 P 型半导体作为衬底,在上面扩散两个高浓度的 N 型区,分别作为源极(S)和漏极(D)。

在源极和漏极之间的衬底表面覆盖一层很薄的二氧化硅绝缘层,然后在绝缘层上沉积一层金属铝,形成栅极(G)。

当栅极电压为零时,源极和漏极之间没有导电沟道,MOS 管处于截止状态。

当在栅极和源极之间加上正向电压(VGS),并且 VGS 超过一定的阈值电压(VT)时,在靠近栅极下方的 P 型半导体表面会形成一个N 型导电沟道。

此时,若在漏极和源极之间加上电压(VDS),就会有电流(IDS)从漏极流向源极,MOS 管处于导通状态。

而且,IDS的大小与 VGS 和 VDS 都有关系。

在 VGS 一定的情况下,当 VDS 较小时,IDS 随 VDS 线性增加,MOS 管工作在电阻区。

随着 VDS 的增大,靠近漏极一端的导电沟道会变窄,这种现象被称为沟道夹断。

当 VDS 增加到使得沟道在漏极一端刚好夹断时,称为预夹断状态。

继续增大 VDS,夹断区会延长,而IDS 基本保持不变,MOS 管工作在恒流区。

P 沟道增强型 MOS 管的工作原理与 N 沟道增强型 MOS 管类似,只是所加电压的极性相反。

再谈谈 MOS 管在电路中的应用。

集成电路版图基础-CMOS版图篇01

沟道长度 L 电流方向

设计中,常以宽度和长度值的比例式即宽 长比(W/L)表示器件尺寸。 例:假设一MOS管,尺寸参数为20/5。则 在版图上应如何标注其尺寸。

20/5

3、图形绘制

英特尔65纳米双核处理器的扫描电镜(SEM)截面图

常用图层 版图图层名称 Nwell Active Pselect Nselect Poly cc Metal1 Metal2 Via 含义 N阱 有源扩散区 P型注入掩膜 N型注入掩膜 多晶硅 引线孔 第一层金属 第二层金属 通孔

“混合棒状图”法:

矩形代表有源区(宽度不限); 实线代表金属; 虚线代表多晶硅;

“×”代表引线孔。其它层次不画,

通常靠近电源vdd的是P管,靠近地线gnd 的是N管。

反相器棒状图

电路图-棒状图-版图

a

b

练习

三输入与非门、或非门棒状图

注意:

不同软件对图层名称定义不同; 严格区分图层作用。

版图图层名称 cc(或cont) Via

含义 引线孔(连接金属与多晶硅 或有源区) 通孔(连接第一和第二层金 属)

MOS器件版图图层 ——PMOS

N阱——NWELL P型注入掩模——PSELECT 有源扩散区——ACTIVE 多晶硅栅——POLY 引线孔——CC 金属一——METAL1 通孔一——VIA 金属二——METAL2

MOS器件版图图层 ——NMOS

N型注入掩模——NSELECT 有源扩散区——ACTIVE 多晶硅栅——POLY 引线孔——CC 金属一——METAL1 通孔一——VIA 金属二——METAL2

MOS管及简单CMOS逻辑门电路原理图

MOS 管及简单CMOS 逻辑门电路原理图现代单片机主要是采用CMO 工艺制成的。

1、MOS 管 MOS 管又分为两种类型:N 型和P 型。

如下图所示:V DD45 Ic6=VssP 型MOS 管以N 型管为例,2端为控制端,称为“栅极”;3端通常接地,称为 “源极”;源极电压记作Vss , 1端接正电压,称为“漏极”,漏极电压记作VDD 要使1端与3端导通,栅极2上要加高电平。

对P 型管,栅极、源极、漏极分别为 5端、4端、6端。

要使4 端与6端导通,栅极5要加低电平。

在CMO 工艺制成的逻辑器件或单片机中,N 型管与P 型管往往是 成对出现的。

同时出现的这两个 CMO 管,任何时候,只要一只导通,另一只则 不导通(即“截止”或“关断”),所以称为“互补型—CMO 管”。

.2、CMO 逻辑电平高速CMO 电路的电源电压 VDD S 常为+5V; Vss 接地,是0V 。

高电平视为逻辑“ 1”,电平值的范围为:VDD 勺65%-VDD 或者VDD-1.5V 〜VDD低电平视作逻辑“ 0”,要求不超过 VDD 的35%或 0〜1.5V 。

+1.5 V 〜+3.5V 应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有 助于降低功耗。

VDD 为3.3V 的CMO 器件已大量使用。

在便携式应用中, VDC 为2.7V ,甚至1.8V 的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V , 但低于VDD 的 35%勺电平视为逻辑“ 0”,高于VDD 勺65%勺电平视为逻辑“ 1” 的规律仍然是适用的。

VDD VssV DD_ VssI 订]原理图非门(反向器)是最简单的门电路,由一对 CMOS 管组成。

其工作原理如 下: A 端为高电平时,P 型管截止,N 型管导通,输出端C 的电平与Vss 保持一 致,输出低电平;A 端为低电平时,P 型管导通,N 型管截止,输出端C 的电平 与V DD —致,输出高电平。

模拟集成电路课件 第2章CMOS技术

栅电压相对背栅为负时,多子被向上抽取积累在栅氧化层下。 (沟道没形成积累型)

开始正偏时,多数载流子被排斥,形成耗尽区,随着偏压增 大,耗尽区加宽,电容减小。(耗尽区电阻大)

一旦偏压等于阈值电压,沟道弱反型(沟道电阻大)

适中(沟道电阻逐渐减小)

正偏压进一步加大,沟道强反型,Cj和Cox并联

这种电容器在低电压时,电容值很小。

2. MOS器件的工作原理

nMOS管沟道的形成 MOS晶体管的分类 MOS管的阈值电压 MOS管的版图和结构

nMOS管沟道的形成

反型层和n型硅都依靠自由电子

导电,但电子产生的方法不同。

n型硅自由电子是在制造过程中由 扩散掺杂工艺产生 反型层自由电子则由栅极电压感应 产生

故MOS管又称场效应晶体管

0 vDS 2 iD (vGS VT )vDS 2 (vGS VT ) 2 2

Vi Vss V o Vdd

N+

N+

P+

P+

P+

T2

P-Well

RW 压降

p-

T1

压降

RS

Vss Vss

n-si

Vdd

③采用保护环 保护环可以有效地降低横向电阻和横向电流密 度。同时,由于加大了 P-N-P 管的基区宽度使 βpnp下降。

Vi Vss Vdd

Vo

P+

N+

N+

P+

N+

P+

P+

N+

T2

SOI/CMOS电路

下图示出理想的SOI/CMOS结构。业已应用兰宝石衬底外延硅结构 (SOS-Silicon on Sapphire结构)。 SOI结构是针对亚微米CMOS器件提出的,以取代不适应要求的常规 结构,SOI结构在高压集成电路和三维集成电路中也有广泛应用。

第1-2讲MOS管特性和CMOS版图基础..

多晶硅

poly

metal1

via

n+

p+

n+ substrate substrate (衬底)

Manufacturing

8

EE141 Integrated © Digital

Байду номын сангаас

Circuits2nd

CMOS有三类工艺:

Well---阱 P-Well CMOS Process (也基本不用) N-Well CMOS Process Dual-Well CMOS Process

EE141 Integrated © Digital

Circuits2nd

Manufacturing

2

Die Cost

Single die

Wafer

Going up to 12” (30cm)

EE141 Integrated Circuits 2nd © Digital

From

Manufacturing

12

3、几种工艺方法 1) oxidation (氧化)

氧气

Si-substrate or P-type or N-type

SiO2

Si-substrate or P-type or N-type SiO2 是绝缘体。 它的作用是什么?

EE141 Integrated © Digital

Circuits2nd

Manufacturing

4

多项目晶圆服务

多项目晶圆(多目标芯片) Multi Project Wafer --- MPW

多个使用相同工艺的设计,放在同一晶圆片上流片。 每个设计可以得到数十片芯片样品。 制造费用按照芯片面积分摊,成本仅为单独进行制造的5%10%。

最经典MOS管电路工作原理及详解没有之一

最经典MOS管电路工作原理及详解没有之一最经典MOS管电路工作原理及详解没有之一一、引言电路的设计和分析是电子工程师的基本能力之一。

在众多的电子元件中,MOS管是一种重要的器件,在各种电路中广泛应用。

本文将详细介绍MOS管的工作原理和使用方法。

二、MOS管的基本结构和工作原理1\MOS管的基本结构MOS管是一种金属\氧化物\半导体场效应晶体管,由源极(S)、栅极(G)、漏极(D)和栅极氧化层组成。

其中,源极和漏极是导电层,栅极氧化层作为绝缘层起到隔离作用。

2\MOS管的工作原理MOS管通过在栅极上施加正向或负向的电压,来控制漏极和源极之间的电流流动。

当栅极电压为零时,MOS管处于关闭状态,几乎没有漏极电流。

当正向偏置栅极电压时,MOS管进入导通状态,漏极电流增加。

当负向偏置栅极电压时,MOS管也处于关闭状态。

三、MOS管的工作区域和特性曲线1\MOS管的工作区域MOS管可以分为三个工作区域:截止区、放大区和饱和区。

截止区是栅极电压低于阈值电压时,MOS管处于关闭状态。

放大区是栅极电压高于阈值电压时,MOS管处于放大状态。

饱和区是栅极电压继续增加,导致漏极电流不再线性变化的状态。

2\MOS管的特性曲线MOS管的特性曲线是漏极电流与栅极电压之间的关系图。

曲线上显示了MOS管在不同工作区域的电流变化情况。

随着栅极电压的增加,曲线从截止区逐渐过渡到饱和区。

四、MOS管的应用1\MOS管在放大电路中的应用MOS管可以作为放大器的核心部件,通过调节栅极电压来控制放大器的增益和工作状态。

常见的应用包括音频放大器、功率放大器等。

2\MOS管在开关电路中的应用MOS管也可以用作开关,通过控制栅极电压来控制电路的通断状态。

常见的应用包括模拟开关、数字开关等。

五、附件本文档涉及的附件包括原理图、示意图和数据表等,可供读者参考和。

六、法律名词及注释1\MOS管:金属\氧化物\半导体场效应晶体管的简称,是一种重要的电子元件。

MOS管的工作原理及特性

金氧半场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,

板级电路应用上,都十分广泛。

一、MOS管的工作原理

以增强型MOS管为例,我们先简单来看下MOS管的工作原理。

由上图结构我们可以看到MOS管类似三极管,也是背靠背的两个PN结!三极管的原理是在偏置的情况下注入电流到很薄的基区通过电子-空穴复合来控制CE 之间的导通,MOS管则利用电场来在栅极形成载流子沟道来沟通DS之间。

如上图,在开启电压不足时,N区和衬底P之间因为载流子的自然复合会形成一个中性的耗尽区。

给栅极提供正向电压后,P区的少子(电子)会在电场的作用下聚集到栅极氧化硅下,最后会形成一个以电子为多子的区域,叫反型层,称为反型因为是在P型衬底区形成了一个N型沟道区。

这样DS之间就导通了。

二、MOS管的特性

1、由于MOSFET是电压驱动器件(G极加电压控制电流),因此无直流电流流入栅极。

2、要开通MOSFET,必须对栅极施加高于额定栅极阈值电压Vth的电压。

3、处于稳态开启或关断状态时,MOSFET栅极驱动基本无功耗(但是请注意交叉点附近,就是电压下降与电流上升导致的功耗)。

4、通过驱动器输出看到的MOSFET栅源电容根据其内部状态而有所不同。

5、MOSFET通常被用作频率范围从几kHz到几百kHz的开关器件。

这点尤其需要注意。

三、结语

希望本文对大家能够有所帮助。

CMOS门电路工作原理介绍

四、其他类型的CMOS门电路

1.其他逻辑功能的CMOS门电路 在CMOS门电路的系列产品中, 除反相器外常用的还有: 与非门、或非门、与门、 或门、与或非门、异或门等几种。

上页 下页 返15回

(1)CMOS与非门电路

VDD 当A,B两个输入端全为“1”时,

T3

T4

T1和T2都导通,T3和T4都截止,

(2)CMOS“或非”门电

路

VDD

B

当A,B两个输入端全为“1”

T4

或 其中一个为“1”时,

A

输出端为“0”。

T3

只有当输入端全为“0”时,

Y 输出端才为“1”。

T1

T2

CMOS或非门

Y (A B)

存在和与非门类似的问题。

上页 下页 返17回

2.带缓冲级的CMOS门电路

电路构成: 在门电路的每个输入端、输出端各增设一级反相器, 加进的这些反相器具有标准参数,所以称为缓冲器。 优点: 这些带缓冲级的门电路,其输出电阻和输出的高、 低电平以及电压传输特性将不受输入端状态的影响, 电压传输特性的转折区也变得更陡。

Y 输出端为“0”。

T2

当输入端有一个或全为“0”时,

A

T1或T2(或都)截止,T3或T4 (或

都)导通 ,

B

T1

输出端Y为“1” 。

CMOS与非门

Y (AB)

缺点:1. 输入端的工作状态不同时影响电压传输特性。

2. 输出的高、低电平受输入端数目的影响。

3. 它的输出电阻受输入状态的影响。 上页 下页 返16回

vI

vO 当vI = VIH= VDD 时, T2导通,T1截止,输出为低

(完整word版)MOS管概述

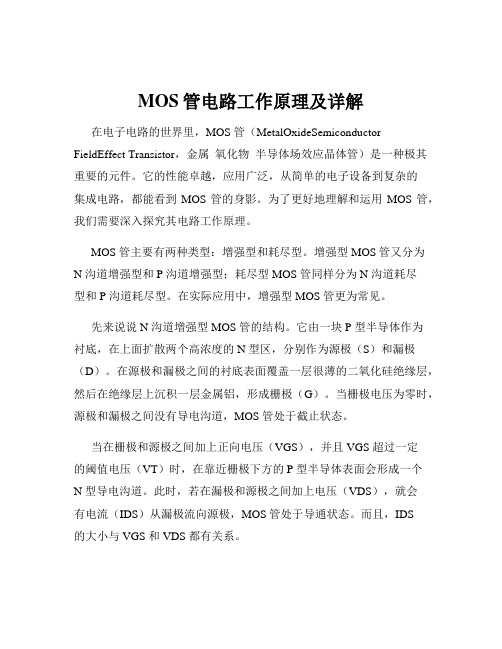

基本电子电路系列——MOS管MOS管学名是场效应管,是金属-氧化物-半导体型场效应管,英文:MOSFET(Metal Oxide Semiconductor Field Effect Transistor),属于绝缘栅型。

本文就结构构造、特点、实用电路等几个方面用工程师的话简单描述。

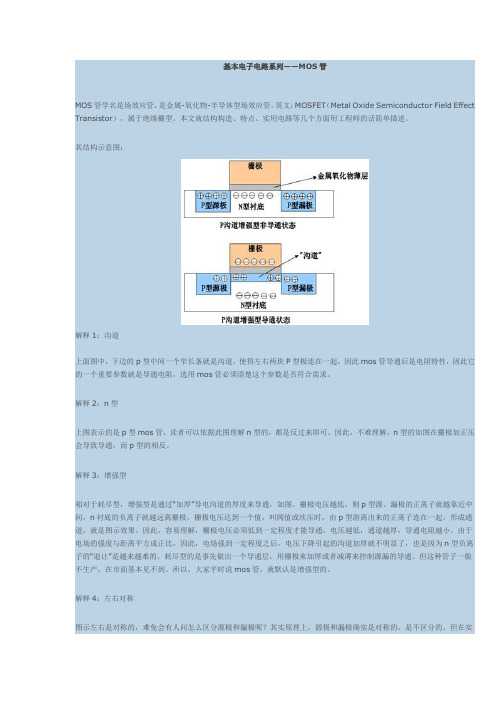

其结构示意图:解释1:沟道上面图中,下边的p型中间一个窄长条就是沟道,使得左右两块P型极连在一起,因此mos管导通后是电阻特性,因此它的一个重要参数就是导通电阻,选用mos管必须清楚这个参数是否符合需求。

解释2:n型上图表示的是p型mos管,读者可以依据此图理解n型的,都是反过来即可。

因此,不难理解,n型的如图在栅极加正压会导致导通,而p型的相反。

解释3:增强型相对于耗尽型,增强型是通过“加厚”导电沟道的厚度来导通,如图。

栅极电压越低,则p型源、漏极的正离子就越靠近中间,n衬底的负离子就越远离栅极,栅极电压达到一个值,叫阀值或坎压时,由p型游离出来的正离子连在一起,形成通道,就是图示效果。

因此,容易理解,栅极电压必须低到一定程度才能导通,电压越低,通道越厚,导通电阻越小。

由于电场的强度与距离平方成正比,因此,电场强到一定程度之后,电压下降引起的沟道加厚就不明显了,也是因为n型负离子的“退让”是越来越难的。

耗尽型的是事先做出一个导通层,用栅极来加厚或者减薄来控制源漏的导通。

但这种管子一般不生产,在市面基本见不到。

所以,大家平时说mos管,就默认是增强型的。

解释4:左右对称图示左右是对称的,难免会有人问怎么区分源极和漏极呢?其实原理上,源极和漏极确实是对称的,是不区分的。

但在实际应用中,厂家一般在源极和漏极之间连接一个二极管,起保护作用,正是这个二极管决定了源极和漏极,这样,封装也就固定了,便于实用。

我的老师年轻时用过不带二极管的mos管。

非常容易被静电击穿,平时要放在铁质罐子里,它的源极和漏极就是随便接。

解释5:金属氧化物膜图中有指示,这个膜是绝缘的,用来电气隔离,使得栅极只能形成电场,不能通过直流电,因此是用电压控制的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Introduction

29

EE141 Integrated © Digital

Circuits2nd

Manufacturing

3

1、Fabrication services

芯片制造代工厂

(Foundry)

1) TSMC 台积电 (台湾) 可获工艺:0.5um, 0.35um, 0.25um, 0.18um, 0.13um, 0.09um 0.065um, 0.045um 2) CSM 或称 Chartered 新加坡特许 (新加坡) 可获工艺:0.35um, 0.25um, 0.18um, 0.13um, 0.09um, 0.065um, 0.045um 3) SMIC 中芯国际 (上海) 可获工艺:0.35um, 0.25um, 0.18um, 0.13um, 0.09um 4)HJTC或称 HJ 和舰科技 (苏州) 可获工艺:0.35um, 0.25um, 0.18um 5)CSMC 华润上华 (无锡) 可获工艺:3.0至0.5微米 6)GSMC 宏力 (上海) 可获工艺:0.25um, 0.18um, 0.15um 7)HHNEC 华虹 (上海) 可获工艺:0.35um, 0.25um, 0.18um 8)SinoMOS 中纬 (宁波) 可获工艺:0.8um/1um

第一、二讲 MOS管特性与CMOS版图

一、CMOS工艺简介; 二、MOS管特性; 三、Layout设计; 四、估算寄生参数; 五、SPICE中 MOS器件参数设置

参考书: [1] Jan M. RabaeyAnantha Chandrakasan Borivoje Nikolic, Digital Integrated Circuits– A Design Perspective [2] 中译本:数字集成电路:电路、系统与设计(第二版)周润 德译,电子工业出版社出版

EE141 Integrated © Digital

Circuits2nd

Manufacturing

6

2、 Overview

MOS 管结构图: 3D Perspective

S

G

D

S G

D

G

S

EE141 Integrated © Digital

D

Circuits2nd

Manufacturing

7

Cross section insulator.

EE141 Integrated © Digital

Circuits2nd

Manufacturing

2

Die Cost

Single die

Wafer

Going up to 12” (30cm)

EE141 Integrated Circuits 2nd © Digital

From

poly

p-well n-well

SiO2 p+n+p-epi Nhomakorabea+

EE141 Integrated © Digital

Circuits2nd

Manufacturing

11

VDD M2

VDD

M4 Vin Vout Vout2

M1

M3

EE141 Integrated © Digital

Circuits2nd

SiO2 metal3 metal2 metal1 transistor

多晶硅

poly

metal1

via

n+

p+

n+ substrate substrate (衬底)

Manufacturing

8

EE141 Integrated © Digital

Circuits2nd

CMOS有三类工艺:

Well---阱 P-Well CMOS Process (也基本不用) N-Well CMOS Process Dual-Well CMOS Process

EE141 Integrated © Digital

Circuits2nd

Manufacturing

4

多项目晶圆服务

多项目晶圆(多目标芯片) Multi Project Wafer --- MPW

多个使用相同工艺的设计,放在同一晶圆片上流片。 每个设计可以得到数十片芯片样品。 制造费用按照芯片面积分摊,成本仅为单独进行制造的5%10%。

EE141 Integrated © Digital

Circuits2nd

Manufacturing

1

一、 CMOS Manufacturing Process

Technology (Process) 三类工艺:

双极型 bipolar (三极管,二极管,电阻 )

NMOS

CMOS (NMOS,PMOS):目前主流工艺

EE141 Integrated © Digital

Circuits2nd

Manufacturing

5

Educational

services (MPW服务机构)

美国:MOSIS (MOS Implementation Support Project) 台湾:CIC (Chip Implementation Center) .tw/cic_v13/main.jsp 欧盟:Europractice / 上海集成电路设计研究中心 /icc/index.asp 中国科学院EDA中心 /index.htm

Manufacturing

12

3、几种工艺方法 1) oxidation (氧化)

氧气

Si-substrate or P-type or N-type

SiO2

Si-substrate or P-type or N-type SiO2 是绝缘体。 它的作用是什么?

EE141 Integrated © Digital

Circuits2nd

Manufacturing

9

N-Well CMOS Process

EE141 Integrated © Digital

Circuits2nd

Manufacturing

10

Dual-Well CMOS Process

gate-oxide TiSi2 AlCu SiO2 Tungsten