MOSFET-1-清华大学半导体物理与器件

半导体物理与器件基础知识

9金属半导体与半导体异质结一、肖特基势垒二极管欧姆接触:通过金属-半导体的接触实现的连接。

接触电阻很低。

金属与半导体接触时,在未接触时,半导体的费米能级高于金属的费米能级,接触后,半导体的电子流向金属,使得金属的费米能级上升。

之间形成势垒为肖特基势垒。

在金属与半导体接触处,场强达到最大值,由于金属中场强为零,所以在金属——半导体结的金属区中存在表面负电荷。

影响肖特基势垒高度的非理想因素:肖特基效应的影响,即势垒的镜像力降低效应。

金属中的电子镜像到半导体中的空穴使得半导体的费米能级程下降曲线。

附图:电流——电压关系:金属半导体结中的电流运输机制不同于pn结的少数载流子的扩散运动决定电流,而是取决于多数载流子通过热电子发射跃迁过内建电势差形成。

附肖特基势垒二极管加反偏电压时的I-V曲线:反向电流随反偏电压增大而增大是由于势垒降低的影响。

肖特基势垒二极管与Pn结二极管的比较:1.反向饱和电流密度(同上),有效开启电压低于Pn结二极管的有效开启电压。

2.开关特性肖特基二极管更好。

应为肖特基二极管是一个多子导电器件,加正向偏压时不会产生扩散电容。

从正偏到反偏时也不存在像Pn结器件的少数载流子存储效应。

二、金属-半导体的欧姆接触附金属分别与N型p型半导体接触的能带示意图三、异质结:两种不同的半导体形成一个结小结:1.当在金属与半导体之间加一个正向电压时,半导体与金属之间的势垒高度降低,电子很容易从半导体流向金属,称为热电子发射。

2.肖特基二极管的反向饱和电流比pn结的大,因此达到相同电流时,肖特基二极管所需的反偏电压要低。

10双极型晶体管双极型晶体管有三个掺杂不同的扩散区和两个Pn结,两个结很近所以之间可以互相作用。

之所以成为双极型晶体管,是应为这种器件中包含电子和空穴两种极性不同的载流子运动。

一、工作原理附npn型和pnp型的结构图发射区掺杂浓度最高,集电区掺杂浓度最低附常规npn截面图造成实际结构复杂的原因是:1.各端点引线要做在表面上,为了降低半导体的电阻,必须要有重掺杂的N+型掩埋层。

半导体物理与器件-第7章

第 7 章 MOS 结构及 MOSFET 器件

第 7 章 MOS 结构及 MOSFET 器件

第 7 章 MOS 结构及 MOSFET 器件

7. 1 理想 MOS 结构 7. 2 MOSFET 基础 习题

第 7 章 MOS 结构及 MOSFET 器件

MOS 结构是当今微电子技术的核心结构。 MOS 结构指的 是金属 ( Metal )、氧化物( Oxide )二氧化硅和半导体( Semiconductor )硅构成的系统,更广义的说法是金属 ( Metal )绝缘体(Insulator )半导体( Semiconductor )结 构,即 MIS 结构。其中用到的绝缘体不一定是二氧化硅。半 导体也不一定是硅。由于 MIS 结构和 MOS 结构较为相似, 在本章中将主要分析 讨论 MOS 结构。

第 7 章 MOS 结构及 MOSFET 器件

从半导体表面开始的空间电荷区内存在电场,到空间电荷区的 另一端,电场强度减小为零。由于存在电场,在空间电荷区内 还存在电势的变化,并导致电势能在空间电荷区内逐点 变化,导致了能带的弯曲。下面针对一种具体的 MOS 结构分 析它在不同的外加偏压下空间电荷区内的具体变化情况。

7. 1 理想 MOS 结构 在这一节中将讨论理想 MOS 结构的情况。

第 7 章 MOS 结构及 MOSFET 器件

7. 1. 1 MOS 结构的构成 MOS 结构由三部分组成,即由氧化层、氧化层隔开的金

半导体物理与器件考核试卷

B.硅化

C.硼化

D.镍化

17.在半导体工艺中,以下哪些步骤属于前道工艺?()

A.光刻

B.蚀刻

C.离子注入

D.镀膜

18.以下哪些材料常用于半导体器件的互连?()

A.铝

B.铜导线

C.镓

D.硅

19.在半导体物理中,以下哪些现象与载流子的复合有关?()

A.发射

B.复合

C.陷阱

D.所有上述现象

20.以下哪些因素会影响半导体激光器的阈值电流?()

半导体物理与器件考核试卷

考生姓名:__________答题日期:__________得分:__________判卷人:__________

一、单项选择题(本题共20小题,每小题1分,共20分,在每小题给出的四个选项中,只有一项是符合题目要求的)

1.半导体的导电性能介于导体和绝缘体之间,主要因为其()

C. Nitrogen(氮的)

D. Excess electrons(过剩电子)

5. P-N结在反向偏置时,其内部的电场强度()

A.减小

B.增大

C.消失

D.不变

6.以下哪个不是太阳能电池的工作原理?()

A.光电效应

B.热电效应

C.光生伏特效应

D.量子效应

7.在MOSFET(金属-氧化物-半导体场效应晶体管)中,MOS电容的C-V特性曲线中,积累区对应于()

18. A, B

19. D

20. D

三、填空题

1.禁带

2.电子

3.降低

4.金属-氧化物-半导体

5.温度

6.栅氧化层质量

7.紫外光

8.能级

9.玻尔兹曼分布

10.温度

半导体物理与器件第十一章1

VDS

VDS

L

ID

漏源电压VDS对漏电流ID有调制作用

求 L 与 VDS 的关系:

对漏和衬底形成的NP结,其可视为单边突变结, 施加的VDS可认为全部落在P衬底上,则漏源电压 为VDS时,漏-衬底结的空间电荷宽度为:

2 s xp (VB VDS ) qNA

当

VDS VDS (sat) VGS VT

11.1.2 沟道长度调制效应

沟道长度调制效应:当MOSFET偏置在饱和 区时,漏源电压VDS使漏端的耗尽区横向延 伸而进入沟道,沟道被夹断,从而减少了有 效沟道长度,影响到漏电流IDS的大小。

VDS (sat) VGS VT VDS VDS VDS (sat)

ID W nCox (VGS VT ) 2 2( L L)

kV D

kL

E

工作电流

kWn s o I D' (kVG VT ' ) 2 k 2 I D ktox kL

功耗

P' VD' I D' kVD k 2 I D 3k 2 P

数据来源:THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

则:

VTH

1 (QG QS ) Cox

QDS

Xd

QG

QDS

Xs

eN A xdT L L' (1 ) CO 2L

由几何推导可得:

2

L L' 2 2 (rj xdT ) (rj ) xdT 2

2 xdT L ' L 2r j [ 1 1] rj

半导体物理与器件物理

半导体物理、材料、工艺 半导体器件物理 集成电路工艺 集成电路设计和测试 微系统,系统

微电子学发展的特点

向高集成度、高性能、低功耗、高可靠性电路方向发展 与其它学科互相渗透,形成新的学科领域: 光电集成、MEMS、生物芯片

半导体概要

固体材料:绝缘体、半导体、导体 (其它:半金属,超导体)

MEM

Math

Bus

Controller

IO

Graphics

PCB集成 工艺无关

系统

亚微米级工艺 依赖工艺 基于标准单元互连 主流CAD:门阵列 标准单元

集成电路芯片

世纪之交的系统设计

SYSTEM-ON-A-CHIP

深亚微米、超深亚 微米级工艺 基于IP复用 主流CAD:软硬件协 同设计

1970

1980

1990

2000

2010

存储器容量 60%/年 每三年,翻两番

1965,Gordon Moore 预测 半导体芯片上的晶体管数目每两年翻两番

1.E+9 1.E+8 1.E+7 1.E+6 1.E +5 1.E+4 1.E+3

’70 ’74 ’78 ’82 ’86 ’90 ’94 ’98 ’2002

Pentium II: 7,500,000

微处理器的性能

100 G 10 G Giga 100 M 10 M Mega Kilo

1970 1980 1990 2000 2010

Peak Advertised Performance (PAP)

Moore’s Law

Real Applied Performance (RAP) 41% Growth

chapt7-MOS电容-清华大学半导体物理

MOSFET是现代数字集成电路的核心器件。

MOSFET剖面图•MOSFET与半导体表面及半导体-绝缘层界面性质密切相关。

•MOSFET的核心部分是MOS(MIS)结构。

2半导体表面以及半导体-绝缘层界面性质;表面电场效应(是MOSFEF工作的基础);MOS结构C-V特性。

4由于晶格周期性在表面处中断而出现的局(定)域于表面附近的电子态——表面态禁带中的电子态数等于表面原子数,表面原子面密度∼1015/cm 2,所以表面能级准连续地分布在禁带中。

总之,表面态起因于周期场在表面处中断;空间上定域于晶体表面;能级位于禁带中。

7.1.1 表面态§7.1 半导体表面和Si -SiO 2界面界面性质。

量级;离子。

界面态起源于界面处的。

界面态和表面态性质相似:位于Si-SiO101214151617达到最大且基本不变;19变化引起数量很大的2122V。

FB2324包括两部分:;V不很大s很小。

27对交流小信号ΔVQ n完全跟上ΔV g变化。

32scC-V是非平衡的瞬态特性333435若栅压V g 为一由V 1(积累)到V 2(强反型)的阶跃电压,则V =V 2下电容随时间的变化曲线称为MOS 电容的C -t 特性。

由MOS 电容的C -t 特性可求耗尽层少子寿命τ和表面复合速度S 。

,取“−”号,取“+”号i FB归一化平带电容与氧化层厚度及衬底掺杂浓度的关系。

半导体物理与器件

n0 Na p0 Nd

n0 Na pa p0 Nd nd

其中,n0:导带电子浓度;p0:价带空穴浓度。nd是施 主中电子密度;Nd+代表离化的施主杂质浓度;pa:受 主中的空穴密度;Na-:离化的受主杂质浓度。

掺杂时为本征载流子浓度

偿,类本征半导体

掺杂浓度大于ni时,杂质 电子浓度才起主要作用

半导体物理与器件

同理利用

p0

ni 2 n0

可推导出空穴浓度为:

p0

Na

2

Nd

Na

2

Nd

2

ni 2

例4.9的结果显示,在非 简并条件下,多数载流 子浓度近似等于掺杂浓

度(非补偿)

例4.10结果显示,在掺 杂浓度和本征载流子浓 度相差不大时,须考虑 本征载流子浓度的影响

Nc 2Nd

1

exp

Ec kT

Ed

1

绝对零度时,所有施主杂质 能级都被电子所占据,导带 无电子。

半导体物理与器件

§4.5 掺杂半导体的载流子浓度

前边讨论了本征半导体的载流子浓度;讨论了施主杂质和 受主杂质在半导体中的表现。定性的给出了杂质在不同温 度下的电离情况,并且定性的知道了载流子浓度和掺杂水 平的相关性。这节我们要具体推导掺杂半导体的载流子浓 度和掺杂的关系。

E Ec dE

Ec

1

exp

E

EF kT

仍然做变量代换

并且定义:

E Ec

kT

F

EF Ec kT

半导体物理与器件

载流子浓度公式变为:

半导体物理与器件-第十章-MOSFET基础(1)(MOS结构-CV特性)

11.2.2反型状态(高频)

加较大的正栅压,使反型层电荷出现,但栅 压变化较快,反型层电荷跟不上栅压的变化, 只有耗尽层电容对C有贡献。此时,耗尽层宽 度乃至耗尽层电容基本不随栅压变化而变化。

C' (inv)

C' (dep)min

tox

ox ox

tox

xdT

f 5 ~ 100Hz

f ~ 1MHz

强反型状态(低频)

加大的正栅压且栅压变化较慢,反型层 电荷跟得上栅压的变化

C' (inv)

Cox

ox

tox

平带 本征

41

10.2 C-V特性

n型与p型的比较

负偏栅压时为堆积模式, 正偏栅压时为反型模式。

p型衬底MOS结构

n型衬底MOS结构

正偏栅压时为堆积模式, 负偏栅压时为反型模式。

42

10.2 C-V特性

Cox

Cox

+2 fp

ms

| Q'SD max | Cox

VFB+2 fp

|QSDmax|=e Na xdT

f (半导体掺杂浓度,氧化层电荷,平带电压,栅氧化层电容)27

10.1 MOS电容 阈值电压:与掺杂/氧化层电荷的关系

P型衬底MOS结构

Q′ss越大,则VTN的绝对值 越大; Na 越高,则VTN的值(带符 号)越大。

栅压频率的影响

43

小节内容

理想情况CV特性

CV特性概念 堆积平带耗尽反型下的概念 堆积平带耗尽反型下的计算

频率特性

高低频情况图形及解释

44

10.2.3固定栅氧化层电荷和界面电荷效应

对MOS的C-V的影响主要有两种: (1)固定栅氧化层电荷 (2)氧化层-半导体界面电荷

MOSFET_2_清华大学半导体物理与器件

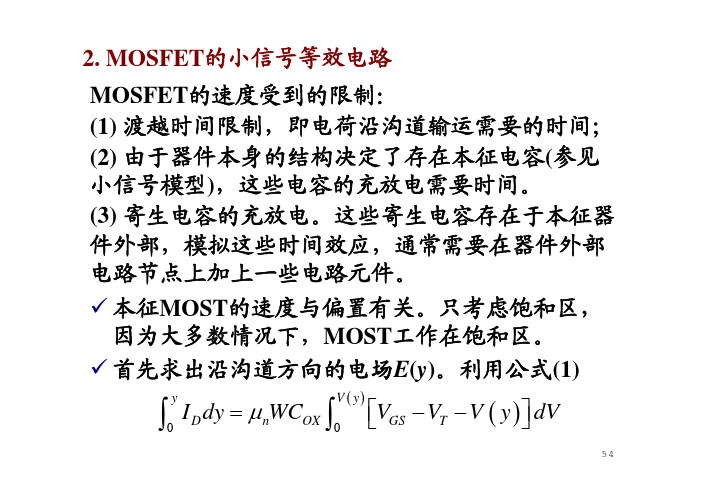

2. MOSFET 的小信号等效电路MOSFET 的速度受到的限制:(1) 渡越时间限制,即电荷沿沟道输运需要的时间;(2) 由于器件本身的结构决定了存在本征电容(参见小信号模型),这些电容的充放电需要时间。

(3) 寄生电容的充放电。

这些寄生电容存在于本征器件外部,模拟这些时间效应,通常需要在器件外部电路节点上加上一些电路元件。

9本征MOST 的速度与偏置有关。

只考虑饱和区,因为大多数情况下,MOST 工作在饱和区。

9首先求出沿沟道方向的电场E (y )。

利用公式(1)()()yV y D n OX GS T I dy WC V V V y dV μ=−−⎡⎤⎣⎦∫∫MOSFET 小信号等效电路•C GSO ,C GDO —栅源、栅漏覆盖电容•C GS —栅极-源端沟道电荷之间的电容•C GD —栅极-漏端沟道电荷之间的电容•C TS , C TD —衬底和源漏扩散区的pn 结势垒电容•R S , R D —源区、漏区串联电阻•R BS ,R BD ——源漏耗尽区边缘与衬底电极之间的欧姆电阻上述元件中,只有栅-沟道电容C GS 和C GD 对器件性能有实际意义跨导的含义:单位栅压变化导致漏极电流的变化量。

反映栅压对漏极电流的控制能力。

考虑速度饱和效应后,沟道长度对跨导的影响?和理想情况相比考虑速度饱和效应后,跨导仍然和沟道长度有关。

沟道越短,跨导越大,栅压对漏极电流的控制越强。

C BSC GSO C BDC GDO栅-沟道电容的Meyer 模型Meyer 模型中,栅-沟道之间的分布电容C GC 和C CB 被分解为三个集总电容:C GS ,C GD ,C GB而变化,仅沟道电荷随栅电压而变化。

0dV⎣⎦∫•Meyer模型虽然简单,但存在一些缺陷,主要缺陷是电荷不守恒,因而导致在模拟动态RAM和开关电容之类的电路时误差较大。

但由其简洁性,仍被广泛采用于不存在电荷守恒问题的电路模拟中。

Meyer模型是SPICE Level=1~4级模型采用的缺省电容模型。

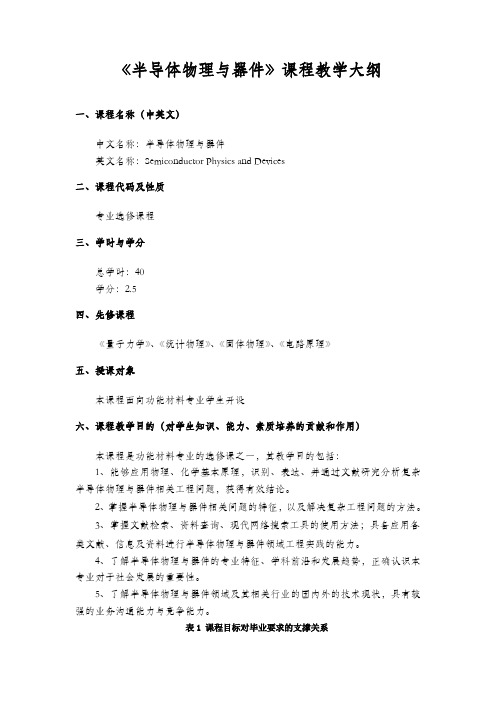

《半导体物理与器件》课程教学大纲

《半导体物理与器件》课程教学大纲一、课程名称(中英文)中文名称:半导体物理与器件英文名称:Semiconductor Physics and Devices二、课程代码及性质专业选修课程三、学时与学分总学时:40学分:2.5四、先修课程《量子力学》、《统计物理》、《固体物理》、《电路原理》五、授课对象本课程面向功能材料专业学生开设六、课程教学目的(对学生知识、能力、素质培养的贡献和作用)本课程是功能材料专业的选修课之一,其教学目的包括:1、能够应用物理、化学基本原理,识别、表达、并通过文献研究分析复杂半导体物理与器件相关工程问题,获得有效结论。

2、掌握半导体物理与器件相关问题的特征,以及解决复杂工程问题的方法。

3、掌握文献检索、资料查询、现代网络搜索工具的使用方法;具备应用各类文献、信息及资料进行半导体物理与器件领域工程实践的能力。

4、了解半导体物理与器件的专业特征、学科前沿和发展趋势,正确认识本专业对于社会发展的重要性。

5、了解半导体物理与器件领域及其相关行业的国内外的技术现状,具有较强的业务沟通能力与竞争能力。

表1 课程目标对毕业要求的支撑关系七、教学重点与难点课程重点:(1)掌握能带理论以及从能带理论的角度分析半导体的导电机制;熟悉半导体中电子的状态及其运动规律;熟悉实际半导体中的杂质和缺陷的种类、性质及其作用;掌握并且会计算热平衡状态下载流子的浓度问题以及非平衡载流子的概念、产生及其随时间的演化规律(寿命问题);掌握载流子的几种输运机制。

(2)理解和熟悉PN结及其能带图;掌握PN结的电流-电压特性以及电容-电压特性;熟悉PN结的三种击穿机理;理解和掌握PN结二极管的工作原理。

(3)在对PN结二极管工作原理分析的基础上,学会将此分析进行合理的拓宽,即从单结/两端二极管发展到双结/三端晶体管;掌握双极型晶体管(BJT)的基本概念、符号的定义、工作原理的定性分析以及关键的关系表达式等。

(4)系统地了解和掌握MOSFET的基本工作原理与物理机制;掌握MOSFET器件的主要结构形式、工作特性和有关的物理概念;熟悉MOSFET的电容-电压特性、伏-安特性及其交流效应,并能掌握主要参数和特性的分析与计算方法;了解半导体器件制备的方法、过程及几个器件制备的实例。

半导体物理

二维半导体薄膜

03

基于光子的量子计算机

利用光子实现量子比特,表现出传输速度快和适合分布式计算的优点。

量子信息和量子计算

01

基于超导量子比特的量子计算机

通过超导电路实现量子比特,实现算力呈指数级增长的计算能力。

02

基于离子阱的量子计算机

性质

定义和性质

半导体材料

如硅和锗,是最常用的半导体材料。

元素半导体

化合物半导体

非晶半导体

纳米半导体

由两种或两种以上的元素组成的化合物,如砷化镓、碳化硅等。

由非晶态物质组成的半导体,如非晶硅、非晶硒等。

由纳米结构组成的半导体材料,具有尺寸效应等特殊性质。

19世纪末和20世纪初:半导体概念的形成和发展。

பைடு நூலகம்

半导体光电子器件和光子集成

06

半导体物理的应用领域

微电子学

半导体物理研究为微电子学的发展提供了理论基础和技术支持,使得集成电路的制造成为可能,推动了电子工程领域的进步。

电子器件设计

半导体物理的研究为电子器件的设计提供了理论基础,如设计更高效的太阳能电池、发光二极管和激光器等。

电子工程和计算机科学

根据应用需求,选择不同材料和性质的薄膜。

薄膜制备方法

包括物理沉积、化学沉积、分子束外延等。

薄膜质量影响因素

包括温度、压力、磁场、电场等。

薄膜制备

包括离子注入、扩散、化学气相沉积等。

掺杂方法

杂质种类和作用

杂质控制技术

包括施主杂质和受主杂质,对半导体导电性能的影响不同。

采用多种掺杂方法,结合半导体制造工艺,实现杂质的有效控制。

清华大学微电子本科生培养课程设置.

一、简介

微纳电子系本科生一级学科名称为电子科学与技术,二级学科名称为微电子

学。

二、课程设置

课程编号:30260093 课程名称:固体物理学

课程属性:专业核心课开课学期:09秋

任课教师:王燕

内容简介:固体物理学是固体材料和固体器件的基础。

该课程主要研究晶体的

结构及对称性,晶体中缺陷的形成及特征,晶格动力学,能带理论的基础知识以及晶体中的载流子输运现象等。

是微纳电子专业的核心课。

课程编号:40260103 课程名称:数字集成电路分析与设计

课程属性:专业核心课开课学期:09秋

任课教师:吴行军

内容简介:本课程从半导体器件的模型开始, 然后逐渐向上进行, 涉及到反相器, 复杂逻辑门 (NAND , NOR , XOR , 功能模块(加法器,乘法器,移位器,寄存器和系统

模块(数据通路,控制器,存储器的各个抽象层次。

对于这些层次中的每一层,都确定了其最主要的设计参数,建立简化模型并除去了不重要的细节。

课程编号:40260173 课程名称:数字集成电路分析与设计(英

课程属性:专业核心课开课学期:09秋

任课教师:刘雷波。

清华大学(微电子学研究所)集成电路工程硕士人才培养

清华(电子信息)本科 生课程设置

任选 限选 4 8 核心 25 论文 15

15

核心课程

电磁场与波 数字信号处理 信号处理实验与设计 通信电路 通信电路实验 微波工程基础 电磁场与微波实验 随机过程 专业实践

25

3 4 2 3 1 3 1 4 5

政治 14 体育 军事 4 外语 3 6 文化 13 公共课程 40

– – – – – –写(Written)–说(Oral)–画(Graphic)–听(Listening) Business & management skills(商业头脑与管理技能) Histor(历史) –The environment(环境) –Customer and societal needs(客户和社会需求)

单片机和嵌入式系统 数字系统集成化设计与综合

模拟集成电路分析与设计 集成电路课程设计

数字VLSI系统的高层次综合 结构化集成电路设计

2004年以来工程硕士招生和毕 业情况

6

2012-3-14

培养精品工程师是我们的目标

工学博士在校 及毕业数字

在校生 2011级 2010级 2009级 2008级 2007级 毕业生 2011年 2010年 2009年 2008年 2007年 2006年 2005年 2004年 22 26 19 16 12 15 13 19 13 10 12 9 13

5

2012-3-14

集成电路设计方向的研究生知识结构

电路类课程 课程 电路原理 模拟电子技术基础 数字逻辑电路 通信电路 数字集成电路分析与设计 数字大规模集成电路 模拟大规模集成电路 高等模拟集成电路 实验 电路原理实验 电子技术实验 通信电路实验 信号类课程 通信/计算机 课程 实验 课程 实验 信号与系统 通信原理概论 通信原理实验 数字信号处理 信号处理实验与设计 现代通信原理 高频电路系统课程设计 微机原理 射频通信系统课程设计

BJT-清华大学半导体物理与器件

Bipolar JunctionTransistors双极型晶体管14集成电路中的npn-BJT杂质分布特点:•两头大,中间小•发射区掺杂浓度比基区高很多•四层结构•A E < A C本征晶体管非本征晶体管•埋层•隔离:采用pn 结5双极晶体管的四个工作区9正向有源区(正向放大模式,有源模式)——发射结正偏,集电结反偏9反向有源区(反向放大模式)——发射结反偏,集电结正偏SaturationCutoffActive InvertedV CB (pnp )V BC (npn )V EB (pnp ) V BE (npn )9截止区——两个结都反偏9饱和区——两个结都正偏双极型晶体管使用时,有共基极、共发射极和共集电极三种接法。

BJT的电流方向67理想npn-BJT ( 原型BJT )8•发射结正偏•集电结反偏910处于正向有源区BJT 的内部少子分布示意图162. 杂质任意分布的晶体管理论BJT 的晶体管作用主要发生在基区,研究基区的特性是获得BJT 电流电压关系的关键。

•缓变基区——基区杂质分布为任意形式•通过缓变基区的研究,将获得BJT 的基区电场分布、载流子分布以及电流分布的公式•介绍BJT 的一个重要的参数——基区渡越时间常数182.1 基区电流求基区非平衡少子(电子) 分布及电流密度分布——Moll-Ross方法推导前提是6个基本假定:1)少子在基区中的运动是一维的2)基区宽度大于载流子的平均自由程3)基区中准中性近似成立4)载流子的迁移率等于常数(可以引入平均迁移率)5)基区处于小注入状态6)忽略基区复合(对于现代高β-BJT是成立的)1922问题:分析基区电流的漂移流成分与扩散流成分归一化基区非平衡少子浓度分布2.3 重掺杂发射区为了获得高增益,发射结要求高注入比,即I pE(–x E) << I nB(0) ,因此发射区要求重掺杂1) 禁带变窄•重掺杂会导致电子在杂质原子之间进行共有化运动。

新能源相关专业中“半导体物理与器件”课程教学

新能源相关专业中“半导体物理与器件”课程教学发布时间:2021-03-17T16:09:31.083Z 来源:《中国电业》2020年31期作者:窦瑶[导读] 半导体物理与器件是新能源相关专业的基础课程,也是电子科学与技术窦瑶成都职业技术学院摘要:半导体物理与器件是新能源相关专业的基础课程,也是电子科学与技术,光电子信息工程,微电子等专业的重要基础课程。

为了适应新时代高等教育的要求,应着重于培养学生的创新和创业技能,学生的实践技能和学生的自主学习技能。

本文主要从课程教育改革入手,分析当前课程存在的问题和不足,并结合本课程的专业特点,探索教育理念,教学方法,教学模式和综合绩效评价标准的改革,并改进这一过程。

提高教育质量,提高学生的创新创业能力和实践能力,提高学生的整体素质。

关键词:半导体物理与器件;课程教学;有效策略1.引言随着新能源产业、半导体技术和集成电路的飞速发展,现代半导体产业已经形成了设计,制造,封装和测试的完整产业链,其应用包括计算机,汽车电子,太阳能电池,光纤通信,半导体照明和平板显示器,已经成为国民经济发展的重要战略产业。

半导体物理和器件课程是获取半导体技术的主要课程,旨在研究半导体材料和器件的基本性能和内部机理,并且是集成电路技术,设计和应用研究的重要理论基础。

该课程理论基础较深,知识点多,范围广,理论推导复杂,纪律性强,对学生的数学物理基础有很高的要求。

当前教科书和传统教学方法的大多数特征都强调的理论推导,导致学生逐渐失去对学习兴趣,从而影响教学质量。

因此,迫切需要改善这些问题和不足,并优化和整合教育内容。

2.半导体物理与器件教学面临的问题2.1课程内容抽象,教学方法缺乏吸引力“半导体物理和器件”课程是一门涵盖了广泛的内容,抽象的概念和知识点,以及更复杂的理论推导和公式的课程。

该课程的传统教学方法采用“以课本为中心,知识驱动”的教学方法,这种教学方法忽略了学生的主体地位,缺乏生动的案例描述。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOSFET

金属-氧化物-半导体场效应晶体管M etal O xide S emiconductor

F ield E ffect T ransistor

1. MOSFET的基本工作原理纵向结构:

金属-氧化层-半导体

横向结构:

源区-沟道区-漏区

四端(4个电极):

漏极D (Drain)

栅极G (Gate)

源极S (Source)

衬底B (Bulk ,

Substrate)

几何参数:W、L和t

OX

区域划分:有源区,场区

p

1.1 电流-电压关系

推导理想长沟MOSFET 基本的电流电压关系:

上图:强反型状态MOSFET 的坐标系统

V (y ) ——以源端为参考点的沟道电势V B =V S =0

V (y )

进一步分析电流饱和:

漏电压大于饱和漏电压后,沟道中的电势分布

V T=1V

•沟道夹断点的电势始终是V Dsat

•漏源电压大于V Dsat的那一部分(V DS−V Dsat) 全部降落在夹断区上。

•沟道电子一旦运动到夹断点,就会被空间电荷区反偏电压扫到漏区

沿沟道方向导带底的弯曲

沿沟道方向的电场分布

nMOSFET:V GS −V T = 2V

源端沟道电场随漏极电压的变化:

MOSFET 的水库模型

V DS = 0线性区

饱和区

考虑沟道长度调制效应:

漏极电流不饱和,输出电阻为有限值

实线:不考虑CLM

虚线:考虑CLM

V GS >V T V SB > 0

(()22B SB s A Fp V Q V q N φε+=参考公式(7.63)

三维能带图

V B=0, V S=V D =0

V B = −1V, V S =V D =0

三维能带图

加上衬偏电压后,需要能带更大的弯曲才能使表面反型,因此需要更大的栅电压,也就是说阈值电压上升了。

向的变化

实际情况:

MOS1(approx)和MOS2(exact)非饱和区输出特性曲线的比较

1.5 离子注入调整阈值电压离子注入工艺能够比

较精确地调整阈值电

压的大小

右图:典型的离子注

入形成的掺杂分布

•实线:离子注入后的

杂质分布

•虚线:退火后的分布•点线:用于计算阈值

电压的近似分布

根据注入深度x

i 的不同,分三种情况来分析:

①深注入x

i >> x d max(最大表面耗尽区厚度)

②中等深度注入x

i < x d max

③浅注入x

i

<< x d max

9第①种情形可以直接利用阈值电压公式计算。

缺点:提高了耗尽区靠近衬底一侧的掺杂浓度,增大了衬底电容;降低了沟道区击穿电压;阈值电压受衬偏的影响更加严重。

9第③种情形,相当于杂质全部位于表面无限薄的硅中。

薄层中离化的受主中心的作用与氧化层电荷相似,可等效于平带电压中增加了一个修正项。

浅注入的衬偏调制系数γ最小,但浅注入器件实际上很难做到。

1.6 亚阈值电流

MOSFET的一级近似认为:

>V T时,才能有漏极电流流过MOSFET 只有V

GS

这对大多数实际情况是

适用的。

但在某些应用

中,非常小的电流也是

不能忽略的,例如低功

耗IC或DRAM。

V GS<V T时的漏极小电流

称为亚阈值电流。

萨方程不适用于亚阈值区的原因:

9强反型近似中的关于耗尽层的假定不适用

z该假定认为:V GS≤V T时,Q n=0。

z实际上,Q n随表面势指数变化。

当栅电压低于阈值电压时,Q

指数下降,漏极电流也是如此。

n

z强反型时,由于|Q n|数值很大,计算|Q n|时可忽略V GS=V T时已经出现了的表面电子电荷。

9只考虑了漂移电流,未考虑扩散电流

在亚阈值区,扩散电流>>漂移电流。

亚阈值区导电与BJT中基区的电流传输有些相似。

MOSFET的表面势分布

(V

很小, p型衬底为零电势)

DS

(a)

(b)

表面为积累状态

(c)

(d)

表面为强反型状态表面为弱反型状态

(亚阈值区)

9在亚阈值区,漏极电压几乎全部降落在反偏漏衬结上,因此,漏极电流的漂移流部分可以忽略。

9自由载流子浓度沿沟道方向的梯度相当大,因此,亚阈值电流的主要成分是扩散流,类似于双极晶体管(BJT)的基区电流。

9栅极电压V

G 使半导体表面能带弯曲,降低了从源区

到沟道区的电子势垒,电子从重掺杂的源区(类似BJT的发射区)注入到p型表面区(类似BJT的基区),大部分注入的电子被漏区收集(类似BJT的集电区)。

9MOSFET亚阈值区与BJT导电的物理机制的区别:

z MOSFET亚阈值导电的注入是局部的,只发生在表面区域;

z BJT中V BE是外加的,MOSFET与之类似的电压

是沟道靠近源区一端的表面能带弯曲和源极电压

V S的差值。

载流子。

9降低S 的方法:

降低t OX ;降低衬底掺杂浓度N sub ;

提高衬偏电压|V BS |;降低界面陷阱密度D it 9S 的极限:理想情况下,C OX >> (C D +qD it ),n=1

S = 59.6 mV/decade

9室温(25℃)下,现代典型工艺制造的MOSFET 的S 值范围为70到120mV/decade 。

9对设计者来说,S 的大小非常重要,因为设计者需要用它来确定保证MOSFET 处在“关”态所需要的栅压

9例如:MOSFET 处在“关”态的标准是当V G =0时流过漏极的电流不超过V G =V T 时漏极电流的0.001。

如果给定了S ,就可以求出V T 的下限。

在MOS数字电路设计中,对ON/OFF电流比的要求限制了可用阈值电压的范围。

较低的阈值电压可以降低对电源电压的要求。

为达到某些电路要求的性能,可以用更为精细的工艺制造出两种不同阈值电压的n沟MOSFET。

这样,大部分晶体管的阈值电压较高,限制了关态电流,从而降低了静态功耗。

但是也有较小一部分晶体管需要在开启状态下能够提供较大的电流(保证高速工作),这些器件的阈值电压就设计的比较低。

为了获得高性能,必须付出的代价是较高的关态电流。

为了减小这些晶体管的泄漏电流,我们可以在这些晶体管不工作的时候,加上衬偏电压来提高它们的阈值电压。

1.7 电场对迁移率的影响

在前面的分析中,假设载流子迁移率是常数。

但实际

上,V

GS 和V

DS

分别在沟道中产生的纵向电场和横向电

场,都会对载流子的迁移率产生影响。

1.7.1 迁移率下降

MOSFET的漏极电流是可动电荷Q n在电场的作用下,沿着靠近表面区域移动的结果。

这些电子受到表面散射、受主杂质散射以及热声子散射的影响。

严格求解这些现象对载流子迁移率的影响是不可行的,但是,通过引入表面附近x轴方向的有效电场ℰ

eff

来作近似处理,可以得到比较简单的迁移率模型

Si-SiO 2界面和反型层边缘:

界面势垒和Si 导带势垒

反型层边缘

散射

•(18)式在较大的范围内都是成立的,在这个范围内载流子主要受声子散射的限制。

但是当其它散射机构占支配地位,比如在低温(77K)。