典型处理器及体系结构

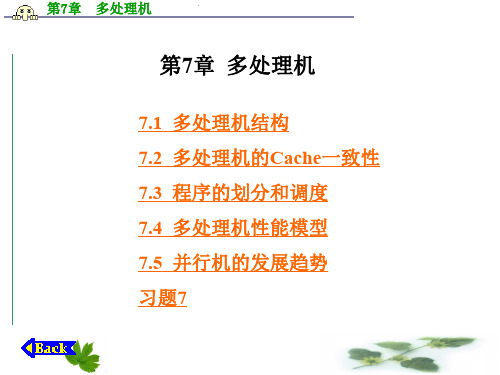

计算机体系结构-第7章 多处理机

第7章 多处理机

主 CPU

主存

CIOP

高速系统总线 BIOP NIOP GIOP

ACOP

CIOP----字符处理机 BIOP----数组处理机 NIOP----网络处理机 GIOP----图形处理机 ACOP----向量加速处理机

图7.5 异构非对称式多处理机的一般结构

第7章 多处理机

2. 松耦合(loosely coupled)多处理机 松耦合多处理机是通过消息传递方式来实现处理机间的相互通 信的。 而每台处理机是由一个独立性较强的计算机模块组成,该模 块由处理器、较大容量的本地存储器(在运算时所需的绝大部分的 指 令 和 数 据 均 取 自 本 地 存 储 器 ) 、 I/O 设 备 以 及 与 消 息 传 递 系 统 (Message Transfer System,MTS)相连的接口组成。当不同模块上 运行的进程间需要通信时,可通过网络接口电路及消息传递系统 进行信息交换。由于这种相互间的耦合程度是很松散的,因此称 之为松耦合多处理机。 松耦合多处理机可分为非层次式和层次式两种结构。

第7章 多处理机

(5)合理地进行资源分配和任务调度。 在MIMD多处理机中,由于任务的大小不相同, 各处理机的速度也可能不相同(如异构型多处理机系统), 互连网络的拓扑结构和通信延迟在不同的多处理机中 也有很大的差别,在执行并发任务时,并不是使用的 处理机个数越多,系统获得的性能就越高。因此需要 采用软件手段,合理地进行资源分配和任务调度,否 则系统性能将受较大影响。而在SIMD并行处理机中, 程序员只需用屏蔽的手段来设置部分处理单元为不活 跃状态,来控制实际参加并行操作的处理单元数目。

因此,Cm*是一个三层总线多处理机,三级的访 存时间分别为:计算机模块内3.5μs,计算机模块群内 9.3μs,而群间则为26μs。

第2章 ARM体系结构

• 控制位

–

程序状态寄存器PSR(Program Status Register)的最低8位I、F、T和 M[4:0]用作控制位。当异常出现时改变控制位。处理器在特权模式 下时也可由软件改变。

• 中断禁止位 I:置1,则禁止IRQ中断; F:置1,则禁止FIQ中断。 • T位 T=0 指示ARM执行; T=1 指示Thumb执行。 • 模式控制位 M4、M3、M2、Ml和M0(M[4:0])是模式位,决定处理器 的工作模式,如表2.3.1所列。

6 (最低)

6 5

数据中止

IRQ (外部中断请求) FIQ (快速中断请求)

中止(数据)

IRQ FIQ

中止模式

IRQ FIQ

0x0000,0010

0x0000,0018 0x0000,001C

2

4 3

2.4.2 异常类型的含义

(1)复位

• • 处理器的复位电平有效时,产生复位异常 当ARM处理器或协处理器遇到不能处理的指令时,产生未定义指令异常

2.4 ARM微处理器的异常处理

• 异常:在一个正常的程序流程执行过程中,由内 部或外部源产生的一个事件使正常的程序产生暂 时的停止,称之为异常。

2.4.1 ARM体系结构的异常类型

• ARM体系结构支持7种类型的异常

• 异常出现后,强制从异常类型对应的固定存储器地址开始 执行程序。这些固定的地址称为异常向量(Exception Vectors)。

M[4:0]模式控制位

M[4: 0] 10000 10001 10010 10011 10111

处理器工作 模式 用户模式 FIQ模式 IRQ模式 管理模式 中止模式

可访问的寄存器 PC,CPSR,R14~R0 PC,R7~R0,CPSR, SPSR_fiq,R14_fiq~ R8_fiq PC,R12~R0,CPSR, SPSR_irq,R14_irq, R13_irq PC,R12~R0, CPSR, SPSR_svc,R14_svc, R13_svc PC,R12~R0, CPSR, SPSR_abt,R14_abt, R13_abt

电脑的大脑CPU

电脑的大脑CPU(中央处理器)CPU是中央处理单元(Central Processing Unit)的缩写,它可以被简称做微处理器(Microprocessor),不过经常被人们直接称为处理器(processor)。

不要因为这些简称而忽视它的作用,CPU是计算机的核心,其重要性好比大脑对于人一样,因为它负责处理、运算计算机内部的所有数据,而主板芯片组则更像是心脏,它控制着数据的交换。

CPU的种类决定了你使用的操作系统和相应的软件。

CPU主要由运算器、控制器、寄存器组和内部总线等构成,是电脑的核心,再配上储存器、输入/输出接口和系统总线组成为完整的电脑。

CPU的基本结构、功能及参数CPU主要由运算器、控制器、寄存器组和内部总线等构成。

寄存器组用于在指令执行过后存放操作数和中间数据,由运算器完成指令所规定的运算及操作。

CPU主要的性能指标有:1.主频主频也叫时钟频率,单位是MHz(或GHz),用来表示CPU的运算、处理数据的速度。

CPU的主频=外频×倍频系数。

很多人认为主频就决定着CPU的运行速度,这不仅是个片面的,而且对于服务器来讲,这个认识也出现了偏差。

至今,没有一条确定的公式能够实现主频和实际的运算速度两者之间的数值关系,即使是两大处理器厂家Intel和AMD,在这点上也存在着很大的争议,我们从Intel的产品的发展趋势,可以看出Intel很注重加强自身主频的发展。

像其他的处理器厂家,有人曾经拿过一块1G的全美达处理器来做比较,它的运行效率相当于2 G的Intel处理器。

所以,CPU的主频与CPU实际的运算能力是没有直接关系的,主频表示在CPU内数字脉冲信号震荡的速度。

在Intel的处理器产品中,我们也可以看到这样的例子:1 GHz Itanium芯片能够表现得差不多跟2.66 GHz Xeon/Opteron一样快,或是1.5 GHz Itanium 2大约跟4 GHz Xeon/Opteron一样快。

项目1:知识点2典型处理器及体系结构

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

8086 CPU

40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

VCC AD15 A16/ S3 A17/ S4 A18/ S5 A19/ S6 BHE/ S7 MN/MX RD HOLD (RQ/GT0) HLDA (RQ/GT1) WR (LOCK) M/IO (S2) DT/R (S1) DEN (S0) ALE (QS0) INTA (QS1) TEST READY RESET

(8) ALE地址锁存允许信号 (输出) 高电平有效,此信号在 T1 状态有效,为 地址码锁存的选通信号,送地址锁存器。 (9) READY准备就绪信号 (输入) 高电平有效,是从所寻址的存储器或 I/O 电路来的响应信号,用于解决CPU与慢速存储 器或 I/O 电路的同步问题。 CPU 在 T3 周期开始 采样 READY 线,若为低电平,则 T3 之后插入 TW等待周期直到READY为高电平,进入T4完 成数据传送。

2.2 8086的引脚信号及工作模式

一、8086的两种工作模式

最小模式:即由 8086 组成的单处理器系 统,所有的总线控制信号由 8086 直接产生, 系统中的总线控制逻辑电路被减到最少。

最大模式:即由 8086 组成的中等规模或

者大型的系统。包含两个或多个微处理器,

8086为主处理器,其它的为协处理器。

(2) 地址/状态信号线A19/S6~A16/S3(输出、三态)

在总线周期的第一个时钟周期(T1)用于输出 地址信号的最高4bit并锁存。

其它时钟周期中用来输出状态信号S6~S3, 其中: S6——低电平,表示8086当前与总线相连。 S5——表示标志寄存器中“中断允许位”的状态 (IF)。 S4, S3的组合指出了分段情况。如下表所示。

计算机体系结构

• 硬件和软件是学习计算机知识经常遇到的术语。 硬件是指计算机系统中实际设备的总称。它可 以是电子的、电的、磁的、机械的、光的元件 或设备,或由它们组成的计算机部件或整个计 算机硬件系统。 • 计算机系统包括大型机、中小型机以及微机等 多种结构形式,其硬件主要包括: 运算器、控 制器、存储器、输入设备和输出设备等部件。 • 计算机体系结构指的是构成计算机系统主 要部件的总体布局、部件的主要性能以及这些 部件之间的连接方式。

3.小型机的总线型结构 (3)以存储器为中心的双总线结构

图3-6是以存储器为中心的双总线结构。这种结构既保持了 单总线结构的优点,又在CPU和主存储器之间设置了一组高 速存储总线,供CPU与主存储器交换信息。当主存储器通过 存储总线和CPU交换信息时,主存储器还可以通过系统总线 和I/O设备交换信息,而不必经过CPU控制,即减轻了系统 总线的负担,又提高了传输速率。缺点是需要增加硬件。

•

•

•

(1)PCI总线

• PCI(Peripheral Component Interconnect)总线是当 前常用的总线之一,该总线是由 Intel、IBM、DEC公司 所定制的一种局部总线。PCI总线与CPU之间没有直接 相连,而是经过桥接(Bridge)芯片组电路连接。该总 线稳定性和匹配性出色,提升了CPU的工作效率,扩展 槽可达3个以上。它定义了32位数据总线,且可扩展为 64位。

4.大、中型计算机的通道型结构

图3-7是大、中型计算机的通道型结构,分主机、通道、 I/O控制器和I/O设备四级。组成大、中型计算机的目的 是为了扩大系统的功能和提高系统的效率。扩大系统 的功能要求配备日益增多的硬件和软件资源,提高系 统的效率则强调合理地管理和调度资源。 软件资源的增多, 信息存储问题就十 分突出,促使由一 级存储发展到多级 存储,甚至在主存 储器一级也采用多 存储体交叉访问技 术,出现了以存储 系统为核心的计算 机系统结构。

常用微处理器介绍

中断源 软件

外部中断

串行口

软件定时器

HS1.0

高速输出

HSI 数据

A/D 转换完成 定时器溢出

中断向量地址

2011H 2010H 200FH 200EH

200DH 200CH

200BH 200AH

2009H 2008H

2007H 2006H 2005H 2004H

2003H 2002H 2001H 2000H

其停止计数并恢复为 0。 ? 定时器 1产生高速输入单元 HSI 和高速输出单

元HSO的基准时间。

第二十页,编辑于星期一:十二点 三十九分。

高速输入单元

? 高速输入单元 HSI 可用定时器 1作实时时钟来

记录外部事件发生的时间。“高速”表示事

件的获取无需 CPU的干预。

方式选择位

事件定义

00

8 个正跳变为一个事件

? 微机测控系统中最常用的是 8位以及 16位单 片机。

第三页,编辑于星期一:十二点 三十九分。

3.1.1 MCS-51系列单片机

? Intel在20世纪 80年代初研制。在 80年代中期

以专利转让形式把 51内核给了许多半导体厂

商,形成了与 51指令系统兼容的单片机。 ? 目前,国内市场上以 Atmel和Philips 公司的 51

成准 16位。 ? 与51的主要区别:

? 取消累加器结构,可直接对寄存器组合及专用

寄存器构成的 256字节地址空间进行操作。 ? CPU通过专用寄存器直接控制 IO。

? HSI、HSO

? PWM

第十三页,编辑于星期一:十二点 三十九分。

80C196KB 及8098单片机引脚

第十四页,编辑于星期一:十二点 三十九分。

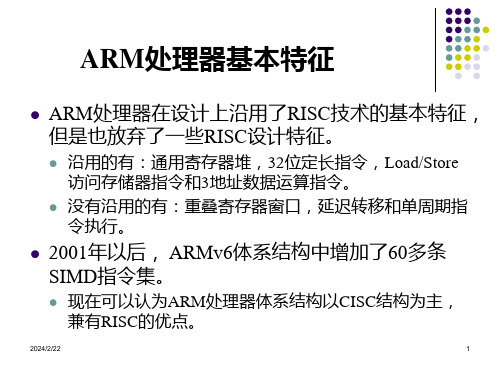

5ARM体系结构

配备MMU和 最快 最高 Cache

合理

媒体播放器,产品举 例:MP3,机顶盒, iPOD,智能手机,

PAD

去除MMU, 较快 合理 备有Cache

较低

数字信号处理,产品 举例:汽车ABS系统, 路由器,交换机,航 电系统

没有存储子 系统,即不 含MMU。

5

体系结构版本V3

这个体系结构版本将寻址范围扩展到了32位。 当前程序状态信息由过去存于R15中移到一个 新的当前程序状态寄存器CPSR(Current Program Status Register)中。增加了程序状态 保存寄存器SPSR(Saved Program Status Registers),以便当异常出现时保留CPSR的 内容。增加了2个指令(MRS和MSR),允许 访问新的CPSR和SPSR寄存器。

ARM状态,运行32位的ARM指令集 Thumb状态,运行16位的Thumb指令集 在任何一种工作状态可以通过转移指令切换到另一种

工作状态。 ARM和Thumb之间的状态切换不影响处理器工作模式

和寄存器中的内容。 加电起动时处理器工作在ARM状态。

2024/2/22

12

指令集压缩

对于传统的微处理器体系结构,指令和数据具有同样 的宽度。 与16位体系结构相比,32位体系结构在操纵32位数 据时呈显了更高的性能,并可更有效地寻址更大的 空间。 一般来讲,16位体系结构比32位体系结构具有更高 的代码密度,但只有近似一半的性能。

提高了T变量中ARM/Thumb之间切换的效率; 让非T变量同T变量一样,使用相同的代码生成技 术。增加了一个前导零计数(count leading zeros) 指令,该指令允许更有效的整数除法和中断优先 程序;增加了软件断点指令;为协处理器设计者 增加了更多可选择指令;对由乘法指令如何设置 标志进行了定义。

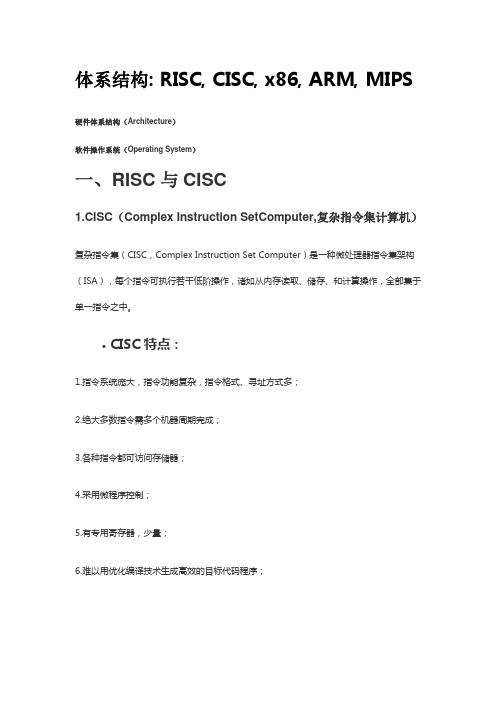

体系结构 RISC, CISC, x86, ARM, MIPS

体系结构: RISC, CISC, x86, ARM, MIPS硬件体系结构(Architecture)软件操作系统(Operating System)一、RISC与CISC1.CISC(Complex Instruction SetComputer,复杂指令集计算机)复杂指令集(CISC,Complex Instruction Set Computer)是一种微处理器指令集架构(ISA),每个指令可执行若干低阶操作,诸如从内存读取、储存、和计算操作,全部集于单一指令之中。

CISC特点:1.指令系统庞大,指令功能复杂,指令格式、寻址方式多;2.绝大多数指令需多个机器周期完成;3.各种指令都可访问存储器;4.采用微程序控制;5.有专用寄存器,少量;6.难以用优化编译技术生成高效的目标代码程序;在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

2.RISC(reduced instruction setcomputer,精简指令集计算机)精简指令集这种设计思路对指令数目和寻址方式都做了精简,使其实现更容易,指令并行执行程度更好,编译器的效率更高。

它能够以更快的速度执行操作。

这种设计思路最早的产生缘自于有人发现,尽管传统处理器设计了许多特性让代码编写更加便捷,但这些复杂特性需要几个指令周期才能实现,并且常常不被运行程序所采用。

此外,处理器和主内存之间运行速度的差别也变得越来越大。

在这些因素促使下,出现了一系列新技术,使处理器的指令得以流水执行,同时降低处理器访问内存的次数。

实际上在后来的发展中,RISC与CISC在竞争的过程中相互学习,现在的RISC指令集也达到数百条,运行周期也不再固定。

虽然如此,RISC设计的根本原则——针对流水线化的处理器优化—0—没有改变,而且还在遵循这种原则的基础上发展出RISC的一个并行化变种VLIW(包括Intel EPIC),就是将简短而长度统一的精简指令组合出超长指令,每次执行一条超长指令,等于并行执行多条短指令。

Cortex-M3体系结构学习笔记-寄存器知识

Cortex-M3体系结构学习笔记-寄存器知识要想了解Cortex-M3体系结构的知识,必须学习一下几个部分:CM3微处理器内核结构,处理器的工作模式及状态,寄存器,总线结构,存储器的组织与映射,指令集,流水线,异常和中断,存储器保护单元MPU。

这篇文章主要是我学习CM3机构寄存器的知识笔记。

Cortex‐M3 处理器拥有R0‐R15 的寄存器组。

其中 R13 作为堆栈指针SP。

SP 有两个,但在同一时刻只能有一个可以看到,这也就是所谓的“banked”寄存器。

CM3寄存器全局图如下所示:1. 通用寄存器通用寄存器包括R0-R12,R0-R7也被称为低组寄存器。

它们的字长全是32位的。

所有指令(包括 16位的和32位的)都能访问他们。

复位后的初始值是随机的。

R8-R12也被称为高组寄存器。

它们的字长也是32位的。

16位的Thumb指令不能访问他们,32位的Thumb-2指令则不受限制。

复位后的初始值也是随机的。

2.堆栈指针R13Cortex‐M3 拥有两个堆栈指针,然而它们是banked,因此任一时刻只能使用其中的一个。

•主堆栈指针(MSP):复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程)•进程堆栈指针(PSP):由用户的应用程序代码使用。

堆栈指针的最低两位永远是0,这意味着堆栈总是4 字节对齐的。

(在ARM 编程领域中,凡是打断程序顺序执行的事件,都被称为异常(exception)。

除了外部中断外,当有指令执行了“非法操作”,或者访问被禁的内存区间,因各种错误产生的fault,以及不可屏蔽中断发生时,都会打断程序的执行,这些情况统称为异常。

在不严格的上下文中,异常与中断也可以混用。

另外,程序代码也可以主动请求进入异常状态的(常用于系统调用).)在处理模式和线程模式下,都可以使用MSP,但只能在线程模式下使用PSP。

堆栈与微处理器模式的对应关系如下图所示。

使用两个堆栈的目的是为了防止用户堆栈的溢出影响系统核心代码(如操作系统内核)的运行。

CPU的功能和组成

CPU的功能和组成提交新文章CPU组成计算机的工作过程就是计算机执行程序的过程。

程序是一个指令序列,这个序列明确告诉计算机应该执行什么操作,在什么地方能够找到用来操作的数据。

一旦把程序装入主存储器,计算机就可以自动执行取出指令和执行指令的任务。

专门用来完成此项工作的计算机部件称为中央处理器(Central Processing Unit,CPU),做成单片集成电路的CPU通常又称为微处理器(Microprocessor)。

图3-1为陶瓷PGA封装的Intel 80486 DX2 CPU。

(a) 顶视图(b) 底视图图3-1 陶瓷PGA封装的Intel 80486 DX2 CPU计算机工业从1960年代早期开始使用CPU这个术语。

迄今为止,CPU从形态、设计到实现都已发生了巨大的变化,但是其基本工作原理却一直没有大的变化。

早期的CPU通常是为大型、特定的应用而定制的。

目前,这种为特定应用而设计定制CPU的昂贵方法,在很大程度上已经让位于开发可大规模生产的通用处理器。

这种标准化趋势,大致始于分立晶体管大型计算机(Mainframe)和小型计算机(Minicomputer)年代,并且随着集成电路(IC)的普及而大大加速。

集成电路可以把日益复杂的CPU设计制造在很小的空间里。

CPU的小型化和标准化,大大增加了这些数字器件在现代生活中的应用范围,远远超出了专用运算机器这一有限的应用。

现代微处理器已经随处可见,从汽车到手机,甚至儿童玩具。

3.1 CPU的功能和组成3.1.1 指令系统的发展指令是计算机硬件能够识别并直接执行操作的命令,一台计算机中所有指令的集合构成了该计算机的指令系统。

指令系统是表征一台计算机性能的重要因素,其格式与功能不仅直接影响到机器的硬件结构,也直接影响到系统软件,影响到机器的适用范围。

因此,设计一个合理有效、功能齐全、通用性强并且丰富的指令系统是至关重要的。

从计算机组成的层次结构来说,计算机的指令分为微指令、机器指令和宏指令三类。

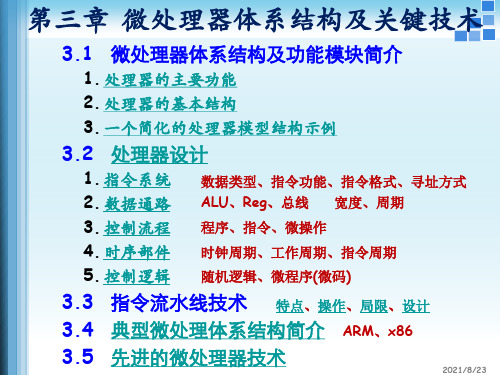

微处理器体系结构及功能模块

第一节 微生物农药

2.真菌杀虫剂

典型的代表是白僵菌杀虫剂。白僵菌是一种广谱寄生的真 菌,广泛地使昆虫致病,由该菌引起的病占昆虫真菌病的 21%左右,能侵染鳞翅目、鞘翅目、直翅目、膜翅目、同翅 目的众多昆虫及螨类。白僵菌接触虫体感染,适宜条件下其 分生孢子萌发长出芽管,并能分泌出几丁质酶溶解昆虫表皮 ,使菌丝侵入体内生长繁殖,并产生毒素(白僵菌素)和草 酸钙结晶,从而使昆虫细胞组织破坏和代谢机能紊乱,最后 虫体上生出白色的棉絮状菌丝和分生孢子梗及孢子堆,整个 虫体水分被菌吸收变成白色僵尸,白僵菌因此而得名。

第一节 微生物农药

1.细菌杀虫剂

苏云金芽孢杆菌杀虫剂,简称Bt杀虫剂,是当今使用最广 泛和产量最大的细菌杀虫剂。它是由昆虫病原细菌苏云金杆 菌的发酵产物加工而成,能防治直翅目、鞘翅目、双翅目、 膜翅目等上百种害虫,如稻纵卷叶螟、棉铃虫、茶毛虫、玉 米螟等。苏云金芽孢杆菌杀虫剂之所以成为目前产量最大、 应用最广、深受欢迎的农药,除其杀虫效果好外,更重要的 是对人、畜无伤害;对植物不产生药害,不影响农作物的色 、香、味;也不伤害害虫的天敌和有益的生物,能保持使用 环境的生态平衡;对土壤、水源、空气环境不造成污染,有 利于社会经济的持续发展。

3次指令,2次数据

1次指令,2次数据

若存储器速度为系统瓶颈,则应采用微码CPU

几个概念

1. 中央处理单元 控制器、运算器、寄存器

Central Processing Unit, CPU

2. 微处理器

单

片

Micro Processing Unit, MPU

芯 片

3. 微控制单元

Micro Control Unit, MCU

第一节 微生物农药

苏云金芽孢杆菌能在细胞内形成杀虫的伴胞晶体和水溶性 的外毒素(苏云金素)。伴胞晶体被敏感性昆虫的幼虫吞食 后,在其碱性的中肠溶解成原毒素,并进而在昆虫肠道被蛋 白酶水解激活,产生毒素核心片段(δ内毒素)。它与中肠 上皮细胞膜上的特异受体结合,能快速并不可逆地插入细胞 膜,形成孔洞,从而破坏细胞的膜结构与渗透吸收特性,使 中肠上皮细胞裂解崩溃,最终导致昆虫的死亡。

ARM体系结构

SIMD Instructions Multi-processing v6 Memory architecture Unaligned data support

Extensions: Thumb-2 (6T2) TrustZone® (6Z) Multicore (6K) Thumb only (6-M)

17

Embedded Processors

Chengdu University of Information Technology

18

Which architecture is your processor?

Chengdu University of Information Technology

---ARM V4

Chengdu University of Information Technology

7

•ARMV4是目前支持的最老的架构,是基于32-bit地址 空间的32-bit指令集。ARMv4除了支持ARMv3的指 令外还扩展了:

支持halfword的存取 支持byte和halfword的符号扩展读 支持Thumb指令 提供Thumb和Normal状态的转换指令 进一步的明确了会引起Undefined异常的指令 对以前的26bits体系结构的CPU不再兼容

4. 如果3中描述的功能不存在,则在该功能标识符前加x

ARM处理器命名(Classic命名)

Chengdu University of Information Technology

15

采用上述的架构,形成一系列的处理器。有时候还要区

分处理器核和处理器系列。不过,在这里其实不用区分太细,

计算机体系结构基础

计算机体系结构基础计算机体系结构是计算机科学中的一个重要概念,它定义了计算机硬件和软件之间的交互方式以及如何组织和设计计算机系统的结构。

本文将探讨计算机体系结构的基础知识,包括指令集体系结构、处理器架构和存储器层次结构。

一、指令集体系结构指令集体系结构(Instruction Set Architecture),简称ISA,是计算机体系结构的基础。

它定义了一组与硬件交互的指令集合,并规定了指令的格式、操作码和寻址方式等。

常见的指令集体系结构包括CISC (复杂指令集计算机)和RISC(精简指令集计算机)。

CISC架构的特点是指令集复杂,提供了丰富的指令集合和多种寻址方式,使得每条指令可以执行多个操作。

而RISC架构则强调指令集的精简性和规范性,将更多的工作转移到编译器层面。

两者的选择取决于需求和设计目标,如应用场景的复杂度和对计算速度和资源利用效率的要求。

二、处理器架构处理器架构(Processor Architecture)决定了计算机的运算能力和效率。

处理器是计算机体系结构的核心部件,其结构和设计方式关系到计算机性能的提升和效能的增加。

传统的处理器架构采用单指令流单数据流(SISD)方式,即每次只能执行一条操作指令和一条数据流,效率有限。

而后来出现的多指令流多数据流(MIMD)方式,则能够同时处理多条指令和数据流,提高了计算能力和效率。

此外,处理器架构还包括流水线结构和超标量结构等。

流水线结构将一条指令的执行过程划分为多个阶段,使得各个阶段可以并行进行,从而提高整体执行效率。

超标量结构则允许多条指令并行执行,更进一步提高了计算速度。

三、存储器层次结构存储器层次结构(Memory Hierarchy)是计算机体系结构中的重要组成部分,用于解决计算机存储器访问速度和容量之间的矛盾。

它按照存取速度和容量的大小将存储器划分为多个层次。

存储器层次结构的基本原理是利用不同层次存储介质的速度和容量差异来平衡。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中断允许标志IF(Interrupt-enable Flag):

IF=1,允许CPU响应外部的可屏蔽中断请 求;IF=0则禁止响应。IF对外部非屏蔽中 断及内部中断不起作用。

C、20位的地址加法器 用于形成20位访问的地址。

D、总线控制逻辑 对AB,DB,CB进行管理

E、指令队列 8086有6个字节,8088有4个字节

2.2 8086的引脚信号及工作模式

一、8086的两种工作模式

最小模式:即由8086组成的单处理器系 统,所有的总线控制信号由8086直接产生, 系统中的总线控制逻辑电路被减到最少。

OF DF IF TF SF ZF

AF

PF

CF

标志寄存器格式

a. 6个状态标志位,即CF、PF、AF、ZF、SF和 OF。

进位标志CF(Carry Flag):

当结果的最高位(字节-D7,字-D15)产生 进位(加法运算)或借位(减法运算)时,CF=1; 否则,CF=0,移位和循环指令也影响CF。

SP

BP

SI

DI

16位

地址

加法 ∑

20位

器

16位 CS

DS

SS

输入/输出

ES

控制电路

IP

外

内部暂存器

部

总

线

ALU

执行部分 控制电路

12 3 4 5 6 8位

指令队列缓冲器

标志寄存器 执行部件 (EU)

8086CPU的结构框图

总线接口部件 (BIU)

1>EU: 执行部件

①执行部件的功能:负责指令的执行。

方向标志DF(Direction Flag):

在串操作指令中,DF=0时,变址指针自 动增量,DF=1时,则自动减量。

D、算术逻辑单元ALU 用于完成数据的算术运算和逻辑运算等。

E、EU控制器 主要是对指令操作码进行译码, 产生各种微操作控制信号。

2>总线接口部件BIU

①功能:负责CPU与存储器,I/O接口之间 的数据传送。具体说就是从内存单元或 外设端口中取数据,传给执行部件或者 把执行部件的操作结果传送到指定的内 存单元或外设端口。

一、8086微处理器的内部结构结构

8086从功能结构来讲,分为两大 部 分 , 即 总 线 接 口 部 件 BIU(Bus Interface Unit ) 和 执 行 部 件 EU(Execution Unit)。

1. 总体功能结构

通用 AH AL AX

寄存 BH BL BX

器

CH CL CX DH DL DX

②执行部件的组成: 四个通用寄存器、四个专业寄存 器 、 一 个 16 位 的 标 志 寄 存器、算术逻辑单元、 EU控制器

A、4个16位通用寄存器 AX—累加器 乘除法作为隐含的乘数或除数,

I/O操作(AL) BX—基址寄存器 访问内存时存放地址 CX—计数寄存器 关于循环操作中用于计数 DX—数据寄存器 和AX进行综合操作,AX放

C、1个16位的标志寄存器 D0:CF 进位标志 D2:PF 奇偶标志 D4:AF 辅助进位标志 D6:ZF 零标志 D7:SF 符号标志 D8:TF 跟踪标志 D9:IF 中断标志 D10:DF 方向标志 D11:OF 溢出标志

FLAG(标志寄存器)为16bit,其中9位有定义

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

奇偶标志位PF(Parity Flag):

若结果中的低8位含有“1” 的个数为偶 数,则PF=1;否则,PF=0。

辅助进位标志AF(Auxitiary Carry Flag):

在低半字节向高半字节有进位或借位时 AF=1;否则,AF=0。

零标志ZF(Zero Flag):

当运算结果为0时ZF=1;否则,ZF=0。

②组成:

A、4个段地址寄存器 一般分为:CS,DS,ES,SS寄存器 CS(代码段寄存器)--

用来存放指令代码。 DS(数据段寄存器)--

数据段中存放程序的有关数据。 ES(附加段寄存器)--

存放运算结果或辅助数据。 SS(堆栈段寄存器)--

用于存放按后进先出顺序存取的信息。

B、指令指针寄存器IP 在程序运行时,由CS指定段地址, IP指定在段内的偏移量。

用表达式给出

OF溢出

CC157

C76 C1514

(字节运算) (字运算)

例:① 2345H+3219H

CF=0 PF=0 AF=0 ZF=0 SF=0 OF=0

② 6400H+7A3CH

CF=0 PF=1 AF=0 ZF=0 SF=1 OF=1

b. 3个控制标志位

追踪标志TF(Trace Flag):

符号标志SF(Sign Flag):

SF等于最高位,对于带符号数,最高位为 符号位,SF=1运算结果为负,SF=0为正。

溢出标志OF(Overflow Flag):

带符号数运算结果超出其表达范围时(字节数: -128 ~ +127 , 字 类 型 数 : -32768 ~ +32767 ) , OF=1;否则, OF=0。

最大模式:即由8086组成的中等规模或 者大型的系统。包含两个或多个微处理器, 8086为主处理器,其它的为协处理器。

GND

AD14

二、8086引脚图

AD13

D10 AD9

插式封装,有40个引

低16位,DX放高16位表示I/O端口号.

B、4个16位专用寄存器 BP:基址指针寄存器—

存放堆栈中某一存储单元的偏移量 SI:源变址寄存器—

存放数据段中源操作数所在存储单 元相对段首址的偏移量 DI:目的变址寄存器— 存放数据段中某目的操作数所在 存储单元的偏移量 SP:堆栈指针寄存器— 存放堆栈段中栈顶单元的偏移量。

学习目的

重点掌握8086处理器内部结构。 掌握 8086系统的构成和工作原理 理解存储器的结构。 了解总线操作及堆栈的工作原理。

2.1 8086微处理器的内部结构

8086微处理器字长16位,HMOS 工艺制造,芯片集成2.9万晶体管, +5V电源,40条引脚双列直插封装, 20根地址线,可寻址地址空间1MB, 时 钟 频 率 5MHz~10MHz , 基 本 指 令 执行时间0.3ms~0.6ms。